1.本实用新型涉及集成电路领域,更具体地说,涉及一种动态随机存取存储器及处理器模块。

背景技术:

2.目前,dram(dynamic random access memory,动态随机存取存储器)技术获得巨大发展,主要应用的有同步动态随机接入存储器(sdram)、双倍数据速率(ddr)sdram、第2代双倍数据速率(ddr2)sdram、第3代双倍数据速率(ddr3)sdram和第4代双倍数据速率(ddr4)sdram等多种类型。对于上述类型的dram,主要由内存控制器和dram晶片(即内存颗粒)构成,cpu(central processing unit,中央处理单元)经由内存控制器向dram晶片发送控制命令,包括时钟信号、命令控制信号以及地址信号等,并通过上述控制命令控制对dram晶片进行数据信号的读写操作。

3.在计算机系统在执行程序时,由cpu执行的相关程序和数据需先放入dram中,在执行程序时cpu根据当前程序指针寄存器的内容从dram取出指令并执行指令,然后再取出下一条指令并执行,如此循环下去直到程序结束指令时才停止执行。其工作过程就是不断地取指令和执行指令的过程,最后将计算的结果放入指令指定的存储器地址中。

4.然而,由于dram的成本较高,通常其存储容量有限,因此大部分程序存储在成本相对较低的大容量存储设备中,例如硬盘、固态硬盘等,在计算机运行时,cpu需将大容量存储设备中的数据搬移到dram,以及将dram的数据写入到大容量存储设备中。并且,因大容量存储设备与中央处理单元的交互速度均大大低于中央处理单元与dram的交互速度,因此大大影响了计算机系统的整体运行效率。

技术实现要素:

5.本实用新型要解决的技术问题在于,针对上述计算机系统中因中央处理单元与大容量存储装置交互速度影响整体运行效率的问题,提供一种动态随机存取存储器及处理器模块。

6.本实用新型解决上述技术问题的技术方案是,提供一种动态随机存取存储器,包括第一芯片、第二芯片以及桥接晶片,所述第一芯片内封装有闪存晶片,所述第二芯片内封装有dram晶片;所述第一芯片、第二芯片以及桥接晶片封装于第一封装体内,且在所述第一封装体内,所述第一芯片与所述第二芯片相叠设置,所述桥接晶片分别与所述第一芯片内的闪存晶片和第二芯片内的dram晶片耦合。

7.作为本实用新型的进一步改进,所述第二芯片的下表面设有多个第一电性导出件,所述桥接晶片包括多个第一金属垫,且每一所述第一电性导出件与一个所述第一金属垫电性连接。

8.作为本实用新型的进一步改进,所述第一电性导出件由位于所述第二芯片下表面的第一焊球构成;或者,所述第一电性导出件由延伸到所述第二芯片下表面的外缘的第一

引脚构成。

9.作为本实用新型的进一步改进,所述第一芯片包括与闪存晶片耦合的多个第二电性导出件;所述第二芯片的上表面具有与dram芯片耦合的多个第三电性导出件;

10.所述桥接晶片位于所述第一芯片和第二芯片之间,所述桥接晶片包括多个第二金属垫、多个第三金属垫,且所述第一金属垫、第二金属垫、第三金属垫均位于所述桥接晶片的上表面,每一所述第二金属垫与一个第二电性导出件电性连接,每一所述第三金属垫与一个第三电性导出件电性连接。

11.作为本实用新型的进一步改进,所述第二芯片的上表面包括重布线层、多个第四电性导出件和多个第五电性导出件,所述第三电性导出件、第四电性导出件和第五电性导出件均位于所述重布线层的表面,且所述第五电性导出件和第三电性导出件通过所述重布线层内的导电结构电性连接;

12.所述第一金属垫、第二金属垫、第三金属垫均位于所述桥接晶片的上表面,所述第二金属垫通过引线键合方式或所述桥接晶片上的硅通孔互连结与所述第五电性导出件电性连接,所述第三金属垫通过引线键合方式或所述桥接晶片上的硅通孔互连结与所述第三电性导出件电性连接;所述第一芯片通过第二电性导出件与第四电性导出件电性连接的方式相固定。

13.作为本实用新型的进一步改进,所述第二芯片的上表面包括重布线层和多个第六电性导出件;

14.每一所述第六电性导出件通过所述第二芯片上的硅通孔互连结构与一个所述第一电性导出件电性连接。

15.作为本实用新型的进一步改进,所述第一金属垫通过引线键合方式与所述第六电性导出件电性连接,或者所述第一金属垫通过所述桥接晶片上的硅通孔互连件与所述第六电性导出件电性连接。

16.作为本实用新型的进一步改进,所述第一芯片通过第二电性导出件与第二金属垫焊接连接的方式与桥接晶片相固定;所述桥接晶片的第三金属垫通过桥接晶片上的硅通孔互连结构与所述第二芯片的第四电性导出件电性连接并固定。

17.作为本实用新型的进一步改进,所述动态随机存取存储器包括封装在所述第一封装体内的第一基板,所述桥接晶片和第一芯片分别位于所述第一基板的上表面;

18.所述桥接晶片分别通过所述第一基板与所述第一芯片内的闪存晶片以及第二芯片内的dram晶片耦合。

19.作为本实用新型的进一步改进,所述桥接晶片包括第二金属垫和第三金属垫,所述第一芯片包括多个第二电性导出件,所述第二芯片的上表面具有多个第三电性导出件和第六电性导出件,每一所述第六电性导出件与一个第一电性导出件电性连接;

20.所述第一基板的上表面包括多个第一焊接部、多个第二焊接部、多个第三焊接部和多个第四焊接部,所述第一基板的下表面包括多个第五焊接部和多个第六焊接部;

21.每一所述第一焊接部通过所述第一基板内的第一导电线路与一个第二焊接部电性连接,且所述桥接晶片的第二金属垫与所述第一焊接部电性连接,所述第一芯片的第二电性导出件与所述第二焊接部电性连接;

22.每一所述第三焊接部通过所述第一基板内的第二导电线路与一个第五焊接部电

性连接,且所述桥接晶片的第三金属垫与所述第三焊接部电性连接,所述第二芯片的第三电性导出件与所述第五焊接部电性连接;

23.每一所述第四焊接部通过所述第一基板内的第三导电线路与一个第六焊接部电性连接,且所述桥接晶片的第一金属垫与所述第四焊接部电性连接,所述第二芯片的第六电性导出件与所述第六焊接部电性连接。

24.本实用新型还提供一种处理器模块,包括处理器晶片和如上任一项所述的动态随机存取存储器,且所述处理器晶片和动态随机存取存储器封装于第二封装体内。

25.作为本实用新型的进一步改进,所述处理器模块包括第二基板,所述处理器晶片和动态随机存取存储器分别叠于所述第二基板的上表面;

26.所述第二芯片的下表面设有多个第一电性导出件,所述第二基板的上表面包括若干第一焊盘和若干第二焊盘,所述基板的下表面包括若干第二焊球或若干第二引脚,且每一所述第一电性导出件分别与一个第一焊盘电性连接,每一所述第二焊盘与所述处理器晶片的一个金属垫电性连接,至少部分所述第二焊盘通过所述第二基板内的导电线路与所述第二焊球或第二引脚电性连接。

27.本实用新型的动态随机存取存储器及处理器模块具有以下有益效果:通过将dram晶片、闪存晶片及桥接晶片封装在一起,并通过桥接晶片直接根据中央处理单元正在执行的指令集更新dram晶片中的内容,从而中央处理单元无需与闪存晶片交互,使得中央处理单元可始终处于高效运行状态,适用于具有多个中央处理单元的系统,可大大提高系统的运行效率。

附图说明

28.图1是本实用新型提供的动态随机存取存储器的框图;

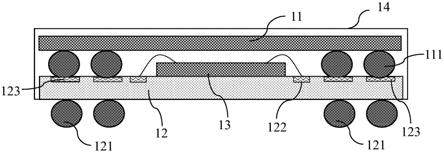

29.图2是本实用新型实施例提供的动态随机存取存储器的剖面结构示意图;

30.图3是本实用新型实施例提供的动态随机存取存储器中桥接晶片与第二芯片的电性连接结构的示意图;

31.图4是本实用新型实施例提供的动态随机存取存储器中桥接晶片与第二芯片的另一电性连接结构的示意图;

32.图5是本实用新型另一实施例提供的动态随机存取存储器的剖面结构示意图;

33.图6是本实用新型又一实施例提供的动态随机存取存储器的剖面结构示意图;

34.图7是本实用新型实施例提供的处理器模块的剖面结构示意图。

具体实施方式

35.为了使本实用新型的目的、技术方案及优点更加清楚明白,以下结合附图及实施例,对本实用新型进行进一步详细说明。应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

36.如图1所示,是本实用新型提供的动态随机存取存储器的框图,该动态随机存取存储器可应用于具有一个或多个中央处理单元的计算机系统,例如云服务器等,并用于暂存一个或多个中央处理单元执行的程序以及数据。本实施例的动态随机存取存储器包括第一芯片11、第二芯片12以及桥接晶片13。第一芯片11内封装有一个或多个闪存晶片(die),即

第一芯片11通过基板(substrate)或导线架(lead frame)及封装体将闪存晶片封装一体,上述闪存晶片具体可采用存储容量相对较大、成本相对较低、数据存取速度相对较慢的nand存储晶片等,其可在断电状态下保存数据;第二芯片12内封装有一个或多个dram晶片(die),即第二芯片12通过基板或导线架及封装体将dram晶片封装一体,上述dram晶片具体可采用存储容量相对较小(即第二芯片12的数据存储容量小于第一芯片11的数据存储容量)、成本相对较高、数据存取速度相对较快的ddr、ddr2、ddr3、ddr4、ddr5或相变存储器等存储晶片,该dram晶片通常在断电时无法保留存储的数据。上述第一芯片11和第二芯片12可具有不同的形状和尺寸,并且,当第二芯片12的尺寸大于第一芯片11的尺寸的两倍以上时,第一芯片11的数量也可多于第二芯片12的数量。

37.结合图2所示,在本实用新型的一个实施例中,动态随机存取存储器的第一芯片11、第二芯片12以及桥接晶片13共同封装于第一封装体14内,且在第一封装体14内,第一芯片11和第二芯片12相叠设置,桥接晶片13分别与第一芯片11内的闪存晶片和第二芯片12内的dram晶片耦合,从而桥接晶片13可分别与闪存晶片和dram晶片进行数据交互。上述第一封装体14可由绝缘材料(例如封装胶)构成,并可通过灌胶工艺等形成于第一芯片11、第二芯片12以及桥接晶片13外。通过第一封装体14,可对第一芯片11、第二芯片12以及桥接晶片13进行保护。

38.上述桥接晶片13可实现闪存晶片与dram晶片之间的数据搬移操作。具体地,在本实施例的动态随机存取存储器安装到包括中央处理单元(cpu)18的计算机系统时,当dram晶片中等待中央处理单元18读取的指令集(即中央处理单元未读取的指令集,上述指令集可包括指令代码以及数据)符合预设条件时,桥接晶片13可从闪存晶片中获取dram晶片中的指令集的后续指令集(包括指令代码以及数据),并将后续指令集存储到dram晶片。该桥接晶片13还可根据中央处理单元18的指令将dram晶片中的数据写入到闪存晶片。

39.上述动态随机存取存储器通过将dram晶片、闪存晶片及桥接晶片封装在一起,并由桥接晶片13直接根据中央处理单元正在执行的指令集更新dram晶片中的内容,使得dram晶片可根据中央处理单元的运行状态自动更新,从而只需小幅增加动态随机存取存储器的成本即可使其存储容量大大提升,适用于云计算等对运算资源要求较高的领域,可大大提高计算机系统的运行效率。

40.在本实用新型的一个实施例中,参见图2、图3,第二芯片12的下表面设有多个第一电性导出件121,桥接晶片13包括多个第一金属垫(pad)131,且每一第一电性导出件121与一个第一金属垫131电性连接。上述多个第一电性导出件12构成动态随机存取存储器的外接接口,通过该外接接口,动态随机存取存储器的桥接晶片13可耦合到计算机系统的主板,并与计算机系统的中央处理单元(cpu)18进行数据交互。

41.在第一封装体14内,第一芯片11可以叠于第二芯片12的上方,桥接晶片13可以位于第一芯片11和第二芯片12之间。其中,第一芯片11的下表面包括与闪存晶片耦合的多个第二电性导出件111(例如在第一芯片11内,每一第二电性导出件111与闪存晶片的主动表面上的一个金属垫电性连接),第二芯片12的上表面具有与dram晶片耦合的多个第三电性导出件122(例如在第二芯片12内,每一第三电性导出件122与dram晶片的主动表面上的一个金属垫(pad)电性连接);相应地,桥接晶片13包括多个第二金属垫、多个第三金属垫,且每一第二金属垫直接或间接与一个第二电性导出件111电性连接,每一第三金属垫与一个

第三电性导出件电性连接。

42.在本实用新型的一个实施例中,第二芯片12的上表面还包括多个第四电性导出件123,且每一第四电性导出件123与桥接晶片13的一个第二金属垫电性连接。第一芯片11和第二芯片12以第一芯片11的下表面朝向第二芯片12的上表面的方式相叠设置,桥接晶片13位于第一芯片11和第二芯片12之间,且第一芯片11的第二电性导出件111和第二芯片12的第四电性导出件123电性连接(例如第二电性导出件111可由焊球构成,第四电性导出件123则可由焊盘构成,且第二电性导出件111与第四电性导出件123焊接在一起)。在具体应用中,上述第二电性导出件111和第四电性导出件123可通过导电胶(例如掺有金属粉末的胶)焊接固定,且第一芯片11的下表面的其他部分(即除了第二电性导出件111外的部分)与第二芯片12的上表面之间则可填充绝缘材料(即第一封装体14),以提高动态随机存取存储器的整体结构强度和抗震性能。通过上述结构,桥接晶片13分别与第一芯片11内的闪存晶片、第二芯片12内的dram晶片耦合。

43.在本实用新型的一个实施例中,结合图3所示,桥接晶片13可通过以下方式与第一芯片11内的闪存晶片、第二芯片12内的dram晶片分别耦合:第二芯片12的上表面包括重布线层126,且该重布线层126的上表面包括多个第三电性导出件122、多个第四电性导出件123、多个第五电性导出件124(例如上述第三电性导出件122、第四电性导出件123、第五电性导出件可分别由焊盘构成),每一第五电性导出件124和一个第四电性导出件123通过重布线层内的导电结构电性连接;桥接晶片13的第二金属垫132通过引线键合(wire bond)方式与第五电性导出件124电性连接;桥接晶片13的第三金属垫133通过引线键合方式与第三电性导出件122电性连接,并且第一芯片11的第二电性导出件111和第二芯片12的第四电性导出件123电性连接(例如焊接)。这样,桥接晶片13的第二金属垫132经由第五电性导出件124、第四电性导出件123、第二电性导出件111与第一芯片11内的闪存晶片耦合,第三金属垫133则通过第三电性导出件122与dram晶片耦合。

44.在本实用新型的另一实施例中,结合图4所示,桥接晶片13还可通过以下方式与第一芯片11内的闪存晶片、第二芯片12内的dram晶片分别耦合:第二芯片12的上表面包括重布线层126,且该重布线层126的上表面包括多个第三电性导出件122、多个第四电性导出件123、多个第五电性导出件124,每一第五电性导出件124和一个第四电性导出件123通过重布线层内的导电结构电性连接;桥接晶片13的第二金属垫132通过硅通孔(tsv)互连结构与第五电性导出件124电性连接;桥接晶片13的第三金属垫133通过硅通孔互连结构与第三电性导出件122电性连接。并且第一芯片11的第二电性导出件111和第二芯片12的第四电性导出件123电性连接。这样,桥接晶片13的第二金属垫132经由第五电性导出件124、第四电性导出件123、第二电性导出件111与第一芯片11内的闪存晶片耦合,第三金属垫133则通过第三电性导出件122与dram晶片耦合。

45.在实际应用中,也可采用第二金属垫132和第三金属垫133中的部分采用引线键合技术与第二芯片12上的电性导出件电性连接、部分采用桥接晶片13上的硅通孔互连结构与第二芯片12上的电性导出件电性连接。

46.在本实用新型的一个实施例中,结合图3

‑

4所示,第二芯片12上表面的重布线层126还包括多个第六电性导出件125,并且,每一第六电性导出件125通过第二芯片12上的硅通孔互连结构与一个第一电性导出件121电性连接。

47.相应地,桥接晶片13的第一金属垫131通过可引线键合方式与第六电性导出件125电性连接,或者第一金属垫131也可通过桥接晶片13上的硅通孔互连结构与第六电性导出件125电性连接。

48.在本实用新型的一个实施例中,结合图5所示,与图3

‑

4的实施例不同的是,本实施例的第二芯片12的上表面仅包括第三电性导出件和第六电性导出件,而不包括第四电性导出件和第五电性导出件,第一芯片11通过第二电性导出件111(例如由焊球或焊柱构成)直接与第二金属垫电性连接的方式与桥接晶片13相固定。同时,桥接晶片13的第三金属垫通过桥接晶片13上的硅通孔互连结构与第二芯片12上表面的第三电性导出件(例如由焊球或焊柱构成)电性连接并固定。

49.在本实施例中,桥接晶片13的第一金属垫也通过桥接晶片13上的硅通孔互连结构与第二芯片12上表面的第六电性导出件(例如由焊球或焊柱构成)电性连接并固定。第六电性导出件可采用与图3

‑

4相同的方式与第二芯片12底部的第一电性导出件121电性连接。

50.在本实用新型的一个实施例中,结合图6所示,与图2

‑

5的实施例不同的是,本实施例的动态随机存取存储器除了包括第一芯片11、第二芯片12及桥接晶片外,还包括封装在第一封装体14内的第一基板17,桥接晶片13和第一芯片11分别位于第一基板17的上表面,且桥接晶片13分别通过第一基板17与第一芯片11内的闪存晶片以及第二芯片12内的dram晶片耦合。

51.具体地,本实施例中的桥接晶片13包括第一金属垫、第二金属垫和第三金属垫,第一芯片11包括多个第二电性导出件,第二芯片12的上表面具有多个第三电性导出件122和第六电性导出件125,每一第六电性导出件125与第二芯片12的下表面的一个第一电性导出件121电性连接。

52.上述第一基板17的上表面包括多个第一焊接部、多个第二焊接部、多个第三焊接部和多个第四焊接部,且该第一基板17的下表面包括多个第五焊接部和多个第六焊接部。上述第一焊接部、第二焊接部、第三焊接部、第四焊接部、第五焊接部和第六焊接部分别可由焊盘或焊球构成。

53.并且,每一第一焊接部通过第一基板17内的第一导电线路与一个第二焊接部电性连接,且桥接晶片13的第二金属垫与第一焊接部电性连接,第一芯片的第二电性导出件与第二焊接部电性连接,即桥接晶片13经由第二金属垫、第一焊接部、第一导电线路、第二焊接部、第二电性导出件与第一芯片11内的闪存晶片耦合。

54.每一第三焊接部通过第一基板17内的第二导电线路与一个第五焊接部电性连接,且桥接晶片13的第三金属垫与第三焊接部电性连接,第二芯片12的第三电性导出件与第五焊接部电性连接,即桥接晶片13经由第三金属垫、第三焊接部、第二导电线路、第五焊接部、第三电性导出件与第二芯片12内的dram晶片耦合。

55.每一第四焊接部通过第一基板17内的第三导电线路与一个第六焊接部电性连接,且桥接晶片13的第一金属垫与第四焊接部电性连接,第二芯片12的第六电性导出件与第六焊接部电性连接,即桥接晶片13通过第一金属垫、第四焊接部、第三导电线路、第六焊接部、第六电性导出件与第二芯片12底部的第一电性导出件121耦合(第六电性导出件可采用与图3

‑

4相同的方式与第二芯片12底部的第一电性导出件121电性连接)。

56.如图7所示,是本实用新型提供的处理器模块的结构示意图,该处理器模块包括处

理器晶片16和如上所述的动态随机存取存储器,且处理器晶片16和动态随机存取存储器封装在第二封装体内。上述处理器晶片16可以为嵌入式处理器,并且当该处理器模块应用于计算机系统时,处理器晶片16可作为计算机系统的中央处理单元。

57.上述处理器模块可直接安装到计算机系统的主板,且主板上无需再设置内存,而由处理器模块内的动态随机存取存储器实现内存功能,大大简化了计算机系统的结构。并且,由于动态随机存取存储器与处理器晶片16集成在一起,大大加快了处理器晶片16与动态随机存取存储器之间的数据交互速度。

58.在本实用新型的一个实施例中,上述处理器模块包括第二基板15,该第二基板15的上表面包括若干第一焊盘151和第二焊盘152,且第二基板15的下表面包括若干第二焊球(或第二引脚)153。每一第一焊盘151分别与一个第二焊球(或第二引脚)153电性连接,处理器晶片16包括多个金属垫,且该处理器晶片16的部分金属垫分别与第一焊盘151电性连接(例如通过引线键合工艺),从而实现处理器晶片16与第二焊球(或第二引脚)153的电性连接。

59.动态随机存取存储器与第二基板15之间通过第一电性导出件121和第二焊盘152焊接固定,从而实现第二基板15与动态随机存取存储器之间的电性连接。并且,处理器晶片16的另一部分金属垫与第二焊盘152电性连接(例如通过引线键合工艺),实现处理器晶片16与动态随机存取存储器的桥接晶片13的电性连接,从而处理器晶片16可与桥接晶片13进行数据交互。

60.以上所述,仅为本实用新型较佳的具体实施方式,但本实用新型的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本实用新型揭露的技术范围内,可轻易想到的变化或替换,都应涵盖在本实用新型的保护范围之内。因此,本实用新型的保护范围应该以权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。