[0001]

本公开涉及存储器电路及方法。

背景技术:

[0002]

存储器阵列通常用于存储和访问用于各种类型计算(例如逻辑或数学运算)的数据。为了执行这些操作,数据通过存储器阵列和用于执行这些计算的电路之间的数据端口而被移动。在一些情况下,存储器阵列中通过其访问存储数据的数据线的数目小于数据端口的数目,而且一些或全部数据线被共享用于数据移动操作。

技术实现要素:

[0003]

根据本公开的一个实施例,提供了一种存储器电路,包括:选择电路,被配置为:在第一输入处接收第一地址并在第二输入处接收第二地址,当选择信号具有第一逻辑状态时,将所述第一地址传递到输出,并且当选择信号具有不同于所述第一逻辑状态的第二逻辑状态时,将所述第二地址传递到所述输出;以及解码器,被配置为对所传递的第一地址或第二地址进行解码。

[0004]

根据本公开的另一实施例,提供了一种操作存储器电路的方法,所述方法包括:在选择电路处接收第一地址和第二地址;使用所述选择电路将所述第一地址或所述第二地址中的一个地址传递到地址解码器;并且使用所述地址解码器对所述第一地址或所述第二地址中的所述一个地址进行解码。

[0005]

根据本公开的又一实施例,提供了一种存储器电路,包括:存储器阵列;选择电路,被配置为:在第一输入处接收写入地址,并且在第二输入处接收读取地址,当选择信号具有第一逻辑状态时,将所述写入地址传递到输出,并且当所述选择信号具有不同于所述第一逻辑状态的第二逻辑状态时,将所述读取地址传递到所述输出;以及解码器,被配置为:对所传递的写入地址或读取地址进行解码,并且激活所述存储器阵列中与经解码的写入地址或读取地址相对应的字线信号路径。

附图说明

[0006]

当结合附图阅读时,从以下详细描述中可以最佳地理解本公开的各方面。应注意,根据工业中的标准实践,各种特征未按比例绘制。实际上,为了清楚讨论,各种特征的尺寸可被任意增大或减小。

[0007]

图1是根据一些实施例的存储器电路的示图。

[0008]

图2a和图2b是根据一些实施例的存储器电路操作参数的曲线图。

[0009]

图3a和图3b是根据一些实施例的控制电路的示图。

[0010]

图4a和图4b是根据一些实施例的存储器电路操作参数的曲线图。

[0011]

图5是根据一些实施例的信号生成电路的示图。

[0012]

图6是根据一些实施例的信号生成电路的示图。

[0013]

图7a和图7b是根据一些实施例的存储器电路操作参数的曲线图。

[0014]

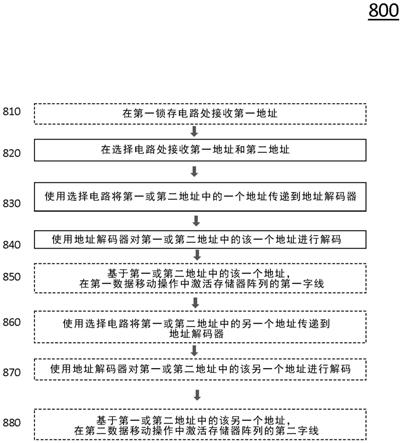

图8是根据一些实施例的操作存储器电路的方法的流程图。

具体实施方式

[0015]

以下公开内容提供了用于实现所提供主题的不同特征的许多不同实施例或示例。以下描述部件、值、操作、材料、布置等的具体示例以简化本公开。当然,这些仅仅是示例,而非意在进行限制。其他部件、值、操作、材料、布置等被预计到。此外,在以下描述中,在第二特征上方或者上形成第一特征可以包括第一特征和第二特征以直接接触的方式形成的实施例,并且也可以包括在第一特征和第二特征之间可以形成额外的特征,从而使得第一特征和第二特征可以不直接接触的实施例。另外,本公开可以在各种示例中重复参考数字和/或字母。这种重复是为了简化和清楚的目的,并且本身并不指示所讨论的各种实施例和/或配置之间的关系。

[0016]

而且,为了便于描述,本文可以使用诸如“在

…

下方”、“在

…

下面”、“下”、“在

…

之上”、“上”之类的空间相对术语以描述如图所示的一个元件或特征与另一个(或另一些)元件或特征的关系。除了图中所示的方位外,空间相对术语旨在包括器件在使用或操作中的不同方位。装置可以以其他方式定向(旋转90度或在其他方位上),并且本文使用的空间相对描述符可以同样地作出相应的解释。

[0017]

在各种实施例中,电路包括单个解码器和选择电路,并且被配置为选择和解码对应于存储器阵列中的数据移动(例如,读取和写入)操作的两个地址中的一个。通过在数据移动操作期间使用单个解码器来激活控制线,与在存储器阵列数据移动操作中为两个地址中的每一个使用单独的解码器的方法相比,减小了面积需求。

[0018]

图1是根据一些实施例的存储器电路100的示图。存储器电路100(也称为电路100)包括锁存电路110、选择电路120、锁存电路130、预解码器140、解码器150、存储器阵列160、以及控制电路170。如下所述,控制电路170包括信号生成部分以及时钟缓冲部分,在一些实施例中,该信号生成部分也称为双泵生成器,并且被配置为生成各种时序信号,该时钟缓冲部分被配置为基于时序信号输出各种控制信号。

[0019]

如下所述,存储器电路100被配置为接收来自端口p1的地址rx、来自端口p2的地址wx、时钟信号clk、以及启用信号reb和web,并且响应于时钟信号clk和启用信号reb和web而选择并解码地址rx或wx中的一个,从而在相应的一个或多个字线信号路径wp[1]-wp[n]上生成n个字线信号wl[1]-wl[n]中的一个或多个。

[0020]

在一些实施例中,存储器阵列160是包括单端口存储器单元的静态随机存取存储器(sram)阵列,并且存储器电路100被配置为促进数据移入和移出由地址rx和wx标识的单端口存储器单元。在一些实施例中,存储器电路100被配置为促进数据移入和移出由地址rx和wx标识的列位置(也称为x位置)处的单端口存储器单元。在一些实施例中,地址rx和wx是从包括附加信息(例如,列标识符)的相应地址(未示出)导出的,并且地址rx和wx不包括附加信息。

[0021]

在一些实施例中,存储器阵列160包括包含单端口存储器单元的处理器寄存器的寄存器文件,并且存储器电路100被配置为控制伪双端口寄存器文件(2prf)操作中的数据移动。在伪2prf操作中,在一些实施例中,通过使用单个时钟信号而不是两个单独的时钟信

号,单端口存储器单元被用于执行双端口存储器单元的功能。单个时钟信号的时钟周期的前半部分用于基于在读取端口上接收的读取地址来控制读取操作,并且时钟周期的后半部分用于基于在写入端口上接收到的写入地址来控制写入操作。在一些实施例中,存储器电路100被包括在超高密度(uhd)伪2prf电路中。在一些实施例中,存储器电路100是集成电路(ic)。

[0022]

在图1中描绘的实施例中,存储器电路100包括通过字线信号路径wp[1]-wp[n]耦合到解码器150的存储器阵列160。在各种实施例中,存储器电路100包括字线信号路径wp[1]-wp[n]但不包括存储器阵列160,或者既不包括存储器阵列160也不包括字线信号路径wp[1]-wp[n]。

[0023]

锁存电路110耦合到端口p2、选择电路120、以及控制电路170;选择电路120耦合到端口p1、每个锁存电路110和130、以及控制电路170;锁存电路130耦合到选择电路120、预解码器140、以及控制电路170;预解码器140耦合到锁存电路130、解码器150、以及控制电路170;解码器150耦合到预解码器140和存储器阵列160。

[0024]

基于一个或多个直接信号连接和/或一个或多个间接信号连接(包括在两个或更多个的电路元件之间的一个或多个逻辑设备,例如反相器或逻辑门),则认为两个或更多个电路元件耦合。在一些实施例中,两个或更多个耦合的电路元件之间的信号通信能够被一个或多个逻辑设备修改,例如被反转或限制以条件。

[0025]

地址rx和wx中的每一个包括逻辑状态的组合,逻辑状态被配置为标识存储器阵列(例如,存储器阵列160)中对应于给定字的一个或多个物理位置。在一些实施例中,每个字对应于一行存储器阵列160,地址rx被配置为在读取操作中标识存储器阵列160中相应的行,并且地址wx被配置为在写入操作中标识存储器阵列160中相应的行。

[0026]

地址rx或wx包括在一些或全部存储器(例如,存储器阵列160)中对应于2

l

个字的l个逻辑状态。在一些实施例中,l是逻辑状态的数目,范围从对应于四个字的两个逻辑状态至对应于4096个字的12个逻辑状态。在一些实施例中,地址rx或wx包括l等于对应于16个字的四个逻辑状态。在一些实施例中,对应于地址rx和wx中的l个逻辑状态的2

l

字等于字线信号路径wp[1]-wp[n]的数目n。

[0027]

在图1中描绘的实施例中,端口p1和p2、锁存电路110和130、选择电路120、以及预解码器140中的每一个包括一个或多个电路径,这些电路被配置为传导与包括在地址rx和wx中的l个逻辑状态相对应的一个或多个信号。在一些实施例中,端口p1和p2、锁存电路110和130、选择电路120、以及预解码器140中的每一个包括等于l的多个电路径。

[0028]

在各种实施例中,锁存电路110或130中的至少一个是多个锁存电路(未示出)中的一个和/或选择电路120是多个选择电路(未示出)中的一个,该至少一个锁存电路和/或选择电路被配置为共同传导对应于包括在地址rx和wx中的l个逻辑状态的一个或多个信号。在一些实施例中,锁存电路110和130中的每一个包括单个电路径并且是l个锁存电路中的一个锁存电路,选择电路120包括单个电路径并且是l个选择电路中的一个选择电路,并且因此,电路100被配置为共同传导与包括在地址rx和wx中的l个逻辑状态相对应的一个或多个信号。

[0029]

锁存电路110是电子电路,该电子电路包括:输入111,其被配置为从端口p2接收地址wx;输入113,其被配置为从控制电路170接收时钟脉冲信号cktw;以及输出112,其被配置

为输出地址wx,响应于时钟脉冲信号cktw而被选择性地锁存。

[0030]

选择电路120是电子电路,该电子电路包括输入121,其被配置为从端口p1接收地址rx;输入123,其被配置为从锁存电路110的输出112接收地址wx;输入125,其被配置为从控制电路170接收选择信号psel;以及输出122,其被配置为响应于选择信号psel而输出地址rx或wx中的一个。由此,选择电路120被配置为将所选地址rx或wx传递到输出122。在一些实施例中,选择电路120包括多路复用器。

[0031]

锁存电路130是电子电路,该电子电路包括:输入131,其被配置为从选择电路120的输出122接收地址rx或wx中的一个;输入133,其被配置为从控制电路170接收时钟脉冲信号cktr;以及输出132,其被配置为输出所接收的地址rx或wx,响应于时钟脉冲信号cktr而被选择性地锁存。

[0032]

预解码器140是组合逻辑电路,该组合逻辑电路包括:输入141,其被配置为从锁存电路130的输出132接收地址rx或wx;输入143,其被配置为从控制电路170接收时钟脉冲信号ckp;以及输出142,其被配置为基于所接收的地址rx或wx输出部分解码的地址pd,响应于时钟脉冲信号ckp而被选择性地启动。

[0033]

解码器150是组合逻辑电路,该组合逻辑电路包括:输入151,其被配置为从预解码器140的输出142接收部分解码的地址pd;以及输出152,其被配置为基于部分解码的地址pd在一个或多个字线信号路径wp[1]-wp[n]上输出相应的一个或多个字线信号wl[1]-wl[n]。

[0034]

在图1中描绘的实施例中,预解码器140和解码器150是单独的电路。在一些实施例中,预解码器140和解码器150是单个组合逻辑电路,该单个组合逻辑电路被配置为基于来自锁存电路130的输出132的、在输入141上接收的地址rx或wx在一个或多个字线信号路径wp[1]-wp[n]上输出相应的一个或多个字线信号wl[1]-wl[n],响应于时钟脉冲信号ckp而被选择性地启用。

[0035]

在一些实施例中,存储器电路100不包括解码器150,预解码器140的输出142是存储器电路100的输出,并且预解码器140被配置为输出部分解码的地址pd来作为存储器电路100的一个或多个输出信号。

[0036]

存储器阵列160是以行和列布置的存储器单元阵列(未示出)。存储器阵列160的存储器单元包括电设备、机电设备、电磁设备、或被配置为存储由逻辑状态表示的位数据的其他设备。在一些实施例中,逻辑状态对应于存储在给定存储器单元中的电荷的电压电平。在一些实施例中,逻辑状态对应于给定存储器单元的部件的物理特性,例如,电阻或磁取向。

[0037]

在一些实施例中,存储器阵列160的存储器单元包括sram单元。在各种实施例中,sram单元包括五晶体管(5t)sram单元、六晶体管(6t)sram单元、八晶体管(8t)sram单元、九晶体管(9t)sram单元、或具有其他数目的sram单元晶体管。在一些实施例中,存储器阵列160的存储器单元包括动态随机存取存储器(dram)单元或能够存储位数据的其他存储器单元类型。

[0038]

存储器阵列160的给定行或列的一些或全部存储器单元被配置为响应于从一个或多个字线信号路径wp[1]-wp[n]接收的相应的一个或多个字线信号wl[1]-wl[n],在读取和写入操作中作为字而被同时激活。在一些实施例中,每个字对应于存储器阵列160中的一行存储器单元,并且字线信号路径wp[1]-wp[n]中的每一个耦合到对应于给定字的行中的存储器单元。

[0039]

地址rx和wx,时钟脉冲信号cktw、cktr、和ckp,选择信号psel,字线信号wl[1]-wl[n],以及由下面讨论的存储器电路100使用的其他信号被配置为具有对应于逻辑状态的一个或多个电压电平。高逻辑状态对应于等于或高于第一预定阈值的电压电平,且低逻辑状态对应于等于或低于第二预定阈值的电压电平。在各种实施例中,第一预定阈值对应于处于或接近存储器电路100的工作电压电平(例如,电压电平vdd或vddm)的电压电平,和/或第二预定阈值对应于处于或接近存储器电路100的参考电压电平(例如,电压电平vss或地电位)的电压电平。

[0040]

在各种实施例中,锁存电路110被配置为响应于时钟脉冲信号cktw具有高或低逻辑状态中的预定一个而锁存地址wx,选择电路120被配置为响应于选择信号psel具有高或低逻辑状态中的相应一个而将地址rx或wx中的给定一个传递至输出122,锁存电路130被配置为响应于时钟脉冲信号cktr具有高或低逻辑状态中的预定一个而锁存地址rx或wx。预解码器140被配置为响应于具有高逻辑状态或低逻辑状态中的预定一个的时钟脉冲信号而输出部分解码的地址pd。

[0041]

在各种实施例中,解码器150被配置为通过将具有高或低逻辑状态中的预定一个的一个或多个字线信号wl[1]-wl[n]输出来激活给定的一个或多个字线信号路径wp[1]-wp[n],并由此激活相应的字。在一些实施例中,将具有高或低逻辑状态中的预定一个的字线信号wl[1]-wl[n]中的给定一个输出也被称为激活字线信号wl[1]-wl[n]中的给定的一个,并且将具有高或低逻辑状态中的另一个的字线信号wl[1]-wl[n]中的给定的一个输出被称为去激活字线信号wl[1]-wl[n]中的给定的一个。

[0042]

控制电路170是电子电路,该电子电路被配置为接收时钟信号clk以及启用信号reb和web,并生成时钟脉冲信号cktw、cktr、和ckp,并基于时钟信号clk和启用信号reb和web来选择信号psel。控制电路170被配置为控制存储器电路100的操作参数,从而生成时钟脉冲信号cktw、cktr、和ckp以及如下面关于图2a和2b所讨论的具有时序关系的选择信号psel。在一些实施例中,控制电路170包括下面关于图3讨论的控制电路300。

[0043]

图2a是根据一些实施例的存储器电路100操作参数的曲线图。在图2a中描绘的非限制性示例中,信号clk、cktw、cktr、psel、和ckp包括在对应于存储器电路100操作在时间t1-t5处的高逻辑状态和低逻辑状态之间的转换,如下所述。图2a描绘了其中启用信号reb和web中的每一个具有与启用状态相对应的逻辑状态的情况,并且为了清楚起见未示出启用信号。

[0044]

在图2a中描绘的实施例中,锁存电路110和130中的每一个被配置为响应于相应的时钟脉冲信号转换到高逻辑状态,将所接收的地址锁存并将锁存的地址传递到相应的输出,直到相应的时钟脉冲信号转换为低逻辑状态,以及响应于相应的时钟脉冲信号具有低逻辑状态,将所接收的地址传递到相应的输出而不执行锁存操作。选择电路120被配置为响应于选择信号psel具有相应的低逻辑状态和高逻辑状态,将地址rx和wx中的每一个传递到输出122,并且预解码器140被配置为响应于时钟脉冲信号ckp具有高逻辑状态而选择性地输出部分解码的地址pd。

[0045]

在各种实施例中,存储器电路100被配置为基于具有与图2a中所描绘的那些不一样的一个或多个逻辑状态和/或转换的信号clk、cktw、cktr、psel、或ckp中的一个或多个来操作。

[0046]

时钟信号clk由存储器电路100外部的电路生成,并且包括具有预定周期t的一系列脉冲。脉冲的上升沿对应于从低逻辑状态到高逻辑状态的转换,并且脉冲的下降沿对应于从高逻辑状态到低逻辑状态的转换。

[0047]

在时间t1,控制电路170被配置为在选择信号psel具有低逻辑状态时,通过在每个时钟脉冲信号cktw、cktr、和ckp中生成上升沿来响应时钟信号clk的上升沿。

[0048]

基于时钟脉冲信号cktw的上升沿,锁存电路110锁存地址wx并将锁存地址wx传递到输出112。基于选择信号psel的低逻辑状态,选择电路120将地址rx传递到输出122。基于时钟脉冲信号cktr的上升沿,锁存电路130锁存地址rx并将锁存地址rx传递到输出122。基于时钟脉冲信号ckp的上升沿,预解码器140变至启用,从而基于锁存地址rx在输出142处生成部分解码的地址pd,并且解码器150激活字线信号wl[1]-wl[n]中对应于地址rx的字线信号,如下面关于图2b所讨论的那样。

[0049]

时间t1之后,在时间t2,控制电路170被配置为在选择信号psel中生成上升沿,同时时钟脉冲信号cktw、cktr、和ckp中的每一个保持在高逻辑状态。

[0050]

由于时钟脉冲信号cktw保持在高逻辑状态,因此锁存电路110继续将锁存地址wx传递到输出112。基于选择信号psel的上升沿,选择电路120将锁存地址wx传递到输出122。由于时钟脉冲信号cktr保持在高逻辑状态,锁存电路130继续将锁存地址rx传递到输出132。由于时钟脉冲信号ckp保持在高逻辑状态,预解码器140保持启用,从而继续基于锁存地址rx在输出142处生成部分解码的地址pd,使得解码器150继续激活字线信号wl[1]-wl[n]中对应于地址rx的字线信号。

[0051]

在时间t2之后,在时间t3,控制电路170被配置为在时钟脉冲信号cktr和ckp中的每一个中生成下降沿,同时使时钟脉冲信号cktw和选择信号psel中的每一个保持在高逻辑状态。

[0052]

由于时钟脉冲信号cktw保持在高逻辑状态,因此锁存电路110继续将锁存地址wx传递到输出112。因为选择信号psel保持在高逻辑状态,所以选择电路120继续将锁存地址wx传递到输出122。基于时钟脉冲信号cktr的下降沿,锁存电路130停止锁存地址rx并将锁存地址wx传递到输出122。基于时钟脉冲信号ckp的下降沿,预解码器140变为禁用,从而停止基于锁存地址rx在输出142处生成部分解码的地址pd,并且解码器150去激活字线信号wl[1]-wl[n]中对应于地址rx的字线信号。

[0053]

在时间t3之后,在时间t4,控制电路170被配置为在时钟脉冲信号ckp中生成上升沿,同时使时钟脉冲信号cktw和选择信号psel中的每一个保持在高逻辑状态并且使时钟脉冲信号cktr保持在低逻辑状态。

[0054]

由于时钟脉冲信号cktw保持在高逻辑状态,因此锁存电路110继续将锁存地址wx传递到输出112。由于选择信号psel保持在高逻辑状态,所以选择电路120继续将锁存地址wx传递到输出122。由于时钟脉冲信号cktr保持在低逻辑状态,所以锁存电路130继续将锁存地址wx传递到输出122。基于时钟脉冲信号ckp的上升沿,预解码器140变为启用,从而基于锁存地址wx在输出142处生成部分解码的地址pd,并且解码器150激活字线信号wl[1]-wl[n]中对应于地址wx的字线信号,如下面关于图2b所讨论的那样。

[0055]

在时间t4之后,在时间t5,控制电路170被配置为在时钟脉冲信号cktw和ckp以及选择信号psel中的每一个中生成下降沿,同时使时钟脉冲信号cktr保持在低逻辑状态。

[0056]

基于时钟脉冲信号cktw的下降沿,锁存电路110停止将锁存地址wx传递到输出112。基于选择信号psel的下降沿,选择电路120将地址rx传递到输出122。由于时钟脉冲信号cktr继续具有低逻辑状态,锁存电路130将地址rx传递到输出122。基于时钟脉冲信号ckp的下降沿,预解码器140变为禁用,从而停止基于锁存地址wx在输出142处生成部分解码的地址pd,解码器150去激活字线信号wl[1]-wl[n]中对应于地址wx的字线信号。

[0057]

从时间t1到t3的间隔对应于时钟脉冲信号cpk的脉冲pl1,在此期间,解码器150基于被传递到预解码器140的锁存地址rx来激活字线信号wl[1]-wl[n]中的一个。在一些实施例中,脉冲pl1对应于存储器阵列160中的读取操作。

[0058]

在图2a中描绘的实施例中,存储器电路100被配置为在脉冲pl1期间通过在先于时间t2生成选择信号psel的上升沿的时间t1处生成时钟脉冲信号cktw、cktr、和ckp中的每一个的上升沿而将锁存地址rx传递到预解码器140。在各种实施例中,存储器电路100被配置为在脉冲pl1期间通过生成具有与图2a中所描绘的时序不同的时序的时钟脉冲信号cktw、cktr、和ckp的上升沿而将锁存地址rx传递到预解码器140,这样的时序包括在时刻t2生成选择信号psel的上升沿之前使锁存地址rx传递到预解码器140。

[0059]

从时间t4到t5的间隔对应于时钟脉冲信号ckp的脉冲pl2,在此期间,解码器150基于被传递到预解码器140的锁存地址wx来激活字线信号wl[1]-wl[n]中的一个。在一些实施例中,脉冲pl2对应于存储器阵列160中的写入操作。

[0060]

在图2a中描绘的实施例中,存储器电路100被配置为在脉冲pl2期间通过先于时间t4生成脉冲pl2的上升沿在时间t1生成时钟脉冲信号cktw的上升沿和在时间t2生成选择信号psel的上升沿而将锁存地址wx传递到预解码器140。在各种实施例中,存储器电路100被配置为在脉冲pl2期间具有与图2a中所描绘的时序不同的时序的时钟脉冲信号cktw和选择信号psel的上升沿而将锁存地址wx传递到预解码器140,这样的时序包括在时刻t4生成时钟脉冲信号ckp的上升沿之前或同时使锁存地址wx传递到预解码器140。

[0061]

如上所述,图2a描绘了启用信号reb和web中的每一个具有与启用状态对应的逻辑状态的情况。在一些实施例中,存储器电路100被配置为通过在没有脉冲pl1的情况下生成时钟脉冲信号ckp来响应其中启用信号reb具有与禁用状态相对应的逻辑状态的情况和/或通过在没有脉冲pl2的情况下生成时钟脉冲信号ckp来响应启用信号web具有对应于禁用状态的逻辑状态的情况。

[0062]

如在图2a的非限制性示例中所描绘的那样,存储器电路100被配置为在小于时钟信号clk的周期t的从时间t1到t5的间隔内生成脉冲pl1和pl2。因此,存储器电路100能够在时钟信号clk的单个周期t期间在存储器阵列160中启用读取操作和写入操作。

[0063]

图2b是根据一些实施例的存储器电路100操作参数的曲线图。图2b描绘了响应于所接收地址rx和wx、时钟信号clk、以及启用信号reb和web而生成的字线信号wl[1]-wl[n]的非限制性示例。图2b的非限制性示例图示出了四个时钟信号周期ta、tb、tc、和td,并且包括具有与启用状态对应的低逻辑状态的启用信号reb和web中的每一个,以及具有对应于激活状态的高逻辑状态的字线信号wl[1]-wl[n]。地址nr是所接收地址rx的非限制性示例,地址nw是所接收地址wx的非限制性示例。

[0064]

在时钟信号周期ta的开始,启用信号reb具有对应于启用读取操作的低逻辑状态,并且启用信号web具有对应于启用写入操作的低逻辑状态。在时钟信号周期tb的开始,启用

信号reb具有对应于启用读取操作的低逻辑状态,并且启用信号web具有对应于禁用写入操作的高逻辑状态。在时钟信号周期tc的开始,启用信号reb具有对应于禁用读取操作的高逻辑状态,并且启用信号web具有对应于启用写入操作的低逻辑状态。在时钟信号周期td的开始,启用信号reb具有与禁用读取操作相对应的高逻辑状态,并且启用信号web具有与禁用写入操作相对应的高逻辑状态。

[0065]

因此,电路100在时钟信号周期ta期间生成的时钟脉冲信号ckp包括脉冲pl1和pl2中的每一个,在时钟信号周期tb期间生成的包括脉冲pl1而没有脉冲pl2,在时钟信号周期tc期间生成的包括脉冲pl2而没有脉冲pl1,以及在时钟信号周期td期间生成的既不包括脉冲pl1也不包括pl2。

[0066]

图2b描绘了针对两种情况的字线信号wl[1]-wl[n]的非限制性示例:第一种情况,其中单个字线信号wl[nr=nw]对应于与地址nw相同的地址nr;以及第二种情况,其中字线信号wl[nr]对应于地址nr,字线信号wl[nw]对应于与地址nr不同的地址nw。在各种实施例中,地址nr和nw中的每一个具有等于4的数目l,并且地址nr或nw中的一个或两个等于0000和/或1111。

[0067]

在第一种情况中,在时钟信号周期ta期间,解码器150生成包括响应于地址nr和脉冲pl1的激活读取状态以及响应于地址nw和脉冲pl2的激活写入状态的字线信号wl[nr=nw]。在时钟信号周期tb期间,解码器150生成包括响应于地址nr和脉冲pl1的激活读取状态但不包括激活写入状态的字线信号wl[nr=nw]。在时钟信号周期tc期间,解码器150生成不包括激活读取状态但包括响应于地址nw和脉冲pl2的激活写入状态的字线信号wl[nr=nw]。在时钟信号周期td期间,解码器150生成既不包括激活读取状态也不包括激活写入状态的字线信号wl[nr=nw]。

[0068]

在第二种情况中,在时钟信号周期ta期间,解码器150生成包括响应于地址nr和脉冲pl1的激活读取状态但不包括激活写入状态的字线信号wl[nr],并生成不包括激活读取状态但包括响应于地址nw和脉冲pl2的激活写入状态的字线信号wl[nw]。在时钟信号周期tb期间,解码器150生成包括响应于地址nr和脉冲pl1的激活读取状态但不包括激活写入状态的字线信号wl[nr],并生成不包括激活读取状态且不包括激活写入状态的字线信号wl[nw]。在时钟信号周期tc期间,解码器150生成不包括激活读取状态并且不包括激活写入状态的字线信号wl[nr],并且生成不包括激活读取状态但包括响应于地址nw和脉冲pl2的激活写入状态的字线信号wl[nw]。在时钟信号周期td期间,解码器150生成不包括激活读取状态并且不包括激活写入状态的字线信号wl[nr],并且生成不包括激活读取状态并且不包括激活写入状态的字线信号wl[nw]。

[0069]

通过上面讨论的配置,存储器电路100能够在单个时钟周期期间使用解码器150和选择电路120来选择和解码对应于存储器阵列160中的数据移动操作的两个地址中的一个。因此,与在单个时钟周期期间针对存储器阵列数据移动操作中的两个地址中的每一个使用单独的解码器的方法相比,降低了对存储器电路100面积方面的要求。

[0070]

通过减少用于激活存储器阵列中的给定字的数据线的数目来实现面积的显著减小。通过将解码器的数目从两个减少到一个,携带用于激活给定字的启用信号的数据线的数目类似地也从两个减少到一个。

[0071]

图3a和图3b是根据一些实施例的控制电路300的示图。控制电路300可用作上面关

于存储器电路100和图1-图2b讨论的控制电路170。

[0072]

图3a描绘了控制电路300的信号生成部分,该信号生成部分被配置为基于时钟信号clk和启用信号reb和web生成包括选择信号psel的各种信号。图3b描绘了控制电路300的时钟缓冲器部分,该时钟缓冲器部分被配置为基于各种信号生成时钟脉冲信号cktw、cktr、和ckp,如下所述。

[0073]

控制电路300的信号生成部分包括锁存电路310和320,信号生成电路330、340、和350,端口跟踪电路360和370,或门or1和与非门nand1。控制电路300的时钟缓冲器部分包括反相器inv1和与非门nand2和nand3。

[0074]

锁存电路310的输出耦合到信号生成电路330的输入和或门or1的输入。锁存电路320的输出耦合到信号生成电路350的输入和或门or1的输入。或门or1的输出耦合到信号生成电路340的输入。

[0075]

信号生成电路330的输出耦合到与非门nand1的输入,信号生成电路340的输出耦合到与非门nand1的另一输入,并且信号生成电路350的输出耦合到端口跟踪电路370的输入。与非门nand1的输出耦合到端口跟踪电路360的输入。

[0076]

端口跟踪电路360的输出耦合到信号生成电路330的输入和信号生成电路340的输入。端口跟踪电路370的输出耦合到信号生成电路350的输入。

[0077]

锁存电路310是电子电路,该电子电路被配置为接收启用信号reb和时钟信号clk,并且响应于时钟信号clk,锁存和输出启用信号reb到信号生成电路330和或门or1。

[0078]

锁存电路320是电子电路,该电子电路被配置为接收启用信号web和时钟信号clk,并且响应于时钟信号clk,锁存和输出启用信号web到信号生成电路350和或门or1。

[0079]

或门or1是逻辑门,被配置为接收锁存的启用信号reb和web,并且响应于锁存的启用信号reb和web,将启用信号rweb输出到信号生成电路340。

[0080]

信号生成电路330是电子电路,该电子电路被配置为接收时钟信号clk、所锁存启用信号reb、以及复位信号rsc1,并且响应于时钟信号clk、所锁存启用信号reb、以及复位信号rsc1,输出时钟脉冲信号ckpb1到与非门nand1和nand3以及反相器inv1。信号生成电路330被配置为生成包括下面关于图4a和图4b讨论的逻辑状态转换的时钟脉冲信号ckpb1。在一些实施例中,信号生成电路330是下面关于图5讨论的信号生成电路500。

[0081]

信号生成电路340是电子电路,该电子电路被配置为接收时钟信号clk、启用信号rweb、以及复位信号rsc1,并且响应于时钟信号clk、启用信号rweb、以及复位信号rsc1,将时钟脉冲信号ckpb1_trk输出到与非门nand1和nand2。信号生成电路340被配置为生成包括下面关于图4a和图4b讨论的逻辑状态转换的时钟脉冲信号ckpb1_trk。在一些实施例中,信号生成电路340是下面关于图5讨论的信号生成电路500。

[0082]

信号生成电路350是电子电路,该电子电路被配置为接收时钟脉冲信号ckp1_trk、锁存启用信号web、以及复位信号rsc2,并且响应于时钟脉冲信号ckp1_trk、锁存启用信号web、以及复位信号rsc2,将时钟脉冲信号ckpb2输出到端口跟踪电路370和与非门nand2和nand3,将复位信号rstckb输出到与非门nand2,并将上面关于图1和图2a讨论的选择信号psel输出。信号生成电路330被配置为生成包括下面关于图4a讨论的逻辑状态转换的时钟脉冲信号ckpb2、复位信号rstckb、以及选择信号psel。在一些实施例中,信号生成电路350是下面关于图6讨论的信号生成电路600。

[0083]

与非门nand1是逻辑门,该逻辑门被配置为接收时钟脉冲信号ckpb1和ckpb1_trk,并且响应于时钟脉冲信号ckpb1和ckpb1_trk,将时钟脉冲信号ckp1_trk输出到端口跟踪电路360。

[0084]

端口跟踪电路360是电子电路,该电子电路被配置为接收时钟脉冲信号ckp1_trk并且响应于跟踪电路(未示出)的时序而生成复位信号rsc1,该跟踪电路被配置为使用端口p1复制读取操作并且由时钟脉冲信号ckp1_trk来启动,从而生成包括在足够长的跟踪间隔之后的逻辑状态转换的复位信号rsc1,以确保在端口p1上完成读取操作。

[0085]

端口跟踪电路370是电子电路,该电子电路被配置为接收时钟脉冲信号ckpb2并且响应于跟踪电路(未示出)的时序而生成重置信号rsc2,该跟踪电路被配置为使用端口p2复制写入操作并由时钟脉冲信号ckpb2来启动,从而生成包括在足够长的跟踪间隔之后的逻辑状态转换的复位信号rsc2,以确保在端口p2上完成写入操作。

[0086]

反相器inv1是逻辑门,该逻辑门被配置为接收时钟脉冲信号ckpb1并输出反相时钟脉冲信号ckpb1来作为上面关于图1和图2a讨论并在下面关于图4b讨论的时钟脉冲信号cktr。

[0087]

与非门nand2是逻辑门,该逻辑门被配置为接收时钟脉冲信号ckpb1_trk和ckpb2以及复位信号rstckb,并且响应于时钟脉冲信号ckpb1_trk和ckpb2以及复位信号rstckb,输出上面关于图1和图2a讨论并在下面关于图4b讨论的时钟脉冲信号cktw。

[0088]

与非门nand3是逻辑门,该逻辑门被配置为接收时钟脉冲信号ckpb1和ckpb2,并且响应于时钟脉冲信号ckpb1和ckpb2,输出上面关于图1-图2b讨论并在下面关于图4b讨论的时钟脉冲信号ckp。

[0089]

图4a和图4b是根据一些实施例的存储器电路100和控制电路300的操作参数的曲线图。在图4a和图4b中描绘的非限制性示例中,信号clk、ckpb1、ckpb1_trk、ckp1_trk、rsc1、rstckb、ckpb2、rsc2、psel、ckp、cktr、以及cktw包括对应于控制电路300操作的高逻辑状态和低逻辑状态之间的转换t1-t24,如下所述。图4a和图4b描绘了启用信号reb、web、以及由此rweb具有对应于启用状态的逻辑状态并且为了清楚起见未被示出的情况。

[0090]

如图4a中所描绘的,转换t1是时钟信号clk的上升沿。响应于转换t1,信号生成电路330生成转换t2,即时钟脉冲信号ckpb1的下降沿,并且信号生成电路340生成转换t3,即时钟脉冲信号ckpb1_trk的下降沿。在图4a和图4b中描绘的情况中,其中信号生成电路330和340都被启用,同时生成转换t2和t3。响应于转换t2或t3中的任何一个,与非门nand1生成转换t4,即时钟脉冲信号ckp1_trk的上升沿。

[0091]

响应于转换t4,信号生成电路350生成转换t5,即复位信号rstckb的下降沿,并且响应于转换t5,生成转换t6,即选择信号psel的上升沿。响应于转换t4,并且在上面讨论的跟踪间隔之后,端口跟踪电路360生成转换t7,即复位信号rsc1的下降沿。

[0092]

响应于转换t7,信号生成电路330生成转换t8,即时钟脉冲信号ckpb1的上升沿,并且信号生成电路340生成转换t9,即时钟脉冲信号ckpb1_trk的上升沿。响应于转换t8和t9,与非门nand1生成转换t10,即时钟脉冲信号ckp1_trk的下降沿。

[0093]

响应于转换t10,信号生成电路350生成转换t11,即时钟脉冲信号cpkb2的下降沿。响应于转换t11,并且在上面讨论的跟踪间隔之后,端口跟踪电路370生成转换t12,即复位信号rsc2的下降沿。

[0094]

响应于转换t12,信号生成电路350生成转换t13,即复位信号rstckb的上升沿,以及转换t14,即时钟脉冲信号ckpb2的上升沿。

[0095]

响应于转换t14,端口跟踪电路370生成转换t15,即复位信号rsc2的上升沿,并且信号生成电路350生成转换t16,即选择信号psel的下降沿。

[0096]

如图4b所示,响应于转换t2和t8,即时钟脉冲信号ckpb1的相应下降沿和上升沿,与非门nand3生成转换t17和t18。转换t17和t18,即时钟脉冲信号ckp的脉冲pl1的相应上升沿和下降沿,由此对应于基于时钟脉冲信号ckpb1的脉冲pl1的脉冲宽度。

[0097]

响应于转换t11和t14,即时钟脉冲信号ckpb2的相应下降沿和上升沿,与非门nand3生成转换t19和t20。转换t19和t20,即时钟脉冲信号ckp的脉冲pl2的相应上升沿和下降沿,由此对应于基于时钟脉冲信号ckpb2的脉冲pl2的脉冲宽度。

[0098]

响应于转换t2和t8,即时钟脉冲信号ckpb1的相应下降沿和上升沿,反相器inv1生成转换t21和t22,即时钟脉冲信号cktr的相应上升沿和下降沿。

[0099]

响应于转换t3和t14,即时钟脉冲信号ckpb1_trk的相应下降沿和时钟脉冲信号ckpb2的上升沿,与非门nand2生成转换t23和t24,即时钟脉冲信号cktw的相应上升沿和下降沿。

[0100]

转换t17由与非门nand3响应于转换t2而生成,由此在转换t2之后单个门延迟,该单个门延迟为对应于逻辑门中的逻辑状态转换的时间间隔。转换t21由反相器inv1响应于转换t2而生成,由此在转换t2之后单个门延迟。转换t23由与非门nand2响应于转换t3并同时响应于转换t2而生成,由此在转换t2之后单个门延迟。

[0101]

通过使转换t17、t21、以及t23中的每一个(各个时钟脉冲信号ckp、cktr、以及cktw的上升沿)在转换t2之后单个门延迟,控制电路300被配置为在时间t1处或附近生成各个时钟脉冲信号ckp、cktr、以及cktw的上升沿,如上面关于图2a所讨论的那样。

[0102]

转换t4由与非门nand1响应于同时转换t2或t3中的任一个而生成,并由此在转换t2之后单个门延迟。转换t6由信号生成电路350响应于转换t4而生成,并由此在转换t4之后至少一个门延迟,并在转换t2之后至少两个门延迟。

[0103]

通过使转换t6(即选择信号psel的上升沿)在转换t2之后至少两个门延迟,控制电路300被配置为在时间t1之后的时间t2生成选择信号psel的上升沿,如上面关于图2a讨论的那样,由此确保了:在选择电路120基于选择信号psel的上升沿停止将地址rx传递到锁存电路130之前,锁存电路130便已基于时钟脉冲信号cktr的转换t21而具有锁存地址rx。

[0104]

由于转换t18(即时钟脉冲信号ckp的脉冲pl1的下降沿)以及转换t22(即时钟脉冲信号cktr的下降沿)在转换t7(即复位信号rsc1的下降沿)之后相应的跟踪间隔,控制电路300被配置为使得部分解码的地址pd基于锁存地址rx来从预解码器140输出,直到时间t3,如上面关于图2a所讨论的,从而确保在信号转换t18和t22之前完成相应的读取操作。

[0105]

通过使转换t16(即选择信号psel的下降沿)在转换t18和t22之后,控制电路300被配置为使选择电路120和锁存电路130在相应的读取操作完成之后将锁存地址wx传递到预解码器140。

[0106]

通过使转换t9(时钟脉冲信号ckp的脉冲pl2的上升沿)在转换t18(即时钟脉冲信号ckp的脉冲pl1的下降沿)之后,控制电路300被配置为提供从时间t3到时间t4的间隔,如上面关于图4所讨论的那样,从而确保了在后续写入操作开始之前将锁存地址wx传递到预

解码器140。

[0107]

通过将或门or1、信号生成电路330和340、以及与非门nand1包括在内,控制电路300被配置为响应于启用信号reb或web中的任一个具有对应于启用状态的逻辑状态,在时钟脉冲信号ckp1_trk中生成转换t10,从而使时钟脉冲信号ckp的脉冲pl2在时间t4开始,以使得写入操作具有相对于时钟信号clk的时序,而与执行读取操作无关。

[0108]

如上所述,在对应于写入操作的跟踪间隔已经过去之后,发生转换t12(即复位信号rsc2的下降沿)。转换t14(即时钟脉冲信号ckpb2的上升沿)在转换t12之后。由于转换t20(即时钟脉冲信号ckp的脉冲pl2的下降沿)和转换t24(即时钟脉冲信号cktw的下降沿)在转换t14之后,控制电路300被配置成使得部分解码的地址pd基于锁存地址wx来从预解码器140输出,直到时间t5,如上面关于图2a所讨论的那样,从而确保了在信号转换t20和t24之前完成相应的写入操作。

[0109]

如上所述,图4a和图4b描绘了启用信号reb和web中的每一个具有与启用状态对应的逻辑状态的情况。在启用信号reb具有与禁用状态对应的逻辑状态的情况下,信号生成电路330被配置为使得不生成时钟脉冲信号ckpb1中的转换t2和t8,并且控制电路300由此被配置为通过生成没有脉冲pl1的时钟脉冲信号ckp来响应禁用状态,如上面关于图2b所讨论的那样,使得在从时间t1到时间t3的间隔期间,预解码器140不输出部分解码的地址pd。

[0110]

在启用信号web具有与禁用状态对应的逻辑状态的情况下,信号生成电路350被配置为使得不生成时钟脉冲信号ckpb2中的转换t11和t14,并且控制电路300由此配置为通过生成没有脉冲pl2的时钟脉冲信号ckp来响应禁用状态,如上面关于图2b所讨论的那样,使得在从时间t4到时间t5的间隔期间,预解码器140不输出部分解码的地址pd。

[0111]

除了上面关于图3a和图3b中描绘的配置所讨论的时序特征之外,控制电路300能够基于具有上面关于存储器电路100和图1-图2b所讨论的时序控制和益处的时钟信号clk和启用信号reb和web生成时钟脉冲信号cktw、cktr、和ckp、以及选择信号psel。

[0112]

图5是根据一些实施例的信号生成电路500的示图。信号生成电路500可用作上面关于控制电路300和图3a-图4b所讨论的信号生成电路330或340中的一个或两个。

[0113]

信号生成电路500包括p型金属氧化物半导体(pmos)晶体管p1-p7、n型金属氧化物半导体(nmos)晶体管n1-n7、以及逻辑门反相器inv2-inv4和或非门nor1。

[0114]

晶体管p1、n1、以及n2串联耦合在电源节点vdd和参考节点vss之间。晶体管p1的源极端子耦合到电源节点vdd,晶体管p1的漏极端子耦合到晶体管n1的漏极端子,晶体管n1的源极端子耦合到晶体管n2的漏极端子,并且晶体管n2的源极端子耦合到参考节点vss。

[0115]

晶体管p2和p3彼此串联耦合并与晶体管p1并联。晶体管p2的源极端子耦合到电源节点vdd,晶体管p2的漏极端子耦合到晶体管p3的源极端子,晶体管p3的漏极端子耦合到晶体管p1和n1的漏极端子。

[0116]

晶体管n3与晶体管n2并联耦合。晶体管n3的漏极端子耦合到晶体管n2的漏极端子,晶体管n3的源极端子耦合到参考节点vss。

[0117]

晶体管p4、p5、n4、以及n5串联耦合在电源节点vdd和参考节点vss之间。晶体管p4的源极端子耦合到电源节点vdd,晶体管p4的漏极端子耦合到晶体管p5的源极端子,晶体管p5的漏极端子耦合到晶体管n4的漏极端子,晶体管n4的源极端子耦合到晶体管n5的漏极端子,并且晶体管n5的源极端子耦合到参考节点vss。

[0118]

晶体管p6、p7、n6、以及n7串联耦合在电源节点vdd和参考节点vss之间。晶体管p6的源极端子耦合到电源节点vdd,晶体管p6的漏极端子耦合到晶体管p7的源极端子,晶体管p7的漏极端子耦合到晶体管n6的漏极端子,晶体管n6的源极端子耦合到晶体管n7的漏极端子,并且晶体管n7的源极端子耦合到参考节点vss。

[0119]

晶体管p4和p6的漏极端子与晶体管p5和p7的源极端子彼此耦合,晶体管p5和n7的栅极被配置为接收复位信号rsc1,如上面关于控制电路300和图3a-图4b所讨论的那样,并且晶体管p6和n4的栅极被配置为接收时钟信号clk。

[0120]

晶体管p5、p7、n4、以及n6的漏极端子彼此耦合并耦合到输出out1,并且由此被配置为输出上面关于控制电路300和图3a-图4b讨论的时钟脉冲信号ckpb1或ckpb1_trk中的一个。

[0121]

反相器inv2耦合到晶体管p2和n2的栅极,并且由此被配置为接收时钟信号clk并将反相时钟信号clk作为时钟信号clkb输出到晶体管p2和n2的栅极。

[0122]

反相器inv3耦合在反相器inv4与晶体管p1和n1的栅极之间,并且由此被配置为将信号ckp1b输出到晶体管p1和n1的栅极。

[0123]

反相器inv4耦合在输出out1和反相器inv3以及晶体管p7和n6的栅极之间,并且由此被配置为将反相时钟脉冲信号ckpb1或ckpb1_trk输出到反相器inv3及晶体管p7和n6的栅极。

[0124]

或非门nor1耦合到晶体管p1、p3、以及n1的漏极以及晶体管p3、p4、n3、以及n5的栅极,并且由此被配置为接收信号ceb,其是上面关于存储器电路100、控制电路300、以及图1-图4b讨论的锁存启用信号reb或rweb中的一个的补充,并将信号clk_en输出到晶体管p3、p4、n3、以及n5的栅极。

[0125]

在操作中,信号生成电路500的初始状态包括具有低逻辑状态的时钟信号clk、具有与信号生成电路500的激活对应的低逻辑状态的信号ceb、具有高逻辑状态的复位信号rsc1、以及具有高逻辑状态的时钟脉冲信号ckpb1或ckpb1_trk。

[0126]

响应于时钟信号clk具有低逻辑状态,反相器inv2将具有高逻辑状态的信号clkb输出,从而关断晶体管p2并导通晶体管n2并将晶体管p1和n1配置为反相器。

[0127]

具有高逻辑状态的复位信号rsc1使晶体管p5关断,并且具有低逻辑状态的时钟信号clk使晶体管n4关断,从而使输出out1与晶体管p4和n5去耦合。

[0128]

具有低逻辑状态的时钟信号clk导通晶体管p6,并且具有高逻辑状态的复位信号rsc1导通晶体管n7,从而将晶体管p7和n6配置为与反相器inv4交叉耦合的反相器。

[0129]

响应于信号ceb具有低逻辑状态,或非门nor1响应于晶体管p1、p3、以及n1的漏极的逻辑状态来输出信号clk_en。

[0130]

响应于时钟脉冲信号ckpb1或ckpb1_trk具有高逻辑状态,反相器inv4输出低逻辑状态,并且反相器inv3将具有高逻辑状态的信号ckp1b输出,从而关断晶体管p1并导通晶体管n1。晶体管p1、p3、以及n1的漏极具有低逻辑状态,并且或非门nor1将具有高逻辑状态的信号clk_en输出,从而关断晶体管p3和p4并导通晶体管n3和n5。

[0131]

响应于上面关于控制电路300和图3a-4b所讨论的时钟信号clk的转换t1,具有高逻辑状态的时钟信号clk使晶体管p6关断并导通晶体管n4,从而使输出out1与电源节点vdd去耦合,通过晶体管n4和n5将输出out1耦合到参考节点vss,并使生成时钟脉冲信号ckpb1

或ckpb1_trk具有低逻辑状态。时钟脉冲信号ckpb1或ckpb1_trk从高逻辑状态变为低逻辑状态对应于上面关于控制电路300和图3a-图4b所讨论的相应的转换t2或t3。

[0132]

响应于时钟信号clk具有高逻辑状态,反相器inv2将具有低逻辑状态的信号clkb输出,从而导通晶体管p2并关断晶体管n2。

[0133]

响应于时钟脉冲信号ckpb1或ckpb1_trk具有低逻辑状态,反相器inv4输出高逻辑状态,并且反相器inv3将具有低逻辑状态的信号ckp1b输出,从而导通晶体管p1并关断晶体管n1。晶体管p1、p3、以及n1的漏极具有高逻辑状态,并且或非门nor1将具有低逻辑状态的信号clk_en输出,从而导通晶体管p3和p4并关断晶体管n3和n5。

[0134]

由于反相器inv3、晶体管p1和n1、以及或非门nor1引入的门延迟,晶体管n5在晶体管n7导通之后关断,并且输出out1通过晶体管n6和n7耦合到参考节点vss。

[0135]

响应于上面关于控制电路300和图3a-图4b所讨论的复位信号rsc1的转换t7,具有低逻辑状态的复位信号rsc1导通晶体管p5并使晶体管n7关断,从而使输出out1与参考节点vss去耦合,通过晶体管p4和p5将输出out1耦合到电源节点vdd,并使生成时钟脉冲信号ckpb1或ckpb1_trk具有高逻辑状态。从低逻辑状态变为高逻辑状态的时钟脉冲信号ckpb1或ckpb1_trk对应于上面关于控制电路300和图3a-图4b所讨论的相应转换t8或t9。

[0136]

通过图5中描绘并且在上面讨论的配置,信号生成电路500能够响应于具有上面关于存储器电路100、控制电路300、以及图1-图4b讨论的时序控制和益处的时钟信号clk、相应的启用信号reb或rweb、以及复位信号rsc1生成时钟脉冲信号ckpb1或ckpb1_trk中的每一个。

[0137]

图6是根据一些实施例的信号生成电路600的示图。信号生成电路600可用作上面关于控制电路300和图3a-图4b所讨论的信号生成电路350。

[0138]

信号生成电路600包括逻辑门与非门nand4-nand8、反相器inv5-inv7、以及或非门nor2和nor3、延迟电路610、以及字跟踪电路620和630。

[0139]

与非门nand4包括被配置为接收时钟脉冲信号ckp1_trk、启用信号web、以及复位信号rsc2的输入,以及耦合到与非门nand5的输入的输出。

[0140]

与非门nand5包括耦合到与非门nand6的输出的输入和耦合到与非门nand6的输入和反相器inv5的输入的输出。与非门nand6包括被配置为接收复位信号rsc2的输入。

[0141]

反相器inv5包括耦合到或非门nor2的输入和与非门nand8的输入的输出,并且由此被配置为输出复位信号rstckb。或非门nor2包括被配置为接收时钟脉冲信号ckp1_trk的输入,以及耦合到延迟电路610和与非门nand7的输入的输出,并且由此被配置为输出信号trk_en。

[0142]

反相器inv6包括耦合到延迟电路610的输入和耦合到字跟踪电路620的输出。反相器inv7包括耦合到延迟电路610的输入和耦合到字跟踪电路630的输出。或非门nor3包括耦合到的字跟踪电路620和630中的每一个,以及耦合到与非门nand7的输入的输出,并且由此被配置为将信号ckp2_pre输出到与非门nand7。

[0143]

与非门nand7包括耦合到与非门nand8的输入并且被配置为输出上面关于控制电路300和图3a-图4b所讨论的时钟脉冲信号ckpb2的输出。与非门nand8被配置为输出上面关于存储器电路100、控制电路300、以及图1-图4b所讨论的选择信号psel。

[0144]

延迟电路610是可配置电子电路,该可配置电子电路被配置为将从或非门nor2输

出的信号trk_en延迟由信号ptsel[1:0]确定的间隔,并将延迟信号trk_en输出。在图6中描绘的实施例中,延迟电路610被配置为接收具有四个逻辑状态组合中的一个的信号ptsel[1:0],并且将具有等于零、两个、四个、或六个门延迟的相应延迟的信号trk_en输出。在各种实施例中,延迟电路610被配置为接收具有少于或多于四个逻辑状态组合的信号ptsel[1:0],并且将具有等于一组除零、两个、四个、或六个门延迟之外的门延迟的相应延迟的信号trk_en输出。

[0145]

在各种实施例中,信号ptsel[1:0]包括对应于由跳线、引脚、或其他合适的导电元件配置的电压电平或短路和开路的逻辑状态。

[0146]

在操作中,延迟电路610响应于信号ptsel[1:0]而引入的可配置延迟包括在时钟脉冲信号ckpb2和选择信号psel的时序中,如下所述。因此,时钟脉冲信号ckpb2和选择信号psel的时序包括包含基于延迟电路610的配置的预定延迟分量的总延迟。由于预定延迟分量是基于信号ptsel[1:0]的,所以延迟电路610使得能够基于其中正在使用信号生成电路600的应用的用户输入反映时序要求来调整时序控制。

[0147]

字跟踪电路620和630中的每一个是电子电路,该电子电路被配置为接收由延迟电路610延迟并由相应的反相器inv6或inv7反转的信号trk_en,并且响应于配置为使用端口p2复制写入操作并由延迟和反转信号trk_en启动的跟踪电路(未示出)的时序生成输出信号。因此,字跟踪电路620和630中的每一个被配置为生成包括在足够长的跟踪间隔之后的逻辑状态转换的输出信号,以确保在端口p2上完成写入操作。

[0148]

字跟踪电路620和630包括跟踪电路,该跟踪电路被配置为跟踪写入操作的各个方面,使得由跟踪电路620和630生成的输出信号包括单独的时序信息。在一些实施例中,字跟踪电路620包括跟踪电路,该跟踪电路被配置为基于存储器阵列(例如,上面关于存储器电路100和图1-图2b所讨论的存储器阵列160)的列内的字线的深度来跟踪时序。在一些实施例中,字跟踪电路630包括跟踪电路,该跟踪电路被配置为基于存储器阵列(例如,上面关于存储器电路100和图1-图2b所讨论的存储器阵列160)的列的宽度来跟踪时序。

[0149]

在操作中,信号生成电路600的初始状态包括:具有低逻辑状态的时钟脉冲信号ckp1_trk、具有对应于信号生成电路600的激活的高逻辑状态的启用信号web、具有高逻辑状态的复位信号rsc2,并且输出低逻辑状态的与非门nand5被锁存到输出高逻辑状态的与非门nand6。

[0150]

响应于时钟脉冲信号ckp1_trk具有低逻辑状态,与非门nand4将高逻辑状态输出到与非门nand5。响应于与非门nand 5具有低逻辑状态,反相器inv5将具有高逻辑状态的复位信号rstckb输出。

[0151]

响应于时钟脉冲信号ckp1_trk具有低逻辑状态并且复位信号rstckb具有高逻辑状态,或非门nor2将具有低逻辑状态的信号trk_en输出。响应于信号trk_en具有低逻辑状态,延迟电路610将低逻辑状态输出到反相器inv6和inv7中的每一个,反相器inv6和inv7中的每一个将高逻辑状态输出到对应的字跟踪电路620或630,字跟踪电路620和630中的每一个将高逻辑状态输出到或非门nor3,并且或非门nor3将具有低逻辑状态的信号ckp2_pre输出。

[0152]

响应于信号ckp2_pre具有高逻辑状态并且信号trk_en具有低逻辑状态,与非门nand7将具有高逻辑状态的时钟脉冲信号ckpb2输出。

[0153]

响应于时钟脉冲信号ckpb2具有高逻辑状态并且复位信号rstckb具有高逻辑状态,与非门nand8将具有低逻辑状态的选择信号psel输出。

[0154]

作为时钟脉冲信号ckp1_trk的转换t4(如上面关于控制电路300和图3a-图4b所讨论的那样)的结果,时钟脉冲信号ckp1_trk具有高逻辑状态。响应于时钟脉冲信号ckp1_trk具有高逻辑状态,与非门nand4将低逻辑状态输出,与非门nand5将高逻辑状态输出,并且反相器inv5将具有低逻辑状态的复位信号rstckb输出。复位信号rstckb从高逻辑状态变为低逻辑状态对应于上面关于控制电路300和图3a-图4b所讨论的转换t5。

[0155]

响应于时钟脉冲信号ckp1_trk具有高逻辑状态和复位信号rstckb具有低逻辑状态,或非门nor2继续输出具有低逻辑状态的信号trk_en,或非门nor3继续输出具有高逻辑状态的信号ckp2_pre,并且与非门nand7继续输出具有高逻辑状态的时钟脉冲信号ckpb2。

[0156]

响应于时钟脉冲信号ckpb2具有高逻辑状态和复位信号rstckb具有低逻辑状态,与非门nand8将具有高逻辑状态的选择信号psel输出。选择信号psel从低逻辑状态变为高逻辑状态对应于上面关于控制电路300和图3a-图4b所讨论的转换t6。

[0157]

作为时钟脉冲信号ckp1_trk的转换t10(如上面关于控制电路300和图3a-图4b所讨论的那样)的结果,时钟脉冲信号ckp1_trk具有低逻辑状态。响应于时钟脉冲信号ckp1_trk具有低逻辑状态,与非门nand4输出高逻辑状态,并且与非门nand5响应于与非门nand6输出低逻辑状态而继续输出高逻辑状态。因此,反相器inv5继续输出具有低逻辑状态的复位信号rstckb。

[0158]

响应于时钟脉冲信号ckp1_trk和复位信号rstckb中的每一个具有低逻辑状态,或非门nor2将具有高逻辑状态的信号trk_en输出。响应于信号trk_en具有高逻辑状态,延迟电路610最初继续输出低逻辑状态,或非门nor3继续输出具有低逻辑状态的信号ckp2_pre,并且与非门nand7继续输出具有高逻辑状态的时钟脉冲信号ckpb2。

[0159]

在上面讨论的可配置延迟之后,延迟电路610将高逻辑状态输出到反相器inv6和inv7中的每一个,并且反相器inv6和inv7中的每一个将低逻辑状态输出到对应的字跟踪电路620和630。

[0160]

基于上面讨论的时序,字跟踪电路620和630中的每一个通过在相应的跟踪延迟之后输出低逻辑状态来响应所接收的低逻辑状态。在字跟踪电路620和630都输出低逻辑状态之前,或非门nor3继续输出具有低逻辑状态的信号ckp2_pre。响应于字跟踪电路620和630两者都输出低逻辑状态,或非门nor3将具有高逻辑状态的信号ckp2_pre输出。

[0161]

响应于输出信号ckp2_pre和信号trk_en具有高逻辑状态,与非门nand7将具有低逻辑状态的时钟脉冲信号ckpb2输出。时钟脉冲信号ckpb2从高逻辑状态变为低逻辑状态对应于上面关于控制电路300和图3a-图4b所讨论的转换t11。

[0162]

响应于时钟脉冲信号ckpb2和复位信号rstckb中的每一个具有低逻辑状态,与非门nand8继续输出具有高逻辑状态的选择信号psel。

[0163]

响应于复位信号rsc2的转换t12(如上面关于控制电路300和图3a-图4b所讨论的那样),复位信号rsc2具有低逻辑状态。响应于复位信号rsc2具有低逻辑状态,与非门nand6输出高逻辑状态,与非门nand5输出低逻辑状态,并且反相器inv5将具有高逻辑状态的复位信号rstckb输出。复位信号rstckb从低逻辑状态变为高逻辑状态对应于上面关于控制电路300和图3a-图4b所讨论的转换t13。

[0164]

响应于时钟脉冲信号ckp1_trk具有低逻辑状态并且复位信号rstckb具有高逻辑状态,或非门nor2将具有低逻辑状态的信号trk_en输出。响应于信号trk_en具有低逻辑状态并且信号ckp2_pre具有低逻辑状态或高逻辑状态,与非门nand7将具有高逻辑状态的时钟脉冲信号ckpb2输出。时钟脉冲信号ckpb2从低逻辑状态变为高逻辑状态对应于上面关于控制电路300和图3a-图4b所讨论的转换t14。

[0165]

响应于时钟脉冲信号ckpb2和复位信号rstckb中的每一个具有高逻辑状态,与非门nand8将具有低逻辑状态的选择信号psel输出。选择信号psel从高逻辑状态变为低逻辑状态对应于上面关于控制电路300和图3a-图4b所讨论的转换t16。

[0166]

通过图6中描绘的配置并且如上所述,信号生成电路600能够响应于具有上面关于存储器电路100、控制电路300、以及图1-图4b所讨论的时序控制和益处的时钟脉冲信号ckp1_trk、启用信号web、以及复位信号rsc2生成时钟脉冲信号ckpb2、复位信号rstckb、以及选择信号psel。

[0167]

此外,通过图6中描绘的配置并且如上所述,信号生成电路600能够生成包括自时序的选择信号psel,该自时序确保读取和写入地址被锁存而不需要额外的时序电路。

[0168]

图7a和图7b是根据一些实施例的存储器电路100和控制电路300操作参数的曲线图。在图7a和7b中描绘的实施例中,存储器电路100被配置为在写入操作期间生成具有高逻辑状态的时钟脉冲信号cktr,从而使锁存电路130在写入操作期间锁存地址wx。存储器电路100被配置为生成具有高逻辑状态的时钟脉冲信号cktw,从而使得锁存电路110还在图7a所示的实施例中的每次写入操作中以及图7b所示的实施例中的每个写入操作的一部分中锁存地址wx。

[0169]

图7a和图7b中描绘的非限制性示例中的每一个都包括包含转换t2、t3、t6、t8、t11、t14、以及t16-t24(每个都在上面关于图1-图4b进行了讨论)的信号ckpb1_trk、ckpb1、ckpb2、rstckb、ckp、cktr、cktw、和psel,以及包含下面讨论的转换t25和t26的时钟脉冲信号cktr。图7a和图7b中的每一个描绘了其中启用信号reb和web中的每一个具有对应于启用状态的逻辑状态并且为了清楚起见未被示出的情况。

[0170]

在图7a和图7b中描绘的实施例中,控制电路300被配置为响应于转换t11生成转换t25,即时钟脉冲信号cktr的上升沿,并且响应于转换t14生成转换t26,即时钟脉冲信号cktr的下降沿。

[0171]

在操作中,转换25使锁存电路130锁存从选择电路120接收的地址wx,并基于选择信号psel的高逻辑状态将锁存地址wx输出到预解码器140。因为锁存电路130被配置为只要时钟脉冲信号cktr具有高逻辑状态就输出锁存地址wx,所以时钟脉冲信号cktw和选择信号psel在转换25和26之间的逻辑状态不影响锁存电路130在时钟脉冲信号ckp的脉冲pl2期间将锁存地址wx输出到预解码器140。

[0172]

与图3a-图4b中描绘的实施例相反,在图7a和图7b中描绘的每个实施例中,控制电路300被配置为响应于时钟脉冲信号ckpb2中的转换t11并且在至少一个门延迟之后,在选择信号psel中生成转换t16。控制电路300由此被配置为在锁存电路130基于转换t25具有锁存地址wx之后并且在锁存电路130基于转换t26不再输出锁存地址wx之前生成转换t16。

[0173]

与图3a-图4b以及图7a中描绘的实施例相反,在图7b中描绘的实施例中,控制电路300被配置为响应于时钟脉冲信号ckpb2中的转换t11并且在至少一个门延迟之后,在时钟

脉冲信号cktw中生成t24。控制电路300由此被配置为在锁存电路130基于转换t25具有锁存地址wx之后并且在锁存电路130基于转换t26不再输出锁存地址wx之前生成转换t24。

[0174]

在图7a和图7b中所描绘的实施例中,控制电路300由此被配置为使得锁存电路130在时钟脉冲信号ckp的脉冲pl2期间将锁存地址wx输出到预解码器140。在一些实施例中,锁存电路130在时钟脉冲信号ckp的脉冲pl2期间将锁存地址wx输出到预解码器140对应于存储器阵列(例如,上面关于存储器电路100和图1-图2b所讨论的存储器阵列160)中的写入操作。

[0175]

通过上面关于图7a和图7b所讨论的配置,控制电路300能够基于具有上面关于存储器电路100和图1-图2b所讨论的优点的时钟信号clk和启用信号reb和web生成时钟脉冲信号cktw、cktr、以及ckp、以及选择信号psel。

[0176]

图8是根据一个或多个实施例的操作存储器电路的方法800的流程图。方法800可与存储器电路(例如,上面关于图1-图2b所讨论的存储器电路100)一起使用。

[0177]

图8中描绘的操作方法800的序列仅是出于阐述的目的的。操作方法800能够以不同于图8中所描绘的顺序执行。在一些实施例中,还可以在图8中描绘的那些操作之前、之间、期间、和/或之后执行除了图8中描绘的操作之外的操作。

[0178]

在一些实施例中,方法800的一些或全部操作是在处理器中的寄存器数据移动操作(例如,如上所述的伪2prf操作)的子集。

[0179]

在操作810处,在一些实施例中,在存储器电路的第一锁存电路处接收第一地址。第一地址包括被配置为标识存储器阵列中的一个或多个位置的信息。在一些实施例中,一个或多个位置对应于数据字。在一些实施例中,一个或多个位置对应于存储器阵列的列内的位置(例如,x位置)。

[0180]

在一些实施例中,存储器阵列包括包含多个处理器寄存器的寄存器文件,并且第一地址对应于处理器寄存器。在各种实施例中,存储器阵列包括在存储器电路中或独立于存储器电路。

[0181]

在一些实施例中,接收第一地址包括从耦合到存储器电路的第一数据端口接收第一地址。在一些实施例中,接收第一地址包括接收第一地址来作为在存储器阵列中执行数据移动操作的一部分。在一些实施例中,接收第一地址包括接收写入地址来作为在存储器阵列中执行写入操作的一部分。

[0182]

在一些实施例中,在第一锁存电路处接收第一地址包括在第一锁存电路处接收控制信号并通过锁存第一地址来响应该控制信号。在一些实施例中,接收控制信号包括使用控制电路生成控制信号。在一些实施例中,生成控制信号包括响应于时钟信号和一个或多个启用信号而生成控制信号。

[0183]

在一些实施例中,第一地址是地址wx,和/或第一锁存电路是锁存电路110,和/或存储器阵列是存储器阵列160,每个都如在上面关于存储器电路100和图1-图2b所讨论的那样。在一些实施例中,生成和/或接收控制信号包括生成和/或接收上面关于存储器电路100、控制电路170和300、以及图1-图4b和图7a及图7b所讨论的时钟脉冲信号cktw。

[0184]

在操作820处,在选择电路处接收第一地址和第二地址。第二地址是与上面讨论的第一地址相同类型的地址。在一些实施例中,接收第一和第二地址包括从锁存电路(例如,第一锁存电路)接收第一或第二地址中的一个或两个。

[0185]

在一些实施例中,接收第二地址包括从耦合到存储器电路的第二数据端口接收第二地址。在一些实施例中,接收第二地址包括接收第一地址来作为在存储器阵列中执行数据移动操作的一部分。在一些实施例中,接收第二地址包括接收读取地址来作为在存储器阵列中执行读取操作的一部分。

[0186]

在一些实施例中,接收第一和第二地址包括在多路复用器处接收第一和第二地址。在一些实施例中,接收第一和第二地址包括在选择电路120处接收上面关于存储器电路100和图1-图2b所讨论的地址rx和wx。

[0187]

在操作830处,选择电路用于将第一或第二地址中的一个传递到地址解码器。在一些实施例中,使用选择电路将第一或第二地址中的一个传递到地址解码器包括使用多路复用器。

[0188]

在一些实施例中,使用选择电路将第一或第二地址中的一个传递到地址解码器包括在选择电路处接收控制信号并通过选择第一或第二地址中的一个来响应控制信号。在一些实施例中,接收控制信号包括使用控制电路生成控制信号。在一些实施例中,生成控制信号包括响应于时钟信号和一个或多个启用信号而生成控制信号。

[0189]

在一些实施例中,第一和第二地址是地址wx和rx,和/或选择电路是选择电路120,和/或地址解码器是解码器150,每个都如上面关于存储器电路100和图1-图2b所讨论。在一些实施例中,生成和/或接收控制信号包括生成和/或接收上面关于存储器电路100、控制电路170和300、信号生成电路600、以及图1-图4b和图6-图7b所讨论的选择信号psel。

[0190]

在一些实施例中,使用选择电路将第一或第二地址中的一个传递到地址解码器包括在锁存电路(例如,第二锁存电路)处从选择电路接收第一或第二地址中的一个。在一些实施例中,使用选择电路将第一或第二地址中的一个传递到地址解码器包括在上面关于存储器电路100和图1-图2b所讨论的锁存电路130处接收第一或第二地址中的一个。

[0191]

在一些实施例中,在第二锁存电路处接收第一或第二地址中的一个包括在第二锁存电路处接收控制信号并通过锁存第一或第二地址中的一个来响应控制信号。在一些实施例中,接收控制信号包括使用控制电路生成控制信号。在一些实施例中,生成控制信号包括响应于时钟信号和一个或多个启用信号而生成控制信号。

[0192]

在一些实施例中,第一或第二地址中的一个是地址wx或rx中的一个和/或第二锁存电路是锁存电路130,每个都如上面关于存储器电路100和图1-图2b所讨论。在一些实施例中,生成和/或接收控制信号包括生成和/或接收上面关于存储器电路100、控制电路170和300、以及图1-图4b及图7a和图7b所讨论的时钟脉冲信号cktr。

[0193]

在一些实施例中,使用选择电路将第一或第二地址中的一个传递到地址解码器包括在预解码器处从选择电路接收第一或第二地址中的一个。在一些实施例中,使用选择电路将第一或第二地址中的一个传递到地址解码器包括在上面关于存储器电路100和图1-图2b所讨论的预解码器140处接收第一或第二地址中的一个。

[0194]

在操作840处,地址解码器用于解码由选择电路传递的第一或第二地址中的一个。在一些实施例中,使用地址解码器包括使用预解码器,例如,上面关于存储器电路100和图1-图2b所讨论的预解码器140。

[0195]

在一些实施例中,使用地址解码器来解码第一或第二地址中的一个包括在预解码器和/或地址解码器处接收控制信号并通过预解码和/或解码第一或第二地址中的一个来

响应该控制信号。在一些实施例中,接收控制信号包括使用控制电路生成控制信号。在一些实施例中,生成控制信号包括响应于时钟信号和一个或多个启用信号生成控制信号。

[0196]

在一些实施例中,第一或第二地址中的一个是地址wx或rx中的一个,和/或解码器是解码器150,每个都如上面关于存储器电路100和图1-图2b所讨论。在一些实施例中,生成和/或接收控制信号包括生成和/或接收上面关于存储器电路100、控制电路170和300、以及图1-图4b及图7a和图7b所讨论的时钟脉冲信号ckp。

[0197]

在操作850处,在一些实施例中,基于第一或第二地址中的一个,在第一数据移动操作中激活存储器阵列的第一字线。激活第一字线包括使用解码器,例如上面关于存储器电路100和图1-图2b所讨论的解码器150。在一些实施例中,激活第一字线包括在解码器和第一字线之间使用一个或多个电路,例如逻辑门。在各种实施例中,第一数据移动操作是存储器阵列中的读取操作或写入操作。

[0198]

在各种实施例中,激活存储器阵列的第一字线包括激活包括在存储器电路中或者独立于存储器电路的存储器阵列的第一字线。在一些实施例中,激活第一字线包括激活存储器阵列的一个或多个存储器单元。在一些实施例中,激活第一字线包括激活上面关于存储器电路100和图1-图2b所讨论的存储器阵列160的字线。

[0199]

在一些实施例中,激活第一字线包括在上面关于存储器电路100和图1-图2b所讨论的字线信号路径wp[1]-wp[n]中的一个上生成字线信号wl[1]-wl[n]中相应的一个。

[0200]

在操作860处,在一些实施例中,选择电路用于将第一或第二地址中的另一个传递到地址解码器。使用选择电路将第一或第二地址中的另一个传递到地址解码器是以与上面关于操作830所讨论的使用选择电路将第一或第二地址中的一个传递到地址解码器相同的方式执行的。

[0201]

在操作870处,在一些实施例中,地址解码器用于解码第一或第二地址中的另一个。使用解码器解码第一或第二地址中的另一个是以与上面关于操作840所讨论的使用解码器解码第一或第二地址中的一个相同的方式执行的。

[0202]

在操作880处,在一些实施例中,基于第一或第二地址中的另一个,在写入操作中激活存储器阵列中的第二字线。激活存储器阵列中的第二字线是以与上面关于操作850所讨论的激活存储器阵列的第一字线相同的方式执行的。

[0203]

在一些实施例中,使用上面关于存储器电路100、控制电路170和300、信号生成电路500和600、以及图1-图7b所讨论的自时序控制信号(例如,时钟脉冲信号cktw、chtr、以及ckp)以及选择信号psel来执行操作830到880。在一些实施例中,操作830到880在时钟信号(例如,上面关于存储器电路100、控制电路170和300、信号生成电路500和600、以及图1-图7b所讨论的时钟信号clk)的单个周期内执行。

[0204]

通过执行方法800的一些或全部操作,存储器电路用于基于所接收的两个地址中的所选择的一个执行数据移动操作,从而获得上面关于存储器电路100、控制电路300、以及信号生成电路600所讨论的益处。

[0205]

在一些实施例中,电路包括选择电路,该选择电路被配置为在第一输入处接收第一地址并且在第二输入处接收第二地址,当选择信号具有第一逻辑时将第一地址传递到输出并且当选择信号具有不同于第一逻辑状态的第二逻辑状态时,将第二地址传递到输出。该电路还包括:解码器,该解码器被配置为对所传递的第一地址或第二地址进行解码。在一

些实施例中,该电路包括:第一锁存电路,该第一锁存电路被配置为响应于第一时钟脉冲信号将第一地址输出到第一输入;以及第二锁存电路,该第二锁存电路耦合在选择电路和解码器之间,第二锁存电路被配置为响应于第二时钟脉冲信号而锁存所传递的第一地址或第二地址。在一些实施例中,该电路包括控制电路,该控制电路被配置为接收时钟信号、第一启用信号、以及第二启用信号,并基于时钟信号、第一启用信号、以及第二启用信号生成选择信号、第一时钟脉冲信号、以及第二时钟脉冲信号。在一些实施例中,第二锁存电路被配置为响应于第二时钟脉冲信号从第一逻辑状态或第二逻辑状态中的第一个逻辑状态到第一逻辑状态或第二逻辑状态中的第二个逻辑状态的第一转换而锁存所传递的第一地址或第二地址,并且控制电路被配置为在选择信号具有第一逻辑状态时生成第一转换。在一些实施例中,第二锁存电路被配置为响应于第二时钟脉冲信号从第一逻辑状态或第二逻辑状态中的第二个逻辑状态到第一逻辑状态或第二逻辑状态中的第一个逻辑状态的第二转换而输出所传递的第一地址或第二地址,并且控制电路被配置为在选择信号具有第二逻辑状态时生成第二转换。在一些实施例中,该电路包括预解码器,耦合在第二锁存电路和解码器之间预解码器,其中,控制电路被配置为针对第一间隔和第二间隔激活预解码器,在第一间隔期间,第二时钟脉冲信号具有第一逻辑状态或第二逻辑状态中的第二个逻辑状态,并且选择信号从第二逻辑状态转换到第一逻辑状态,并且在第二间隔期间,第二时钟脉冲信号具有第一逻辑状态或第二逻辑状态中的第二个逻辑状态,并且选择信号具有第一逻辑状态。在一些实施例中,控制电路被配置为基于时钟信号使得选择信号从第二逻辑状态转换到第一逻辑状态,并且基于跟踪信号从第一逻辑状态转换到第二逻辑状态。在一些实施例中,控制电路被配置为响应于第一启用信号并响应于第二启用信号而生成跟踪信号。在一些实施例中,解码器包括耦合到多个字线信号路径的输出,并且解码器被配置为激活多个字线信号路径中的与经解码的所传递的第一地址或第二地址相对应的字线信号路径。

[0206]

在一些实施例中,操作存储器电路的方法包括在选择电路处接收第一地址和第二地址,使用选择电路将第一地址或第二地址中的一个地址传递到地址解码器,并使用地址解码器解码第一地址或第二地址中的该一个地址。在一些实施例中,在选择电路处接收第一地址包括从锁存电路接收第一地址。在一些实施例中,将第一地址或第二地址中的该一个地址传递到地址解码器包括在锁存电路处从选择电路接收第一地址或第二地址中的该一个地址。在一些实施例中,该方法包括使用选择电路将第一地址或第二地址中的另一个地址传递到地址解码器,并使用地址解码器解码第一地址或第二地址中的另一个地址。在一些实施例中,该方法包括:基于经解码的第一地址,在写入操作中激活存储器阵列的第一字线,并且基于经解码的第二地址,在读取操作中激活存储器阵列的第二字线。

[0207]

在一些实施例中,存储器电路包括存储器阵列和选择电路,该选择电路被配置为在第一输入处接收写入地址并在第二输入处接收读取地址,当选择信号具有第一逻辑状态时将写入地址传递到输出,并且当选择信号具有不同于第一逻辑状态的第二逻辑状态时,将读取地址传递到输出。存储器电路还包括:解码器,该解码器被配置为对所传递的写入地址或读取地址进行解码,并激活存储器阵列中与经解码的写入地址或读取地址相对应的字线信号路径。在一些实施例中,存储器电路包括控制电路,该控制电路被配置为响应于时钟信号生成时钟脉冲信号,其中,时钟脉冲信号包括在时钟信号的周期期间的第一脉冲或第二脉冲中的至少一个,并且存储器电路被配置为在第一脉冲期间激活与经解码的读取地址

对应的字线信号路径,并且在第二脉冲期间激活与经解码的写入地址对应的字线信号路径。在一些实施例中,第一脉冲具有基于第一跟踪间隔的第一脉冲宽度,第二脉冲具有基于第二跟踪间隔的第二脉冲宽度。在一些实施例中,存储器电路被配置为从第一端口接收读取地址并且从第二端口接收写入地址,第一跟踪间隔基于使用第一端口的读取操作,第二跟踪间隔基于使用第二个端口的写入操作。在一些实施例中,控制电路被配置为响应于第一启用信号生成第一脉冲,并且响应于第二启用信号生成第二脉冲。在一些实施例中,存储器阵列包括处理器寄存器的寄存器文件,并且存储器电路被配置为控制伪双端口寄存器文件(2prf)操作中的数据移动。

[0208]

前面概述了若干实施例的特征,使得本领域普通技术人员可以更好地理解本公开的各方面。本领域普通技术人员应该意识到,他们可以容易地将本公开用作用于设计或修改用于执行与本文引入实施例相同的目的和/或实现相同优点的其他过程和结构的基础。本领域普通技术人员还应该意识到,这种等效构造不背离本公开的精神和范围,并且他们可以进行各种改变、替换、和修改而不背离本公开的精神和范围。

[0209]

示例1.一种存储器电路,包括:选择电路,被配置为:在第一输入处接收第一地址并在第二输入处接收第二地址,当选择信号具有第一逻辑状态时,将所述第一地址传递到输出,并且当选择信号具有不同于所述第一逻辑状态的第二逻辑状态时,将所述第二地址传递到所述输出;以及解码器,被配置为对所传递的第一地址或第二地址进行解码。

[0210]

示例2.根据示例1所述的电路,还包括:第一锁存电路,被配置为响应于第一时钟脉冲信号而将所述第一地址输出到所述第一输入;以及第二锁存电路,被耦合在所述选择电路和所述解码器之间,所述第二锁存电路被配置为响应于第二时钟脉冲信号而锁存所传递的第一地址或第二地址。

[0211]

示例3.根据示例2所述的电路,还包括:控制电路,被配置为:接收时钟信号、第一启用信号、以及第二启用信号,并且基于所述时钟信号、所述第一启用信号、以及所述第二启用信号生成所述选择信号、所述第一时钟脉冲信号、以及所述第二时钟脉冲信号。

[0212]

示例4.根据示例3所述的电路,其中,所述第二锁存电路被配置为:响应于所述第二时钟脉冲信号从所述第一逻辑状态或所述第二逻辑状态中的第一个逻辑状态到所述第一逻辑状态或所述第二逻辑状态中的第二个逻辑状态的第一转换,锁存所传递的第一地址或第二地址,并且所述控制电路还被配置为:在所述选择信号具有所述第一逻辑状态时生成所述第一转换。

[0213]

示例5.根据示例4所述的电路,其中,所述第二锁存电路被配置为:响应于所述第二时钟脉冲信号从所述第一逻辑状态或所述第二逻辑状态中的所述第二个逻辑状态到所述第一逻辑状态或所述第二逻辑状态中的所述第一个逻辑状态的第二转换,输出所传递的第一地址或第二地址,并且所述控制电路还被配置为:在所述选择信号具有所述第二逻辑状态时生成所述第二转换。

[0214]

示例6.根据示例5所述的电路,还包括:预解码器,耦合在所述第二锁存电路和所述解码器之间,其中所述控制电路还被配置为:针对第一间隔和第二间隔激活所述预解码器,在所述第一间隔期间,所述第二时钟脉冲信号具有所述第一逻辑状态或所述第二逻辑状态中的所述第二个逻辑状态,并且所述选择信号从所述第二逻辑状态转换到所述第一逻辑状态,并且在所述第二间隔期间,所述第二时钟脉冲信号具有所述第一逻辑状态或所述

第二逻辑状态中的所述第二个逻辑状态,并且所述选择信号具有所述第一逻辑状态。

[0215]

示例7.根据示例3所述的电路,其中,所述控制电路还被配置为使得所述选择信号:基于所述时钟信号从所述第二逻辑状态转换到所述第一逻辑状态,并且基于跟踪信号从所述第一逻辑状态转换到所述第二逻辑状态。

[0216]

示例8.根据示例7所述的电路,其中,所述控制电路还被配置为:响应于所述第一启用信号并响应于所述第二启用信号而生成所述跟踪信号。

[0217]

示例9.根据示例1所述的电路,其中,所述解码器包括耦合到多个字线信号路径的输出,并且所述解码器被配置为:激活所述多个字线信号路径中与经解码的所传递的第一地址或第二地址相对应的字线信号路径。

[0218]

示例10.一种操作存储器电路的方法,所述方法包括:在选择电路处接收第一地址和第二地址;使用所述选择电路将所述第一地址或所述第二地址中的一个地址传递到地址解码器;并且使用所述地址解码器对所述第一地址或所述第二地址中的所述一个地址进行解码。

[0219]

示例11.根据示例10所述的方法,其中,在所述选择电路处接收所述第一地址包括从锁存电路接收所述第一地址。

[0220]

示例12.根据示例10所述的方法,其中,将所述第一地址或所述第二地址中的所述一个地址传递到所述地址解码器包括:在锁存电路处从所述选择电路接收所述第一地址或所述第二地址中的所述一个地址。

[0221]

示例13.根据示例10所述的方法,还包括:使用所述选择电路将所述第一地址或所述第二地址中的另一个地址传递到所述地址解码器;并且使用所述地址解码器对所述第一地址或所述第二地址中的所述另一个地址进行解码。

[0222]

示例14.根据示例13所述的方法,还包括:基于经解码的第一地址,在写入操作中激活存储器阵列的第一字线;并且基于经解码的第二地址,在读取操作中激活所述存储器阵列的第二字线。

[0223]

示例15.一种存储器电路,包括:存储器阵列;选择电路,被配置为:在第一输入处接收写入地址,并且在第二输入处接收读取地址,当选择信号具有第一逻辑状态时,将所述写入地址传递到输出,并且当所述选择信号具有不同于所述第一逻辑状态的第二逻辑状态时,将所述读取地址传递到所述输出;以及解码器,被配置为:对所传递的写入地址或读取地址进行解码,并且激活所述存储器阵列中与经解码的写入地址或读取地址相对应的字线信号路径。

[0224]

示例16.根据示例15所述的存储器电路,还包括:控制电路,被配置为响应于时钟信号而生成时钟脉冲信号,其中所述时钟脉冲信号包括在所述时钟信号的周期期间的第一脉冲或第二脉冲中的至少一个,以及存储器电路,被配置为:在所述第一脉冲期间激活对应于经解码的读取地址的字线信号路径,并且在所述第二脉冲期间激活对应于经解码的写入地址的字线信号路径。

[0225]

示例17.根据示例16所述的存储器电路,其中,所述第一脉冲具有基于第一跟踪间隔的第一脉冲宽度,并且所述第二脉冲具有基于第二跟踪间隔的第二脉冲宽度。

[0226]

示例18.根据示例17所述的存储器电路,其中,所述存储器电路被配置为:从第一端口接收所述读取地址并从第二端口接收所述写入地址,所述第一跟踪间隔基于使用所述

第一端口的读取操作,并且所述第二跟踪间隔基于使用所述第二端口的写入操作。

[0227]

示例19.根据示例16所述的存储器电路,其中,所述控制电路被配置为:响应于第一启用信号而生成所述第一脉冲,并且响应于第二启用信号而生成所述第二脉冲。

[0228]

示例20.根据示例15所述的存储器电路,其中,所述存储器阵列包括处理器寄存器的寄存器文件,并且所述存储器电路被配置为:控制伪双端口寄存器文件(2prf)操作中的数据移动。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。