磁盘装置

[0001]

相关申请

[0002]

本申请享有以日本专利申请2019-151438号(申请日:2019年8月21日)作为在先申请的优先权。本申请通过参照该在先申请而包括在先申请的全部内容。

技术领域

[0003]

本实施方式涉及磁盘装置。

背景技术:

[0004]

在磁盘装置中,在使读写条件最佳化时,需要确认读写质量。因此,执行与读写质量相关的指标的测定。

技术实现要素:

[0005]

一实施方式提供便利性高的磁盘装置。

[0006]

根据一实施方式,磁盘装置具备第1解码电路、第2解码电路、控制电路、存储电路、判定电路以及取得电路。第1解码电路通过对从磁盘读出的信号序列执行使用了用于将分支度量标准化的参数的维特比(viterbi)解码来计算似然信息。第2解码电路通过使用了似然信息的迭代解码来生成第1比特数据序列,并且对该第1比特数据序列执行使用了奇偶校验矩阵的校验。控制电路使第1解码电路及第2解码电路反复执行解码,并且根据每次执行基于第1解码电路及第2解码电路的解码时获得的校验的结果来进行参数的更新。判定电路判定进行了基于第1解码电路及第2解码电路的解码的次数是否与第1值相等。取得电路取得与第2比特数据序列所包含的错误比特数对应的数值信息并保存于存储电路,所述第2比特数据序列是在次数与第1值相等时获得的第1比特数据序列。

附图说明

[0007]

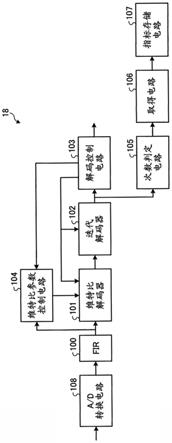

图1是示出第1实施方式涉及的磁盘装置的构成的一个例子的示意图。

[0008]

图2是示出第1实施方式涉及的rdc的详细的构成的一个例子的示意图。

[0009]

图3是用于说明计算第1实施方式涉及的使用了奇偶校验矩阵的奇偶校验式的违规数的方法的图。

[0010]

图4是示出第1实施方式涉及的磁盘装置的通常的读出动作的一个例子的流程图。

[0011]

图5是示出第1实施方式涉及的磁盘装置的读写质量的测定的动作的一个例子的流程图。

[0012]

图6是示出在测定读写质量时在一次读出中执行的第1实施方式涉及的rdc的动作的一个例子的流程图。

[0013]

图7是示出第2实施方式涉及的rdc的详细的构成的一个例子的示意图。

[0014]

图8是示出在测定读写质量时在一次读出中执行的第2实施方式涉及的rdc的动作的一个例子的流程图。

[0015]

图9是示出第2实施方式涉及的磁盘装置执行的写电流的调整的动作的详细的一个例子的流程图。

[0016]

图10是示出第3实施方式涉及的rdc的详细的构成的一个例子的示意图。

[0017]

图11是示出在测定读写质量时在一次读出中执行的第3实施方式涉及的rdc的动作的一个例子的流程图。

[0018]

图12是示出第3实施方式的读出重试动作的一个例子的流程图。

[0019]

图13是示出第4实施方式涉及的rdc的详细的构成的一个例子的示意图。

[0020]

图14是示出第4实施方式涉及的磁盘装置的读写质量的测定的动作的一个例子的流程图。

[0021]

图15是示出第4实施方式涉及的磁盘装置执行的写电流的调整的动作的详细的一个例子的流程图。

具体实施方式

[0022]

以下参照附图对实施方式涉及的磁盘装置详细地进行说明。此外,本发明不被这些实施方式所限定。

[0023]

(第1实施方式)

[0024]

图1是示出第1实施方式涉及的磁盘装置1的构成的一个例子的示意图。如图1所示,磁盘装置1能够连接于主机2。主机2是向磁盘装置1发出用于进行所期望的动作的命令的计算机装置。命令例如包括用于将数据向磁盘装置1写入的写命令(write command)、和用于从磁盘装置1读出数据的读命令(read command)。主机2例如是服务器等。

[0025]

磁盘装置1具备磁盘10、磁头11、头致动器12、spm(spindle motor:主轴马达)13、vcm(voice coil motor:音圈马达)14、spm驱动电路15、vcm驱动电路16、前置放大器17、rdc(read channel:读通道)18、hdc(hard disk controller:硬盘控制器)19、mpu(micro processor unit:微处理器)20以及存储器21。

[0026]

磁盘10是在圆盘状的铝和/或玻璃基板等物体上形成有磁性层的存储介质。

[0027]

spm13使磁盘旋转驱动。

[0028]

头致动器12在前端安装有磁头11。磁头11被头致动器12支承为与磁盘10的记录面相对。

[0029]

vcm14驱动头致动器12。由此,安装于头致动器12的前端的磁头11能够相对于磁盘10的记录面进行相对移动。

[0030]

磁头11向磁盘10(更详细而言为磁盘10的磁性层)写入数据、从磁盘10读出数据。

[0031]

spm驱动电路15驱动spm13旋转。vcm驱动电路16驱动vcm14。

[0032]

前置放大器17是放大由磁头11从磁盘10读出的信号及向磁盘10写入的信号的放大器。

[0033]

rdc18能够对向磁盘10写入的数据进行编码、对从磁盘10读取出的信号进行解码。

[0034]

mpu20统括控制磁盘装置1内的各构成要素的动作。存储器21是保存有固件程序、数据等的可改写的存储介质。mpu20例如基于保存于存储器21的固件程序来实现控制。此外,mpu20是处理器的一个例子。

[0035]

hdc19控制在磁盘装置1与主机2之间收发的数据。

[0036]

此外,rdc18、hdc19以及mpu20安装于控制电路基板22。此外,安装于控制电路基板22的构成要素并不限定于此。

[0037]

图2是示出第1实施方式涉及的rdc18的详细的构成的一个例子的示意图。rdc18具备a/d(模拟/数字)转换电路108、fir(finite impulse response:有限脉冲响应)滤波器100、维特比(viterbi)解码器101、迭代解码器102、解码控制电路103、维特比参数控制电路104、次数判定电路105、取得电路106以及指标存储电路107。

[0038]

此外,维特比解码器101是第1解码电路的一个例子。迭代解码器102是第2解码电路的一个例子。解码控制电路103及维特比参数控制电路104是控制电路的一个例子。指标存储电路107是存储电路的一个例子。次数判定电路105是判定电路的一个例子。

[0039]

磁头11读出的信号(再现信号)经由前置放大器17向a/d转换电路108输入。之后,再现信号在经a/d转换电路108进行了a/d转换后向fir滤波器100输入。

[0040]

fir滤波器100是将来自磁头11的再现信号与将要使用的pr(partial response:部分响应)特性相匹配的波形均衡器。通过选择与磁盘10的再现信号特性相似的pr特性来作为目标的pr特性,从而抑制由均衡导致的杂音成分的放大。波形均衡器将再现信号波形均衡为与目标的pr特性(pr class)相应的响应波形(部分响应波形信号)。由此,生成将各符号(symbol)表示为波高即电平的波形信号序列。将这样获得的波形信号序列标记为样本数据序列。

[0041]

维特比解码器101对从fir滤波器100输出的样本数据序列实施维特比解码,计算似然信息。

[0042]

维特比解码的步骤包括分支度量(branch metric)的计算、路径度量(path metric)的计算、路径度量的比较、以及幸存路径的选择。例如,分支度量是按预定长度(在一个例子中为3个符号)的每个数据样式(data pattern)准备的电平(数据比特的电平(level))的期待值与样本数据序列所包含的符号的电平的平方误差。路径度量是将分支度量累积而得到的。路径度量成为最小的路径被设为最大似然序列。

[0043]

在此,维特比解码器101输出似然信息。似然信息是按每个符号示出最大似然序列的可靠性的信息。在一个例子中,似然信息是按每个符号获得的平方误差。

[0044]

样本数据序列可以包括噪声。该噪声并不限于随机噪声。因此,维特比解码器101在进行维特比解码时执行分支度量的标准化。例如,维特比解码器101通过将电平的平均值与样本数据序列所包含的电平的平方误差除以电平的标准偏差所对应的值,从而将该平方误差标准化。由此,能够获得在假定为样本数据序列所包含的噪声是随机噪声的情况下的分支度量。通过将分支度量标准化,维特比解码的精度提高。

[0045]

此外,电平的标准偏差所对应的值是用于将分支度量标准化的参数的一个例子。用于将分支度量标准化的参数可以包括电平的平均值。另外,用于将分支度量标准化的参数可以包括与预定长度的数据的各比特数据(bit data,位数据)相乘的加权系数。

[0046]

按预定长度的每个数据样式单独准备用于将分支度量标准化的参数。以后,将用于将分支度量标准化的参数表示为维特比参数。

[0047]

维特比参数控制电路104执行维特比参数的更新。更具体而言,维特比参数控制电路104基于样本数据序列与通过后述的迭代解码器102获得的比特数据序列的关系来实施维特比参数的学习,并利用通过学习的结果获得的值对维特比参数的设定值进行更新。

[0048]

迭代解码器102基于从维特比解码器101输出的似然信息来实施迭代解码,并制作样本数据序列所对应的比特数据序列。另外,迭代解码器102对该比特数据序列执行使用了奇偶校验矩阵的校验而计算奇偶校验式的违规数。

[0049]

作为由迭代解码器102进行的迭代解码的方式,可以采用使用了概率传播算法的任意的方式。在一个例子中,可以采用ldpc(low density parity check:低密度奇偶校验)作为由迭代解码器102进行的迭代解码。

[0050]

图3是用于说明计算第1实施方式涉及的使用了奇偶校验矩阵的奇偶校验式的违规数的方法的图。

[0051]

奇偶校验矩阵h是以包含奇偶校验位(bit)的数据比特(data bit)位置作为列,以奇偶校验式作为行的矩阵。对从右对该奇偶校验矩阵h乘以比特数据序列而得到的序列的各要素计算对2取的余数。根据通过该计算而获得的序列来运算奇偶校验式的违规数。以后,将奇偶校验式的违规数表示为奇偶违规数。

[0052]

返回到图2进行说明。解码控制电路103基于作为使用了奇偶校验矩阵的校验的结果获得的奇偶违规数来控制维特比解码及迭代解码的反复。

[0053]

另外,解码控制电路103基于奇偶违规数来判定是否执行维特比参数的学习。解码控制电路103在判定为执行维特比参数的学习的情况下,向维特比参数控制电路104指示学习的执行。

[0054]

在使用了奇偶校验矩阵的校验中合格了的情况下,即在奇偶违规数为0的情况下,能够推定为解码成功,因此解码控制电路103将从迭代解码器102生成的比特数据序列向后段的处理电路发送。后段的处理电路例如是解调器。

[0055]

次数判定电路105判定执行了维特比解码及迭代解码的次数是否与预先设定的指标存储片(slice)相等。指标存储片例如由mpu20设定。此外,指标存储片既可以被固定,也可以由mpu20等根据状况进行变更。此外,以后,将执行了维特比解码及迭代解码的次数标记为解码的执行次数。指标存储片是第1实施方式的第1值的一个例子。

[0056]

取得电路106在解码的执行次数与指标存储片相等的情况下,取得表示读写质量的指标,并将所取得的指标保存于指标存储电路107。

[0057]

此外,只要与扇区错误率之间具有强相关性,就可以采用任意的数值信息作为表示读写质量的指标。

[0058]

例如,可以认为在解码的执行次数与指标存储片相等时所取得的比特数据序列所包含的错误比特(bit error)数与保存该比特数据序列的扇区的扇区错误率具有相关性。由此,可以采用在解码的执行次数与第1值相等时所取得的比特数据序列所包含的错误比特数来作为指标。

[0059]

具体而言,例如,取得电路106将在向磁盘10写入之前等获得的、没有错误的比特数据序列保存于预定的寄存器等。并且,取得电路106计算保存于该寄存器的比特数据序列与在解码的执行次数与指标存储片相等时由迭代解码器102生成的比特数据序列的异或(xor)。并且,取得电路106对通过异或判明的错误比特进行累计,从而能够取得上述的错误比特数。

[0060]

进而,可以认为在解码的执行次数与指标存储片相等时所计算出的奇偶违规数也与保存该比特数据序列的扇区的扇区错误率具有相关性。可以采用在解码的执行次数与指

标存储片相等时所计算出的奇偶违规数来作为指标。

[0061]

例如,取得电路106能够取得在解码的执行次数与指标存储片相等时由迭代解码器102计算出的奇偶违规数来作为指标。

[0062]

在读写质量差的情况下,所获得的错误比特数或奇偶违规数变大。相反地,在读写质量好的情况下,所获得的错误比特数或奇偶违规数变小。也就是说,像上述那样取得的错误比特数和/或奇偶违规数可以用作表示读写质量的指标。

[0063]

即使读写质量差,在解码成功了的情况下,错误比特数和/或奇偶违规数也均为0。即,在解码成功了之后,无法获得与读写质量对应的指标。在实施方式中,使得:不论最终解码是否成功,在反复执行的解码的中途都取得错误比特数和/或奇偶违规数。由此,即使在最终解码成功这样的情况下,也能够获得与读写质量相应的定量值。

[0064]

此外,比特数据序列所包含的错误比特数及奇偶违规数分别是与比特数据序列所包含的错误比特数对应的数值信息的一个例子。

[0065]

此外,在此,作为一个例子,取得电路106对每个预定的存储区域执行指标的取得,所取得的指标的累积值保存于指标存储电路107。也就是说,取得电路106例如在从最初的存储区域取得指标时,将该指标保存于指标存储电路107。而且,取得电路106在从后续的存储区域新取得指标时,将该新取得的指标与保存于指标存储电路107的指标(或指标的累积值)进行合计,并用合计后的值来更新指标存储电路107的内容。

[0066]

预定的存储区域例如是扇区。但是,预定的存储区域并不限定于扇区。

[0067]

此外,指标的保存方法并不限定于以上所述。取得电路106也可以利用按每个预定的存储区域取得的指标以覆写形式来更新指标存储电路107的内容。

[0068]

指标存储电路107例如由小规模的存储器和/或寄存器构成。保存于指标存储电路107的指标例如由mpu20读出。mpu20能够将指标用于读写条件的控制。

[0069]

图4是示出第1实施方式涉及的磁盘装置1的通常的读出动作的一个例子的流程图。

[0070]

首先,在磁盘装置1中,例如mpu20设定维特比参数的初始值(s101)。在此,作为一个例子,维特比参数的值按每个区单独地进行管理。磁盘装置1将与包括读出对象的扇区组的区有关的值设定为初始值。

[0071]

区是将连续的多个磁道汇总而得到的。每个区的维特比参数的值例如在制造工序等中,使用对应的区内的特定的磁道上的多个扇区来最佳化。

[0072]

此外,维特比参数的值的管理的单位不限定于区。另外,被设定为初始值的值并不限定于以上所述。每个区的维特比参数的值的运算方法并不限定于以上所述。

[0073]

接下来,磁盘装置1选择读出对象的扇区组的开头的扇区的编号(s102)。将所选择出的编号设为x。

[0074]

接下来,磁盘装置1执行扇区x的比特数据序列的读出(s103)。在读出时,在rdc18中执行解码。另外,在解码时,执行维特比参数的学习和更新。

[0075]

在解码不成功的情况下(s104:否(no)),磁盘装置1停止读出的处理并执行后处理(s105)。另外,在s105中后处理结束时,磁盘装置1将x的值递增1并再次开始读出,执行s103的处理。

[0076]

后处理可以任意地构成。在一个例子中,rdc18向hdc19报告解码失败。hdc19根据

解码失败的报告而停止读出,并向主机2报告错误。

[0077]

此外,在s105中,hdc19可以等待从主机2读出下一扇区的指示,当接收到该指示时,进行x的递增及s103的执行。或者,hdc19也可以不等待来自主机2的指示便进行x的递增及s103的执行。

[0078]

在解码成功了的情况下(s106:是(yes)),磁盘装置1判定扇区x是否为读出对象的扇区组中的最终扇区(s106)。在扇区x不是最终扇区的情况下(s106:否),磁盘装置1将x递增1(s107),并再次执行s103的处理。

[0079]

在扇区x为最终扇区的情况下(s106:是),通常的读出动作结束。

[0080]

在上述说明的通常的读出动作中,按每个扇区执行维特比参数的学习。并且,通过各扇区的读出而学习完成的维特比参数在下一扇区的读出时被沿用,在该下一读出中进一步执行学习。

[0081]

此外,例如,在刚刚执行包含在某区(标记为第1区)中的扇区的读出后执行包含在另一区(标记为第2区)中的扇区的读出时,不进行维特比参数的沿用,而设定与第2区有关的维特比参数的值。此外,即使在这样的情况下也可以进行维特比参数的沿用。

[0082]

图5是示出第1实施方式涉及的磁盘装置1的读写质量的测定的动作的一个例子的流程图。

[0083]

首先,mpu20设定在指标的取得时机(timing)判定中所使用的指标存储片(s201)。然后,磁盘装置1向读写质量的测定对象的扇区组写入比特数据序列(s202)。取得电路106也可以在执行s202时将写入之前的比特数据序列保存于预定的寄存器等。

[0084]

接下来,mpu20将磁盘装置1的动作模式设定为错误忽略模式(s203)。错误忽略模式是指即使报告了解码的失败也不执行读出的停止的动作模式。

[0085]

接下来,在磁盘装置1中,例如mpu20设定维特比参数的初始值(s204)。在此,作为一个例子,维特比参数的值按每个区单独地进行管理。磁盘装置1将与包括读写质量的对象的扇区组的区有关的值设定为初始值。此外,与s101同样地,初始值的设定方法并不限定于此。

[0086]

接下来,磁盘装置1选择读出对象的扇区组的开头的扇区的编号(s205)。将选择出的编号设为x。

[0087]

接下来,磁盘装置1读出扇区x的比特数据序列(s206)。在读出时,在rdc18中执行解码。另外,在解码时,执行维特比参数的学习和更新。另外,在解码的执行次数与指标存储片相等时,由取得电路106取得指标。

[0088]

接下来,磁盘装置1判定扇区x是否为读写质量的测定对象的扇区组中的最终扇区(s207)。在扇区x不是最终扇区的情况下(s207:否),磁盘装置1将x递增1(s208),并再次执行s206的处理。

[0089]

在扇区x为最终扇区的情况下(s207:是),mpu20取得在指标存储电路107中累积的指标(s209)。通过s209,读写质量的测定的动作结束。

[0090]

在测定读写质量时的读出动作中,按每个扇区执行维特比参数的学习。并且,通过各扇区的读出而学习完成的维特比参数在下一扇区的读出时被沿用,在该下一读出中进一步执行学习。

[0091]

此外,例如,在刚刚执行包含在某区(标记为第1区)中的扇区的读出后执行包含在

另一区(标记为第2区)中的扇区的读出时,不进行维特比参数的沿用,而设定与第2区有关的维特比参数的值。此外,即使在这样的情况下也可以进行维特比参数的沿用。

[0092]

图6是示出在测定读写质量时在一次读出(具体而言s206的处理)中执行的第1实施方式的rdc18的动作的一个例子的流程图。

[0093]

首先,fir滤波器100生成波形均衡后的样本数据序列(s301)。维特比解码器101使用样本数据序列和来自维特比参数控制电路104的维特比参数使用来进行维特比解码,计算似然信息(s302)。

[0094]

继s302之后,迭代解码器102基于通过s302获得的似然信息来进行迭代解码,并制作比特数据序列(s303)。进而,迭代解码器102使用所制作的比特数据序列和奇偶校验矩阵来计算奇偶违规数(s304)。

[0095]

接下来,解码控制电路103判定通过s304获得的奇偶违规数是否为预定值以下(s305)。预定值可以通过任意的方法来决定。

[0096]

在判定为奇偶违规数为预定值以下的情况下(s305:是),解码控制电路103向维特比参数控制电路104指示学习的执行,维特比参数控制电路104根据该指示执行维特比参数的学习(s306)。

[0097]

在s306中,维特比参数控制电路104基于通过s301从fir滤波器100输出的样本数据序列与通过s303制作的比特数据序列的关系来执行维特比参数的学习。在通过学习获得的值与维特比参数的当前的设定值不同的情况下,维特比参数控制电路104利用通过学习获得的值来更新维特比参数的设定值。

[0098]

在判定为奇偶违规数不是预定值以下的情况下(s305:否),跳过s306的处理。在奇偶违规数不是预定值以下的情况下,通过跳过s306的处理,能够在比特数据序列所包含的错误比特数在一定程度上减少了的时间点执行维特比参数的学习。

[0099]

在s306之后、或者在判定为奇偶违规数不是预定值以下的情况下(s305:否),解码控制电路103判定奇偶违规数是否为0(s307)。

[0100]

在判定为奇偶违规数不是0的情况下(s307:否),次数判定电路105判定解码的执行次数,即成对的维特比解码与迭代解码的执行次数是否与指标存储片相等(s308)。在判定为解码的执行次数与指标存储片相等的情况下(s308:是),取得电路106取得比特数据序列所包含的错误比特数和奇偶违规数,并保存于指标存储电路107(s309)。在此,作为一个例子,取得电路106对错误比特数和奇偶违规数分别进行累积,但也可以不对错误比特数和奇偶违规数分别进行累积。

[0101]

此外,在此,取得电路106取得错误比特数及奇偶违规数这两方作为指标,但指标并不限定于此。取得电路106也可以仅取得错误比特数及奇偶违规数中的一方来作为指标。

[0102]

此外,取得电路106能够通过由s303生成的比特数据序列与在s202中保持于寄存器的向磁盘10写入之前的比特数据序列的比较来取得错误比特数。此外,错误比特数的取得的方法并不限定于此。

[0103]

在判定为解码的执行次数与指标存储片不相等的情况下(s308:否),跳过s309的处理。

[0104]

在s309之后、或者在判定为解码的执行次数与指标存储片不相等的情况下(s308:否),解码控制电路103判定是否能够进行进一步的迭代解码(s310)。

[0105]

例如,在对多个扇区连续执行读出的情况下,要求无延迟地执行该多个扇区的读出。由此,解码一个扇区所需要的时间自然被限制。例如,在剩余有能够进一步反复进行解码(成对的维特比解码与迭代解码)的时间的情况下,判断为能够进行进一步的迭代解码。在没有剩余能够进一步反复进行解码(成对的维特比解码与迭代解码)的时间的情况下,判断为无法进行进一步的迭代解码。此外,判断是否能够进行迭代解码的方法并不限定于此。

[0106]

在判定为无法进行进一步的迭代解码的情况下(s310:否),解码控制电路103例如向mpu20报告解码失败(s311),在测定读写质量时,在一次读出中所执行的动作结束。

[0107]

在判定为能够进行进一步的迭代解码的情况下(s310:是),再次执行s302的处理。此外,在再次执行s302的处理时,在s302中,维特比解码器101能够将在前一次执行的迭代解码中所生成的对数似然信息作为事先信息使用。由此,维特比解码器101能够通过计算获得与上次进行维特比解码时相比改善了的似然信息。

[0108]

在s307的判定处理中判定为奇偶违规数为0的情况下(s307:是),能够推定迭代解码成功。在该情况下,次数判定电路105判定解码的执行次数是否小于指标存储片(s312)。

[0109]

在判定为解码的执行次数小于指标存储片的情况下(s312:是),取得电路106取得比特数据序列所包含的错误比特数和奇偶违规数,并保存于指标存储电路107(s313)。在此作为一个例子,取得电路106对错误比特数和奇偶违规数分别进行累积,但也可以不对错误比特数和奇偶违规数分别进行累积。

[0110]

此外,在s313中,与s309同样地,取得电路106也可以仅取得错误比特数及奇偶违规数中的一方作为指标。另外,取得电路106能够通过由s303生成的比特数据序列与在s202中保持于寄存器的向磁盘10写入之前的比特数据序列的比较来取得错误比特数。此外,错误比特数的取得的方法并不限定于此。

[0111]

在判定为解码的执行次数不是小于指标存储片的情况下(s312:否),跳过s313的处理。

[0112]

在s313的处理之后、或者在判定为解码的执行次数不是小于指标存储片的情况下(s312:否),解码控制电路103例如向mpu20报告解码成功(s314),在测定读写质量时,在一次读出中所执行的动作结束。

[0113]

通过图5所示的动作,按构成作为读写质量的测定对象的扇区组的每个扇区执行图6所示的一系列的动作。通过对每个扇区执行图6所示的一系列的动作,按每个扇区取得的指标在指标存储电路107中累积。在指标存储电路107中累积的作为读写质量的测定对象的扇区组的每个扇区的指标由mpu20通过s209的处理来取得。

[0114]

mpu20能够将所取得的每个扇区的指标用于读写条件的最佳化。读写条件的最佳化可以包括任意的处理。

[0115]

例如,mpu20可以基于一个以上的指标进行写电流的调整。另外,mpu20可以基于一个以上的指标进行记录密度的调整。记录密度既可以是tpi(tracks per inch,每英寸磁道数),也可以是bpi(bits per inch,每英寸比特数,位密度),也可以是这两方。

[0116]

此外,图6所示的一系列的动作也可以在通常的读出中执行。即,rdc18也可以在通常的读出中取得指标。mpu20也可以不取得在通常的读出中rdc18所取得的指标。

[0117]

如上所述,根据第1实施方式,作为第1解码电路的维特比解码器101通过对样本数据序列执行使用了作为用于将分支度量标准化的参数的维特比参数的维特比解码来计算

似然信息。作为第2解码电路的迭代解码器102通过使用了似然信息的迭代解码来生成比特数据序列,并且对该比特数据序列执行使用了奇偶校验矩阵的校验。作为控制电路的解码控制电路103及维特比参数控制电路104根据每次执行基于维特比解码器101及迭代解码器102的解码时获得的校验的结果(即奇偶违规数)来进行维特比参数的更新。作为判定电路的次数判定电路105判定解码的执行次数是否与指标存储片(第1值)相等。取得电路106取得在解码的执行次数与指标存储片相等时获得的比特数据序列所包含的错误比特数所对应的数值信息并保存于作为存储电路的指标存储电路107。此外,数值信息例如是在解码的执行次数与指标存储片相等时获得的比特数据序列所包含的错误比特数、或者在解码的执行次数与指标存储片相等时获得的奇偶违规数。

[0118]

作为与第1实施方式进行比较的技术,可考虑以下将说明的技术(标记为第1比较例)。在第1比较例中,禁止成对的维特比解码与迭代解码的反复,由此,故意使解码失败。在解码失败的情况下,取得此时的奇偶违规数或比特数据序列所包含的错误比特数来作为指标。

[0119]

然而,根据第1比较例,由于禁止成对的维特比解码与迭代解码的反复,所以不执行维特比参数的学习。也就是说,根据第1比较例,在与通常的读出在维特比参数这一点上不同的条件下取得指标,所以很难说作为指标获得的值是与读写质量的相关性高的数值信息。

[0120]

另外,作为与第1实施方式进行比较的另一技术,可考虑以下将说明的技术(标记为第2比较例)。在第2比较例中,首先对对象的扇区执行通常的读出,在该读出时,进行维特比参数的学习。之后,在成对的维特比解码与迭代解码的反复被禁止了的状态下,对该对象的扇区执行读出。由此,故意使解码失败。在解码失败了的情况下,取得此时的奇偶违规数或比特数据序列所包含的错误比特数来作为指标。

[0121]

根据第2比较例,在通过通常的读出执行了维特比参数的学习之后,执行用于取得指标的读出。由此,能够在与通常的读出类似的条件下取得指标。然而,根据第2比较例,由于在执行了通常的读出之后执行指标的取得,所以取得指标所需要的时间增大。

[0122]

根据第1实施方式,通过如上所述的构成,能够不禁止成对的维特比解码与迭代解码的反复而取得指标。因此,例如,通过对多个扇区依次执行读出,能够在进行使用了学习完成的参数的读出的同时取得指标。由此,与第1比较例相比,能够获得与读写质量的相关性较高的数值信息来作为指标。另外,与第2比较例相比,能够缩短取得每个扇区的指标所需要的时间。也就是说,便利性提高。

[0123]

此外,在上述的说明中,在测定与读写质量对应的指标时,执行某扇区的读出,之后,将通过该扇区的读出进行了学习后的维特比参数的值用作执行下一扇区的读出时的维特比参数的初始值。

[0124]

在这样的运用中,在下一扇区的读出时使用学习完成的维特比参数的值这一点与实施方式的通常的读出时相同。由此,关于维特比参数,由于能够在与通常的读出相同的条件下取得与读写质量对应的指标,所以能够取得对于读写质量的相关性较高的值作为指标。

[0125]

另外,根据上述那样的运用,在从第二个以后的扇区进行读出时,能够大幅度地减少为了使奇偶违规数成为预定值(图6的s305的处理中的预定值)以下所需的解码的执行次

数。由此,与第2比较例相比,能够缩短取得每个扇区的指标所需要的时间。

[0126]

此外,磁盘10具备多个存储区域,所述多个存储区域分别是用于通常的读出及读写质量的测定的读出单位。在以上所说明的例子中,设为该多个存储区域分别为扇区。多个存储区域中的每一个并不限定于扇区。

[0127]

(第2实施方式)

[0128]

当写电流不足时,例如在像“00100”那样,在同一值连续的中途仅少数位(bit)反转了这样的数据样式等中错误比特数增加。由此,若按每个数据样式测定错误比特数,则能够将该测定的结果用于写电流的调整。此外,此处所说的特定的数据样式与在维特比解码中用于计算分支矩阵的数据样式不同。

[0129]

第2实施方式的磁盘装置1在具备rdc18a来替代rdc18这一点上与第1实施方式不同。在以后的第2实施方式的说明中,对与第1实施方式相同的构成要素标注与第1实施方式相同的名称及标号,并省略详细的说明。

[0130]

图7是示出第2实施方式涉及的rdc18a的详细的构成的一个例子的示意图。rdc18a具备a/d转换电路108、fir滤波器100、维特比解码器101、迭代解码器102、解码控制电路103、维特比参数控制电路104、次数判定电路105、取得电路106a以及多个指标存储电路107a。

[0131]

在此,作为多个指标存储电路107a的一个例子,设置有四个指标存储电路107a-1、107a-2、107a-3、107a-4。此外,设置于rdc18a的指标存储电路107a数并不限定于四个。四个指标存储电路107a-1、107a-2、107a-3、107a-4例如由小规模的存储器、寄存器构成。此外,多个指标存储电路107a是存储电路的另一个例子。

[0132]

取得电路106a具备样式检测电路109。在样式检测电路109中预先设定有例如上述的“00100”等一个以上的数据样式。并且,样式检测电路109从向磁盘10写入之前的比特数据序列中检测预先设定的特定的数据样式。取得电路106a按由样式检测电路109检测出的每个数据样式取得错误比特数。

[0133]

例如,假设在样式检测电路109中预先设定数据样式“00100”和数据样式“11100”。由迭代解码器102生成的比特数据序列在五个部位包括数据样式“00100”,在七个部位包括数据样式“11100”,在关于五个部位的数据样式“00100”合计出现了三个错误比特,关于七个部位的数据样式“11100”合计出现了一个错误比特的情况下,由取得电路106a取得“3”作为与数据样式“00100”有关的错误比特数,并取得“1”作为与数据样式“11100”有关的错误比特数。

[0134]

在样式检测电路109中设定的一个以上的数据样式与四个指标存储电路107a-1、107a-2、107a-3、107a-4中的任一个相关联。数据样式与指标存储电路107a的对应关系可以是一对一,也可以是多对一。取得电路106a将按每个数据样式取得的错误比特数保存于对应的指标存储电路107a。

[0135]

也就是说,在第2实施方式中,取得按每个数据样式取得的错误比特数来作为指标。此外,除了按每个数据样式取得的错误比特数以外,指标也可以包括由迭代解码器102生成的比特数据序列所包含的错误比特数或由迭代解码器102计算出的奇偶违规数。

[0136]

图8是示出在测定读写质量时在一次读出中执行的第2实施方式的rdc18a的动作的一个例子的流程图。如图8所示,第2实施方式的rdc18a的动作与第1实施方式的rdc18的

动作的不同之处在于,包括s401来替代图6的s309的处理,并且包括s402来替代图6的s313的处理。在此,对s401的处理及s402的处理进行说明,对其他处理省略说明。

[0137]

s401的处理及s402的处理均是取得指标的处理,并执行彼此相同的动作。具体而言,在s401的处理及s402的处理中,样式检测电路109从向磁盘10写入之前的比特数据序列中检测预先设定的特定的数据样式。向磁盘10写入之前的比特数据序列例如预先保存于预定的寄存器等。取得电路106a对由样式检测电路109检测出的每个数据样式计数错误比特数。并且,取得电路106a将每个数据样式的错误比特数保存于对应的指标存储电路107a。在此,作为一个例子,取得电路106按每个数据样式累积错误比特数,但也可以不累积每个数据样式的错误比特数。

[0138]

图9是示出第2实施方式涉及的磁盘装置1执行的写电流的调整的动作的详细的一个例子的流程图。

[0139]

例如,预先确定写电流能够设定的值的范围(调整范围)。mpu20将写电流能够设定的值的范围内的一个值设定为写电流的设定值(s501)。接下来,执行读写质量的测定(s502)。

[0140]

在s502中,执行图5所示的一系列的处理。但是,在s202中,使用通过s501设定的写电流。另外,在一次读出(也就是说s206的处理)时,执行图8所示的一系列的处理。

[0141]

接下来,mpu20判定是否能够在调整范围以内进一步变更写电流(s503)。在该处理中,判定在调整范围以内是否剩余有尚未被设定为写电流的值。在调整范围以内剩余有尚未被设定为写电流的值的情况下,能够将该剩余的值设定为写电流。在判定为能够在调整范围以内进一步变更写电流的情况下(s503:是),再次执行s501的处理。在s501中,将尚未被设定为写电流的值设定为写电流。

[0142]

在调整范围以内没有剩余尚未被设定为写电流的值的情况下,在调整范围以内无法进一步变更写电流。在判定为在调整范围以内无法进一步变更写电流的情况下(s503:否),mpu20基于每次设定写电流时取得的、按每个数据样式进行计数而得到的错误比特数,从写电流能够设定的值的范围中选择一个写电流,并将选择出的写电流决定为调整后的写电流(s504)。mpu20选择写电流能够设定的值的范围内的、按每个数据样式进行计数而得到的错误比特数成为最佳的值来作为调整后的写电流。通过s504,调整写电流的一系列的处理结束。

[0143]

这样,根据第2实施方式,预先设定一个以上的数据样式,取得电路106a对所述第3比特数据序列所包含的每个数据样式计数错误比特数。并且,取得电路106a将按每个数据样式进行计数而得到的错误比特数作为指标保存于指标存储电路107a。

[0144]

由于写电流的不足可能表现为每个数据样式的错误比特数的偏差,所以若使用通过上述的构成获得的每个数据样式的错误比特数来进行写电流的调整,则能够提高写电流的调整精度。

[0145]

(第3实施方式)

[0146]

当包含由于写电流不足而被误写入的多个比特数据时,在反复执行维特比解码和迭代解码时,有时奇偶违规数的减小在中途停止而没有收敛为0。在第3实施方式中,为了使得能够判定奇偶违规数的减小是否在中途停止,设定有多个各自不同的值(第2值)来作为指标存储片,每当解码的执行次数与某个指标存储片相等时便取得奇偶违规数来作为指

标。

[0147]

第3实施方式的磁盘装置1在具备rdc18b来替代rdc18这一点上与第1实施方式不同。在以后的第3实施方式的说明中,对与第1实施方式相同的构成要素标注与第1实施方式相同的名称及标号,并省略详细的说明。

[0148]

图10是示出第3实施方式涉及的rdc18b的详细的构成的一个例子的示意图。rdc18b具备a/d转换电路108、fir滤波器100、维特比解码器101、迭代解码器102、解码控制电路103、维特比参数控制电路104以及多个次数判定电路105b。另外,与多个次数判定电路105b对应地,rdc18b具备多个取得电路106b及多个指标存储电路107b。

[0149]

此外,多个次数判定电路105b是判定电路的另一个例子。多个取得电路106b是取得电路的另一个例子。多个指标存储电路107b是存储电路的再一个例子。

[0150]

在此,作为多个次数判定电路105b的一个例子,设置有三个次数判定电路105b-1、105b-2、105b-3。此外,设置于rdc18b的次数判定电路105b数并不限定于三个。三个指标存储电路107b-1、107b-2、107b-3例如由小规模的存储器、寄存器构成。

[0151]

另外,作为多个取得电路106b,设置有三个取得电路106b-1、106b-2、106b-3。另外,作为多个指标存储电路107b,设置有三个指标存储电路107b-1、107b-2、107b-3。

[0152]

三个次数判定电路105b-1、105b-2、105b-3中的每一个预先设定有各自不同的指标存储片。次数判定电路105b-1判定解码的执行次数是否与自身所设定的指标存储片相等。在解码的执行次数与对次数判定电路105b-1设定的指标存储片相等的情况下,取得电路106b-1取得奇偶违规数来作为表示读写质量的指标,并将所取得的奇偶违规数保存于指标存储电路107b-1。

[0153]

次数判定电路105b-2判定解码的执行次数是否与对自身设定的指标存储片相等。在解码的执行次数与对次数判定电路105b-2设定的指标存储片相等的情况下,取得电路106b-2取得奇偶违规数来作为表示读写质量的指标,并将所取得的奇偶违规数保存于指标存储电路107b-2。

[0154]

次数判定电路105b-3判定解码的执行次数是否与对自身设定的指标存储片相等。在解码的执行次数与对次数判定电路105b-3设定的指标存储片相等的情况下,取得电路106b-3取得奇偶违规数来作为表示读写质量的指标,并将取得的奇偶违规数保存于指标存储电路107b-3。

[0155]

也就是说,在第3实施方式中,在解码的执行次数不同的时机取得的多个奇偶违规数相当于指标。此外,指标还可以包括在取得奇偶违规数的时机取得的错误比特数。

[0156]

图11是示出在测定读写质量时在一次读出中执行的第3实施方式的rdc18b的动作的一个例子的流程图。如图11所示,第3实施方式的rdc18b的动作与第1实施方式的rdc18的动作的不同之处在于,包括s601、s602的处理来替代图6的s308、s309的处理,并且省略了图6的s312、s313的处理。在此,对s601、602的处理进行说明,对其他处理省略说明。

[0157]

在s601的处理中,各次数判定电路105b通过判定解码的执行次数是否与自身所设定的指标存储片相等,从而判定解码的执行次数是否与任一指标存储片相等(s601)。

[0158]

在判定为解码的执行次数与任一指标存储片相等的情况下(s601,yes),判定为解码的执行次数与自身所设定的指标存储片相等的次数判定电路105b所对应的取得电路106b取得奇偶违规数并保存于对应的指标存储电路107b(s602)。在判定为解码的执行次数

与任一指标存储片均不同的情况下(s601:否),跳过s602的处理。

[0159]

由此,取得在解码的执行次数不同的时机取得的多个奇偶违规数来作为指标。

[0160]

此外,图11的处理也可以在通常的读出中实施。在通常的读出中,在读出成功的情况下,也就是说在奇偶违规数成为0的情况下(s307:是),解码控制电路103将通过s303生成的比特数据序列作为解码后的比特数据序列向后段的处理电路发送。在读出失败了的情况下,也就是说在向例如mpu20报告了解码失败的情况下(s311),在基于mpu20的控制下执行读出的重试。在读出的重试中准备了多个设定。在读出的重试中,一边改变设定一边多次重试读出,直到读出成功为止。

[0161]

在奇偶违规数的减小停止的情况下,能够推定包含由于写电流不足而写入失败了的多个比特数据。在该情况下,不使用通常选择的设定,而使用在存在由于写电流不足而写入失败了的比特数据的情况下选择的设定来执行读出的重试。

[0162]

图12是示出第3实施方式的读出重试动作的一个例子的流程图。

[0163]

mpu20在取得按每个指标存储片获得的奇偶违规数时,判定奇偶违规数的减小是否停止(s701)。

[0164]

例如,在奇偶违规数不是0并且当解码的执行次数增大时奇偶违规数的减少量连续为0的情况下,mpu20能够判定为奇偶违规数的减小停止。在即使解码的执行次数增大时奇偶违规数的减少量也为1以上的情况下,mpu20能够判定为奇偶违规数的减小未停止。此外,奇偶违规数的减小是否停止的判定的方法并不限定于此。

[0165]

在判定为奇偶违规数的减小未停止的情况下(s701:否),mpu20控制磁盘装置1整体,使用通常的设定(第1设定)来执行读出(s702)。在判定为奇偶违规数的减小停止的情况下(s701:是),mpu20控制磁盘装置1整体,使用用于存在由于写电流不足而写入失败了的比特数据的情况下的、与通常不同的特殊的设定(第2设定)来执行读出的重试(s703)。通过s702或s703的处理,读出重试动作完成。

[0166]

这样,根据第3实施方式,每当解码的执行次数达到指标存储片时,取得电路106b取得奇偶违规数。

[0167]

由此,能够推定在比特数据序列中是否存在由于写电流不足而写入失败了的比特数据。

[0168]

另外,如使用图12所说明的那样,mpu20在进行读出的重试时,能够基于按每个指标存储片取得的奇偶违规数来调整设定。

[0169]

在推定为存在由于写电流不足而写入失败了的比特数据的情况下,通过使用与通常的设定不同的、用于存在由于写电流不足而写入失败了的比特数据的情况下的设定来重试读出,从而能够有效地执行读出的重试。

[0170]

(第4实施方式)

[0171]

当写电流不足时,由于部分介质灵敏度的偏差等的影响,有时一个磁道内的每个扇区的错误比特数的变动不是正态分布。在按每个磁道使用了指标的平均值或累积值的情况下,由于不知道错误比特数的变动是否成为正态分布,所以有时会在写条件的最佳化时选择不适当的设定。

[0172]

在第4实施方式中,rdc(rdc18c)构成为,记录按每个扇区取得的指标的最大值和最小值,以使得能够判断每个扇区的错误比特数的变动是否成为正态分布。

[0173]

此外,第4实施方式的磁盘装置1在具备rdc18c来替代rdc18这一点上与第1实施方式不同。在以后的第4实施方式的说明中,对与第1实施方式相同的构成要素标注与第1实施方式相同的名称及标号,并省略详细的说明。

[0174]

图13是示出第4实施方式涉及的rdc18c的详细的构成的一个例子的示意图。rdc18c具备a/d转换电路108、fir滤波器100、维特比解码器101、迭代解码器102、解码控制电路103、维特比参数控制电路104、次数判定电路105、取得电路106c、指标存储电路107c-1、最大值存储电路107c-2以及最小值存储电路107c-3。

[0175]

此外,取得电路106c是取得电路的又一个例子。指标存储电路107c-1、最大值存储电路107c-2以及最小值存储电路107c-3是存储电路的又一个例子。

[0176]

指标存储电路107c-1、最大值存储电路107c-2以及最小值存储电路107c-3由小规模的存储器、寄存器构成。

[0177]

取得电路106c在解码的执行次数与第1值相等的情况下,取得表示读写质量的指标,并将所取得的指标保存于指标存储电路107c-1。指标既可以是错误比特数,也可以是奇偶违规数。此外,取得电路106c取得指标并将其保存于指标存储电路107c-1的处理与第1实施方式的取得电路106取得指标并将其保存于指标存储电路107的处理相同。

[0178]

在第4实施方式中,进而,在对多个扇区中的每一个依次执行读出时,取得电路106c将从各自不同的扇区取得的多个指标的最大值保存于最大值存储电路107c-2,并将该多个指标的最小值保存于最小值存储电路107c-3。

[0179]

图14是示出第4实施方式涉及的磁盘装置1的读写质量的测定的动作的一个例子的流程图。

[0180]

在第4实施方式中,首先,与第1实施方式同样地,执行s201~s206的处理。在s206的处理中,在从对象的扇区读出比特数据序列时,在rdc18c中执行解码。另外,在解码时,执行维特比参数的学习和更新。另外,在解码的执行次数与第1值相等时,由取得电路106c取得指标。然后,取得电路106c将所取得的指标累积到指标存储电路107c-1(s801)。

[0181]

继s801的处理之后,取得电路106c判定通过s206的处理取得的指标是否比保存于最大值存储电路107c-2的值大(s802)。此外,在开始图14的处理的时间点,最大值存储电路107c-2以预定的足够小的值(例如0)被重置(reset)。在判定为该指标比保存于最大值存储电路107c-2的值大的情况下(s802:是),取得电路106c用通过s206的处理取得的指标来更新最大值存储电路107c-2的内容(s803)。在判定为该指标不比保存于最大值存储电路107c-2的值大的情况下(s802:否),跳过s803的处理。

[0182]

接下来,取得电路106c判定通过s206的处理取得的指标是否比保存于最小值存储电路107c-3的值小(s804)。此外,在开始图14的处理的时间点,最大值存储电路107c-2以预定的足够大的值(例如全1)被重置。在判定为该指标比保存于最小值存储电路107c-3的值小的情况下(s804:否),取得电路106c用通过s206的处理取得的指标来更新最小值存储电路107c-3的内容(s805)。在判定为该指标不比保存于最小值存储电路107c-3的值小的情况下(s804:否),跳过s805的处理。

[0183]

在s805的处理之后、或者在s804的判定处理中判定为否的情况下,执行s207的处理。

[0184]

在s207的判定处理中判定为扇区x为最终扇区的情况下(s207:是),磁盘装置1取

得累积到指标存储电路107c-1的指标、保存于最大值存储电路107c-2的值(即指标的最大值)、以及保存于最小值存储电路107c-3的值(即指标的最小值)(s806)。然后,读写质量的测定的动作结束。

[0185]

图15是示出第4实施方式涉及的磁盘装置1执行的写电流的调整的动作的详细的一个例子的流程图。

[0186]

例如,预先确定写电流能够设定的值的范围。mpu20将写电流能够设定的值的范围内的一个值设定为写电流的设定值(s901)。该处理例如与图9的s501相同。

[0187]

接下来,执行读写质量的测定(s902)。在s902中,执行图14所示的一系列的处理。但是,使用通过s901设定的写电流。

[0188]

接下来,mpu20判定是否能够在调整范围以内进一步变更写电流(s903)。该处理例如与s503同样。在判定为能够在调整范围以内进一步变更写电流的情况下(s903:是),再次执行s901的处理。

[0189]

在判定为无法在调整范围以内进一步变更写电流的情况下(s903:否),mpu20选择获得写电流能够设定的值的范围内的最优的指标(即累积得到的指标)的值来作为调整后的写电流(s904)。但是,指标的变动量,也即是指标的最大值与最小值之差成为了预定值以上的写电流的值除外。

[0190]

例如,在指标的变动构成正态分布的情况和指标的变动不构成正态分布的情况这两方中,均测定指标的变动量。在指标的变动不构成正态分布的情况下,与指标的变动构成正态分布的情况相比,有指标的变动量变大的倾向。将与指标的变动构成正态分布的情况下的变动量与指标的变动不构成正态分布的情况下的变动量的边界相当的值设定为在s904的判定处理中使用的预定值。此外,预定值的决定方法并不限定于此。

[0191]

通过s904的处理,写电流的调整的动作结束。

[0192]

如上所述,根据第4实施方式,取得电路106c按扇区取得指标,将指标的最大值保存于最大值存储电路107c-2,将指标的最小值保存于最小值存储电路107c-3。

[0193]

由此,由于能够判定写电流不足的状态,所以写条件的最佳化的精度提高。

[0194]

另外,mpu20基于指标的最大值和最小值来控制写电流。

[0195]

由于能够基于写电流是否不足来执行写电流的控制,所以写电流的最佳化的精度提高。

[0196]

对本发明的多个实施方式进行了说明,但这些实施方式是作为例子而提示出的,并非意在限定发明的范围。这些新颖的实施方式可以以其他各种各样的方式实施,在不脱离发明的要旨的范围内可以进行各种省略、替换、变更。这些实施方式及其变形包含于发明的范围、要旨中,并且包含于在权利要求书所记载的发明及与其等同的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。