1.本实用新型涉及数据处理领域,尤其涉及一种射频数据采集处理主板及装置。

背景技术:

2.目前的射频数据采集处理装置中通过多种电路板分别采集和处理数据,导致设备体积臃肿,集成度不高,同时对于高频射频数据采集和处理的数据吞吐量要求较高,现有的射频数据采集处理装置难以满足要求。

技术实现要素:

3.本实用新型要解决的技术问题就在于:针对现有技术存在的技术问题,本实用新型提供一种射频数据采集处理主板及装置,具有较高集成度并可以满足数据吞吐量的要求。

4.为解决上述技术问题,本实用新型提出的技术方案为:

5.一种射频数据采集处理主板,包括用于采集射频信号的adc模块、fpga模块、dsp模块、cpld模块、电源模块和时钟模块,所述adc模块和fpga模块的jesd204b接口连接,所述fpga模块的srio接口和dsp模块的srio接口连接,所述fpga模块的emif接口和dsp模块的emif接口连接,所述cpld模块的输出端和fpga模块、dsp模块和adc 模块的供电端分别连接,所述cpld模块的输入端和电源模块连接,所述cpld模块的控制端和dsp模块连接,所述时钟模块的输出端分别和adc模块、fpga模块连接。

6.进一步的,还包括第一缓存单元、第二缓存单元和信息存储单元,所述第一缓存单元、信息存储单元分别和fpga模块连接,所述第二缓存单元和dsp模块连接。

7.进一步的,所述第一缓存单元、第二缓存单元分别采用ddr3存储器。

8.进一步的,所述信息存储单元采用nor flash存储器。

9.进一步的,还包括第一矩形连接器,所述fpga模块、dsp模块分别设有jtag接口,所述第一矩形连接器和fpga模块、dsp模块的jtag接口连接。

10.进一步的,还包括第二矩形连接器,所述fpga模块设有rs422接口和rs232接口,所述fpga模块的rs232接口和第一矩形连接器连接,所述fpga模块的rs422接口和第二矩形连接器连接。

11.进一步的,所述dsp模块设有以太网接口,所述dsp模块的以太网接口和第二矩形连接器连接。

12.本实用新型还提出一种射频数据采集处理装置,包括至少一块射频数据采集处理主板,所述射频数据采集处理主板为任一上述的射频数据采集处理主板。

13.进一步的,还包括超宽带信号处理单元和脉内分析处理单元,所述射频数据采集处理主板中fpga模块的srio接口和超宽带信号处理单元、脉内分析处理单元分别连接。

14.进一步的,还包括gps模块,所述射频数据采集处理主板中fpga模块的gpio接口和 gps模块连接。

15.与现有技术相比,本实用新型的优点在于:

16.1.本实用新型的射频数据采集处理主板包括fpga模块和dsp模块,fpga模块对射频数据整理后发送给dsp模块进行预处理,dsp模块具有较高处理速度,同时fpga模块的 jesd204b接口连接adc模块,fpga模块的srio接口和dsp模块的srio接口连接,fpga 模块的emif接口和dsp模块的emif接口连接,通过jesd204b接口、srio接口和emif 接口进行高速数据传输满足了数据吞吐量的要求;

17.2.本实用新型的射频数据采集处理主板包括用于采集射频信号的adc模块,可直接采集射频数据并发送给fpga模块,从而实现射频数据采集处理主板直接采集射频数据;

18.3.本实用新型的射频数据采集处理主板通过时钟模块输出不同时钟信号实现高功率和低功率的切换,降低时钟模块输出时钟信号的频率即可降低功耗;

19.4.本实用新型的射频数据采集处理主板包括第一矩形连接器和第二矩形连接器,第一矩形连接器连接fpga模块、dsp模块的jtag接口,还连接fpga模块的rs232接口,第二矩形连接器连接fpga模块的rs422接口以及dsp模块的以太网接口,从而便于从外部进行射频数据采集处理主板的调试和控制。

附图说明

20.图1为本实用新型的射频数据采集处理主板的系统框图。

21.图2为本实用新型的射频数据采集处理主板的时钟框图。

22.图3为本实用新型的射频数据采集处理主板的供电示意图。

23.图4为本实用新型的射频数据采集处理装置的系统框图。

24.图例说明:1

‑

adc模块、2

‑

fpga模块、3

‑

dsp模块、4

‑

cpld模块、5

‑

电源模块、6

‑

时钟模块、7

‑

第一缓存单元、8

‑

第二缓存单元、9

‑

信息存储单元、101

‑

第一矩形连接器、102

‑

第二矩形连接器。

具体实施方式

25.以下结合说明书附图和具体优选的实施例对本实用新型作进一步描述,但并不因此而限制本实用新型的保护范围。

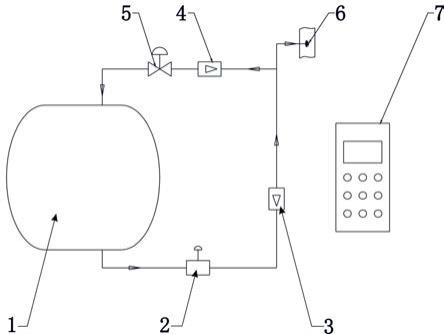

26.如图1所示,本实用新型提出一种射频数据采集处理主板,包括用于采集射频信号的adc 模块1、fpga模块2、dsp模块3、cpld模块4、电源模块5和时钟模块6,adc模块1 和fpga模块2的jesd204b接口连接,fpga模块2的srio接口和dsp模块3的srio 接口连接,fpga模块2的emif接口和dsp模块3的emif接口连接,cpld模块4的控制端和dsp模块3连接(为使示意图清晰,图中省略连接线),如图3所示,cpld模块4 的输出端和fpga模块2、dsp模块3和adc模块1的供电端分别连接,cpld模块4的输入端和电源模块5连接,如图1和图2所示,时钟模块6的输出端分别和adc模块1、fpga 模块2连接,时钟模块6使得每个adc模块1具备同一时钟源,保证了时钟的同频同源。

27.本实施例中,adc模块1为4个,每个adc模块1分别采集2g~18g的射频数据后发送给fpga模块2,fpga模块2对射频数据整理后发送给dsp模块3进行预处理,实现对于射频数据的采集和处理,fpga模块2的jesd204b接口连接adc模块1,jesd204b接口具备8通道,是一种高速adc/dac数据传输接口,同时fpga模块2的srio接口和dsp 模块3的srio接口连接,

fpga模块2的rs422接口和第二矩形连接器102连接,外部控制信号可通过第一矩形连接器101和第二矩形连接器102输入fpga模块2。

35.如图1所示,本实施例的dsp模块3设有以太网接口,dsp模块3的以太网接口和第二矩形连接器102连接,因此外部向第二矩形连接器102发送关闭电源的通知时,fpga模块2 通过rs422接口接受到关闭电源的通知并转发给dsp模块3,或者dsp模块3通过以太网接口接受到关闭电源的通知,之后dsp模块3控制cpld模块4关闭fpga模块2和dsp模块3的电源,从而降低功耗,达到休眠的状态。

36.如图3所示,本实施例中还提出一种射频数据采集处理装置,包括至少一块射频数据采集处理主板,射频数据采集处理主板为任一上述的射频数据采集处理主板。

37.如图3所示,本实施例的射频数据采集处理装置还包括超宽带信号处理单元和脉内分析处理单元,射频数据采集处理主板中fpga模块2的srio接口和超宽带信号处理单元、脉内分析处理单元分别连接。本实施例中,fpga模块2通过4路srio

×

4接口和脉内分析处理单元连接,4路srio

×

4接口的传输速率达到6.25gbps,为数据传输提供了足够大的带宽。

38.本实施例中,超宽带信号处理单元用于进行中频信号高速采集、数字信道化处理,实现载频(rf)、幅度(pa)、脉宽(pw)、到达时刻(toa)、方位角(az)等参数测量,形成脉冲描述字(pdw)进行分选处理,实现超宽带雷达信号监测,然后将信号传送给脉内分析处理单元;脉内分析处理单元用于对超宽带信号处理单元传过来的信号进行时域、频域、时频域分析处理,计算信号的参数,包括脉冲信号调制方式检测、频率和幅值计算等功能,实现脉内分析功能。

39.如图3所示,本实施例的射频数据采集处理装置还包括gps模块,射频数据采集处理主板中fpga模块2的gpio接口和gps模块连接,gps模块接受gps信号作为外部时统信号, fpga模块2从gps模块获取外部时统信号,从而实现与外部时钟同步。

40.为实现国产化的要求,降低生产成本,本实施例中:

41.adc模块1采用天光半导体的cx9208bn芯片;

42.fpga模块2采用复旦微电子的smq7vx690tffg1927芯片;

43.dsp模块3采用国防科大的ft

‑

m6678n芯片;

44.cpld模块4采用成都华微科技的hw240t

‑

lqfp100芯片;

45.第一缓存单元6、第二缓存单元7采用紫光国芯的hxi15h4g160af

‑

13k芯片;

46.第一矩形连接器101采用中航光电的j30j

‑

21tjwp7

‑

j连接器,第二矩形连接器102采用中航光电的j30j

‑

21zkwp7

‑

j连接器。

47.通过上述结构,本实施例的射频数据采集处理主板及装置可以直接处理原始射频数据,电源和复位可控,可满足多种用途需求,同时与外部时钟同步实现时钟可调,从而满足多种信号速率要求。

48.上述只是本实用新型的较佳实施例,并非对本实用新型作任何形式上的限制。虽然本实用新型已以较佳实施例揭露如上,然而并非用以限定本实用新型。因此,凡是未脱离本实用新型技术方案的内容,依据本实用新型技术实质对以上实施例所做的任何简单修改、等同变化及修饰,均应落在本实用新型技术方案保护的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。