1.本实用新型涉及频率电压转换装置,尤其涉及一种高速稳定的宽频带频率电压转换装置。

背景技术:

2.无线通信以及电气自动化行业中常用到频率和电压的转化,把频率的周期信号转换成模拟电压更加利于信号的后一级处理。

3.公开号cn107315440a的中国专利公开了一种高速宽频带频率电压转换电路,该电路通过输入信号的连续两个上升沿对mos管进行开关,继而对电容c进行充电,这样,其开关的时间长短决定了电容的充电时长,继而导致在不同频率时经过电容积分的两端电压值呈现出差异;由于电容充电电流的非线性,相应的,频率与电压的关系也呈现出非线性,同时因为mos管的响应速度相对较慢,对于高频信号分辨能力较差,频率与电压的对应斜率较小,不能保证频率电压转换精度。

4.adi公司也推出过专门的用于频率电压转换的芯片,只需要搭建简单的外部电路就可以实现功能,方便工程师进行开发,中北大学发表的学术文章《一种频率/电压转换电路的设计》基于的就是这种方法。该方法通过比较器将输入信号转换成数字信号,输入ad650频率电压转换芯片,该芯片输出的即为对应频率的电压。但受限于芯片的性能,无法实现对频率为1mhz以上信号的分辨;此外,由于芯片温漂的存在,即使在频率量程内也无法实现高精度的转换。

5.公开号cn 202998070 u的中国专利公开了一种数字型频率电压转换电路,该电路采用数字式的鉴频方法,通过单片机对输入频率进行计数,采用“时间/周期”测频法对信号的频率进行精确测量,将该测量结果经处理后增加对应比例,再由数字模拟转换器输出对应电压。该专利描述的方法对于低频信号有较好的分辨能力,且电压与频率的对应关系为线性,但受限于单片机的性能,对于高频段的信号不能准确分析,即其不能实现“宽频带”的频率电压转换。

6.此外,上述的频率电压转换方法普遍采用单片机的系统时钟对输入的数字信号进行计数,受限于奈奎斯特采样定律,当输入信号接近系统时钟的二分之一时,计数将失效。所以只能在0.5hz~20khz频率段工作。同时单片机的电平逻辑比较固定,当输入信号的幅度较小时无法触发对应的门电路,继而使得处理器对输入信号产生误判。

技术实现要素:

7.为了解决上述技术问题,本实用新型的目的是提供一种高速稳定的宽频带频率电压转换装置,该装置可实现高速、稳定、精确的宽频带频率电压转换。

8.基于上述目的,本实用新型提供一种宽频带频率电压转换装置,该装置包括控制部件、混频部件、频率信号转换部件、分频部件、通信部件、计数部件及电压输出部件,其中,所述混频部件、频率信号转换部件、分频部件、通信部件、计数部件及电压输出部件均与所

述控制部件连接,所述混频部件、频率信号转换部件、分频部件及计数部件顺次连接;

9.所述混频部件,包括混频器和频率发生模块,所述混频器的第一输入端通过第一射频开关与装置输入端连接,混频器的输出端通过第二射频开关与频率信号转换部件连接;所述频率发生模块的输入端与控制部件连接,频率发生模块的输出端与混频器的第二输入端连接。

10.作为优选,该装置还包括与控制部件连接的通信部件,该通信部件还与上位机电性连接。

11.作为优选,所述计数部件的计数频率为150mhz。

12.作为优选,所述混频部件还包括低通滤波模块,该低通滤波模块连接于混频器的输出端与第二射频开关之间。

13.作为优选,所述频率信号转换部件包括高速比较器。

14.作为优选,所述分频部件包括分频器。

15.作为优选,所述分频器的分频倍数为16

‑

256倍。

16.作为优选,该装置还包括缓冲器,该缓冲器连接于控制部件与电压输出部件之间。

17.作为优选,计数部件、通信部件及控制部件均集成于fpga上。

18.作为优选,所述电压输出部件包括dac8552模块,该模块中还集成有稳压芯片7805af、78m06及电压芯片ref195电压源芯片。

19.作为优选,所述频率发生模块的频率输出范围为20mhz

‑

6ghz。

20.与现有技术相比,本实用新型的有益效果为:

21.该装置具有混频部件及分频部件,可实现对高频信号的连续降频,同时其内部时钟设定有150mhz的高密度计数频率,可实现高速的宽频带的频率电压转换;此外,通过频率信号转换部件将模拟的输入信号转换为数字信号,不仅增加了装置的抗干扰性能,亦进一步加快了频率电压转换速度。

附图说明

22.构成本技术的一部分的说明书附图用来提供对本技术的进一步理解,本技术的示意性实施例及其说明用于解释本技术,并不构成对本技术的限定。

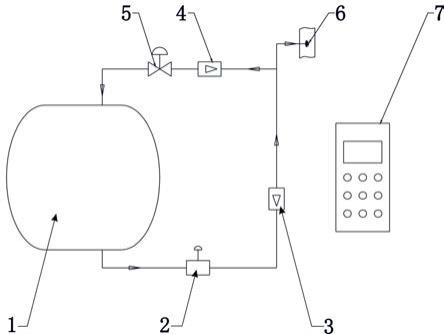

23.图1是频率电压转换装置的结构框图;

24.图2是本实用新型实施例中高速比较器及分频器部分的电路结构图。

具体实施方式

25.下面结合附图与实施例对本实用新型作进一步说明。

26.应该指出,以下详细说明都是示例性的,旨在对本技术提供进一步的说明。除非另有指明,本文使用的所有技术和科学术语具有与本技术所属技术领域的普通技术人员通常理解的相同含义。

27.需要注意的是,这里所使用的术语仅是为了描述具体实施方式,而非意图限制根据本技术的示例性实施方式。如在这里所使用的,除非上下文另外明确指出,否则单数形式也意图包括复数形式,此外,还应当理解的是,当在本说明书中使用术语“包含”和/或“包括”时,其指明存在特征、步骤、操作、器件、组件和/或它们的组合。

28.基于背景技术中的问题及本实用新型的技术方案,本实施例提供一种宽频带频率电压转换装置,如图1所示,该装置包括控制部件、混频部件、频率信号转换部件、分频部件、通信部件、计数部件及电压输出部件,其中,所述混频部件、频率信号转换部件、分频部件、通信部件、计数部件及电压输出部件均与所述控制部件连接,所述混频部件、频率信号转换部件、分频部件及计数部件顺次连接;

29.所述混频部件,包括混频器和频率发生模块,所述混频器的第一输入端通过第一射频开关与装置输入端连接,混频器的输出端通过第二射频开关与频率信号转换部件连接;所述频率发生模块的输入端与控制部件连接,频率发生模块的输出端与混频器的第二输入端连接。

30.作为一种较优的实施方案,所述频率发生模块的频率输出范围为20mhz

‑

6ghz。

31.作为一种较优的实施方案,该装置还包括与控制部件连接的通信部件,该通信部件还与上位机电性连接。

32.作为一种较优的实施方案,所述计数部件的计数频率为150mhz,其采用锁相环电路对内部时钟信号进行倍频实现,优选地,将50mhz的温补晶振倍频至150mhz。150mhz计数频率的产生方法采用fpga模块编辑实现,即在fpga的逻辑电路内部通过硬件描述语言(hdl)实现锁相环电路,由于锁相环的存在,150mhz的信号依旧具有非常好的精准性。优选地,fpga芯片选用cycloneⅳ的ep4ce6f17c8n,其内还集成有sdram存储器,具体的,该sdram存储器为w9812g6kh

‑

6,用于存储上位机发送过来的参数。此外,epcs16为fpga的固件存储芯片,用于存储正常工作所需要的流程代码;50m晶振用于为fpga芯片提供参考时钟,同时也是内部锁相环的参考时钟。此外,为了实现在宽频段的精确测量,需要更改高频本征信号的频率以匹配不同的频率段,在fpga内部编写了异步通信模块(uart协议),通过与上位机通信或于控制部件内预存计算方法实现对本征信号的频率控制,控制范围为20mhz~6ghz。

33.作为一种较优的实施方案,所述混频部件还包括低通滤波模块,该低通滤波模块连接于混频器的输出端与第二射频开关之间。

34.作为一种较优的实施方案,所述频率信号转换部件包括高速比较器,如图2所示,高速比较器模块优选包括max9601芯片;pin为输入,在本实施例中,pin应为频率为0~2ghz的正弦信号。高速比较器的作用是将高频的正弦信号转换成数字信号,即将连续的模拟信号转换成离散的数字信号。使用高速比较器可增加频率测量的准确性及抗干扰性。

35.作为一种较优的实施方案,所述分频部件包括分频器,优选地,如图2所示,所述分频器包括mc100e137、mch100el34和mc100el57等芯片,分频器的电平逻辑为ecl电平,分频倍数通过s1和s0进行组合切换,范围为16倍分频至256倍分频;即分频器的作用是将输入的数字信号进行整数倍分频,以满足计数器的计数范围。其中,还包括mc100elt21电平转换芯片,其作用是将ecl电平转换成ttl电平,即最终的输出信号fre为ttl电平逻辑。另外,r10、r14、r12为分压电阻,分得的high电压和low电压用于确定高速比较器的工作模式,r2、r7、r8、r4为偏置电阻,用于确定ecl的偏置电压。采用ecl电平提升转换速度的同时,有效避免由于期间温漂原因导致的转换不稳定情况,增加抗干扰能力。

36.作为一种较优的实施方案,该装置还包括缓冲器,该缓冲器连接于控制部件与电压输出部件之间。

37.作为一种较优的实施方案,计数部件、通信部件及控制部件均集成于fpga上,fpga

模块使用现场可编程逻辑电路实现,该模块由50mhz的温补晶振驱动,通过硬件描述语言(hdl),在逻辑电路内部实现了锁相环电路,频率计数电路和数字通信电路。锁相环电路将输入的50mhz参考信号倍频至150mhz作为频率计数的基准信号,由于锁相环的存在,150mhz的信号依旧具有非常好的精准性。采用频率超过输入信号4倍的基准信号,保证了频率计数的准确性。通信模块用于接受由上位机(电脑)的参数指令,通过异步通信协议实现。控制单元一方面接受由通信单元传递的参数指令,另一方面控制两个射频开关实现频率切换,控制频率发生模块以产生特定的本征信号,控制数字模拟转换芯片(dac),将计数器计得的频率数增加相应权重后输出至dac。

38.作为一种较优的实施方案,所述电压输出部件包括dac8552模块,该模块中还集成有稳压芯片7805af、78m06及电压芯片ref195电压源芯片。

39.其实施流程为:

40.对输入信号进行鉴频(这里对“鉴频”进行详细说明:由于输入信号的期望频率是已知的,因此其实际频率可进行估值,该估值可由相关的控制器实时计算获得,亦可由人工预先设定并预存入相关控制系统中,该估值并获得结果的过程即为鉴频。),当输入信号的频率不小于阈值f

thr

时,则第一射频开关的输出端切换至与混频器的第一输入端连通,同时,第二射频开关的输入端与混频器的输出端连通,这样,输入的频率f经混频器降频处理后自第二射频开关输出;当输入信号频率小于阈值f

thr

时,则第一射频开关的输出端切换至与第二射频开关联通,混频器被短路,输入信号直接自第二射频开关输出。以阈值f

thr

为2ghz为例,对于频率为2ghz以上的信号,则通过第一射频开关1(射频开关1)切换至混频器,通过滤波器之后继而通过第二射频开关2(射频开关2),此时的频率信号频率与频率发生模块的发出的本征信号混频至2ghz以下;

41.频率信号转换部件将输出的信号转换为数字信号;

42.分频器对该数字信号进行分频,使该数字信号的频率降至计数频率的1/2以下;

43.计数部件对该分频后的数字频率进行计数;

44.控制部件根据计数结果确定输入信号的精度频率值。该装置可实现对0

‑

8ghz范围内的频率计数。

45.此外,需要说明,混频器是输出信号频率等于两输入信号频率之和、差或为两者其他组合的电路,实质上相当于频谱搬移的作用,可以将高频信号搬移至低频段,这样,通过混频器拓宽了频率电压转换范围。

46.尽管上面已经示出和描述了本实用新型的实施例,可以理解的是,上述实施例是示例性的,不能理解为对本实用新型的限制,本领域的普通技术人员在不脱离本实用新型的原理和宗旨的情况下在本实用新型的范围内可以对上述实施例进行变化、修改、替换和变型,凡是依据本实用新型的技术实质对以上实施例所作的任何简单修改、等同变化与修饰,均仍属于本实用新型技术方案的范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。