高纵横比电镀结构以及各向异性电镀工艺

1.对相关申请的交叉引用

2.本技术要求于2019年11月22日提交的第16/693,169号美国专利申请的优先权,并且进一步要求于2018年11月26日提交的第62/771,442号美国临时申请的权益,于此通过引用并入了每个申请的全部内容。

技术领域

3.本发明大体涉及电镀结构以及电镀工艺。

背景技术:

4.用于制造诸如铜或铜合金电路结构(诸如引线、迹线和过孔互连)的结构的电镀工艺一般是已知的并且例如在castellani等的名称为“fine

‑

line circuit fabrication and photoresist application therefor”的美国专利4,315,985中公开。这些类型的工艺例如与以下专利中公开的盘驱动器头悬架的制造结合使用:bennin等的名称为“low resistance ground joints for dual stage actuation disk drive suspensions”的美国专利8,885,299;rice等的名称为“integrated lead suspension with multiple trace configurations”的美国专利8,169,746;hentges等的名称为“multi

‑

layer ground plane structures for integrated lead suspensions”的美国专利8,144,430;hentges等的名称为“multi

‑

layer ground plane structures for integrated lead suspensions”的美国专利7,929,252;swanson等的名称为“method for making noble metal conductive leads for suspension assemblies”的美国专利7,388,733;以及peltoma等的名称为“plated ground features for integrated lead suspensions”的美国专利7,384,531。这些类型的工艺也与相机镜头悬架的制造结合使用,例如在miller的名称为“camera lens suspension with polymer bearings”的美国专利9,366,879中所公开的。

5.超级填充和超级共形镀覆工艺和组成也是已知的并且公开于,例如,下面的文章中:vereecken等的“the chemistry of additives in damascene copper plating”,ibm j.of res.&dev.,vol.49,no.1,2005年1月;andricacos等的“damascene copper electroplating for chip interconnections”,ibm j.of res.&dev.,vol.42,no.5,1998年9月;以及moffat等的“curvature enhanced adsorbate coverage mechanism for bottom

‑

up superfilling and bump control in damascene processing”,electrochimica acta 53,pp.145

‑

154,2007。通过这些工艺,沟槽内电镀(例如,光致抗蚀剂掩膜沟槽限定用于待电镀的结构的空间)优先发生在底部。由此可以避免沉积结构中的空隙。通过引用所有上述专利和文章的整体而将它们并入本文并用于所有目的。

6.仍然存在对增强的电路结构的持续需求。也存在对用于制造电路和其他结构的高效和有效的工艺,包括电镀工艺,的需求。

技术实现要素:

7.描述了包括高纵横比电镀结构的装置和形成高纵横比电镀结构的方法。一种制造金属结构的方法,包括:提供具有金属基部的基底,所述金属基部的特征在于高度与宽度纵横比;以及在所述基部上电镀金属冠以形成所述金属结构,所述金属结构的高度与宽度纵横比大于所述基部的纵横比。

8.根据附图和下面的详细描述,本发明的实施例的其他特征和优点将是显而易见的。

附图说明

9.通过示例而非限制的方式,在附图的图中图示出了本发明的实施例,其中相同的附图标记指示类似的元件,并且其中:

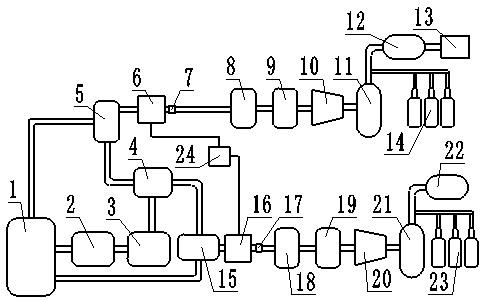

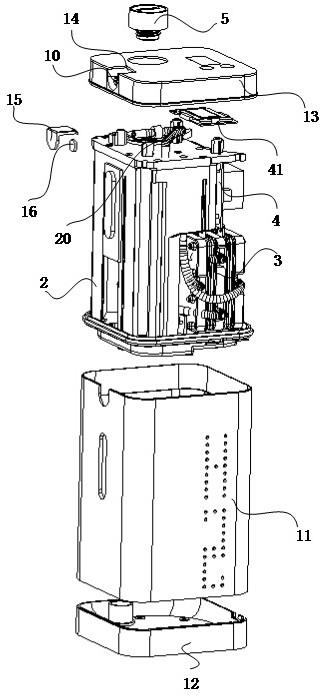

10.图1图示出使用当前印刷电路技术制造的线圈;

11.图2图示出包括根据实施例的高纵横比电镀结构的高密度精密线圈;

12.图3图示出用于表示由包括根据实施例的高纵横比电镀结构的高密度精密线圈所生成的电磁力的图示;

13.图4图示出被配置用于线性马达类型的应用的包括根据实施例的高纵横比电镀结构的多个层的装置;

14.图5图示出根据一些实施例的高纵横比电镀结构;

15.图6图示出根据一些实施例的高纵横比电镀结构;

16.图7图示出根据一些实施例的高纵横比电镀结构;

17.图8图示出具有根据一些实施例的高纵横比电镀结构的多个层的装置,其具有高密度横截面面积;

18.图9图示出在根据实施例的高电流密度镀覆技术和低电流密度镀覆技术期间指示sps覆盖的曲线图;

19.图10a

‑

f图示出用于形成根据实施例的高纵横比电镀结构的工艺;

20.图11图示出根据一些实施例的高纵横比电镀结构;

21.图12图示出根据一些实施例的高纵横比电镀结构的立体图;

22.图13a、13b图示出使用根据实施例的高纵横比电镀结构形成的高密度精密线圈;

23.图14图示出根据实施例的包括高分辨率堆叠导体层的高纵横比电镀结构;

24.图15图示出包括根据实施例的高纵横比电镀结构的高密度精密线圈;

25.图16a

‑

c图示出用于形成根据另一实施例的高纵横比电镀结构的工艺;

26.图17图示出根据实施例的高纵横比电镀结构的选择性形成;

27.图18图示出形成有选择性形成于迹线上的金属冠部分的根据实施例的高纵横比电镀结构的立体图;

28.图19图示出硬驱动盘悬架弯曲部,其包括根据实施例的高纵横比电镀结构;

29.图20图示出图19所示的硬盘驱动器悬架弯曲部的横截面视图;

30.图21a、21b图示出用于在共形镀覆工艺期间使用光致抗蚀剂形成根据实施例的高纵横比电镀结构的工艺;

31.图22图示出根据各种实施例的用于形成初始金属层的工艺、标准/共形镀覆工艺、

以及冠镀覆工艺的示例性化学过程;

32.图23图示出由根据实施例的高纵横比电镀结构形成的感应耦合线圈的顶表面的立体图;

33.图24图示出图21所示的感应耦合线圈的实施例的后表面的立体图;

34.图25图示出与射频识别芯片耦合的根据实施例的感应耦合线圈2502的顶表面的立体图;

35.图26a

‑

j图示出形成由根据实施例的高纵横比电镀结构形成的感应耦合线圈的方法;

36.图27图示出用于包括根据实施例的高纵横比电镀结构的硬盘驱动器的悬架的弯曲部的平面视图;

37.图28图示出在沿如图27所示的线a截取的间隙部分处的弯曲部的间隙部分的横截面;

38.图29图示出根据实施例的具有质量结构的万向节部分;

39.图30图示出包括根据实施例的高纵横比电镀结构的弯曲部的近端部分的沿如图27所示的线b截取的横截面;

40.图31图示出包括根据实施例的高纵横比结构的弯曲部的近端部分的沿如图27所示的线c截取的横截面;以及

41.图32图示出包括根据实施例的高纵横比结构的弯曲部的近端部分的平面视图;

42.图33图示出用于形成根据实施例的高纵横比电镀结构的工艺;

43.图34图示出类似于关于图33描述的类型的更详细的工艺;以及

44.图35图示出使用本文中所述的工艺制造的根据实施例的线圈。

具体实施方式

45.以下描述了根据本发明的实施例的高纵横比电镀结构和制造方法。高纵横比电镀结构提供比当前技术更紧密的导体间距。例如,根据各种实施例,高纵横比电镀结构包括导体堆叠,其中导体堆叠的横截面面积大于50%。此外,高纵横比电镀结构使得实现根据实施例的多层导体成为可能。此外,根据各种实施例,高纵横比电镀结构使得能够在层与层之间实现精密对准(对齐)。例如,高纵横比电镀结构可以在层与层之间具有小于0.030mm的对准。根据各种实施例,高纵横比电镀结构使得能够降低总的堆叠高度。

46.根据各种实施例,高纵横比电镀结构使得能够在磁体和使用高纵横比电镀结构形成的线圈之间实现薄的电介质材料。这使得线圈能够产生比当前印刷电路线圈(诸如图1所示的那些)更强的电磁场。因此,与当前技术相比,高纵横比电镀结构更具有成本效益,产生更高性能的装置,并且减少了装置的所需占用面积(footprint)。

47.图2图示出了包括根据实施例的高纵横比电镀结构的高密度精密线圈。高纵横比电镀结构202成行地形成,在每行和每个高纵横比电镀结构204之间具有电介质材料。高密度精密线圈可以形成为螺旋线圈或其他线圈类型。

48.图3图示出了用于表示由包括根据实施例的高纵横比电镀结构的高密度精密线圈所生成的电磁力的图示。该图示包括在磁体304附近的线圈横截面302。最高电磁力306在较靠近磁体304的线圈层308中。较远离磁体304的线圈层310施加较小的力。影响力的主要因

素来自洛伦兹方程:因为的大小的强度随着线圈和磁体之间的距离而减小,所以是流过铜的电流。横截面302的不作为导体的任何横截面面积对力没有贡献。

49.影响线圈的力能力的主要因素包括磁场内的匝数(最靠近磁体的磁极的匝提供了最大的力)、线圈到磁体的距离(较靠近磁体的层将施加更大的力)、以及磁场内的铜横截面面积的总百分比。与使用当前线圈技术的线圈相比,根据各种实施例的高纵横比电镀结构的使用改善了这些方面。

50.例如,具有使用当前技术的两层的线圈具有大约210微米的总厚度、38微米的导体间距、大约20%的铜的横截面百分比、3.1欧姆的估计电阻、1.0的估计力比(1.0的估计b比和1.0的估计j比)、以及1.0的估计功率比。相比之下,根据各种实施例,包括高纵横比电镀结构的高密度精密线圈具有大约116微米的总厚度、40微米的导体间距、大约60%的铜的横截面百分比、5.5欧姆的估计电阻、1.2的估计力比(1.5的估计b比和0.8的估计j比)、以及0.71的估计功率比。因此,根据各种实施例,包括高纵横比电镀结构的高密度精密线圈是更高性能的装置。因此,根据一些实施例,这样的高密度精密线圈以使用当前现有技术水平的线圈的一半的厚度提供了大20%的力和小30%的功率。

51.图4图示出了被配置用于线性马达类型的应用的包括根据实施例的高纵横比电镀结构的多个层的装置。由于相比于当前技术的尺寸优势,高纵横比电镀结构的每个层402a

‑

d比当前技术(诸如图1所示)更可能较接近磁体404。此外,每个层402a

‑

d更接近于磁体404通过利用体积场(磁通密度)而改善了线性马达的力能力。因此,将多层高纵横比电镀结构用于线性马达将比使用当前技术的结构需要更少的层。此外,这样的结构在获得比如低电阻的电特性方面提供了更大的灵活性。

52.图5图示出了根据一些实施例的在制造工艺期间的阶段的高纵横比电镀结构。在制造工艺期间的这个阶段的高纵横比电镀结构的层602是使用半添材技术形成的,以创建具有大约1比1的初始高度与宽度纵横比(a/b)的精细间距、抗蚀剂限定的导体。例如,高纵横比电镀结构可以具有20微米的高度和20微米的宽度。根据一些实施例,这时停止镀覆工艺以使用包括本领域已知的那些的技术去除籽晶层(种子层)和诸如光致抗蚀剂掩膜的限定工件。

53.图6图示出了根据一些实施例的在制造工艺期间的另一阶段的高纵横比电镀结构。在制造工艺期间的这个阶段的高纵横比电镀结构的层702是使用冠镀覆技术(crown plate technology)形成的,以将半添材导体转换成高纵横比、高百分比金属导体电路。例如,高纵横比电镀结构具有大于1比1的最终高度与宽度比(a/s)。根据各种实施例,最终高度与宽度比可以在包括1.2至3.0的范围中。其他实施例包括大于3.0的最终高度与宽度比。然而,本领域技术人员将理解,可以使用本文中所述的技术获得任何最终高度与宽度比以满足设计和性能标准。在从如图5所示的前一阶段形成的如图6所示的形成阶段,对如各种实施例中所公开的高纵横比电镀结构的最终高度没有特别限制。

54.图7图示出了根据一些实施例的在制造工艺期间的又另一阶段的高纵横比电镀结构。在制造工艺期间的这个阶段的高纵横比电镀结构的层802a、b是使用平面化技术转换形成的,以允许使用半添材技术堆叠多层高纵横比电镀结构来形成后续层。图8图示出了根据一些实施例的具有多层高纵横比电镀结构的装置,其具有高分数的导体横截面面积901。

55.用于从诸如图5中所示的那些结构形成高纵横比电镀结构的方法包括使用低电流密度镀覆技术。该镀覆技术镀覆侧壁,直到在高纵横比电镀结构之间获得期望的空间。对于各种实施例,如果高纵横比电镀结构之间的空间不是足够窄,则可能发生顶部的不希望的挤压。挤压发生在相邻结构的顶部边缘一起生长并夹断间隙的地方,这导致短路。对于各种实施例,通过足够的流体交换来增强低电流密度镀覆工艺,以使得新鲜的镀覆镀液连续地可用于发生铜镀覆的表面。此外,用于形成高纵横比电镀结构的方法包括使用高电流密度镀覆技术。这种高电流密度镀覆技术在质量传递极限的高百分比下运行。这主要或仅镀覆到形成高纵横比电镀结构的导电材料的顶部上。通过精确的电流密度控制增强了高电流密度镀覆工艺。图9图示出了具有较上线1002和较下线1004的曲线图,较上线1002指示根据实施例的高电流密度镀覆技术期间的高sps覆盖,并且较下线1004指示根据实施例的在低电流密度镀覆技术期间的低的、非常均匀的催化剂(促进剂)覆盖。

56.图10a

‑

f图示出了用于形成根据实施例的高纵横比电镀结构的工艺。图10a图示出了在工艺的时间t1处以抗蚀剂能力(抗蚀能力)的厚度极限形成的迹线1102。对于一些实施例,使用诸如镶嵌工艺的工艺,或使用包括本领域已知的那些的蚀刻和沉积技术,由铜形成预镀覆传统迹线。图10b图示出了在低电流密度或共形镀覆工艺期间在时间t2处高纵横比电镀结构的形成。根据实施例,共形镀覆工艺以大致相同的速率生长迹线的所有表面。此外,共形镀覆工艺抑制镀覆动力学(低催化剂覆盖)。共形镀覆工艺还提供相当均匀的金属浓度,其具有高的、均匀的抑制剂覆盖以进行补偿。通过在镀覆镀液中包含整平剂可以增强这种抑制镀覆动力学的效果。获得均匀的金属浓度并获得高的、均匀的抑制剂覆盖需要较低的电流密度。根据一些实施例,使用每平方分米2安培的共形镀覆工艺用于镀覆,诸如铜,光亮剂添加剂,镀覆器的温度和流体力学。这样的共形镀覆工艺的示例包括但不限于低电流密度镀覆工艺。在低电流密度下,镀覆镀液维持均匀抑制的状态,以提供共形镀覆。对于另一实施例,可以在镀覆镀液中添加整平剂以提供较高的电流密度和较快的镀覆。对于又另一实施例,可以使用将铜含量增加至接近镀覆镀液中的硫酸铜的溶解度极限来进一步增大电流密度。这提供了使电流密度加倍或甚至更大以实现相同共形镀覆质量的能力。例如,铜含量可高达40克/升,其具有降低的酸含量,以防止常见的离子效应。

57.对于一些实施例,低电流密度镀覆工艺将导电材料(诸如铜)沉积到迹线1102的顶部和侧壁上,例如,t2在低电流密度镀覆工艺期间进入该工艺大约五分钟(t1 5分钟)。图10c图示出了在低电流密度镀覆工艺期间在进入工艺的时间t3处的高纵横比电镀结构的形成。对于实施例,低电流密度镀覆工艺将导电材料(诸如铜)沉积到迹线1102的顶部和侧壁上,例如,t3在低电流密度镀覆工艺期间进入该工艺大约五分钟(t1 15分钟)。

58.图10d图示出了在冠镀覆工艺期间进入工艺的时间t4处的高纵横比电镀结构的形成,冠镀覆工艺诸如是高电流各向异性超镀覆工艺。例如,t4进入工艺大约15分10秒(t1 15分10秒)。对于一些实施例,高电流各向异性超镀覆工艺是冠镀覆。冠镀覆基于平衡以下因素之间的相互作用:溶液中的金属浓度;光亮剂添加剂;抑制剂添加剂;到表面的质量传递

‑

流体交换速率;整平剂;以及基底处的电流密度。溶液中的金属浓度可以包括但不限于铜。光亮剂添加剂可以包括但不限于sps(双(3

‑

磺丙基)

‑

二硫化物)、dps(3

‑

n,n

‑

二甲基氨基二硫代氨基甲酰基

‑1‑

丙磺酸)和mps(巯基丙基磺酸)。抑制剂添加剂可以包括但不限于各种分子量的直peg(包括本领域技术人员已知的那些)、泊洛沙胺、聚乙烯和聚丙二醇的共嵌段

聚合物,诸如以各种商业名称已知的水溶性泊洛沙姆,诸如巴斯夫聚丙二醇与环氧乙烷的加聚物(basf pluronic)f127,以及诸如ucon系列高性能流体的无规共聚物(再次以各种比例的单体和各种分子量)、各种分子量的聚乙烯吡咯烷酮。

59.根据一些实施例,高电流各向异性超镀覆工艺包括为加速电流的1%的受抑制交换电流。此外,形成的高纵横比电镀结构的侧壁具有几乎为零的催化剂覆盖。几乎为零的催化剂覆盖是通过移位用于铜沉积的能斯特(nernst)电位以有助于抑制剂覆盖来实现的。此外,高过电位和铜可用性(传输现象)导致在形成的结构顶部的高催化剂覆盖。还可以调节铜混合浓缩物(copper bulk concentrate)以在该工艺期间支持几乎为零的催化剂覆盖。例如,用于高电流各向异性超镀覆工艺的铜混合浓缩物为14克/升或更低。对于一些实施例,铜混合浓缩物取决于具体的流体力学。因为该工艺的各种实施例在质量传递极限的高分数下运行,所以跨待镀覆物品的流体速度的小差异将影响质量传递极限,实现对镀覆线之间的间隙的充分控制而没有对跨待镀覆物品的所有区域的流体速度的高度控制是困难的。根据一些实施例,高电流各向异性超镀覆工艺包括整平剂添加剂以使催化剂覆盖失效,从而最小化或消除正在形成的结构的侧壁上的镀覆。对于其他实施例,使用镀覆镀液,而无整平剂添加剂。

60.根据一些实施例,在升高的电流密度(诸如在高电流各向异性超镀覆工艺中使用的那些)下,三重反馈机制起作用。质量传递效应耗尽了迹线之间空间中的铜。此外,高电流密度支持催化剂(例如,sps)主导的表面。为了维持受抑制的侧壁,通过铜质量传递效应来调节质量传递以降低能斯特电位。例如,流体边界层厚度和每条迹线之间的间隔被设计成降低能斯特电位。

61.此外,根据一些实施例,高电流各向异性超镀覆工艺包括以一定铜浓度操作,在该铜浓度下,这些差异可以创建大于四倍的浓度差异。在这样的条件下,较低的铜浓度和能斯特电位有助于降低镀覆速率。例如,当能斯特电位大约在50毫伏(“mv”)至60mv的范围中移位时,这可能有助于镀覆速率的20倍的降低。这样的条件诱发tafel动力学,对于铜镀覆而言,其是对于施加电压(不是整流器电压)的每120mv的改变,电流的十倍的改变。较低的侧壁电流反馈到正形成的结构的顶表面,其中扩散长度短,这促进金属从镀覆镀液(溶液)到表面的较快输送和较高的催化剂覆盖而不是抑制,以及高能斯特电位。对于一些实施例,使用两添加剂系统(例如,光亮剂和抑制剂)。整平剂通过阻挡镀覆特征的顶侧上的sps动作来减少反馈机制。

62.随着金属导体或迹线之间的间隔不断缩小,金属导体之间的空间的高度与宽度的纵横比基本上增大。根据一些实施例,本文中所提供电镀工艺的方法在金属导体之间的间隔中以7:1和更大的纵横比实现镀覆。

63.根据一些实施例,形成高纵横比电镀结构的方法在选择性位置或区域提供金属冠镀覆的选择性形成。在一个示例性实施例中,通过根据以下关系进行电镀工艺来实现金属冠的选择性形成:

[0064][0065]

其中,c是发生镀覆的金属(在这种情况下是铜)的浓度,c∞是镀覆镀液中的体积

浓度。这种关系也可以表示为进行镀覆工艺,其中等于或大于质量传递极限的百分之67(67%)。根据其他实施例,通过根据以下关系进行电镀工艺来实现金属冠的选择性形成:

[0066][0067]

或者在等于或大于质量传递极限的80%的情况下。在另一方面,通过根据以下关系进行电镀工艺来实现金属冠的选择性形成:

[0068][0069]

这里i是电流密度,i

limit

是电流密度极限。

[0070]

图10e图示出了在高电流各向异性超镀覆工艺期间在时间t5处的高纵横比电镀结构的形成。例如,t5进入工艺大约15分30秒(t1 15分30秒)。对于另一实施例,如图10e所示的高纵横比电镀结构的形成发生在时间t5=t1 5分钟处。图10f图示出了在高电流各向异性超镀覆工艺期间在时间t6处的高纵横比电镀结构的形成。这图示出了冠镀覆工艺的结束,其结束了根据一些实施例的高纵横比电镀结构的形成。例如,t6进入工艺大约20分钟(t1 20分钟)。对于另一实施例,如图10f所示的高纵横比电镀结构的形成发生在时间t6=t1 10分钟处。

[0071]

对于一些实施例,用于形成高纵横比电镀结构的方法使用包括在本文中描述的共形镀覆和各向异性镀覆在内的工艺。根据一些实施例,共形镀覆工艺使用总镀覆时间的2/3。对于其他实施例,共形镀覆工艺使用总镀覆时间的1/3。此外,共形镀覆工艺对于低金属镀覆镀液以2安培/平方分米(“asd”)开始或对于高金属镀覆镀液以4asd开始。例如,镀覆镀液包括12克/升的铜和1.85摩尔(摩尔/升)的硫酸。替换地,共形镀覆工艺是以0.4至1.2微米/分钟的速率镀覆的工艺。根据实施例,共形镀覆工艺继续进行,直到迹线之间的空间在包括6

‑

8微米的范围内。随着形成的结构的表面积增加,电流密度将缓慢降低。然而,该工艺将实现所形成的所有表面的均匀电流密度和生长速率。对于一些实施例,随着形成的高纵横比结构的表面积增加,可以增加电流以维持电流密度。

[0072]

根据一些实施例,各向异性镀覆工艺使用总镀覆时间的1/3,以形成高纵横比电镀结构。各向异性镀覆工艺将asd增加到7asd(共形镀覆工艺的电流的3.5倍),但平均来说,是形成的金属结构顶部处的两倍。可以维持与共形镀覆工艺中使用的相同的流体流量。例如,镀覆速率在形成的结构的顶部为3微米/分钟,在结构的侧壁上具有几乎为零的镀覆速率。随着结构的生长,平均电流下降一半,但根据实施例,峰值电流密度在结构的顶部维持约14asd。例如,峰值电流密度刚好超过顶部表面处质量传递极限的50%,并且即使侧壁暴露于约3克/升的铜,侧壁也以小于质量传递极限的10%或5:1镀覆速率镀覆。在质量传递极限的较高分数,可以获得较高的镀覆速率比。

[0073]

用于形成高纵横比电镀结构的方法的实施例包括以上描述的那些的变型,以形成包括不同特性的高纵横比电镀结构。例如,如上所述,配置为各向异性镀液的镀覆镀液中的铜含量可以不同于13.5克/升。在使用相同电流密度的同时更改平坦迹线镀液中的铜含量可用于控制高纵横比电镀结构之间的间隔。本文中所述方法的另一实施例包括使用具有其

中铜含量为12克/升的平坦迹线镀液的平坦迹线镀液,以形成间隔开8微米的高纵横比电镀结构。本文中所述方法的又另一实施例包括使用具有其中15克/升的平坦迹线镀液的平坦迹线镀液,以形成间隔开4微米的高纵横比电镀结构。因此,本领域技术人员将理解,调整本文中所述方法的其他参数可用于改变高纵横比电镀结构的特性。本文中所述方法的一些实施例包括调整电流密度以匹配当前的镀覆条件,诸如质量传递速率、镀覆镀液中包含的金属、流体速度、铜浓度、使用的添加剂、以及温度。

[0074]

用以形成高纵横比电镀结构的方法还包括使用薄电介质工艺。根据一些实施例,光敏聚酰亚胺用作每个高纵横比电镀结构之间的电介质。液体光敏聚酰亚胺使得能够实现小的过孔能力,高纵横比导体之间的良好覆盖,良好的对准/边缘能力,是高可靠性材料,并且具有与铜紧密匹配的热膨胀系数(“cte”)。液体光敏聚酰亚胺可以容易地填充高纵横比电镀结构之间的间隙。根据一些实施例,使用液体光敏聚酰亚胺来创建低至0.030毫米的过孔通路。可以使用的其他电介质包括但不限于kmpr和su

‑

8。

[0075]

图11图示出了根据一些实施例的使用本文中所述方法形成的高纵横比电镀结构。每个高纵横比电镀结构1202包括多个纹理线1204,其示出电镀工艺如何进行以形成结构。薄电介质1206形成于高纵横比电镀结构1202之间并且设置在高纵横比电镀结构1202上。图12图示出了根据一些实施例的使用本文中所述方法形成的高纵横比电镀结构1302的立体图。

[0076]

本文中所述方法可用于形成形成高密度精密线圈的高纵横比电镀结构。图13a图示出了使用根据实施例的高纵横比电镀结构形成的高密度精密线圈。线圈1402由诸如本文中描述的那些的高纵横比电镀结构形成。高密度精密线圈还包括中心线圈过孔1404。中心线圈过孔1404在本文中描述的制造步骤期间减小跨线圈的电压降。此外,中心线圈过孔1404使得能够实现以下能力,即,通过在本文中描述的各向异性镀覆工艺期间更好地控制电压降和电流来更好地控制线圈内的间距的可变性。中心线圈过孔1404还使得能够更好地控制所形成的高密度精密线圈的电压降。图13b图示出了作为如本文中所述的高密度精密线圈的一部分的中心线圈过孔1404的横截面。

[0077]

图14图示出了根据实施例的包括高分辨率堆叠导体层的高纵横比电镀结构。第一导体层1502a包括使用包括本文中所述的那些的技术形成的高纵横比电镀结构1504。使用包括本文中所述的那些的技术、使用薄电介质工艺形成第一电介质层1508。第一电介质层1508填充第一导体层1502a的高纵横比电镀结构之间的所有空间,并在高纵横比电镀结构1504之上形成涂层。使用本领域已知的技术平面化第一电介质层1508。第二导体层1502b包括在第一电介质层1508的平面化表面之上形成的高纵横比电镀结构1506。使用包括本文中所述的那些的技术、使用薄电介质工艺形成第二电介质层1510,以填充第二导体层1502b的高纵横比电镀结构1506之间的所有空间,并且在高纵横比电镀结构1506之上形成涂层。第二电介质层1510也可以被平面化。可以使用本文中所述的技术形成包括高纵横比电镀结构的附加层。

[0078]

图15图示出了包括根据实施例的高纵横比电镀结构的高密度精密线圈,其包括高分辨率堆叠导体层。第一导体层1602a包括使用包括本文中所述的那些的技术形成的高纵横比电镀结构。使用包括本文中所述的那些的技术、使用薄电介质工艺形成第一电介质层1608。第一电介质层1608填充第一导体层1602a的高纵横比电镀结构之间的所有空间,并在

高纵横比电镀结构之上形成涂层。使用本领域已知的技术平面化第一电介质层1608。第二导体层1602b包括在第一电介质层1608的平面化表面之上形成的高纵横比电镀结构。使用包括本文中所述的那些的技术、使用薄电介质工艺形成第二电介质层1610,以填充第二导体层1602b的高纵横比电镀结构之间的所有空间,并且在高纵横比电镀结构之上形成涂层。第二电介质层1610也可以被平面化。可以使用本文中所述的技术形成包括高纵横比电镀结构的附加层。

[0079]

高密度精密线圈形成为在第一导体层1602a的高纵横比电镀结构与第二导体层1602b的高纵横比电镀结构之间具有第一距离1614。对于各种实施例,第一距离1614小于0.020毫米。对于另一实施例,第一距离1614是0.010毫米。高密度精密线圈形成为在第二电介质层1610的表面1618与第一导体层1602a的高纵横比电镀结构之间具有第二距离1616。对于各种实施例,第二距离1616小于0.010毫米。对于一些实施例,第二距离1616是0.005毫米。对于一些实施例,第二距离1616可以是起始间隙减去最终期望间隙除以2。高密度精密线圈形成为在第一导体层1602a的高纵横比电镀结构和第一电介质层1622的表面之间具有第三距离1620。对于各种实施例,第三距离1620小于0.020毫米。对于一些实施例,第三距离1620小于0.015毫米。对于另一实施例,第三距离1620是0.010毫米。对于各种实施例,使用包括本文中所述的那些的技术在基底1624上形成第一电介质层。对于一些实施例,基底1624是不锈钢层。本领域技术人员将理解,基底1624可以由其他材料形成,包括但不限于钢合金,诸如青铜的铜合金,纯铜,镍合金,铍铜合金和其他金属,包括本领域已知的那些。

[0080]

使用如本文中所述的高纵横比电镀结构形成装置的其他优点包括具有高结构强度、高可靠性、以及高热耗散能力的装置。通过在装置的所有层上形成非常致密浓度的金属高纵横比电镀结构的能力来提供高结构强度。此外,用于形成本文中所述的金属高纵横比电镀结构的工艺提供层与层之间的结构的横向对准,从而增加了高结构强度。使用用于形成本文中所述的金属高纵横比电镀结构的工艺形成的装置的高结构强度也是电介质层材料(诸如光敏聚酰亚胺层)与结构的良好粘附性的结果。对于一些实施例,使用本文中所述技术形成的高纵横比电镀结构涂覆有非磁性镍层以增加电介质层的粘附性。这将进一步增加使用本文中所述的高纵横比电镀结构形成的最终装置的高结构强度。

[0081]

使用本文中所述的高纵横比电镀结构形成的装置的可靠性也是高的,因为使用了高可靠性的材料,诸如用于电介质层的光敏聚酰亚胺,其提供了稳健的电性能。使用本文中所述的技术,提供了形成具有较少电介质材料的装置的能力并减小了所形成的装置的总厚度。因此,与使用当前工艺技术的装置相比,通过增加的热导率而增加了热耗散。

[0082]

图16a

‑

c图示出了用于形成根据另一实施例的高纵横比电镀结构的工艺。图16a图示出了使用减材蚀刻在基底1804上形成的迹线1802。根据一些实施例,在基底1804之上形成金属层。使用包括本领域已知的那些的技术在金属层之上形成光致抗蚀剂层。对于一些实施例,光致抗蚀剂层是以液体形式沉积在金属层之上的光敏聚酰亚胺。使用包括本领域已知的那些的技术对光致抗蚀剂进行图案化和显影。然后使用包括本领域已知的那些的技术蚀刻金属层。在蚀刻工艺之后,形成了迹线1802。

[0083]

图16b图示出了使用共形镀覆工艺(诸如本文中所述的那些)的高纵横比电镀结构的形成。图16c图示出了使用冠镀覆工艺(诸如本文中所述的那些)的高纵横比电镀结构的形成。对于各种实施例,在不使用共形镀覆工艺(诸如参考图16b所描述的工艺)的情况下形

成高纵横比电镀结构。相反,在形成如图16a所示的迹线1802之后使用冠镀覆工艺(诸如参考图16c所描述的工艺)。

[0084]

图17图示出了根据实施例的高纵横比电镀结构的选择性形成。一旦使用包括本文中所述的那些的技术形成了迹线1902,就在所形成迹线1902中的一个或多个的部分之上形成光致抗蚀剂层1904。光致抗蚀剂层1904可以是光敏聚酰亚胺,并使用包括本文中所述的那些的技术沉积和形成。使用如本文中所述的共形镀覆工艺和冠镀覆工艺中的一种或两种,在迹线1902上形成金属冠1906。图18图示出了形成有选择性形成于迹线上的金属冠部分的根据实施例的高纵横比电镀结构的立体图。根据一些实施例,在迹线上选择性地形成金属冠部分用于改善高纵横比电镀结构的结构性质,改善高纵横比电镀结构的电气性能,改善热传递特性,并满足使用高纵横比电镀结构形成的装置的定制尺寸要求。电气性能改善的示例包括但不限于高纵横比电镀结构的电容、电感和电阻属性。此外,在迹线上选择性地形成金属冠部分可用于调节使用高纵横比电镀结构形成的电路的机械或电气属性。

[0085]

图19图示出了硬驱动盘悬架弯曲部2102,其包括使用如本文中所述的选择性形成形成的根据实施例的高纵横比电镀结构。图20图示出了沿线a

‑

a截取的图19中所示的硬盘驱动器悬架弯曲部的横截面视图。弯曲部2102的横截面包括高纵横比电镀结构2104和迹线2106。高纵横比电镀结构2104是使用如本文中所述的选择性形成技术形成的。形成高纵横比电镀结构2104以用作弯曲部的预定区域中的导体可以实现dc电阻的降低。这允许在弯曲部上需要处形成细线和空间,同时满足dc电阻的设计要求并改善弯曲部的电气性能。

[0086]

图21a、b图示出了用于在共形镀覆工艺期间使用光致抗蚀剂形成根据实施例的高纵横比电镀结构的工艺。图21a图示出了使用包括本文中所述的那些的技术在基底2304上形成的迹线2302。图21b图示出了使用如本文中所述的镀覆工艺的高纵横比电镀结构的形成。使用包括本文中所述的那些的沉积和图案化技术在基底2304之上形成光致抗蚀剂部分2306。一旦形成了光致抗蚀剂部分2306,就执行共形镀覆工艺和冠镀覆工艺中的一种或两者,以在迹线2302上形成金属部分2308。光致抗蚀剂部分2306可用于更好地限定高纵横比电镀结构之间的间隔。

[0087]

图22图示出根据各种实施例的用于形成初始金属层的工艺、标准/共形镀覆工艺、以及冠镀覆工艺的示例性化学过程。

[0088]

图23图示出了由根据实施例的高纵横比电镀结构2504形成的具有集成调谐电容器的感应耦合线圈2502的顶表面2501的立体图。与使用当前技术形成线圈的感应耦合线圈相比,使用高纵横比电镀结构来形成感应耦合线圈减小了感应耦合线圈的占用面积。这使得感应耦合线圈2502能够用于空间有限的应用中。此外,使用集成在感应耦合线圈中的电容器进一步减小了感应耦合线圈的占用面积,这是因为不需要额外的空间要求来容纳分立电容器,诸如表面安装技术(“smt”)电容器。

[0089]

图24图示出了图23所示的感应耦合线圈2502的实施例的后表面2604的立体图。图25图示出了与射频识别(“rfid”)芯片2704耦合的根据实施例的感应耦合线圈2502的顶表面的立体图。

[0090]

图26a

‑

j图示出了形成由根据实施例的高纵横比电镀结构2504形成的感应耦合线圈2502的方法。根据各种实施例,感应耦合线圈包括集成调谐电容器。图26a图示出了使用包括本领域已知的那些的技术形成的基底2802。对于一些实施例,基底2802由不锈钢形成。

可用于基底的其他材料包括但不限于钢合金,铜,铜合金,铝,可使用包括等离子体气相沉积、化学气相沉积和无电解化学沉积在内的技术金属化的非导体材料。在基底2802之上形成荫罩2804。根据一些实施例,荫罩2804是高k电介质。可以使用的高k电介质的示例包括但不限于二氧化钛(tio2)、氧化铌(nb2o5)、氧化钽(tao)、氧化铝(al2o3)、二氧化硅(sio2)、聚酰亚胺、su

‑

8、kmpr、以及其他高介电常数电介质材料。根据一些实施例,使用包括本领域已知的那些的技术、使用溅射工艺形成荫罩2804。对于一些实施例,荫罩2804形成为具有包括在500至1000埃的范围内的厚度。对于其他实施例,使用高介电常数墨水的丝网印刷形成荫罩2804。高介电常数墨水的示例包括墨水,其包括环氧树脂,该环氧树脂加载有由二氧化钛(tio2)、氧化铌(nb2o5)、氧化钽(tao)、氧化铝(al2o3)、二氧化硅(sio2)、聚酰亚胺、以及其他高介电常数电介质材料中的一种或多种制成的颗粒。对于又其他实施例,使用掺杂有高k填料的光可成像电介质的缝模应用(slot die application)来形成荫罩2804。高k填料的示例包括二氧化锆(zro2)。

[0091]

图26b图示出了形成在荫罩2804之上的金属电容器板2806。金属电容器板2806和基底2802形成集成电容器的两个电容器板。荫罩2804的厚度可用于设定集成电容器的有效电容。此外,用于形成荫罩2804的高k电介质的纯度可用于设定集成电容器的有效电容。金属电容器板2806的表面积也可用于设定集成电容器的有效电容。

[0092]

图26c图示出了形成在荫罩2804、金属电容器板2806、以及基底2802的至少一部分之上的基部电介质层2808。根据一些实施例,基部电介质层2808通过使用包括本领域已知的那些的技术沉积电介质材料、图案化电介质材料、以及固化电介质材料而形成。可以使用的电介质材料的示例包括但不限于聚酰亚胺、su

‑

8、kmpr和硬烘焙光致抗蚀剂(诸如由销售的那些)。基部电介质层2808也可以被图案化或蚀刻以形成过孔。例如,跨接过孔2812和分路电容器过孔2810形成在基部电介质层2808中。形成分路电容器过孔2810以将集成电容器与待形成的电路的其余部分互连。类似地,跨接过孔2812用于将要形成的电路元件与基底2802互连。

[0093]

图26d图示出了使用包括本文所述的那些的技术、使用用于形成线圈的高纵横比电镀结构在基部电介质层2808之上形成的线圈2814。对于一些实施例,线圈2814是单层线圈。线圈2814包括中心连接部分2816,其连接到分路电容器过孔2810中的一个和与集成电容器的金属电容器板2806电气接触的跨接过孔2812中的一个。线圈2814还包括电容器连接部分2818,以将线圈2814连接到分路电容器过孔2810中的另一个,该另一个分路电容器过孔2810与被配置为集成电容器的下板的基底2802电气接触。根据各种实施例,端子焊盘2820由使用包括本文中所述的那些的技术的高纵横比电镀结构形成。端子焊盘2820可以在与用于形成线圈2814的相同工艺期间形成。

[0094]

图26e图示出了形成在线圈2814、端子焊盘2820和基部电介质层2808之上以包裹感应耦合线圈的线圈侧的覆盖涂层2822。使用包括本领域已知的那些的沉积、蚀刻和图案化步骤形成覆盖涂层2822。例如,覆盖涂层2822可以由聚酰亚胺焊料掩膜、su

‑

8、kmpr或环氧树脂形成。

[0095]

图26f图示出了根据实施例形成的感应耦合线圈的背侧。至少第一焊盘2824和第二焊盘2826形成在基底2802的与线圈2814相反的一侧上。根据一些实施例,使用包括本领域已知的那些的沉积和图案化技术由金形成第一焊盘2824和第二焊盘2826。形成第一焊盘

2824和第二焊盘2826以提供用于将集成电路芯片(诸如rfid芯片)附连到基底2802的电气接触。

[0096]

图26g图示出了形成在根据实施例形成的感应耦合线圈的背侧上的背侧电介质层2828。形成感应耦合线圈的方法可任选地包括在基底2802上形成背侧电介质层2828。背侧电介质层2828是使用与形成基部电介质层2808的那些类似的技术形成的。根据在一些实施例,背侧电介质层2828被图案化以防止基底2802与附连的集成电路芯片之间的短路。根据各种实施例,背侧电介质层2828被图案化以提供用于待蚀刻的基底2802的跨接图案2830,以在后续步骤中形成跨接路径。可以形成背侧电介质中的其他图案以便也蚀刻基底2802的其他部分。

[0097]

图26h图示出了根据实施例的形成为其最终形状的感应耦合线圈2834。未被背侧电介质层2828覆盖的基底2802的部分被蚀刻。被蚀刻的部分包括跨接图案2830以形成跨接路径2832。使用包括本领域已知的那些的技术来执行蚀刻。本领域技术人员将理解,可以蚀刻基底2802的其他部分以形成类似于跨接路径2832的其他导电路径。图26i图示出了根据实施例的包括跨接路径2832的感应耦合线圈2834的线圈侧。

[0098]

图26j图示出了根据实施例的包括附连到感应线圈的背侧的集成芯片2836的感应耦合线圈2834的线圈侧。用于形成感应耦合线圈2834的方法可以可选地包括使用包括本领域已知的那些的技术将集成芯片2836(诸如rfid芯片)附连到感应耦合线圈2834的步骤。这样的集成芯片2836使用粘合剂附连,该粘合剂包括但不限于导电环氧树脂、焊料和用于实现电气连接的其他材料。

[0099]

电容器集成到包括高纵横比电镀结构的装置中提供了利用通过使用高纵横比电镀结构而能够实现的小的占用面积需求的能力。感应耦合线圈的其他实施例包括具有多个集成电容器的感应耦合线圈。如本领域中已知的,集成电容器可以并联或串联连接。包括也可包括集成电容器的高纵横比电镀结构的其他装置包括但不限于降压变压器、信号调整装置、调谐装置、以及包括一个或多个电感器和一个或多个电容器的其他装置。

[0100]

根据本文中所述实施例的高纵横比电镀结构可以用于形成装置或形成装置的一部分,以优化性能并实现小的占用面积。这样的装置包括但不限于功率转换器(例如,降压变压器、分压器、ac变压器)、致动器(例如,线性、vcm)、天线(例如,rfid、用于电池充电的无线功率传递、以及安全芯片)、无线无源线圈、可再充电的手机和医疗装置电池、接近传感器、压力传感器、非接触式连接器、微电机、微流体、封装上的冷却/热沉、带有空气芯电容和电感的长窄柔性电路(例如,用于导管)、叉指式声波换能器、触觉振动器、植入物(例如,起搏器、刺激器、骨生长装置)、用于手术(例如,食道、结肠镜检查)的磁共振成像(“mri”)装置、超出触觉(例如,服装、手套)、用于检测/过滤器释放的涂覆表面、安全系统、高能量密度电池、感应加热装置(用于小局部区域)、用于流体/药物分配的磁场和通过通道脉冲实现的剂量输送、跟踪和信息装置(例如,农业、食品、贵重物品)、信用卡安全、音响系统(例如,扬声器线圈、耳机中的再充电机构、耳塞)、热传递、机械导热密封、能量采集器和互锁形状(类似于钩环紧固件)。此外,如本文中所述的高纵横比电镀结构可用于形成高带宽、低阻抗互连。在互连应用中使用高纵横比电镀结构可用于改善电气特性(例如,电阻、电感、电容),改善热传递属性,以及定制尺寸要求(厚度控制)。包括如本文中所述的高纵横比电镀结构的互连应用可用于针对给定频率范围调节一个或多个电路的带宽。包括高纵横比电镀结构的

其他互连应用可以集成一个或多个改变电流(例如,信号和功率)的电路。高纵横比电镀结构的使用允许实现具有不同横截面的电路,允许一些电路具有更大的载流能力,以便紧密地制造在一起以维持密集的整体封装大小。高纵横比电镀结构也可出于机械目的而用于互连应用。例如,可能期望使电路的一些区域突出到其他区域上方以用作机械止动件、支承、电气接触区域或用于增加刚度。

[0101]

图27图示出了用于包括根据实施例的高纵横比电镀结构的硬盘驱动器的悬架的弯曲部的平面视图。弯曲部2900包括远端部分2901、万向节部分2902、中间部分2904、间隙部分2906和近端部分2908。近端部分2908被配置为附连到底板,以使得远端部分2901延伸到旋转盘介质之上。根据一些实施例,万向节部分2902被配置为包括:一个或多个马达,诸如压电马达;以及一个或多个电气部件,诸如用于读取或写入盘介质的头滑动器;以及用于加热辅助磁记录(“hamr”)/热辅助磁记录(“tamr”)或微波辅助磁记录(“mamr”)的部件。一个或多个马达和一个或多个电气部件通过形成在弯曲部的导体层上的一个或多个迹线电连接到其他电路,该导体层从弯曲部2900的远端部分2901经中间部分2904延伸到间隙部分2906之上并且超出近端部分2908。间隙部分2906是弯曲部的一部分,在该部分,基底层(诸如不锈钢层)部分地或完全地被去除。因此,弯曲部的导体层中的一个或多个迹线在没有任何支撑的情况下延伸到间隙部分2906之上。本领域技术人员将理解,弯曲部可在沿着弯曲部的任何位置处具有一个或多个间隙部分2906。

[0102]

图28图示出了在沿如图27所示的线a截取的间隙部分处的弯曲部的间隙部分的横截面。间隙部分2906包括设置在电介质层3004之上的迹线3002。诸如聚酰亚胺层的电介质层设置在诸如不锈钢层的基底3006之上。基底3006和电介质层3004限定空隙3008,以使得迹线3002延伸到空隙3008之上。迹线3002包括金属冠部分以形成高纵横比结构。使用本文中所述的技术在迹线3002上选择性地形成金属冠部分。金属冠部分形成在迹线3002上,以提供跨越空隙3008的附加强度,并且在使用时与空隙3008的区域处的互连应用电耦合。

[0103]

图29图示出了根据实施例的具有质量结构3102的万向节部分2902。使用本文中所述的技术、使用高纵横比电镀结构形成质量结构3102。对于一些实施例,质量结构3102用作调节万向节部分2902的共振的配重。因此,可以确定质量结构3102的形状、大小和位置,以调节万向节部分2902的共振,从而增强硬驱悬架的性能。本文中描述的用于形成高纵横比结构的工艺可用于维持高纵横比结构的大小,以使得可以对共振进行精细调节。此外,该工艺能够在超出当前光刻工艺能力的尺寸上形成高纵横比结构,从而能够更好地控制所形成的最终结构。

[0104]

质量结构3102也可以被配置为用作机械止动件。例如,一个或多个机械止动件可以形成任何形状以用作后挡和/或用于将部件对准安装在万向节部分2902或弯曲部的其他部分上。

[0105]

图30图示出了包括根据实施例的高纵横比电镀结构的弯曲部的近端部分的沿如图27所示的线b截取的横截面。近端部分2904包括:包括设置在电介质层3004之上的迹线3002a、b、c、d的导体层。电介质层3004设置在基底3006之上。覆盖层3001设置在导体层和电介质层之上。导体层包括常规迹线3002a、b和迹线3002c、d,它们形成为迹线的至少一部分包括金属冠部分3202a、b,以使用本文中所述的技术形成高纵横比电镀结构。迹线3002a、b、c、d中的一个或多个部分可以形成为包括金属冠部分3202a、b,以调节每个迹线的阻抗。例

如,可以根据需要调节迹线的电阻以满足期望的性能特性。另一示例包括使用金属冠部分,以通过闭合相邻迹线3002a、b、c、d之间的距离来调节阻抗。

[0106]

图31图示出了包括根据实施例的高纵横比结构的弯曲部的近端部分的沿如图27所示的线c截取的横截面。弯曲部的近端部分包括导体层,该导体层至少包括设置在电介质层3004之上的迹线3002。电介质层3004设置在基底3008上。此外,覆盖层3001设置在形成的之上,以包括金属冠部分以使用本文中描述的技术形成高纵横比电镀结构。迹线3002被配置为高纵横比结构,以使迹线的阻抗与终端连接器匹配,并为将迹线3002与连接器电耦合的接头提供强度。图32图示出了包括根据实施例的高纵横比结构的弯曲部的近端部分2908的平面视图。如参考与弯曲部一起使用所描述的高纵横比结构的使用也适用于其他电路板技术,例如用于微电路和射频(“rf”)电路。

[0107]

图33图示出了用于形成根据实施例的高纵横比电镀结构的工艺。如图所示,铜层3318用作基底。然而,其他导电材料也可以用作基底。在3301处,将电介质层3320设置在铜层3318上,诸如本文中描述的那些,并进行标记和穿孔。电介质层3320可以使用包括但不限于光可成像或非光可成像材料、聚合物、陶瓷和其他绝缘材料的材料形成。对于一些实施例,铜层3318是诸如本文中所述的那些的铜合金层。对于一些实施例,在电介质层中标记并穿孔一个或多个通孔或过孔3322以暴露铜层3318。根据一些实施例,电介质层3320是光可成像电介质材料,并且使用包括本文中所述的那些的图案化和显影技术来创建一个或多个通孔或过孔3322。其他实施例包括使用激光、钻孔或蚀刻电介质层3320来创建一个或多个通孔或过孔3322。对于一些实施例,铜合金层具有包括15微米至40微米范围内的厚度。在3302处,迹线3324或其他导电特征设置在电介质层3320上与铜层3318相反的电介质层的一侧。对于一些实施例,使用包括本文中所述的那些的技术来溅射籽晶层以在电介质层3320上形成图案。其他实施例包括使用无电解镀覆来形成籽晶层。使用包括本文中所述的那些的技术,使用镀覆工艺(诸如本文中所述的那些)将一个或多个迹线3324和导电特征形成至期望的厚度。

[0108]

在3304处,使用包括本文中所述的那些的技术,使用共形镀覆工艺(诸如本文中所述的那些)来构建一个或多个迹线和导电特征,以增加电介质层3320与铜层3318相反的一侧上的一个或多个迹线和导电特征的厚度或进一步增强其形状。对于一些实施例,在3304处,在电介质层3320与铜层3318相反的一侧上,除了共形镀覆工艺之外,还使用了冠镀覆工艺,诸如本文中所述的那些。对于一些实施例,使用冠镀覆工艺代替共形镀覆工艺。

[0109]

在3306处,使用包括本文中所述的那些的技术将电介质层3326(诸如覆盖涂层)设置在电介质层与铜层3318相反的一侧上的一个或多个迹线3324和导电特征上。对于一些实施例,不包括覆盖涂层。例如,所形成的一个或多个迹线3324和导电特征可镀覆有金层。在3308处,使用包括本文中所述的那些的技术来蚀刻铜层3318以形成图案。对于一些实施例,蚀刻铜层3318以形成一个或多个迹线3328和/或一个或多个导电特征。

[0110]

在3310处,使用包括本文中所述的那些的技术,使用共形镀覆工艺(诸如本文中所述的那些)来构建一个或多个迹线3328和导电特征,以增加在铜层3318中形成的一个或多个迹线3328和导电特征的厚度或进一步增强其形状。对于一些实施例,在3310处,在铜层3318上,除了共形镀覆工艺之外,还使用了冠镀覆工艺,诸如本文中所述的那些。对于一些实施例,使用冠镀覆工艺代替共形镀覆工艺。

[0111]

在3312处,使用包括本文中所述的那些的技术将电介质层3330(诸如覆盖涂层)设置在由铜层3318形成的一个或多个迹线3328和导电特征上。对于一些实施例,不包括覆盖涂层。例如,所形成的一个或多个迹线3328和导电特征可镀覆有金层。对于一些实施例,该工艺用于在单个基底上制造多个电路或装置。在3316处,对于这样的实施例,电路或装置是分离(单一)的,并且可选地可以使用包括本领域已知的那些的技术来封装。对于一些实施例,使用包括但不限于激光烧蚀、破裂、切割、蚀刻等的技术将电路和/或装置分离。对于一些实施例,可以使用本文中所述的图案化技术来对本文中所述的覆盖涂层进行图案化。例如,覆盖涂层被施加在覆盖层(blanket layer)中。根据一些实施例,使用槽口冲模涂层施加覆盖涂层以施加光可成像电介质材料。可以使用其他技术,诸如辊涂、喷涂、干膜层压或用于施加光可成像或非光可成像材料的其他已知方法。如果材料是非光可成像的,则可以使用其他方法对其进行图案化(例如,激光或蚀刻)。对于一些实施例,电介质层/覆盖涂层中的一个或两者可以形成有表面处理(surface finish),例如,以帮助附着到其他结构或基底。对于一些实施例,通过对电介质层/覆盖涂层进行纹理化或图案化,在电介质层/覆盖涂层上形成表面处理。

[0112]

在3314处,对于一些实施例,可以使用无电解镀覆在基底3318上形成端子焊盘3332(诸如镀覆有金层的镍端子),并且可以向其提供焊料。根据一些实施例,使用镍、金的无电解或电解镀覆对设置在顶侧和/或底侧的裸露铜层上形成的表面处理进行镀覆或进行其他行业标准表面处理。此外,可以将焊料施加在这些区域。

[0113]

图34图示出了类似于参考图33所述的用于形成根据一些实施例的高纵横比电镀结构的类型的更详细工艺。

[0114]

图35图示出了使用本文中所述的工艺制造的线圈。线圈3501包括电耦合以形成线圈3501的多个(例如,三个或更多个)线圈段。对于一些实施例,诸如图35所示的实施例,外线圈段3504中的匝数与两个外线圈段3504之间的内线圈段3502相同。对于一些实施例,内线圈段3402包括比外线圈段3504更多的匝数。其他实施例包括多个线圈段,其中多个线圈段的子集电耦合,例如,参考图35,多个线圈段中的两个电耦合,并且剩余的线圈段不与其他两个线圈段电耦合。因此,任何数量的线圈段的任何组合可以包括在与其他线圈段中的任何线圈段进行电耦合的任何数量的线圈段里。

[0115]

可以通过堆叠每个层来形成包括使用本文中所述的技术制造的迹线和导电特征中任何的一个或多个的多个层,并且每个层之间的连接可以通过穿过填充有导电材料(诸如导电粘合剂)的层的过孔来进行。

[0116]

根据一些实施例,本文中所述的工艺用于形成与其他电路部件(例如,电阻温度检测器(rtd)、应变计和其他传感器)结合的线圈。

[0117]

根据一些实施例,本文中所述的工艺用于形成机械结构和机电结构中任何的一个或多个。

[0118]

尽管结合这些实施例进行了描述,但是本领域技术人员将认识到,可以对形式和细节进行改变而不脱离本发明的精神和范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。