1.本发明涉及一种阀金属的阳极氧化处理方法及在通过阳极氧化处理获得的阳极氧化膜的微孔中填充有导电性材料的各向异性导电性部件的制造方法,尤其涉及一种阳极氧化膜的微孔的直线度良好的阳极氧化处理方法及各向异性导电性部件的制造方法。

背景技术:

2.在设置于绝缘性基材的多个贯穿孔中填充金属等导电性物质而成的结构体为近年来在纳米科技中也受到关注的领域之一,例如,期待作为各向异性导电性部件的用途。

3.各向异性导电性部件只要插入半导体元件等电子零件与电路基板之间并加压即可获得电子零件与电路基板之间的电连接,因此广泛用作半导体元件等电子零件等的电连接部件及进行功能检査时的检査用连接器等。

4.尤其,半导体元件等电子零件的小型化显著。在现有的打线等直接连接配线基板的方式、覆晶接合及热压接合等中,无法充分保证电子零件的电连接稳定性,因此各向异性导电性部件作为电子连接部件而受到关注。

5.例如,在专利文献1中,记载有一种微细结构体的制造方法,该微细结构体由以1000万个/mm2以上的密度具有微孔贯穿孔的基材构成,一部分微孔贯穿孔被除基材的材料以外的物质填充。在专利文献1的微细结构体的制造方法中,基材为氧化铝,并在铝基板上至少依次实施(a)通过阳极氧化处理形成具有微孔的氧化覆膜的处理、(b)从在上述(a)处理中获得的氧化覆膜去除铝的处理、(c)贯穿存在于在上述(b)处理中去除了铝的氧化覆膜的微孔的一部分的处理、(d)在上述(c)处理中贯穿的微孔内填充除氧化覆膜以外的物质的处理、(e)将上述(d)处理后的氧化覆膜的表面及背面通过化学机械研磨处理进行平滑化的表面平滑化处理。

6.以往技术文献

7.专利文献

8.专利文献1:日本特开2013

‑

167023号公报

技术实现要素:

9.发明要解决的技术课题

10.在上述专利文献1的微细结构体的制造方法中,能够通过阳极氧化处理形成具有微孔的氧化覆膜。

11.然而,根据阳极氧化处理的条件,微孔分叉或变斜等难以形成笔直的微孔。在微孔分叉或变斜的情况下,即使试图在微孔内填充除氧化覆膜以外的物质,也无法充分填充于微孔内而产生填充缺陷。因此,例如在填充金属等导电性材料时,由于填充缺陷而无法获得健全的导电通路。

12.本发明的目的在于提供一种能够形成笔直的微孔的阳极氧化处理方法及抑制导电性材料的填充缺陷的各向异性导电性部件的制造方法。

13.用于解决技术课题的手段

14.为了实现上述目的,本发明的第1方式提供一种阳极氧化处理方法,其对阀金属板的表面实施多次阳极氧化处理且在阀金属板的表面形成阳极氧化膜,所述阳极氧化膜具有存在于阀金属板的厚度方向上的微孔和存在于微孔的底部的阻挡层,在多次阳极氧化处理中,第2次以后的阳极氧化处理工序的电流增加期间和电流维持期间是连续的,电流增加期间为电流增加量超过每秒0安培每平方米且为每秒0.2安培每平方米以下、并且为10分钟以下的期间,电流维持期间的电流维持恒定值,恒定值为电流增加期间的最大电流值以下。

15.在电流增加期间,优选使对阀金属板施加的电压阶段性地增加。

16.与阀金属板对置地配置有对置电极,优选导电性的负载部件与阀金属板电性并联连接。

17.在多次阳极氧化处理中,优选第1次阳极氧化处理工序在恒定电压下实施。

18.阀金属板优选铝基板。

19.本发明的第2方式提供一种各向异性导电性部件的制造方法,其具有如下工序:对于通过本发明的第1方式的阳极氧化处理方法获得的具有微孔的阳极氧化膜,将导电性材料填充于阳极氧化膜的微孔中。

20.在将导电性材料填充于阳极氧化膜的微孔中的工序之前,优选具有从阳极氧化膜去除阀金属板的工序和贯穿存在于阀金属板被去除的阳极氧化膜的微孔的工序。

21.发明效果

22.根据本发明,能够获得具有笔直的微孔的阳极氧化膜。并且,能够获得抑制了导电性材料的填充缺陷的各向异性导电性部件。

附图说明

23.图1是表示阳极氧化处理时的电流变化的图表。

24.图2是表示本发明的实施方式的阳极氧化处理时的电流变化的图表。

25.图3是表示本发明的实施方式的各向异性导电性部件的制造方法的第1方式的一工序的示意性剖视图。

26.图4是表示本发明的实施方式的各向异性导电性部件的制造方法的第1方式的一工序的示意性剖视图。

27.图5是表示本发明的实施方式的各向异性导电性部件的制造方法的第1方式的一工序的示意性剖视图。

28.图6是表示本发明的实施方式的各向异性导电性部件的制造方法的第1方式的一工序的示意性剖视图。

29.图7是表示本发明的实施方式的各向异性导电性部件的制造方法的第1方式的一工序的示意性剖视图。

30.图8是表示本发明的实施方式的各向异性导电性部件的制造方法的第2方式的一工序的示意性剖视图。

31.图9是表示本发明的实施方式的各向异性导电性部件的制造方法的第2方式的一工序的示意性剖视图。

32.图10是表示本发明的实施方式的各向异性导电性部件的制造方法的第2方式的一

工序的示意性剖视图。

33.图11是表示本发明的实施方式的各向异性导电性部件的制造方法的第3方式的一工序的示意性剖视图。

34.图12是表示本发明的实施方式的各向异性导电性部件的制造方法的第3方式的一工序的示意性剖视图。

35.图13是表示在本发明的实施方式的各向异性导电性部件的制造方法的第3方式中制造的各向异性导电性部件的供给方式的一例的示意图。

36.图14是放大表示在本发明的实施方式的各向异性导电性部件的制造方法的第3方式中制造的各向异性导电性部件的供给方式的一例的重要部分的示意图。

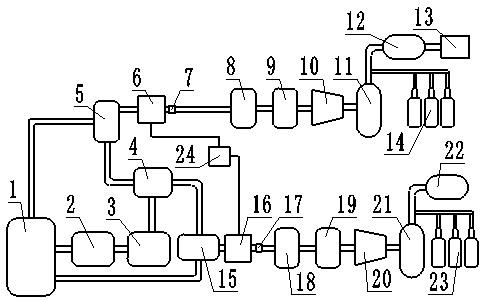

37.图15是表示在本发明的实施方式的各向异性导电性部件的制造方法中用于阳极氧化处理工序的阳极氧化处理装置的一例的示意图。

38.图16是表示本发明的实施方式的各向异性导电性部件的制造方法中阳极氧化处理工序的电流模式的第1例的图表。

39.图17是表示本发明的实施方式的各向异性导电性部件的制造方法中阳极氧化处理工序的电流模式的第2例的图表。

40.图18是表示本发明的实施方式的各向异性导电性部件的制造方法中阳极氧化处理工序的电压模式的一例的图表。

41.图19是表示本发明的实施方式的各向异性导电性部件的制造方法中用于阳极氧化处理工序的阳极氧化处理装置的另一例的示意图。

42.图20是表示本发明的实施方式的各向异性导电性部件的一例的俯视图。

43.图21是表示本发明的实施方式的各向异性导电性部件的一例的示意性剖视图。

44.图22是表示使用了本发明的实施方式的各向异性导电性部件的各向异性导电材料的结构的一例的示意性剖视图。

45.图23是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的第1例的示意图。

46.图24是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的第2例的示意图。

47.图25是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的制造方法的一工序的示意性剖视图。

48.图26是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的制造方法的一工序的示意性剖视图。

49.图27是放大表示具有本发明的实施方式的各向异性导电性部件的层叠装置的制造方法的一工序的示意性剖视图。

50.图28是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的正式接合条件的第1例的图表。

51.图29是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的正式接合条件的第2例的图表。

52.图30是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的正式接合条件的第3例的图表。

53.图31是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的正式接合条件的第4例的图表。

54.图32是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的正式接合条件的第5例的图表。

55.图33是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的正式接合条件的第6例的图表。

56.图34是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的正式接合条件的第7例的图表。

57.图35是表示半导体封装的第1例的示意性剖视图。

58.图36是表示半导体封装的第2例的示意性剖视图。

59.图37是表示半导体封装的第3例的示意性剖视图。

60.图38是表示半导体封装的第4例的示意性剖视图。

61.图39是表示半导体封装的第5例的示意性剖视图。

62.图40是表示层叠了半导体封装基板的结构的示意性剖视图。

63.图41是表示半导体封装的第6例的示意性剖视图。

64.图42是表示半导体封装的第7例的示意性剖视图。

65.图43是用于说明同轴结构的示意性剖视图。

66.图44是用于说明同轴结构的示意性俯视图。

67.图45是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第1例的示意图。

68.图46是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第2例的示意图。

69.图47是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第3例的示意图。

70.图48是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第4例的示意图。

71.图49是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第5例的示意图。

72.图50是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第6例的示意图。

具体实施方式

73.以下,根据附图所示的优选实施方式,对本发明的阳极氧化处理方法及各向异性导电性部件的制造方法进行详细说明。

74.另外,以下所说明的图为用于说明本发明的例示性图,本发明并不限定于以下所示的图。

75.另外,以下,表示数值范围的“~”包括记载于两侧的数值。例如,ε为数值α~数值β表示ε的范围包括数值α和数值β的范围,若以数学符号表示,则为α≤ε≤β。

76.若无特别记载,则“正交”等的角度包括相关技术领域中通常允许的误差范围。并

且,若无特别记载,则温度包括相关技术领域中通常允许的误差范围。

77.图1是表示阳极氧化处理时的电流变化的图表,图2是表示本发明的实施方式的阳极氧化处理时的电流变化的图表。

78.实施阳极氧化处理时,如图1所示,输入电压时电流急剧上升,产生比稳态电流值高的电流值的区域pe。通过对阀金属进行阳极氧化处理来形成微孔时,该电流的急剧上升会导致无法形成笔直的微孔。针对该现象,获得了如下见解:如图2所示,通过使输入电压时的电流的上升缓慢,具体而言,通过将电流增加量设为超过每秒0安培每平方米(0a/(m2·

秒))且每秒0.2安培每平方米(0.2a/(m2·

秒))以下而能够形成笔直的微孔。进而,通过形成笔直的微孔,能够实现向微孔填充金属时的填充缺陷的抑制。

79.以下,对阳极氧化处理方法及各向异性导电性部件的制造方法进行具体说明。

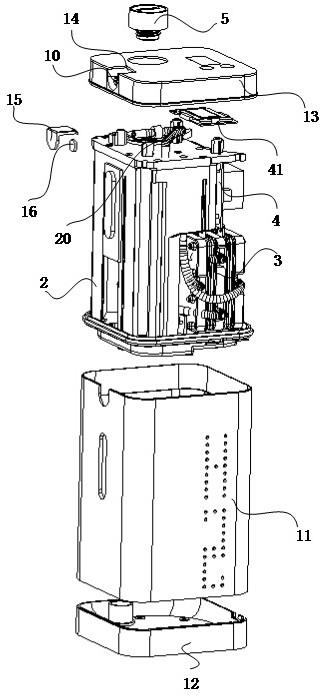

80.<第1方式>

81.图3~图7是按工序顺序表示本发明的实施方式的各向异性导电性部件的制造方法的第1方式的示意性剖视图。

82.各向异性导电性部件是对阀金属板的表面实施多次阳极氧化处理来获得的。各向异性导电性部件具有由阀金属的阳极氧化膜构成的绝缘性基材。阀金属为铝等,但并不特别限定于铝,作为绝缘性基材,以铝的阳极氧化膜为例进行说明。因此,在以下说明中,作为阀金属板,以铝基板为例进行说明。

83.首先,如图3所示,准备铝基板10。

84.铝基板10根据最终获得的各向异性导电性部件20(参考图7)的阳极氧化膜14的厚度即绝缘性基材的厚度、所加工的装置等来适当确定大小及厚度。铝基板10例如为矩形形状的板材。

85.接着,对铝基板10的一侧的表面10a(参考图3)实施多次阳极氧化处理。即,重复实施阳极氧化处理。由此,铝基板10的一侧的表面10a(如图3)被阳极氧化,如图4所示,具有存在于沿铝基板10的厚度方向dt延伸存在的多个微孔12的底部的阻挡层13的阳极氧化膜14形成于铝基板10的表面10a。将上述的实施多次阳极氧化处理的工序称为阳极氧化处理工序。关于阳极氧化处理工序,以下进行详细说明。

86.在具有多个微孔12的阳极氧化膜14,如上所述,在微孔12的底部存在阻挡层13,但如图5所示,去除阻挡层13。将去除该阻挡层13的工序称为阻挡层去除工序。

87.在阻挡层去除工序中,通过使用包含氢过电压比铝更高的金属m1的离子的碱水溶液,去除阳极氧化膜14的阻挡层13的同时,在微孔12的底部例如形成导电性材料即由金属(金属m1)构成的金属层15a。由此,微孔12的底部的铝基板10被金属层15a包覆。

88.将具有图5所示的多个微孔12的阳极氧化膜14即具有多个微孔的绝缘性基材称为结构体17。

89.接着,如图6所示,在阳极氧化膜14的微孔12的内部,例如填充金属15b作为导电性材料。通过在微孔12的内部填充金属15b来形成具有导电性的导电通路16。此时,能够将由金属(金属m1)构成的金属层15a用作电解电镀的电极。

90.将在微孔12的内部填充金属15b的工序称为金属填充工序。在金属填充工序中利用电解电镀,以下对金属填充工序进行详细说明。另外,所填充的材料只要为导电性材料即可,并不限定于金属。

91.在金属填充工序之后,如图7所示,去除铝基板10。由此,获得各向异性导电性部件20。将去除铝基板10的工序称为基板去除工序。

92.通过在金属填充工序之前的阻挡层去除工序中使用包含氢过电压比铝更高的金属m1的离子的碱水溶液来去除阻挡层,不仅去除阻挡层13,也在暴露于微孔12的底部的铝基板10形成比铝还不易产生氢气的金属m1的金属层15a。其结果,金属填充的面内均匀性变良好。认为这是因为因电镀液导致的氢气的产生得到抑制而变得容易进行基于电解电镀的金属填充。

93.并且,发现在阻挡层去除工序中,设置在选自未达阳极氧化处理工序中的电压的30%的范围的电压(保持电压)中的95%以上且105%以下的电压下保持合计5分钟以上的保持工序,组合适用包含金属m1的离子的碱水溶液的工序,由此电镀处理时的金属填充的均匀性得到显著改善。

94.详细机制尚不清楚,但认为出于如下理由:通过在阻挡层去除工序中使用包含金属m1的离子的碱水溶液而在阻挡层下部形成金属m1的层,由此能够抑制铝基板与阳极氧化膜之间的界面受到损伤,且阻挡层的溶解均匀性得到了提高。

95.另外,在阻挡层去除工序中,在微孔12的底部形成有由金属(金属m1)构成的金属层15a,但并不限定于此,仅去除阻挡层13,使铝基板10暴露于微孔12的底部。也可以在暴露铝基板10的状态下,将铝基板10用作电解电镀的电极。

96.<第2方式>

97.图8~图10是按工序顺序表示本发明的实施方式的各向异性导电性部件的制造方法的第2方式的示意性剖视图。

98.另外,在图8~图10中,对与图3~图7所示的结构相同的结构物标注相同符号,并省略其详细说明。另外,图8表示上述图6之后的状态。

99.相较于上述第1方式,在第2方式中,以下所示的工序不同。如图8所示,在金属填充工序之后,将阳极氧化膜14的未设置有铝基板10一侧的表面沿厚度方向去除一部分,使在金属填充工序中填充的金属15比阳极氧化膜14的表面更突出。即,使导电通路16比阳极氧化膜14的表面更突出。将使所填充的金属15比阳极氧化膜14的表面更突出的工序称为表面金属突出工序。

100.如图9所示,在表面金属突出工序之后去除铝基板10(基板去除工序)。

101.接着,如图10所示,在基板去除工序之后,将阳极氧化膜14的设置有铝基板10一侧的表面沿厚度方向去除一部分,使在金属填充工序中填充的金属15,即导电通路16比阳极氧化膜14的表面更突出。由此,获得图10所示的各向异性导电性部件20。

102.关于上述的表面金属突出工序及背面金属突出工序,可以为具有两个工序的方式,也可以为具有表面金属突出工序及背面金属突出工序中的一个工序的方式。也将表面金属突出工序及背面金属突出工序统称为“金属突出工序”。

103.<第3方式>

104.图11及图12是按工序顺序表示本发明的实施方式的各向异性导电性部件的制造方法的第3方式的示意性剖视图。

105.另外,在图11及图12中,对与图3~图7所示的结构相同的结构物标注相同符号,并省略其详细说明。另外,图11表示上述图6之后的状态。

106.相较于上述第1方式,在第3方式中,以下所示的工序不同。如图11所示,在金属填充工序之后,在阳极氧化膜14的未设置有铝基板10一侧的表面设置树脂层19。将设置树脂层19的工序称为树脂层形成工序。

107.接着,如图12所示,在树脂层形成工序之后去除铝基板10(基板去除工序)。由此,获得图7所示的各向异性导电性部件20。

108.在第3方式中,如图13所示,试图将所制造的各向异性导电性部件20在以卷状卷取在卷芯21的状态下供给。通过在使用各向异性导电性部件20时剥离树脂层19(参考图14),例如能够用作各向异性导电性部件。

109.<其他方式>

110.作为制造方法,例如,也可以依次实施上述的阳极氧化处理工序、保持工序、阻挡层去除工序、金属填充工序、表面金属突出工序、树脂层形成工序、基板去除工序及背面金属突出工序。

111.并且,也可以使用所需形状的掩模层来对铝基板的表面的一部分实施阳极氧化处理。

112.〔绝缘性基材〕

113.绝缘性基材由阀金属的阳极氧化膜构成。在阀金属的阳极氧化膜中,具有所需平均开口直径的微孔形成为贯穿孔并容易形成具有导电性的导电通路,因此优选。

114.具体而言,阀金属可举出铝、钽、铌、钛、铪、锆、锌、钨、铋、锑等。其中,从尺寸稳定性良好,相对廉价的方面考虑,优选铝的阳极氧化膜(基材)。因此,优选利用铝基板来形成绝缘性基材即阳极氧化膜,并制造各向异性导电性部件。

115.〔铝基板〕

116.铝基板并无特别限定,作为其具体例,可举出纯铝板;将铝作为主成分,包含微量的异元素的合金板;将高纯度铝蒸镀于低纯度的铝(例如,再循环材料)的基板;通过蒸镀、溅射等方法在硅晶片、石英、玻璃等的表面包覆高纯度铝的基板;将铝贴合的树脂基板;等。

117.铝基板中,通过阳极氧化处理工序设置阳极氧化膜的表面的铝纯度优选99.5质量%以上,更优选99.9质量%以上,进一步优选99.99质量%以上。若铝纯度在上述范围,则微孔排列的规则性变充分。

118.并且,在本发明中,对铝基板中实施阳极氧化处理工序一侧的表面优选预先实施热处理、脱脂处理及镜面抛光处理。

119.其中,关于热处理、脱脂处理及镜面抛光处理,能够实施与日本特开2008

‑

270158号公报的[0044]~[0054]段中记载的各处理相同的处理。

[0120]

〔阳极氧化处理工序〕

[0121]

阳极氧化工序为通过在上述阀金属板的表面实施多次阳极氧化处理而将在上述阀金属板的表面具有存在于阀金属板的厚度方向的微孔和存在于微孔的底部的阻挡层的阳极氧化膜形成于阀金属板的表面的工序。具体而言,如上所述,阳极氧化工序为通过在阀金属板即铝基板的表面实施多次阳极氧化处理而在上述铝基板的表面形成具有存在于铝基板的厚度方向的微孔和存在于微孔的底部的阻挡层的阳极氧化膜的工序。

[0122]

在阳极氧化工序中实施多次阳极氧化处理,但在第2次以后的阳极氧化处理中,如上述图2所示,调整电流的上升而使其变缓慢。

[0123]

其中,图15是表示在本发明的实施方式的各向异性导电性部件的制造方法中用于阳极氧化处理工序的阳极氧化处理装置的一例的示意图。

[0124]

图16是表示本发明的实施方式的各向异性导电性部件的制造方法中阳极氧化处理工序的电流模式的第1例的图表,图17是表示本发明的实施方式的各向异性导电性部件的制造方法中阳极氧化处理工序的电流模式的第2例的图表。

[0125]

图18是表示本发明的实施方式的各向异性导电性部件的制造方法中阳极氧化处理工序的电压模式的一例的图表。

[0126]

并且,图19是表示本发明的实施方式的各向异性导电性部件的制造方法中用于阳极氧化处理工序的阳极氧化处理装置的另一例的示意图。

[0127]

图15所示的阳极氧化处理装置30具有电解槽32、对置电极34、电源部36、控制部38、电流计39。将上述铝基板10与对置电极34对置配置于电解槽32。并且,在电解槽32内充满电解液aq,且铝基板10和对置电极34被浸渍。如上所述,铝基板10为被阳极氧化处理的对象物。

[0128]

电源部36与铝基板10和对置电极34电连接且对铝基板10施加电流或电压。

[0129]

控制部38与电源部36连接且控制电源部36。通过控制部38控制电源部36所施加的电流的电流值、时刻及期间。

[0130]

在控制部38中,例如存储有多种要施加的电流的电流模式,并以任意电流模式从电源部36对铝基板10施加电流。

[0131]

另外,也可以使电源部36具有控制部38的功能,此时,不需要控制部38。并且,也将要施加的电流的电流模式称为电流控制模式。

[0132]

并且,也可以是如下构成:在控制部38中,例如存储有多种要施加的电压的电压模式,并以任意电压模式从电源部36对铝基板10施加电压。另外,如上所述,在施加电压时,也可以使电源部36具有控制部38的功能。也将要施加的电压的电压模式称为电压控制模式。

[0133]

并且,在电源部36与铝基板10之间设置有电流计39,通过电流计39,能够获得流过铝基板10的电流的电流值。也能够将来自电流计39的电流值输出至控制部38,并根据来自电流计39的电流,利用控制部38实施调整施加到铝基板10的电流或电压的反馈控制。另外,除了电流计39,也可以设置电压计。

[0134]

在阳极氧化处理工序中,在图15所示的电解槽32内对置配置铝基板10和对置电极34。然后,使电解槽32内充满电解液aq。

[0135]

接着,根据从控制部38输出的电流模式,从电源部36对铝基板10及对置电极34施加电流。虽实施多次阳极氧化处理,但在第2次以后的阳极氧化处理中,如上述图1所示,需要避免电流急剧上升。在第2次以后的阳极氧化处理中,如上述图2所示,使输入电压时的电流的上升缓慢。即,电流上升时,将电流增加量设为超过每秒0安培每平方米且每秒0.2安培每平方米以下。

[0136]

图16及图17表示2次的阳极氧化处理的工序,但阳极氧化处理只要为多次即可,并不限定于2次。另外,图16及图17所示的符号t为阳极氧化处理时间。

[0137]

第1次阳极氧化处理b1并无特别限定,例如与通常的阳极氧化处理相同。此时,例如,以40v等恒定电压实施。因此,如图16所示,成为恒定的电流值。

[0138]

第2次阳极氧化处理b2的电流增加期间和电流维持期间是连续的,且电流增加期

间为10分钟以下的期间。在第2次阳极氧化处理b2中,连续提高电流值来实施阳极氧化处理。

[0139]

在第2次阳极氧化处理b2中,将上升部ru的上升时间设为tu,将稳态部rs的稳态时间设为ts时,阳极氧化处理时间t为t=tu ts。

[0140]

稳态部rs表示预先设定的维持稳态电的区域。

[0141]

上升部ru为从电流为零的状态到电流变为最大值im为止的区域,为电流值以上述电流增加量增加的区域。

[0142]

上升部ru为电流增加期间,电流增加量如上所述为超过每秒0安培每平方米且每秒0.2安培每平方米以下。若在上升部ru,即电流增加期间,电流增加量超过每秒0安培每平方米且每秒0.2安培每平方米以下,则不会发生如上述图1所示的电流的急剧上升。由此,形成笔直的微孔而不会存在微孔分叉或微孔变斜等问题,因此能够获得具有笔直的微孔的阳极氧化膜。

[0143]

另外,笔直的微孔无分叉且微孔未变斜,并表示微孔的阳极氧化膜的表面侧的直径与背面侧的直径的比为0.9~1.1。

[0144]

在电流增加期间长的情况下,由于被阳极氧化处理一侧的微孔直径有时会变大,进而也存在微孔分叉或微孔变斜等问题,因此将电流增加期间设为10分钟以下。作为电流增加期间的下限值,无特别限定,下限值超过0分钟。若电流增加期间为5分钟以上且10分钟以下,则可更进一步抑制上述微孔的直径变大、微孔分叉及微孔变斜的问题,因此更优选。

[0145]

稳态部rs为在上升部ru中增加的电流得到维持的区域。在稳态部rs,即电流维持期间,电流被维持在恒定值。恒定值为电流增加期间内的最大电流值(即阳极氧化处理的电流值的最大值im)以下。

[0146]

另外,恒定值不会增加或减少,表示变动在以绝对值计10%的范围内。

[0147]

在实施多次阳极氧化处理时,可以连续实施阳极氧化处理,或也可以在阳极氧化处理之间设置不施加电流的期间。不施加电流的期间考虑阳极氧化处理工序的所需时间等而适当确定。

[0148]

实施多次阳极氧化处理时,例如,以图16所示的电流模式实施。图16中连续重复,但并不限定于此。如图17所示,阳极氧化处理也可以以具有不施加电流的期间tm的电流模式,实施多次阳极氧化处理。

[0149]

另外,在阳极氧化处理工序中,预先设定阳极氧化处理的设定次数,并重复实施阳极氧化处理至达到设定次数为止。阳极氧化处理的次数只要为多次,则其次数并无特别限定。

[0150]

阳极氧化处理中的电流值的控制并不限定于连续提高电流值,只要电流增加量在上述范围,也可以阶段性提高电流值。

[0151]

并且,以施加电压控制阳极氧化处理时,可以连续提高施加电压来连续提高电流值。并且,如图18所示,也能够阶段性提高施加电压来阶段性提高电流值,由此将上升中的电流增加量设于上述范围内。

[0152]

通过电压控制时,如图18所示,从电压为零的状态到电压变为最大值vm为止的区域为上升部ru,上升部ru的时间为上升时间tu。将在上升部ru中增加的电压维持在恒定值的区域为稳态部rs。

[0153]

关于电流及电压的增加模式,只要能够将电流增加期间,即上升部ru中的电流增加量设为上述范围,则并无特别限定,并不限定于图16及图18所示的那些。例如,也可以以增加程度不同的3个阶段增加电流或电压。此时,增加的程度用3个线性函数表示。增加的程度只要为多个,则并不限定于3个。

[0154]

并且,也可随时间的经过加大电流或电压的电流值或电压值的增加程度。

[0155]

另外,连续提高电流或电压表示随着电解时间的经过,增加电流值或电压值。此时,电流值或电压值能够由线性函数及二次函数等高阶函数、多个线性函数或线性函数与高阶函数的组合来表示。另外,上述函数均为递增函数,无拐点。

[0156]

分阶段提高电流值或电压值表示随着电解时间的增加,阶梯状增加电流值或电压值。因此,在分阶段提高电流值或电压值时,存在即使经过电解时间,电流值或电压值也不增加的电流值或电压值为恒定值的期间。

[0157]

在连续提高电流或电压时,能够通过上升时间tu和电流的最大值im或电压的最大值vm来求出电流增加量。

[0158]

在阶段性提高电压时,能够通过上升时间tu和电流的最大值im或电压的最大值vm来求出电流增加量。另外,电流值能够通过上述电流计39获得。例如,能够将由电源部36输出的电压的值用作电压值。

[0159]

如上述图2所示,使输入电压时的电流的上升变缓慢,并不限定于上述电流控制及电压控制。例如,能够利用与阳极氧化处理对象即阀金属板电性并联连接的导电性的负载部件来控制电流上升速度。

[0160]

设置导电性的负载部件时,例如能够利用图19所示的阳极氧化处理装置30。图19所示的阳极氧化处理装置30与图15所示的阳极氧化处理装置30相比,在具有与阳极氧化处理对象即铝基板10电性并联连接的金属基板35作为导电性的负载部件这一点不同,除此以外的结构为与图13所示的阳极氧化处理装置30相同的结构,因此省略其详细说明。

[0161]

金属基板35与阳极氧化处理对象即铝基板10一同被浸渍于电解槽32内的电解液aq。

[0162]

金属基板35例如由纯钛、钛合金、不锈钢等构成。

[0163]

金属基板35的形状及大小并无特别限定,例如与作为阳极氧化处理对象的阀金属板即铝基板10相同。

[0164]

在设置有金属基板35时,无需调整要施加的电流或电压,只要施加确定的电流值的电流或电压值的电压即可。此时,通过金属基板35,抑制电流的上升变得急剧而使电流的上升变缓慢,电流增加量在上述范围内。

[0165]

另外,负载部件只要具有导电性且与极氧化处理对象电性并联连接,则并不限定于金属基板35。

[0166]

并且,图15所示的阳极氧化处理装置30及图19所示的阳极氧化处理装置30均设为设置有平板状的铝基板10和对置电极34的结构,但并不限定于此。例如,也可以为具有将阳极氧化处理对象即铝基板10卷取的供电盘和与供电盘对置设置的对置电极的结构。进而,也可以为如下结构:配置多个供电盘并使其通过多个供电盘,重复阳极氧化处理而实施多次。

[0167]

虽实施多次阳极氧化处理,但如上所述,在第1次阳极氧化处理中能够利用以往公

知的方法。此时,作为阳极氧化处理,从提高贯穿孔排列的规则性,保证各向异性导电性部件的各向异性导电性的观点考虑,利用自我规则化法或恒定电压处理为优选。

[0168]

其中,关于阳极氧化处理的自我规则化法及恒定电压处理,能够实施与记载于日本特开2008

‑

270158号公报的[0056]~[0108]段及[图3]中的各处理相同的处理。

[0169]

<阳极氧化处理>

[0170]

阳极氧化处理中的电解液的平均流速优选0.5~20.0m/min,更优选1.0~15.0m/min,进一步优选2.0~10.0m/min。

[0171]

并且,使电解液在上述条件下流动的方法并无特别限定,例如,可利用搅拌器等通常的搅拌装置。尤其,若使用能够以数字显示控制搅拌速度的搅拌器,则能够控制平均流速,因此优选。作为这种搅拌装置,例如,可举出“磁力搅拌器hs

‑

50d(as one corporation.制)”等。

[0172]

关于阳极氧化处理,例如能够利用在酸浓度1~10质量%的溶液中,将铝基板作为阳极来通电的方法。

[0173]

作为用于阳极氧化处理的溶液,优选酸溶液,更优选硫酸、磷酸、铬酸、草酸、磺酰胺酸、苯磺酸、氨基磺酸、乙醇酸、酒石酸、苹果酸、柠檬酸等,其中尤其优选硫酸、磷酸、草酸。这些酸能够单独使用或组合两种以上来使用。

[0174]

阳极氧化处理的条件根据所使用的电解液而发生各种变化,因此无法一概而论,但通常优选电解液浓度为0.1~20质量%、液温为

‑

10~30℃、电流密度为0.01~20a/dm2、电压为3~300v、电解时间为0.5~30小时,更优选电解液浓度为0.5~15质量%、液温为

‑

5~25℃、电流密度为0.05~15a/dm2、电压为5~250v、电解时间为1~25小时,进一步优选电解液浓度为1~10质量%、液温为0~20℃、电流密度为0.1~10a/dm2、电压为10~200v、电解时间为2~20小时。

[0175]

在上述阳极氧化处理工序中,从以将各向异性导电性部件20如图13所示卷取在规定直径及规定宽度的卷芯21的形状供给的观点考虑,通过阳极氧化处理形成的阳极氧化膜的平均厚度优选30μm以下,更优选5~20μm。另外,关于平均厚度,利用聚焦离子束(focused ion beam:fib)沿厚度方向对阳极氧化膜进行切削加工,通过场发射扫描电子显微镜(field emission scanning electron microscope:fe

‑

sem),拍摄其剖面的表面照片(倍率5万倍),并将测定10处的平均值作为平均厚度来算出。

[0176]

〔保持工序〕

[0177]

各向异性导电性部件的制造方法可具有保持工序。保持工序为如下工序:在上述阳极氧化处理工序之后,在选自1v以上且未达上述阳极氧化处理工序中的电压的30%的范围的保持电压的95%以上且105%以下的电压下保持合计5分钟以上。换言之,保持工序为如下工序:在上述阳极氧化处理工序之后,在选自1v以上且未达上述阳极氧化处理工序中的电压的30%的范围的保持电压的95%以上且105%以下的电压下实施保持合计5分钟以上的电解处理。

[0178]

其中,“阳极氧化处理中的电压”为施加于铝基板与对置电极之间的电压,例如,若基于阳极氧化处理的电解时间为30分钟,则为30分钟期间保持的电压的平均值。

[0179]

从将阻挡层的厚度相对于阳极氧化膜的侧壁厚度即微孔的深度控制在适当厚度的观点考虑,保持工序中的电压优选阳极氧化处理中的电压的5%以上且25%以下,更优选

5%以上且20%以下。

[0180]

并且,从进一步提高面内均匀性的理由考虑,保持工序中的保持时间的合计优选5分钟以上且20分钟以下,更优选5分钟以上且15分钟以下,进一步优选5分钟以上且10分钟以下。

[0181]

并且,保持工序中的保持时间为合计5分钟以上即可,优选连续5分钟以上。

[0182]

进而,保持工序中的电压可以设定为从阳极氧化处理工序中的电压连续或阶段性(阶梯状)降低至保持工序中的电压,从进一步提高面内均匀性的理由考虑,优选在结束阳极氧化处理工序之后,在1秒以内设定为上述保持电压的95%以上且105%以下的电压。

[0183]

关于上述保持工序,例如也能够通过在结束上述阳极氧化处理工序时降低电解电位而与上述阳极氧化处理工序连续进行。

[0184]

在上述保持工序中,关于除了电解电位以外的条件,能够采用与上述以往公知的阳极氧化处理相同的电解液及处理条件。

[0185]

尤其,连续实施保持工序与阳极氧化处理工序时,优选使用相同的电解液进行处理。

[0186]

〔阻挡层去除工序〕

[0187]

阻挡层去除工序例如为使用包含氢过电压比铝更高的金属m1的离子的碱水溶液来去除阳极氧化膜的阻挡层的工序。

[0188]

通过上述阻挡层去除工序,阻挡层被去除,且如图5所示,在微孔12的底部形成由金属m1构成的金属层15a。

[0189]

其中,氢过电压(hydrogen overvoltage)表示产生氢所需的电压,例如,铝(al)的氢过电压为

‑

1.66v(journal of the chemical society of japan,1982,(8),1305

‑

1313页)。另外,以下示出氢过电压比铝更高的金属m1的例子及其氢过电压的值。

[0190]

<金属m1及氢(1n h2so4)过电压>

[0191]

·

铂(pt):0.00v

[0192]

·

金(au):0.02v

[0193]

·

银(ag):0.08v

[0194]

·

镍(ni):0.21v

[0195]

·

铜(cu):0.23v

[0196]

·

锡(sn):0.53v

[0197]

·

锌(zn):0.70v

[0198]

在本发明中,从在后述的阳极氧化处理工序中与所要填充的金属m2引起取代反应且对填充至微孔的内部的金属的电特性带来的影响少的理由考虑,在上述阻挡层去除工序中使用的金属m1优选离子化倾向比金属填充工序中使用的金属m2更高的金属。

[0199]

具体而言,将铜(cu)用作金属填充工序的金属m2时,作为在上述阻挡层去除工序中使用的金属m1,例如可举出zn、fe、ni、sn等,其中,优选使用zn、ni,更优选使用zn。

[0200]

并且,将ni用作金属填充工序的金属m2时,作为在上述阻挡层去除工序中使用的金属m1,例如可举出zn、fe等,其中,优选使用zn。

[0201]

使用包含这种金属m1的离子的碱水溶液来去除阻挡层的方法并无特别限定,例如可举出与以往公知的化学蚀刻处理相同的方法。

[0202]

<化学蚀刻处理>

[0203]

关于通过化学蚀刻处理去除阻挡层,例如,能够通过将阳极氧化处理工序后的结构物浸渍于碱水溶液,在微孔的内部填充碱水溶液之后,使阳极氧化膜的微孔的开口部侧的表面与ph(氢离子指数)缓冲液接触的方法等,仅使阻挡层选择性溶解。

[0204]

其中,作为包含上述金属m1的离子的碱水溶液,优选使用选自由氢氧化钠、氢氧化钾及氢氧化锂组成的组中的至少一种碱的水溶液。并且,碱水溶液的浓度优选0.1~5质量%。碱水溶液的温度优选10~60℃,进一步优选15~45℃,进一步优选20~35℃。

[0205]

具体而言,例如,可优选地使用50g/l、40℃的磷酸水溶液、0.5g/l、30℃的氢氧化钠水溶液、0.5g/l、30℃的氢氧化钾水溶液等。

[0206]

另外,作为ph缓冲液,能够适当使用与上述碱水溶液对应的缓冲液。

[0207]

并且,碱水溶液中的浸渍时间优选5~120分钟,更优选8~120分钟,进一步优选8~90分钟,尤其优选10~90分钟。其中,优选10~60分钟,更优选15~60分钟。

[0208]

〔阻挡层去除工序的另一例〕

[0209]

阻挡层去除工序除了上述以外,也可以为去除阳极氧化膜的阻挡层并在微孔的底部暴露铝基板的一部分的工序。

[0210]

此时,去除阻挡层的方法并无特别限定,例如,可举出在比阳极氧化处理工序的阳极氧化处理中的电位更低的电位对阻挡层进行电化学溶解的方法(以下,也称为“电解去除处理”。);通过蚀刻去除阻挡层的方法(以下,也称为“蚀刻去除处理”。);组合这些的方法(尤其,在实施电解去除处理之后,通过蚀刻去除处理去除残存的阻挡层的方法);等。

[0211]

〈电解去除处理〉

[0212]

电解去除处理只要为在比阳极氧化处理工序的阳极氧化处理中的电位(电解电位)更低的电位实施的电解处理,则并无特别限定。

[0213]

关于电解溶解处理,例如能够通过在结束阳极氧化处理工序时降低电解电位而与阳极氧化处理连续实施。

[0214]

在电解去除处理中,关于除了电解电位以外的条件,能够采用与上述的以往公知的阳极氧化处理相同的电解液及处理条件。

[0215]

尤其,如上所述,连续实施电解去除处理和阳极氧化处理时,优选使用相同的电解液来进行处理。

[0216]

(电解电位)

[0217]

电解去除处理中的电解电位优选连续或阶段性(阶梯状)降低至比阳极氧化处理中的电解电位更低的电位。

[0218]

其中,从阻挡层的耐电压的观点考虑,阶段性降低电解电位时的降低幅度(阶梯宽度)优选10v以下,更优选5v以下,进一步优选2v以下。

[0219]

并且,从生产性等的观点考虑,连续或阶段性降低电解电位时的电压降低速度优选均为1v/秒以下,更优选0.5v/秒以下,进一步优选0.2v/秒以下。

[0220]

〈蚀刻去除处理〉

[0221]

蚀刻去除处理并无特别限定,可以为使用酸水溶液或碱水溶液来溶解的化学蚀刻处理,也可以为干式蚀刻处理。

[0222]

(化学蚀刻处理)

[0223]

关于通过化学蚀刻处理去除阻挡层,例如为将阳极氧化处理工序后的结构物浸渍于酸水溶液或碱水溶液,在微孔的内部填充酸水溶液或碱水溶液之后,使阳极氧化膜的微孔的开口部侧的表面与ph(氢离子指数)缓冲液接触的方法等,能够仅使阻挡层选择性溶解。

[0224]

其中,使用酸水溶液时,优选使用硫酸、磷酸、硝酸、盐酸等无机酸或这些的混合物的水溶液。并且,酸水溶液的浓度优选1质量%~10质量%。酸水溶液的温度优选15℃~80℃,进一步优选20℃~60℃,进一步优选30℃~50℃。

[0225]

另一方面,使用碱水溶液时,优选使用选自由氢氧化钠、氢氧化钾及氢氧化锂组成的组中的至少一种碱的水溶液。并且,碱水溶液的浓度优选0.1质量%~5质量%。碱水溶液的温度优选10℃~60℃,进一步优选15℃~45℃,进一步优选20℃~35℃。另外,碱水溶液中可以含有锌及其他金属。

[0226]

具体而言,例如,可优选地使用50g/l、40℃的磷酸水溶液、0.5g/l、30℃的氢氧化钠水溶液、0.5g/l、30℃的氢氧化钾水溶液等。

[0227]

另外,作为ph缓冲液,能够适当使用与上述的酸水溶液或碱水溶液对应的缓冲液。

[0228]

并且,酸水溶液或碱水溶液中的浸渍时间优选8分钟~120分钟,更优选10分钟~90分钟,进一步优选15分钟~60分钟。

[0229]

(干式蚀刻处理)

[0230]

在干式蚀刻处理中,例如优选使用cl2/ar混合气体等气体种类。

[0231]

〔金属填充工序〕

[0232]

金属填充工序为如下工序:在上述阻挡层去除工序之后,利用电解电镀在阳极氧化膜的微孔的内部例如填充金属m2作为导电性材料。通过金属填充工序形成导电性的导电通路。

[0233]

<金属m2>

[0234]

上述金属m2优选电阻率为103ω

·

cm以下的材料,作为其具体例,可优选地例示金(au)、银(ag)、铜(cu)、铝(al)、镁(mg)、镍(ni)、锌(zn)等。

[0235]

其中,从导电性的观点考虑,优选cu、au、al、ni,更优选cu、au,进一步优选cu。

[0236]

另外,在金属填充工序中填充金属,但导电通路并不限定于金属,只要为导电性材料,则也可以为氧化物导电体等。因此,例如也可以填充掺杂有铟的锡氧化物(ito)等来代替金属。

[0237]

然而,由于相较于氧化物导电体,金属的延展性等优异而容易变形,因此接合时的压缩也容易使其变形,因此导电通路优选由金属构成。在金属中,由于cu、au为除了上述导电性以外,也具有通过压缩而容易变形的性质的金属,因此更优选,若考虑成本等,则进一步优选cu。

[0238]

<金属填充方法>

[0239]

作为将上述金属m2填充于微孔的内部的电镀处理的方法,例如,能够利用电解电镀法或无电解电镀法。

[0240]

其中,利用用于着色等的以往公知的电解电镀法,难以将金属选择性在孔中以高纵横析出(生长)。认为这是出于如下理由:析出金属在孔内被消耗,因此即使电解进行一定时间以上,电镀也未生长。

[0241]

因此,在本发明的制造方法中,通过电解电镀法填充金属的情况下,需要在脉冲电解或恒电位电解时设置暂停时间。暂停时间需要10秒以上,优选30~60秒。

[0242]

并且,为了促进电解液的搅拌,也优选施加超声波。

[0243]

进而,电解电压通常为20v以下,优选10v以下,优选预先测定要使用的电解液中的目的金属的析出电位,并在该电位 1v以内进行恒电位电解。另外,进行恒电位电解时,优选能够同时使用循环伏安法,能够利用solartron metrology、bas inc.、hokuto denko corporation、ivium technologies等的恒电位装置。

[0244]

电镀液能够使用以往公知的电镀液。

[0245]

具体而言,在析出铜时,通常使用硫酸铜水溶液,硫酸铜的浓度优选1~300g/l,更优选100~200g/l。并且,若向电解液中添加盐酸,则能够促进析出。此时,盐酸浓度优选10~20g/l。

[0246]

并且,析出金时,优选使用四氯金的硫酸溶液,通过交流电解进行电镀。

[0247]

另外,在无电解电镀法中,在由纵横高的微孔构成的孔中填满金属需要长时间,因此在本发明的制造方法中,优选通过电解电镀法填充金属。

[0248]

认为在本发明中,通过上述阻挡层去除工序去除阻挡层,且在微孔的底部形成有上述的由金属m1构成的金属层,因此,如上所述,抑制因电镀液导致产生氢气而变得容易进行通过电镀处理的金属填充。

[0249]

〔基板去除工序〕

[0250]

基板去除工序为在金属填充工序之后去除上述阀金属板即铝基板的工序。去除铝基板的方法并无特别限定,例如,可优选地举出通过溶解去除的方法等。另外,作为阀金属板,以铝基板为例进行说明,但被去除的基板为阀金属板,并不限定于铝基板。

[0251]

<铝基板的溶解>

[0252]

在上述铝基板的溶解中,优选使用不易溶解阳极氧化膜但容易溶解铝的处理液。

[0253]

这种处理液对铝的溶解速度优选1μm/分钟以上,更优选3μm/分钟以上,进一步优选5μm/分钟以上。同样地,对阳极氧化膜的溶解速度优选变为0.1nm/分钟以下,更优选变为0.05nm/分钟以下,进一步优选变为0.01nm/分钟以下。

[0254]

具体而言,优选包含至少一种离子化倾向比铝更低的金属化合物且ph成为4以下或8以上的处理液,更优选该ph为3以下或9以上为,进一步优选2以下或10以上。

[0255]

作为溶解铝的处理液,将酸或碱水溶液作为基质,优选例如配合有锰、锌、铬、铁、镉、钴、镍、锡、铅、锑、铋、铜、汞、银、钯、铂、金的化合物(例如,氯铂酸)、这些的氟化物、这些的氯化物等混合物。

[0256]

其中,优选酸水溶液基质,优选混合氯化物。

[0257]

尤其,从处理范围的观点考虑,优选对盐酸水溶液混合有氯化汞的处理液(盐酸/氯化汞)、对盐酸水溶液混合有氯化铜的处理液(盐酸/氯化铜)。

[0258]

另外,溶解铝的处理液的组成并无特别限定,例如能够使用溴/甲醇混合物、溴/乙醇混合物及王水等。

[0259]

并且,溶解铝的处理液的酸或碱浓度优选0.01~10mol/l,更优选0.05~5mol/l。

[0260]

进而,使用溶解铝的处理液的处理温度优选

‑

10℃~80℃,优选0℃~60℃。

[0261]

并且,上述铝基板的溶解通过使上述金属填充工序后的铝基板与上述处理液接触

来进行。接触方法并无特别限定,例如可举出浸渍法、喷涂法。其中,优选浸渍法。作为此时的接触时间,优选10秒~5小时,更优选1分钟~3小时。

[0262]

〔突出工序〕

[0263]

为了设置突出部,具有表面突出工序及背面突出工序中的至少1个工序。

[0264]

其中,表面突出工序为如下工序:在上述金属填充工序之后且在上述基板去除工序之前,将上述阳极氧化膜的未设置有上述铝基板一侧的表面沿厚度方向去除一部分,使在上述金属填充工序中填充的上述金属m2比上述阳极氧化膜的表面更突出。

[0265]

并且,背面突出工序为如下工序:在上述基板去除工序之后,将上述阳极氧化膜的设置有上述铝基板一侧的表面沿厚度方向去除一部分,使在上述金属填充工序中填充的上述金属m2比上述阳极氧化膜的表面更突出。

[0266]

关于去除突出工序中的阳极氧化膜的一部分,例如能够通过使具有填充有金属的微孔的阳极氧化膜接触不溶解上述金属m1及金属m2(尤其金属m2)但溶解阳极氧化膜即溶解氧化铝的酸水溶液或碱水溶液来进行。接触方法并无特别限定,例如可举出浸渍法、喷涂法。其中,优选浸渍法。

[0267]

使用酸水溶液时,优选使用硫酸、磷酸、硝酸、盐酸等无机酸或这些的混合物的水溶液。其中,优选不含有铬酸的水溶液在安全性优异这一点。酸水溶液的浓度优选1~10质量%。酸水溶液的温度优选25~60℃。

[0268]

并且,使用碱水溶液时,优选使用选自由氢氧化钠、氢氧化钾及氢氧化锂组成的组中的至少一种碱的水溶液。碱水溶液的浓度优选0.1~5质量%。碱水溶液的温度优选20~35℃。

[0269]

具体而言,例如,可优选地使用50g/l、40℃的磷酸水溶液、0.5g/l、30℃的氢氧化钠水溶液或0.5g/l、30℃的氢氧化钾水溶液。

[0270]

酸水溶液或碱水溶液中的浸渍时间优选8~120分钟,更优选10~90分钟,进一步优选15~60分钟。其中,重复短时间的浸渍处理时,浸渍时间表示各浸渍时间的合计。另外,可以在各浸渍处理期间实施清洗处理。

[0271]

〔树脂层形成工序〕

[0272]

从提高所制作的各向异性导电性部件20的搬送性的理由考虑,优选具有上述树脂层形成工序。

[0273]

其中,树脂层形成工序为在上述金属填充工序之后(具有上述表面突出工序的情况下为表面突出工序之后)且在上述基板去除工序之前,在上述阳极氧化膜的未设置有上述铝基板一侧的表面设置树脂层的工序。

[0274]

作为构成上述树脂层的树脂材料,具体而言,例如能够举出乙烯系共聚物、聚酰胺树脂、聚酯树脂、聚氨酯树脂、聚烯烃系树脂、丙烯酸系树脂及纤维素系树脂等,从搬送性的观点和易于用作各向异性导电性部件的观点考虑,上述树脂层优选能够剥离的带粘合层的膜,更优选粘合性会因加热处理或紫外线曝光处理变弱且能够剥离的带粘合层的膜。

[0275]

上述带粘合层的膜并无特别限定,可举出热剥离型的树脂层及紫外线(ultraviolet:uv)剥离型的树脂层等。

[0276]

其中,热剥离型的树脂层为在常温下具有粘合力,仅通过加热即能够容易剥离,大多数为主要使用发泡性的微胶囊等。

[0277]

并且,作为构成粘合层的粘合剂,具体而言,例如可举出橡胶系粘合剂、丙烯酸系粘合剂、乙烯基烷基醚系粘合剂、硅酮系粘合剂、聚酯系粘合剂、聚酰胺系粘合剂、氨酯系粘合剂、苯乙烯

‑

二烯嵌段共聚物系粘合剂等。

[0278]

并且,uv剥离型的树脂层具有uv固化型的粘接层,并且因固化失去粘合力而能够剥离。

[0279]

作为uv固化型的粘接层,可举出对基质聚合物的聚合物侧链或主链中或者主链末端导入碳

‑

碳双键的聚合物等。作为具有碳

‑

碳双键的基质聚合物,优选将丙烯酸系聚合物作为基本骨架。

[0280]

进而,丙烯酸系聚合物为了使其交联,根据需要也能够包含多官能性单体等来作为共聚用单体成分。

[0281]

具有碳

‑

碳双键的基质聚合物能够单独使用,也能够配合使用uv固化性的单体或低聚物。

[0282]

为了通过uv照射来固化,uv固化型的粘接层优选同时使用光聚合引发剂。作为光聚合引发剂,可举出苯偶姻醚系化合物;缩酮系化合物;芳香族磺酰氯系化合物;光敏肟系化合物;二苯甲酮系化合物;噻吨酮系化合物;樟脑醌;卤化酮;酰基膦氧化物;酰基膦酸酯等。

[0283]

作为热剥离型的树脂层的市售品,例如可举出ws5130c02、ws5130c10等interimer〔注册商标〕胶带(nitta corporation制);somatac〔注册商标〕te系列(somar corporation制);no.3198、no.3198ls、no.3198m、no.3198ms、no.3198h、no.3195、no.3196、no.3195m、no.3195ms、no.3195h、no.3195hs、no.3195v、no.3195vs、no.319y

‑

4l、no.319y

‑

4ls、no.319y

‑

4m、no.319y

‑

4ms、no.319y

‑

4h、no.319y

‑

4hs、no.319y

‑

4lsc、no.31935ms、no.31935hs、no.3193m、no.3193ms等revalpha〔注册商标〕系列(nitto denko corporation制);等。

[0284]

作为uv剥离型的树脂层的市售品,例如,能够利用elp du

‑

300、elp du

‑

2385ks、elp du

‑

2187g、elp nbd

‑

3190k、elp ue

‑

2091j等elep holder〔注册商标〕(nitto denko corporation制);adwill d

‑

210、adwill d

‑

203、adwill d

‑

202、adwill d

‑

175、adwill d

‑

675(均为lintec corporation制);sumilite〔注册商标〕fls的n8000系列(sumitomo bakelite co.,ltd.制);uc353ep

‑

110(furukawa electric co.,ltd.制);等切割胶带、elp rf

‑

7232db、elp ub

‑

5133d(均为nitto denko corporation制);sp

‑

575b

‑

150、sp

‑

541b

‑

205、sp

‑

537t

‑

160、sp

‑

537t

‑

230(均为furukawa electric co.,ltd.制);等背磨胶带。

[0285]

并且,上述贴附带粘合层的膜的方法并无特别限定,能够利用以往公知的表面保护胶带贴附装置及层压机来贴附。

[0286]

〔卷取工序〕

[0287]

从进一步提高所制作的各向异性导电性部件20的搬送性的理由考虑,优选具有在上述任意的树脂层形成工序之后在具有上述树脂层的状态下以卷状卷取各向异性导电性部件20的卷取工序。

[0288]

其中,上述卷取工序中的卷取方法并无特别限定,例如,可举出卷取在规定直径及规定宽度的卷芯21(参考图13)的方法。

[0289]

并且,从上述卷取工序中的卷取容易度的观点考虑,除了树脂层19(参考图14)以

外的各向异性导电性部件20的平均厚度优选30μm以下,更优选5~20μm。另外,关于平均厚度,利用fib(focused ion beam:聚焦离子束)沿厚度方向对除了树脂层以外的各向异性导电性部件20进行切削加工,通过fe

‑

sem(场发射扫描电子显微镜),拍摄其剖面的表面照片(倍率50000倍),并将测定10点的平均值作为平均厚度等方法来算出。

[0290]

〔其他处理工序〕

[0291]

除了上述各工序以外,本发明的制造方法也可以具有国际公开第2015/029881号的[0049]~[0057]段中记载的研磨工序、表面平滑化工序、保护膜形成处理、水洗处理。

[0292]

并且,从制造上的操作性及将各向异性导电性部件20用作各向异性导电性部件的观点考虑,能够适用如下所示的各种工序及形式。

[0293]

<使用临时粘接剂的工序例>

[0294]

在本发明中,也可以具有在通过上述基板去除工序获得各向异性导电性部件20之后,用临时粘接剂(temporary bonding materials)将各向异性导电性部件20恒定在硅晶片上并通过研磨进行薄层化的工序。

[0295]

接着,在薄层化的工序之后,能够在充分清洗表面之后进行上述表面突出工序。

[0296]

接着,能够在突出金属的表面涂布粘接力比之前的临时粘接剂更强的临时粘接剂来恒定在硅晶片上之后,剥离用之前的临时粘接剂粘接的硅晶片,对所剥离的各向异性导电性部件20侧的表面进行上述背面突出工序。

[0297]

<使用石蜡的工序例>

[0298]

在本发明中,也可以具有在通过上述基板去除工序获得各向异性导电性部件20之后,用石蜡将各向异性导电性部件20恒定在硅晶片上,通过研磨进行薄层化的工序。

[0299]

接着,在薄层化的工序之后,能够在充分清洗表面之后进行上述表面突出工序。

[0300]

接着,在突出金属的表面涂布临时粘接剂来恒定在硅晶片上之后,能够通过加热溶解之前的石蜡并剥离硅晶片并对所剥离的各向异性导电性部件20侧的表面进行上述背面突出工序。

[0301]

另外,虽可以使用固态石蜡,但若使用skycoat(nikka seiko co.,ltd.制)等液体石蜡,则能够实现涂布厚度均匀性的提高。

[0302]

<后续进行基板去除处理的工序例>

[0303]

在本发明中,也可以具有在上述金属填充工序之后且在上述基板去除工序之前,用临时粘接剂、石蜡或功能性吸附膜将铝基板恒定在刚性基板(例如,硅晶片、玻璃基板等)之后,通过研磨对上述阳极氧化膜的未设置有上述铝基板一侧的表面进行薄层化的工序。

[0304]

接着,在薄层化的工序之后,能够在充分清洗表面之后进行上述表面突出工序。

[0305]

接着,在突出金属的表面涂布绝缘性材料即树脂材料(例如,环氧树脂、聚酰亚胺树脂等)之后,能够通过与上述方法相同的方法在其表面贴附刚性基板。基于树脂材料的贴附能够如下进行:选择粘接力比基于临时粘接剂等的粘接力变更大,在通过树脂材料进行贴附之后,剥离最初贴附的刚性基板,依次进行上述基板去除工序、研磨工序及背面突出处理工序。

[0306]

另外,作为功能性吸附膜,能够使用q

‑

chuck(注册商标)(maruishi sangyo co.,ltd.制)等。

[0307]

在本发明中,优选各向异性导电性部件20以通过能够剥离的层贴附在刚体基板

(例如,硅晶片、玻璃基板等)的状态作为制品来提供。

[0308]

在这种供给方式中,将各向异性导电性部件20用作接合部件时,将各向异性导电性部件20的表面临时粘接在装置表面,在剥离刚体基板之后将成为连接对象的装置设置于适当的位置来进行加热压接,由此能够通过各向异性导电性部件20接合上下装置。

[0309]

并且,能够剥离的层可以使用热剥离层,也可以使用与玻璃基板的组合的光剥离层。

[0310]

并且,关于上述各工序,各工序能够按单片进行,也能够将铝线圈作为铝料而用网模(web)连续处理。

[0311]

并且,在连续处理的情况下,优选在各工序之间设置适当的清洗工序、干燥工序。

[0312]

通过具有上述各处理工序的制造方法,可获得在源自设置于由铝基板的阳极氧化膜构成的绝缘性基材的微孔的微孔的内部填充金属而成的各向异性导电性部件20。

[0313]

具体而言,通过上述制造方法,能够获得如下各向异性导电性部件:例如,在日本特开2008

‑

270158号公报中记载的各向异性导电性部件即绝缘性基材(具有微孔的铝基板的阳极氧化膜)中,由导电性部件(金属)构成的多个导电通路在彼此绝缘的状态下沿厚度方向贯穿上述绝缘性基材,且以上述各导电通路的一端在上述绝缘性基材的一面暴露,上述各导电通路的另一端在上述绝缘性基材的另一面暴露的状态设置的各向异性导电性部件。

[0314]

进而,如上所述,由于可获得具有笔直的微孔的阳极氧化膜,因此在将导电性材料填充至微孔时,能够获得填充缺陷得到抑制的各向异性导电性部件20。因此,例如在填充金属等导电性材料时,能够获得具有填充缺陷得到抑制的健全的导电通路的各向异性导电性部件。

[0315]

以下,对各向异性导电性部件20进行说明。

[0316]

首先,对用上述制造方法制造的各向异性导电性部件20的一例进行说明。图20是表示本发明的实施方式的各向异性导电性部件的一例的俯视图,图21是表示本发明的实施方式的各向异性导电性部件的一例的示意性剖视图。图21是图20的切断面线ib

‑

ib剖视图。并且,图22是表示使用了本发明的实施方式的各向异性导电性部件的各向异性导电材料的结构的一例的示意性剖视图。

[0317]

如图20及图21所示,如上所述制造的各向异性导电性部件20例如为具备由铝的阳极氧化膜构成的绝缘性基材40和沿绝缘性基材40的厚度方向dt(参考图21)贯穿且以彼此电绝缘的状态设置的多个导电通路16的部件。各向异性导电性部件20进而具备设置于绝缘性基材40的表面40a及背面40b的树脂层44。

[0318]

其中,“彼此电绝缘的状态”表示存在于绝缘性基材的内部的各导电通路在绝缘性基材的内部,各导电通路之间的导通性彼此非常低的状态。

[0319]

关于各向异性导电性部件20,具有导电性的导电通路16彼此电绝缘,导电性在与绝缘性基材40的厚度方向dt(参考图21)正交的方向x上非常低,在厚度方向dt(参考图21)上具有导电性。如此,各向异性导电性部件20为显示各向异性导电性的部件。例如,将各向异性导电性部件20配置成使厚度方向dt(参考图21)与层叠装置60(参考图23)的层叠方向ds(参考图23)匹配。

[0320]

导电通路16由导电性材料构成,并具有导电性。并且,如图20及图21所示,将导电

通路16设置成以彼此电绝缘的状态沿厚度方向dt贯穿绝缘性基材40。

[0321]

进而,如图21所示,导电通路16可以具有从绝缘性基材40的表面40a及背面40b突出的突出部分16a及突出部分16b。各向异性导电性部件20进而可以具备设置于绝缘性基材40的表面40a及背面40b的树脂层44。树脂层44具备粘合性,也赋予接合性。突出部分16a及突出部分16b的长度优选6nm以上,更优选30nm~500nm。

[0322]

并且,在图22及图21中,示出了在绝缘性基材40的表面40a及背面40b具有树脂层44的结构,但并不限定于此,也可以为在绝缘性基材40的至少一个表面具有树脂层44的结构。

[0323]

同样地,图22及图21的导电通路16在两端具有突出部分16a及突出部分16b,但并不限定于此,也可以为在绝缘性基材40的至少具有树脂层44一侧的表面具有突出部分的结构。

[0324]

图21所示的各向异性导电性部件20的厚度h例如为30μm以下。并且,各向异性导电性部件20的ttv(total thickness variation:总厚度变异)优选10μm以下。

[0325]

其中,各向异性导电性部件20的厚度h为如下值:通过场发射扫描电子显微镜以20万倍的倍率观察各向异性导电性部件20,获得各向异性导电性部件20的轮廓形状,在相当于厚度h的区域测定10处的平均值。

[0326]

并且,各向异性导电性部件20的ttv(total thickness variation:总厚度变异)为切断各向异性导电性部件20并观察各向异性导电性部件20的剖面形状来求出的值。

[0327]

如图22所示,各向异性导电性部件20为了进行移送、搬送及搬运以及保管等而设置于支撑体46上。在支撑体46与各向异性导电性部件20之间设置有剥离层47。通过剥离层47可分离地粘接支撑体46与各向异性导电性部件20。如上所述,将各向异性导电性部件20经由剥离层47设置于支撑体46上的物体称为各向异性导电材料28。

[0328]

支撑体46支撑各向异性导电性部件20,例如由硅基板构成。作为支撑体46,除了硅基板以外,例如也能够使用sic、sin、gan及氧化铝(al2o3)等陶瓷基板、玻璃基板、纤维强化塑胶基板以及金属基板。纤维强化塑胶基板中也包括印刷配线基板即fr

‑

4(flame retardant type 4:阻燃类型4)基板等。

[0329]

并且,作为支撑体46,能够使用具有挠性且透明的支撑体。作为具有挠性且透明的支撑体46,例如可举出pet(聚对酞酸乙二酯)、聚环烯烃、聚碳酸酯、丙烯酸树脂、pen(聚萘二甲酸乙二酯)、pe(聚乙烯)、pp(聚丙烯)、聚苯乙烯、聚氯乙烯、聚偏二氯乙烯及tac(三乙酸纤维素)等塑胶膜。

[0330]

其中,透明表示在用于对位的波长的光中透射率为80%以上。因此,虽然透射率在波长400~800nm的整个可见光区域可以较低,但透射率在波长400~800nm的整个可见光区域优选80%以上。透射率可通过分光光度计测定。

[0331]

剥离层47优选层叠有支撑层48和剥离剂49。剥离剂49与各向异性导电性部件20相接,以剥离层47为起点,支撑体46与各向异性导电性部件20分离。在各向异性导电材料28中,例如,通过以预先确定的温度加热,剥离剂49的粘接力减弱,从各向异性导电性部件20去除支撑体46。

[0332]

关于剥离剂49,例如,能够使用nitto denko corporation制revalpha(注册商标)及somar corporation制somatac(注册商标)等。

[0333]

并且,可以在树脂层44设置保护层(未图示)。保护层用于保护结构体表面不受损伤等,因此优选易剥离胶带。作为保护层,例如也可以使用带粘合层的膜。

[0334]

作为带粘合层的膜,例如,能够使用以在聚乙烯树脂膜表面形成有粘合剂层的sunytect〔注册商标〕(sun a.kaken co.,ltd.制)、在聚对酞酸乙二酯树脂膜表面形成有粘合剂层的e

‑

mask〔注册商标〕(nitto denko corporation制)、在聚对酞酸乙二酯树脂膜表面形成有粘合剂层的mastack〔注册商标〕(fujimori kogyo co.,ltd.制)等系列名销售的市售品。

[0335]

并且,贴附带粘合层的膜的方法并无特别限定,能够利用以往公知的表面保护胶带贴附装置及层压机来贴附。

[0336]

以下,对各向异性导电性部件20的结构进行更具体说明。

[0337]

〔绝缘性基材〕

[0338]

绝缘性基材的物性及组成如上所述。

[0339]

绝缘性基材40的厚度ht优选在1~1000μm的范围内,更优选在5~500μm的范围内,进一步优选在10~300μm的范围内。若绝缘性基材的厚度在该范围,则绝缘性基材的操作性变良好。

[0340]

绝缘性基材40的厚度ht为如下值:利用聚焦离子束(focused ion beam:fib)沿厚度方向dt对绝缘性基材40进行切削加工,通过场发射扫描电子显微镜以20万倍的倍率观察其剖面,由此获得绝缘性基材40的轮廓形状,在相当于厚度ht的区域测定10处的平均值。

[0341]

绝缘性基材中的各微孔的间隔优选5nm~800nm,更优选10nm~200nm,进一步优选50nm~140nm。若绝缘性基材中的各微孔的间隔在该范围,则绝缘性基材作为绝缘性隔壁而充分发挥功能。微孔的间隔与导电通路的间隔相同。

[0342]

其中,微孔的间隔即导电通路的间隔表示相邻导电通路之间的宽度w(参考图21),并表示通过场发射扫描电子显微镜以20万倍的倍率观察各向异性导电性部件的剖面且在10处测定相邻导电通路之间的宽度的平均值。

[0343]

〔导电通路〕

[0344]

导电通路由填充至微孔的导电性材料构成。导电性材料只要为电阻率103ωcm以下的材料,则并不特别限定,可使用金属等。作为金属的具体例,可优选地例示金(au)、银(ag)、铜(cu)、铝(al)、镁(mg)及镍(ni)等。除了金属以外,也可优选地例示掺杂有铟的锡氧化物(ito)等。另外,从导电性的观点考虑,优选铜、金、铝及镍,更优选铜及金。

[0345]

<突出部分>

[0346]

将各向异性导电性部件与电极通过压接等方法进行电连接或物理性接合时,从能够充分确保突出部分被压坏时的面方向的绝缘性的理由考虑,导电通路的突出部分的纵横比(突出部分的高度/突出部分的直径)优选0.5以上且未达50,更优选0.8~20,进一步优选1~10。

[0347]

并且,从追随连接对象的半导体部件的表面形状的观点考虑,导电通路的突出部分的高度如上所述优选20nm以上,更优选100nm~500nm。

[0348]

导电通路的突出部分的高度表示通过场发射扫描电子显微镜以2万倍的倍率观察各向异性导电性部件的剖面且在10处测定导电通路的突出部分的高度的平均值。

[0349]

导电通路的突出部分的直径表示通过场发射扫描电子显微镜观察各向异性导电

性部件的剖面且在10处测定导电通路的突出部分的直径的平均值。

[0350]

如上所述,导电通路16通过绝缘性基材40以彼此电绝缘的状态存在,但其密度优选2万个/mm2以上,更优选200万个/mm2以上,进一步优选1000万个/mm2以上,尤其优选5000万个/mm2以上,最优选1亿个/mm2以上。

[0351]

进而,相邻的各导电通路16的中心间距离p(参考图20)优选20nm~500nm,更优选40nm~200nm,进一步优选50nm~140nm。

[0352]

〔树脂层〕

[0353]

如上所述,树脂层设置于绝缘性基材的表面和背面且如上所述埋设导电通路的突出部。即,树脂层包覆从绝缘性基材突出的导电通路的端部,并保护突出部。

[0354]

树脂层通过上述树脂层形成工序形成。树脂层例如优选在50℃~200℃的温度范围内显示流动性且在200℃以上固化。

[0355]

树脂层通过上述树脂层形成工序形成,但也能够使用以下所示的树脂剂的组成。以下,对树脂层的组成进行说明。树脂层含有高分子材料。树脂层可以含有抗氧化材料。

[0356]

<高分子材料>

[0357]

作为树脂层中包含的高分子材料,并无特别限定,从能够有效填埋半导体芯片或半导体晶片与各向异性导电性部件之间的间隙,更加提高半导体芯片或半导体晶片的密合性的理由考虑,优选热固性树脂。

[0358]

作为热固性树脂,具体而言,例如可举出环氧树脂、酚醛树脂、聚酰亚胺树脂、聚酯树脂、聚氨酯树脂、双马来亚酰胺树脂、三聚氰胺树脂、异氰酸酯系树脂等。

[0359]

其中,从进一步提高绝缘可靠性,耐药品性优异的理由考虑,优选使用聚酰亚胺树脂和/或环氧树脂。

[0360]

<抗氧化材料>

[0361]

作为树脂层中包含的抗氧化材料,具体而言,例如可举出1,2,3,4

‑

四唑、5

‑

氨基

‑

1,2,3,4

‑

四唑、5

‑

甲基

‑

1,2,3,4

‑

四唑、1h

‑

四唑

‑5‑

乙酸、1h

‑

四唑

‑5‑

琥珀酸、1,2,3

‑

三唑、4

‑

氨基

‑

1,2,3

‑

三唑、4,5

‑

二氨基

‑

1,2,3

‑

三唑、4

‑

羧基

‑

1h

‑

1,2,3

‑

三唑、4,5

‑

二羧基

‑

1h

‑

1,2,3

‑

三唑、1h

‑

1,2,3

‑

三唑

‑4‑

乙酸、4

‑

羧基

‑5‑

羧基甲基

‑

1h

‑

1,2,3

‑

三唑、1,2,4

‑

三唑、3

‑

氨基

‑

1,2,4

‑

三唑、3,5

‑

二氨基

‑

1,2,4

‑

三唑、3

‑

羧基

‑

1,2,4

‑

三唑、3,5

‑

二羧基

‑

1,2,4

‑

三唑、1,2,4

‑

三唑

‑3‑

乙酸、1h

‑

苯并三唑、1h

‑

苯并三唑

‑5‑

羧酸、苯并呋喃、2,1,3

‑

苯并噻唑、邻苯二胺、间苯二胺、儿茶酚、邻氨基苯酚、2

‑

巯基苯并噻唑、2

‑

巯基苯并咪唑、2

‑

巯基苯并噁唑、三聚氰胺及这些的衍生物。

[0362]

其中,优选苯并三唑及其衍生物。

[0363]

作为苯并三唑衍生物,可举出在苯并三唑的苯环上具有羟基、烷氧基(例如,甲氧基、乙氧基等)、氨基、硝基、烷基(例如,甲基、乙基、丁基等)、卤素原子(例如,氟、氯、溴、碘等)等的取代苯并三唑。并且,也能够举出萘三唑、萘双三唑和同样经取代的取代萘三唑、取代萘双三唑等。

[0364]

并且,作为树脂层中包含的抗氧化材料的其他例子,可举出通常的抗氧化剂即高级脂肪酸、高级脂肪酸铜、酚化合物、烷醇胺、氢醌类、铜螯合剂、有机胺、有机铵盐等。

[0365]

树脂层中包含的抗氧化材料的含量并无特别限定,从防腐蚀效果的观点考虑,相对于树脂层的总质量优选0.0001质量%以上,更优选0.001质量%以上。并且,从在正式接

合工序中获得适当电阻的理由考虑,优选5.0质量%以下,更优选2.5质量%以下。

[0366]

<防迁移材料>

[0367]

从通过捕获树脂层中可含有的金属离子、卤素离子以及源自半导体芯片及半导体晶片的金属离子而进一步提高绝缘可靠性的理由考虑,树脂层优选含有防迁移材料。

[0368]

作为防迁移材料,例如,能够使用离子交换体,具体而言能够使用阳离子交换体与阴离子交换体的混合物,或能够仅使用阳离子交换体。

[0369]

其中,关于阳离子交换体及阴离子交换体,例如分别能够从后述的无机离子交换体及有机离子交换体中适当选择。

[0370]

(无机离子交换体)

[0371]

作为无机离子交换体,例如可举出以含氢氧化锆为代表的金属的含氢氧化物。

[0372]

作为金属的种类,例如,除了锆以外,还已知有铁、铝、锡、钛、锑、镁、铍、铟、铬、铋等。

[0373]

其中,锆系金属对阳离子的cu

2

、al

3

具有交换能力。并且,铁系金属也对ag

、cu

2

具有交换能力。同样地,锡系、钛系、锑系金属为阳离子交换体。

[0374]

另一方面,铋系金属对阴离子的cl

‑

具有交换能力。

[0375]

并且,锆系金属根据制造条件显示阴离子的交换能力。铝系、锡系金属也相同。

[0376]

作为除这些以外的无机离子交换体,已知有以磷酸锆为代表的多价金属的酸性盐、以钼酸铵为代表的杂多酸盐、非溶性亚铁氰化物等合成物。

[0377]

这些无机离子交换体的一部分已在销售,例如已知有toagosei co.,ltd.的商品名“ixe”中的各种等级。

[0378]

另外,除了合成品以外,也能够使用天然沸石或蒙脱石等无机离子交换体的粉末。

[0379]

(有机离子交换体)

[0380]

关于有机离子交换体,可举出作为阳离子交换体具有磺酸基的交联聚苯乙烯,除此以外,也可举出具有羧酸基、膦酸基或次膦酸基的交联聚苯乙烯。

[0381]

并且,可举出作为阴离子交换体具有季铵基、季鏻基或叔锍基的交联聚苯乙烯。

[0382]

这些无机离子交换体及有机离子交换体可考虑欲捕捉的阳离子、阴离子的种类、对该离子的交换容量来适当选择即可。当然,不用说也可以混合使用无机离子交换体和有机离子交换体。

[0383]

电子元件的制造工序中包括加热工序,因此优选无机离子交换体。

[0384]

并且,关于防迁移材料与上述高分子材料的混合比,例如,从机械强度的观点考虑,优选将防迁移材料设为10质量%以下,更优选将防迁移材料设为5质量%以下,进一步优选进而将防迁移材料设为2.5质量%以下。并且,从抑制将半导体芯片或半导体晶片与各向异性导电性部件接合时的迁移的观点考虑,优选将防迁移材料设为0.01质量%以上。

[0385]

<无机填充剂>

[0386]

树脂层优选含有无机填充剂。

[0387]

作为无机填充剂,无特别限制,能够从公知的无机填充剂中适当选择,例如可举出高岭土、硫酸钡、钛酸钡、氧化硅粉末、微粉状氧化硅、气相二氧化硅、无定形二氧化硅、结晶性二氧化硅、熔融二氧化硅、球状二氧化硅、滑石、粘土、碳酸镁、碳酸钙、氧化铝、氢氧化铝、云母、氮化铝、氧化锆、氧化钇、碳化硅、氮化硅等。

[0388]

从防止无机填充剂流入导电通路之间,进一步提高导通可靠性的理由考虑,无机填充剂的平均粒径优选大于各导电通路的间隔。

[0389]

无机填充剂的平均粒径优选30nm~10μm,更优选80nm~1μm。

[0390]

其中,关于平均粒径,将利用激光衍射散射式粒径测定装置(nikkiso co.,ltd.制microtrac mt3300)测定的一次粒径作为平均粒径。

[0391]

<固化剂>

[0392]

树脂层可以含有固化剂。

[0393]

含有固化剂时,从抑制与连接对象的半导体芯片或半导体晶片的表面形状的接合不良的观点考虑,更优选含有在常温下为液体的固化剂而不使用在常温下为固体的固化剂。

[0394]

其中,“在常温下为固体”表示在25℃为固体,例如表示熔点为高于25℃的温度的物质。

[0395]

作为固化剂,具体而言,例如可举出二氨基二苯甲烷、二氨基二苯砜等芳香族胺、脂肪族胺、4

‑

甲基咪唑等咪唑衍生物、二氰二胺、四甲基胍、硫脲加成胺、甲基六氢邻苯二甲酸酐等羧酸酐、羧酸酰肼、羧酸酰胺、多酚化合物、酚醛清漆树脂、多硫醇等,能够从这些固化剂适当选择使用在25℃为液体的化合物。另外,固化剂可以单独使用一种,也可以同时使用两种以上。

[0396]

在不损害其特性的范围内,可以使树脂层含有通常广泛添加于半导体封装的树脂绝缘膜的分散剂、缓冲剂、粘度调整剂等各种添加剂。

[0397]

<形状>

[0398]

从保护导电通路的理由考虑,树脂层的厚度大于导电通路的突出部的高度,优选1μm~5μm。

[0399]

以下,对各向异性导电性部件20的适用例进行说明。

[0400]

[层叠装置]

[0401]

接着,对层叠装置进行说明。层叠装置具有导电部件(具备具有导电性的导电部)和各向异性导电性部件,使导电部与各向异性导电性部件的突出部接触而接合。层叠装置例如单个发挥特定功能。另外,聚合多个层叠装置而发挥特定功能的装置也包括在层叠装置中。

[0402]

图23是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的第1例的示意图,图24是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的第2例的示意图。

[0403]

关于图23所示的层叠装置60,例如半导体元件62、各向异性导电性部件20及半导体元件64依次沿层叠方向ds层叠而被接合且电连接。虽未图示,但使负责半导体元件62的导电的电极或端子等的导电部与各向异性导电性部件20的突出部接触来被接合。

[0404]

层叠装置60为对1个半导体元件62接合1个半导体元件64的形态,但并不限定于此。如图24所示的层叠装置60,也可以为隔着各向异性导电性部件20,将3个半导体元件62、64、66沿层叠方向ds层叠来接合的形态。虽未图示,此时也使负责半导体元件62、64、66的导电的电极或端子等与各向异性导电性部件20的突出部接触来被接合。

[0405]

上述图23及图24所示的层叠装置60均被称作半导体装置或电子装置等。

[0406]

上述半导体元件62、64、66为具备具有导电性的导电部的导电部件。具备具有导电性的导电部的导电部件并不限定于半导体元件,也可以为具有电极的基板。具有电极的基板例如为配线基板及中介层(interposer)等。

[0407]

[层叠装置的制造方法]

[0408]

接着,对具有图23所示的各向异性导电性部件20的层叠装置60的制造方法进行说明。

[0409]

图25及图26是按工序顺序表示具有本发明的实施方式的各向异性导电性部件的层叠装置的制造方法的示意图。图27是放大表示具有本发明的实施方式的各向异性导电性部件的层叠装置的制造方法的一工序的示意性剖视图。在图25~图27中,对与图20~图22所示的各向异性导电性部件20及图23所示的层叠装置60相同的结构物标注相同符号,并省略其详细说明。

[0410]

另外,图25及图26所示的层叠装置60的制造方法的例子有关于芯片在芯片上(chip on chip)。

[0411]

在制造图23所示的层叠装置60时,首先准备图25所示的半导体元件62、半导体元件64及各向异性导电性部件20。半导体元件62例如在半导体元件部70设置有多个用于进行与外部的信号交换或者电压或电流的发送接收的电极72。各电极72通过绝缘层74被电绝缘。电极72的表面72a例如比绝缘层74的表面74a更突出。

[0412]

半导体元件64为与半导体元件62相同的结构。半导体元件64例如在中介层基板71设置有多个用于进行与外部的信号交换或者电压或电流的发送接收的电极73。各电极73通过绝缘层75被电绝缘。电极73的表面73a例如比绝缘层75的表面75a更突出。中介层基板71例如具有引出配线层(lead wiring layer),并且,层叠装置60通过电极73与外部电连接。

[0413]

各向异性导电性部件20为上述图21所示的结构,并具备多个具有导电性的导电通路16(参考图21及图22)。例如,各向异性导电性部件20中示出了粘接树脂层44(参考图21)等具有粘接功能的结构,但也可以为不具有树脂层44(参考图21)的结构。

[0414]

如图25所示,夹着各向异性导电性部件20,对半导体元件62与半导体元件64将电极73与电极72与电极73对置配置。

[0415]

此时,利用分别设置于半导体元件62、64和各向异性导电性部件20的对准标记(未图示)来进行对位。

[0416]

另外,关于利用对准标记的对位,例如,只要能够获得对准标记的图像或反射像并求出对准标记的位置信息,则并无特别限定,能够适当利用公知的对位方法。

[0417]

接着,使半导体元件62、各向异性导电性部件20及半导体元件64靠近并层叠半导体元件62、各向异性导电性部件20及半导体元件64,在对半导体元件62、各向异性导电性部件20及半导体元件64进行对位的状态下,接合半导体元件62、各向异性导电性部件20及半导体元件64。由此,如图26所示,半导体元件62、各向异性导电性部件20及半导体元件64被接合而能够获得层叠装置60。

[0418]

另外,上述接合述半导体元件62、各向异性导电性部件20及半导体元件64的工序为接合工序。在接合工序中,例如可以在进行了临时接合的状态下以预先确定的条件进行接合,但也可以省略临时接合。另外,将进行临时接合的工序称为临时接合工序,也将除了接合工序的临时接合以外的接合称为正式接合。

[0419]

关于在上述接合工序中制造的层叠装置60,如图27所示,电极72的表面72a与各向异性导电性部件20的导电通路16的突出部分16a接触,接触状态良好且确保充分的导通面积。另外,在图27未图示,但各向异性导电性部件20的导电通路16的突出部分16b与电极73的表面73a接触,接触状态良好且确保充分的导通面积。

[0420]

在上述接合工序中,通过使电极72等的导电部与各向异性导电性部件20的突出部分16a接触,使电极73等的导电部与各向异性导电性部件20的突出部分16b接触来接合。

[0421]

以下,对层叠装置的制造方法进行更具体说明。

[0422]

〔临时接合工序〕

[0423]

临时接合工序的临时接合表示在与要接合的对象物对位的状态下,恒定在要接合的对象物上。临时接合保持经对位的状态,但并非是永久恒定的状态。在各向异性导电性部件和接合对象的半导体元件中,在被临时恒定的情况下,处于各向异性导电性部件在对位的状态下恒定在半导体元件的状态。

[0424]

在临时接合工序中,通过使至少2个部件靠近并接触来实施。此时,加压条件并无特别限定,优选10mpa以下,更优选5mpa以下,尤其优选1mpa以下。

[0425]

同样地,临时接合工序中的温度条件并无特别限定,优选0℃~300℃,更优选10℃~200℃,尤其优选常温(23℃)~100℃。

[0426]

在临时接合工序中,能够使用toray engineering co.,ltd、shibuya kogyo co.,ltd.、shinkawa ltd.及yamaha motor co.,ltd.等各公司的装置。

[0427]

〔接合工序〕

[0428]

如上所述,将接合工序的接合也称为正式接合。在进行正式接合时,作为控制因素可举出正式接合时的气氛、加热温度、加压力(荷载)及处理时间,但能够选择适于所使用的半导体元件等装置的条件。

[0429]

正式接合中的温度条件并无特别限定,优选比临时接合温度高的温度,具体而言,更优选150℃~350℃,尤其优选200℃~300℃。

[0430]

并且,正式接合中的加压条件并无特别限定,优选30mpa以下,更优选0.1mpa~20mpa。加压条件的最大荷载优选1mn以下。更优选0.1mn以下。

[0431]

并且,正式接合的时间并无特别限定,优选1秒~60分钟,更优选5秒~10分钟。

[0432]

并且,作为在上述正式接合中使用的装置,例如能够使用mitsubishi heavy industries machine tool co.,ltd.、bondtech公司、pmt corporation、ayumi industry co.,ltd.、tokyo electron limited.(tel)、evg、suss microtec ag(suss)、musashi engineering,inc.等各公司的晶片接合装置。

[0433]

作为正式接合时的气氛,以大气环境为首,能够从包括氮气气氛等非活性气氛及真空气氛的减压气氛选择。

[0434]

加热温度并不特别限定于上述温度,能够在温度100℃~400℃中进行各种选择,且关于升温速度,也能够按照加热阶段的性能或加热方式在10℃/分钟~10℃/秒中选择。关于冷却也相同。并且,能够进行阶梯状加热,也能够分成数段,依次提高加热温度来进行接合。

[0435]

压力(荷载)并不特别限定于上述压力,能够根据接合对象的强度等物理特性等,选择迅速加压或阶梯状加压。

[0436]

能够适当设定正式接合时的气氛、加热及加压各自的保持时间及变更时间。并且,其顺序也能够适当变更。例如,能够设定组合顺序:在变成真空状态之后进行第1段的加压,之后在加热而升温的情况改下进行第2段的加压并保持一定时间,去除荷载的同时进行冷却,在达到一定温度以下的阶段返回大气环境。

[0437]

这种顺序能够进行各种替换,可以在大气环境下加压后设为真空状态来加热,也可以同时进行真空化、加压、加热。将这些的组合例示于图28~图34。

[0438]

并且,若利用在接合时个别控制面内的加压分布、加热分布的机构,则有可能提高接合的良率。

[0439]

关于临时接合,同样能够进行变更,例如通过在非活性气氛下进行而能够抑制半导体元件的电极表面的氧化。进而,也能够一边施加超声波一边进行接合。

[0440]

图28~图34是表示具有本发明的实施方式的各向异性导电性部件的层叠装置的正式接合条件的第1例~第7例的图表。图28~图34表示接合时的气氛、加热温度、加压力(荷载)及处理时间,符号v表示真空度,符号l表示荷载,符号t表示温度。在图28~图34,真空度高表示压力变低。

[0441]

关于接合时的气氛、加热温度及荷载,例如,如图28~图30所示,可以在减轻压力的状态下施加荷载之后,使温度上升。并且,如图31、图33及图34所示,也可以使增加荷载的时刻与提高温度的时刻吻合。如图32所示,也可以在使温度上升之后增加荷载。并且,如图31及图32所示,也可以使压力的减压时刻与提高温度的时刻吻合。

[0442]

关于温度的上升,可以如图28、图29及图33所示,使温度阶梯状上升,也可以如图34所示,分两个阶段进行加热。荷载也可以如图30及图33所示,阶梯状增加。

[0443]

并且,关于减轻压力的时刻,可以如图28、图30、图32、图33及图34所示,在减压后增加荷载,也可以如图29及图31所示,使减压的时刻与增加荷载的时刻吻合。此时,同时进行减压和接合。

[0444]

〔其他接合工序〕

[0445]

作为接合方法,并不限定于上述方法。例如,经由至少包含锡的电极材料作为加热熔融材料来对半导体元件62、各向异性导电性部件20及半导体元件64进行层叠。此时,在图25所示的突出部分16b上配置有电极材料,在电极73的表面73a上配置有电极材料。

[0446]

接着,在压力1

×

104pa以上且在包含甲酸蒸气等羧酸蒸气的气氛中,将含锡的加热熔融材料加热处理至加热熔融材料的熔点以上而使其熔融。由此,在突出部分16b上及电极73的表面73a上,将电极材料成形为电极。接着,使半导体元件62、各向异性导电性部件20及半导体元件64靠近,在加热熔融材料固化之后,排出羧酸蒸气而从1

×

104pa以上的压力状态减压至1

×

102pa以下的压力状态。在电极材料的温度为100℃以上且未达熔点时排出羧酸蒸气。减压后替换为不含羧酸的非活性气体气氛。由此,如图26所示,半导体元件62、各向异性导电性部件20及半导体元件64被接合而能够获得层叠装置60。另外,羧酸作为还元剂发挥作用,能够在更低的温度下进行接合。并且,含锡的电极材料例如为含锡的焊锡材料。

[0447]

并且,例如经由组合物层对半导体元件62、各向异性导电性部件20及半导体元件64进行层叠。此时,在图25所示的突出部分16b上配置有组合物层,在电极73的表面73a上配置有组合物层。然后,在非活性气体、还元性气体或这些的混合气体中的任一气体气氛下,

以温度120~250℃进行加热并施加荷载。由此,如图26所示,半导体元件62、各向异性导电性部件20及半导体元件64被接合而能够获得层叠装置60。

[0448]

另外,气体气氛为包含氢气或甲酸气体的气体气氛。

[0449]

导体形成用组合物含有含铜粒子、有机酸及分散介质。含铜粒子具有含铜的核粒子和包覆核粒子的表面的至少一部分的有机物。有机物包含具有碳原子数为7以下的烃基的烷基胺。

[0450]

含铜粒子例如为日本特开2016

‑

037627的含铜粒子。另外,含铜粒子至少包含铜,但作为除了铜以外的物质,也可以包含金、银、铂、锡、镍等金属或包含这些金属元素的化合物、还元性化合物或有机物等。

[0451]

有机酸例如为用于焊接的焊剂成分的有机羧酸等。分散介质为通常用于导电油墨、导电浆料等的制造中的有机溶剂。

[0452]

关于接合气氛,可以利用除了真空气氛以外,也导入氮气、氩气等非活性气体或者氢、羧酸等还元性气体或者这些非活性气体与还元性气体的混合气体中的任一气体气氛等公知的方法。尤其,优选使用包含还元性气体的气体。关于使用这些气体的技术,能够适用有关焊锡的熔融接合的技术或使用了微细金属粒子的接合技术,能够将含有以甲酸为首的羧酸的还元性气氛气体或含有氢的还元性气氛气体导入腔室内并进行加热加压接合。气氛气体中的羧酸的浓度优选爆炸界限以下且0.002%以上。在含氢气体的情况下,也优选爆炸界限以下且1%以上。通过在还元性气氛下的接合,在本发明中制造的各向异性导电部件的表面突出的铜柱表面的有机物的脱离、氧化膜的去除变得容易,该铜柱与成为接合对象的铜电极的接合得到促进。

[0453]

具体而言,将接合对象导入腔室内之后,暂且对腔室内进行真空排气,并将上述还元性的气氛气体导入腔室内而维持一定的压力。此时,导入腔室内的气体为羧酸蒸气与载气(氮气等)的混合气体,通过气体的导入,腔室内压力成为1

×

104pa以上。在腔室内压力不变的状态下进行被加热的接合对象彼此的接合。接合对象可以在真空排气时加热,也可以在导入还元性气体之后加热。加热工序中的腔室内的压力并无特别限制,也可为通过设为减压条件,趋于进一步促进低温下的导体化,同时进行气体的导入和排气的“流动(flow)”的状态。通过设为“流动”的状态,同时进行脱离气体等排气来减少腔室的污染。

[0454]

以下,对使用了各向异性导电性部件20(参考图20及图21)的半导体封装进行说明。

[0455]

(半导体封装)

[0456]

〔半导体封装的制造方法1〕

[0457]

例如,通过在上述〔金属填充工序〕之后,依次具有在绝缘性基材的表面搭载半导体元件并接合上述金属m2与半导体元件的电极的半导体元件组装工序、用树脂铸模的铸模工序及上述〔基板去除工序〕的制造方法,能够制作图35所示的半导体封装80。

[0458]

图35是表示半导体封装的第1例的示意性剖视图。另外,在以下所示的图35~图44中,对与上述图20~图22所示的各向异性导电性部件20相同的结构物标注相同符号,并省略其详细说明。

[0459]

在图35所示的半导体封装80中,半导体元件82载置于各向异性导电性部件20的表面20a,并通过焊锡球85与各向异性导电性部件20电连接。各向异性导电性部件20的表面

20a(包含半导体元件82在内)被铸模树脂84包覆。

[0460]

[半导体元件组装工序]

[0461]

对本发明的各向异性导电性部件组装半导体元件时,伴随基于加热的组装,但在基于包括回流焊的热压接的组装及基于覆晶(flip chip)的组装中,从实施均匀且确实的组装的观点考虑,可达最高温度优选220~350℃,更优选240~320℃,尤其优选260~300℃。

[0462]

作为维持这些可达最高温度的时间,从实施均匀且确实的组装的观点考虑,优选2秒~10分钟,更优选5秒~5分钟,尤其优选10秒~3分钟。

[0463]

并且,从抑制因铝基板与阳极氧化膜的热膨胀率差导致在阳极氧化膜内产生的裂纹的观点考虑,也能够采用在达到上述可达最高温度之前,以所需的一定温度实施5秒~10分钟的热处理、更优选10秒~5分钟的热处理、尤其优选20秒~3分钟的热处理的方法。作为所需的一定温度,优选80~200℃,更优选100~180℃,尤其优选120~160℃。

[0464]

并且,作为通过打线进行组装时的温度,从实施确实的组装的观点考虑,优选80~300℃,更优选90~250℃,尤其优选100~200℃。作为加热时间,优选2秒~10分钟,更优选5秒~5分钟,尤其优选10秒~3分钟。

[0465]

〔半导体封装的制造方法2〕

[0466]

通过在上述〔金属填充工序〕之后,依次具有通过焊锡或银浆或填充有填料的树脂浆料在上述绝缘性基材的表面搭载半导体元件的元件搭载工序、用树脂铸模的铸模工序、在上述铸模树脂上开孔而暴露元件电极和上述金属m2的开孔工序、使上述金属m2与半导体元件的电极电性导通的配线形成工序、形成包覆上述配线的绝缘层的绝缘层形成工序及上述〔基板去除工序〕的制造方法,能够制作图36所示的半导体封装80。

[0467]

图36是表示半导体封装的第2例的示意性剖视图。

[0468]

在图36所示的半导体封装80中,半导体元件82载置于各向异性导电性部件20的表面20a而与其电连接。各向异性导电性部件20的表面20a(包含半导体元件82在内)被铸模树脂84包覆。在铸模树脂84形成有用于形成使半导体元件82的电极与各向异性导电性部件20的导电通路16电性导通的配线的孔86。设置有穿过孔86的配线87。通过配线87,使半导体元件82的电极与各向异性导电性部件20的金属m2电性导通。并且,在铸模树脂84的上表面设置有包覆配线87的绝缘层88。

[0469]

<配线形成工序>

[0470]

上述配线形成工序为在上述各向异性导电性部件的至少一面形成配线的工序。

[0471]

其中,关于形成上述配线的方法,例如,可举出实施电解电镀处理、无电解电镀处理、取代电镀处理等各种电镀处理;溅射处理;蒸镀处理;等的方法。其中,从耐热性高的观点考虑,优选形成仅由金属构成的层,从厚膜、形成均匀及高密合性的观点考虑,尤其优选通过电镀处理形成层。上述电镀处理为对非导电性物质(复合材料)的电镀处理,因此使用在设置被称为晶种层的还元金属层之后,利用该金属层来形成厚金属层的方法为优选。

[0472]

上述晶种层优选通过溅射处理来形成。并且,在上述晶种层的形成中,可以利用无电解电镀,作为电镀液,优选例如使用由金属盐、还元剂等主成分和例如ph调整剂、缓冲剂、络合剂、促进剂、稳定剂及改良剂等辅助成分构成的溶液。

[0473]

另外,作为电镀液,能够适当使用se

‑

650

·

666

·

680、sek

‑

670

·

797、sfk

‑

63(均为

japan kanigen co.,ltd.制)、melplate ni

‑

4128、enplate ni

‑

433、enplate ni

‑

411(均为meltex inc.社制)等市售品。

[0474]

并且,作为上述配线的材料,使用铜时,能够使用将硫酸、硫酸铜、盐酸、聚乙二醇及表面活性剂为主成分并添加有其他各种添加剂的各种电解液。

[0475]

根据半导体元件等的组装的设计,用公知的方法在如此形成的配线上形成图案。并且,在实际上要组装半导体元件等的部位,能够再次设置包含焊锡的金属,并通过热压接、覆晶或打线等适当加工成易于连接的状态。

[0476]

作为合适的金属,优选焊锡或金(au)、银(ag)、铜(cu)、铝(al)、镁(mg)、镍(ni)等金属材料,从通过加热组装半导体元件等的观点考虑,并从连接可靠性的观点考虑,优选经由焊锡或ni设置au或ag的方法。

[0477]

具体而言,作为在形成有图案的铜(cu)配线上经由镍(ni)来形成金(au)的方法,可举出实施ni底镀(strike)之后实施au电镀的方法。

[0478]

其中,ni底镀以cu配线的表面氧化层的去除和au层密合性确保为目的来实施。

[0479]

并且,在ni底镀中,可以使用通常的ni/盐酸混合液,也可以使用nips

‑

100(hitachi chemical co.,ltd.制)等市售品。

[0480]

另一方面,au电镀以在实施ni底镀之后提高打线或焊锡的润湿性为目的来实施。并且,au电镀优选在无电解电镀中生成,能够使用hgs

‑

5400(hitachi chemical co.,ltd.制)、microfab au系列、galvanomeister gb系列、precious ig系列(均为tanaka kikinzoku kogyo k.k.制)等市售的处理液。

[0481]

另外,作为用上述配线连接本发明的各向异性导电性部件与半导体元件等的方式,例如,也可举出基于c4(controlled collapse chip connection:可控熔塌芯片连接)凸块、焊锡球及cu柱等的覆晶连接、以及使用了导电粒子排列型的各向异性导电膜(acf)的连接等,但本发明的方式并不限定于这些。

[0482]

[同轴结构]

[0483]

另外,例如,如图43及图44所示,也能够配置将上述配线在信号电流所流经的多个线状导体120的周围,隔着规定间隔与接地配线123连接的多个线状导体120。该结构由于是与同轴线路相同的结构,因此能够发挥屏蔽(shield)效果。并且,在相邻配置且不同的信号电流所流经的多个线状导体120之间,配置有与接地配线123连接的多个线状导体120。因此,能够减少在相邻配置的不同的信号电流所流经的多个线状导体120之间产生的电耦合(电容耦合),并能够抑制信号电流所流经的多个线状导体120本身成为杂讯源。在图43中,信号电流所流经的多个线状导体120形成于绝缘性基材121并彼此电绝缘,且与信号配线122电连接。信号配线122及接地配线123与分别通过绝缘层124电绝缘的配线层125电连接。

[0484]

<绝缘层形成工序>

[0485]

上述绝缘层形成工序为形成上述绝缘层的工序。

[0486]

作为形成上述绝缘层的方法,并无特别限定,将后述树脂用作上述绝缘层时,例如,可举出用贴合装置在上述各向异性导电性部件上层叠的方法、用旋涂装置在上述各向异性导电性部件上涂布的方法、用覆晶接合装置将上述各向异性导电性部件与上述半导体元件接合的同时形成绝缘层的方法等。

[0487]

(绝缘层)

[0488]

作为绝缘层的材料,只要为绝缘性高的材料,则并无特别限定,作为其具体例,例如可举出空气、玻璃、氧化铝等无机绝缘体、树脂等有机绝缘体等,可以将这些单独使用一种,也可以同时使用两种以上。这些中,从廉价且导热率高的理由考虑,优选使用树脂。

[0489]

上述树脂的材质优选热固性树脂。作为上述热固性树脂,优选选自由环氧树脂、改性环氧树脂、硅酮树脂、改性硅酮树脂、丙烯酸树脂、氨酯树脂及聚酰亚胺树脂组成的组中的至少一种,更优选环氧树脂、改性环氧树脂、硅酮树脂、改性硅酮树脂。

[0490]

并且,作为上述树脂,优选使用耐热性、耐候性、耐光性优异的树脂。

[0491]

并且,为了使上述树脂具有规定功能,也能够混合选自由填料、扩散剂、颜料、荧光物质、反射性物质、紫外线吸收剂及抗氧化剂组成的组中的至少一种。

[0492]

并且,作为上述树脂,也能够使用粘接性组合物,例如可举出通称为底胶(underfill)材料(液体)、ncp(non conductive paste:非导电胶)(浆料状)、ncf(non conductive film:非导电膜)(膜状)的半导体用的粘接剂,也能够使用干膜抗蚀剂等。

[0493]

进而,作为上述绝缘层,也能够使用作为上述配线记载的导电粒子排列型的各向异性导电膜(acf)。

[0494]

然而,在本发明中,作为上述绝缘层的方式,并不限定于上述方式。

[0495]

<开孔工序>

[0496]

开孔工序可考虑激光加工、钻孔加工、干式蚀刻等物理方法及基于湿式蚀刻的化学方法,但并不限定于这些方法。

[0497]

〔半导体封装的制造方法3〕

[0498]

通过依次具有上述半导体封装的制造方法1及半导体封装的制造方法2中记载的上述金属填充工序和上述半导体元件组装工序或在半导体元件搭载工序之间在各向异性导电性部件的表面形成掩模层的掩模层形成工序、去除填充至上述阳极氧化膜的上述金属m2、金属m1的填充金属去除工序及去除上述掩模层的掩模层去除工序的制造方法,能够制作图37所示的半导体封装80。

[0499]

图37是表示半导体封装的第3例的示意性剖视图。

[0500]

图37所示的半导体封装80与图35所示的半导体封装80相比,各向异性导电性部件20的结构不同,除此以外为相同的结构。在各向异性导电性部件20中,在通过填充金属去除工序去除了金属m2、金属m1的部分填充有树脂83。通过设置于未被去除的导电通路16的焊锡球85,各向异性导电性部件20与半导体元件82电连接。

[0501]

〔半导体封装的制造方法4〕

[0502]

通过依次具有上述半导体封装的制造方法1及半导体封装2中记载的上述金属填充工序和上述半导体元件组装工序或在半导体元件搭载工序之间在上述各向异性导电性部件的表面形成掩模层的掩模层形成工序、去除上述各向异性导电性部件的一部分的各向异性导电性部件去除工序、在上述各向异性导电性部件的一部分被去除的部分填充树脂的树脂填充工序、去除上述掩模层的掩模层去除工序的制造方法,能够制作图38所示的半导体封装80。

[0503]

图38是表示半导体封装的第4例的示意性剖视图。

[0504]

图38所示的半导体封装80与图35所示的半导体封装80相比,各向异性导电性部件20的结构不同,除此以外为相同的结构。在各向异性导电性部件20中,在通过各向异性导电

性部件去除工序被去除的部分通过树脂填充工序填充有树脂99。通过设置于未被去除的导电通路16的焊锡球85,各向异性导电性部件20与半导体元件82电连接。

[0505]

<掩模层形成工序>

[0506]

上述掩模层形成工序为在上述〔金属填充工序〕之后,在绝缘性基材的表面形成具有规定开口图案(开口部)的掩模层的工序。

[0507]

关于上述掩模层,例如,能够通过如下方法形成:在上述绝缘性基材的表面形成图像记录层之后,通过曝光或加热对上述图像记录层赋予能量而显影成规定开口图案的方法等。其中,形成上述图像记录层的材料并无特别限定,能够使用形成以往公知的感光层(光阻层)或感热层的材料,根据需要,也可以含有红外线吸收剂等添加剂。

[0508]

<掩模层去除工序>

[0509]

上述掩模层去除工序为去除上述掩模层的工序。

[0510]

其中,去除上述掩模层的方法并无特别限定,例如可举出使用溶解上述掩模层且不溶解上述铝基板及上述阳极氧化膜的液体来溶解并去除上述掩模层的方法。作为这种液体,例如在上述掩模层上使用感光层及感热层时,可举出公知的显影液。

[0511]

<填充金属去除工序>

[0512]

上述填充金属去除工序为去除构成在上述掩模层的开口部的下部存在的各向异性导电性部件中的导电通路16的金属m2、金属m1的工序。其中,去除上述金属m2、金属m1的方法并无特别限定,例如可举出使用双氧水或酸性水溶液、或者这些的混合液来溶解金属m2、金属m1的方法等。

[0513]

<各向异性导电性部件去除工序>

[0514]

上述各向异性导电性部件去除工序为去除在上述掩模层的开口部的下部存在的各向异性导电性部件的工序。

[0515]

其中,去除上述各向异性导电性部件的方法并无特别限定,例如可举出使用碱蚀刻水溶液或酸性水溶液来溶解各向异性导电性部件的阳极氧化膜的方法等。

[0516]

<水洗处理>

[0517]

在结束上述各处理的工序之后,优选进行水洗。水洗中能够使用纯水、井水及自来水等。可以使用夹持(nipping)装置,以防止将处理液带入下一工序。

[0518]

〔半导体封装的制造方法5〕

[0519]

通过在上述〔基板去除工序〕之后,具有在所暴露的各向异性导电性部件的表面形成至少1层以上的配线层的配线层形成工序的制造方法,能够制作图39所示的半导体封装80。

[0520]

图39是表示半导体封装的第5例的示意性剖视图。

[0521]

图39所示的半导体封装80与图35所示的半导体封装80相比,在各向异性导电性部件20的背面20b设置有配线基板90这一点不同,除此以外为相同的结构。

[0522]

关于配线基板90,在具有电绝缘性的绝缘性基材92上设置有配线层94。配线层94的一侧与各向异性导电性部件20的导电通路16电连接,另一侧与焊锡球95电连接。由此,能够将信号等从半导体元件82提取到半导体封装80的外部。并且,能够从半导体封装80的外部向半导体元件82提供信号、电压或电流等。

[0523]

〔半导体封装的制造方法6〕

[0524]

通过在上述〔半导体封装的制造方法5〕的配线层形成工序之后,具有至少进行1次以上搭载有上述半导体封装和半导体元件的封装基板的接合的工序的制造方法,如图40所示能够制作层叠了半导体封装基板的pop(package on package:层叠封装)基板61。

[0525]

图40是表示层叠了半导体封装基板的结构的示意性剖视图。

[0526]

图40所示的pop基板61中层叠有半导体封装基板80a和半导体封装基板80b,并通过焊锡球108电连接。在半导体封装基板80a中,在各向异性导电性部件20的表面20a设置有配线98。在绝缘层97例如设置有2个配线98。各配线98通过焊锡球85与1个半导体元件82电连接。配线98及1个半导体元件82被铸模树脂84包覆。

[0527]

并且,在各向异性导电性部件20的背面20b设置有配线层100。在配线层100中,在绝缘性基材101设置有2个配线102。各配线102分别经由各向异性导电性部件20的导电通路16与焊锡球108电连接。

[0528]

在半导体封装基板80b中,例如在基板104的两侧设置有电极105,在中央部设置有2个电极106。中央部的各电极106分别经由焊锡球85与半导体元件82电连接。基板104的两侧的电极105分别经由焊锡球108与半导体封装基板80a的配线102电连接。

[0529]

〔半导体封装的制造方法7〕

[0530]

通过在上述〔半导体封装的制造方法2〕中记载的绝缘层形成工序之后,具有为了暴露位于上述绝缘层之下的上述配线而在绝缘层开孔的工序的制造方法,能够制作图41所示的半导体封装80。如此,能够制作内置组件基板。

[0531]

图41是表示半导体封装的第6例的示意性剖视图。

[0532]

图41所示的半导体封装80与图36所示的半导体封装80相比,在绝缘层88设置有暴露配线87的孔89这一点不同,除此以外为相同的结构。

[0533]

另外,本发明并不限于上述实施方式,作为组装形态,例如可举出soc(system on a chip:单芯片系统)、sip(system in package:封装体系)、pop(package on package:层叠封装)、pip(polysilicon insulater polysilicon:多晶硅绝缘体多晶硅)、csp(chip scale package:芯片级封装)、tsv(through silicon via:硅穿孔)等。

[0534]

更详细而言,例如,本发明的各向异性导电性部件不仅用于半导体元件单体的数据信号及电源的连接,也能够用作接地部及导热部。

[0535]

并且,本发明的各向异性导电性部件不仅用于2个以上的半导体元件之间的数据信号或电源的连接,也能够用作接地部及导热部。作为这种方式,例如可举出在以下例子中将本发明的各向异性导电性部件用作中介层的方式。

[0536]

·

三维soc的逻辑装置(例如,均质基板(在中介层上层叠有多层fpga(field programmable gate array:现场可编程门阵列)的基板)、非均质基板(在中介层上层叠有数字装置、模拟装置、rf装置、mems及存储器的基板)等)

[0537]

·

组合有逻辑和存储器的三维sip(wide i/o:加宽输入/输出)(例如,在中介层的上或上下层叠有cpu和dram、在中介层的上或上下层叠有gpu和dram、在中介层的上或上下层叠有asic/fpga和wide i/o存储器、在中介层的上或上下层叠有ape和wide i/o存储器等)

[0538]

·

组合有soc和dram的2.5维非均质基板

[0539]

并且,如图42所示,本发明的各向异性导电性部件也能够用于半导体封装80与印

刷配线基板110的电连接。印刷配线基板110设置于半导体封装80的各向异性导电性部件20的背面20b。在印刷配线基板110上,例如在由树脂构成的绝缘性基材112设置有配线层114。配线层114与各向异性导电性部件20的背面20b的导电通路16电连接。

[0540]

并且,本发明的各向异性导电性部件也能够用于2个以上的半导体封装彼此的连接(pop;package on package:层叠封装),作为此时的方式,例如可举出本发明的各向异性导电性部件经由规定的配线与配置于其上下面侧的2个半导体封装连接的方式。

[0541]

并且,本发明的各向异性导电性部件也能够用于通过将2个以上的半导体元件层叠在基板上的方式或平置在基板上的方式来进行封装的多芯片封装,作为此时的方式,例如可举出在本发明的各向异性导电性部件上层叠2个半导体元件并通过规定的配线连接的方式。

[0542]

(电子装置)

[0543]

以下,对使用了各向异性导电性部件的电子装置进行说明。电子装置为层叠装置的一种。

[0544]

图45是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第1例的示意图,图46是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第2例的示意图。

[0545]

也可以设为如图45所示的电子装置130用中介层137和各向异性导电性部件20将半导体元件134、半导体元件136及半导体元件138沿层叠方向ds层叠并接合且电连接的结构。

[0546]

并且,也可以为如图46所示的电子装置130作为光学传感器发挥功能的结构。在图46所示的电子装置130中,经由各向异性导电性部件20沿层叠方向ds对半导体元件140和传感器芯片142进行层叠。并且,传感器芯片142上设置有透镜144。

[0547]

半导体元件140形成有逻辑电路,只要能够处理在传感器芯片142获得的信号,则其结构并无特别限定。

[0548]

传感器芯片142具有检测光的光传感器。光传感器只要能够检测光,则并无特别限定,例如可使用ccd(charge coupled device:电荷耦合装置)图像传感器或cmos(complementary metal oxide semiconductor:互补金属氧化物半导体)图像传感器。

[0549]

透镜144只要能够将光聚集在传感器芯片142上,则其结构并无特别限定,例如可使用被称为微透镜的透镜。

[0550]

另外,上述半导体元件134、半导体元件136及半导体元件138具有元件区域(未图示)。

[0551]

元件区域为形成有用于发挥作为电子元件的功能的电容器、电阻及线圈等各种元件构成电路等的区域。关于元件区域,例如存在形成有快闪存储器等存储器电路、微处理器及fpga(field

‑

programmable gate array:现场可编程门阵列)等之类的逻辑电路的区域、形成有无线标签(wireless tag)等通信模块及配线的区域。除此以外,在元件区域也可以形成有振荡电路或mems(micro electro mechanical systems:微机电系统)。mems例如为传感器、致动器及天线等。传感器例如包括加速度、声音及光等的各种传感器。

[0552]

如上所述,在元件区域中形成有元件构成电路等,在半导体元件中例如设置有再配线层(未图示)。

[0553]

在层叠装置中,例如能够设为具有逻辑电路的半导体元件和具有存储器电路的半导体元件的组合。并且,可以将半导体元件设为全部具有存储器电路,并且,也可以设为全部具有逻辑电路。并且,作为电子装置130中的半导体元件的组合,可以为传感器、致动器及天线等与存储器电路和逻辑电路的组合,并且根据电子装置130的用途等而适当确定。

[0554]

〔半导体元件〕

[0555]

半导体元件用于上述半导体封装及电子装置。作为半导体元件,并无特别限定,除了上述以外,例如可举出逻辑lsi(large scale integration:大型积体电路)(例如,asic(application specific integrated circuit:特殊应用积体电路)、fpga(field programmable gate array:现场可编程门阵列)、assp(application specific standard product:应用特定标准产品)等)、微处理器(例如,cpu(central processing unit:中央处理器)、gpu(graphics processing unit:图形处理器)等)、存储器(例如,dram(dynamic random access memory:动态随机存取存储器)、hmc(hybrid memory cube:混合存储器立方体)、mram(magneticram:磁存储器)和pcm(phase

‑

change memory:相变化存储器)、reram(resistive ram:可变电阻式存储器)、feram(ferroelectric ram:铁电随机存取存储器)、快闪存储器(nand(not and)快闪)等)、led(light emitting diode:发光二极管)、(例如,可携式终端的微快闪、车载用、投影仪光源、lcd背光、一般照明等)、功率装置、模拟ic(integrated circuit:积体电路)、(例如,dc(direct current:直流电)

‑

dc(direct current:直流电)转换器、绝缘栅双极型晶体管(igbt)等)、mems(micro electro mechanical systems:微机电系统)(例如,加速度传感器、压力传感器、振子、陀螺仪传感器等)、无线(例如,gps(global positioning system:全球定位系统)、fm(frequency modulation:调频)、nfc(near field communication:近场通信)、rfem(rf expansion module:射频扩展模块)、mmic(monolithic microwave integrated circuit:单晶微波积体电路)、wlan(wireless local area network:无线局域网络)等)、离散元件、bsi(back side illumination:背部照明)、cis(contact image sensor:接触式图像传感器)、相机模块、cmos(complementary metal oxide semiconductor:互补金属氧化物半导体)、被动装置、saw(surface acoustic wave:表面声波)滤波器、rf(radio frequency:射频)滤波器、rfipd(radio frequency integrated passive devices:射频整合式被动元件)、bb(broadband:宽频)等。

[0556]

半导体元件例如为自成一件的元件,并且以半导体元件单体发挥电路或传感器等特定功能。

[0557]

作为电子装置,并不限定于对1个半导体元件接合多个半导体元件的形态即1对多个形态,也可以为接合多个半导体元件与多个半导体元件的形态即多对多个形态。

[0558]

图47是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第3例的示意图,图48是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第4例的示意图,图49是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第5例的示意图,图50是表示使用了本发明的实施方式的各向异性导电性部件的电子装置的第6例的示意图。

[0559]

作为多对多个形态,如图47所示,例如可例示用各向异性导电性部件20对1个半导体元件134接合半导体元件136和半导体元件138且电连接的形态的电子装置130a。半导体

元件134也可以具有中介层功能。

[0560]

并且,例如,能够在具有中介层功能的装置上层叠具有逻辑电路的逻辑芯片及存储器芯片等多个装置。并且,此时,即使各装置的电极尺分别不同,也能够接合。

[0561]

在图48所示的电子装置130b中,电极148的大小并不相同,混合具有不同的大小,但用各向异性导电性部件20对1个半导体元件134接合半导体元件136和半导体元件138且电连接。进而,用各向异性导电性部件20将半导体元件136与半导体元件146接合且电连接。将半导体元件147横跨半导体元件136和半导体元件138而用各向异性导电性部件20进行接合且电连接。

[0562]

并且,如图49所示的电子装置130c,用各向异性导电性部件20对1个半导体元件134接合半导体元件136和半导体元件138且电连接。进而,也能够设为用各向异性导电性部件20将半导体元件146和半导体元件147与半导体元件136接合,用各向异性导电性部件20将半导体元件151与半导体元件138接合且电连接的结构。

[0563]

在如上述结构的情况下,通过在包含光波导(optical waveguide)的装置表面层叠vcsel(vertical cavity surface emitting laser:垂直共振腔表面发光激光器)等发光元件及cmos(complementary metal oxide semiconductor:互补金属氧化物半导体)图像传感器等受光元件,也能够应对假设高频的硅光子学。

[0564]

例如,如图50所示的电子装置130d,用各向异性导电性部件20对1个半导体元件134接合半导体元件136和半导体元件138且电连接。进而,用各向异性导电性部件20将半导体元件146和半导体元件147与半导体元件136接合,用各向异性导电性部件20将半导体元件151与半导体元件138接合且电连接。在半导体元件134设置有光波导153。在半导体元件138设置有发光元件155,在半导体元件136设置有受光元件156。从半导体元件138的发光元件155输出的光lo通过半导体元件134的光波导153,并作为射出光ld而射出至半导体元件136的受光元件156。由此,能够应对上述硅光子学。

[0565]

另外,在各向异性导电性部件20中,在相当于光lo及射出光ld的光路的位置形成有孔152。

[0566]

本发明基本上如以上构成。以上,对本发明的阳极氧化处理方法及各向异性导电性部件的制造方法进行了详细说明,但本发明并不限定于上述实施方式,在不脱离本发明的主旨的范围内,当然可以进行各种改良或变更。

[0567]

实施例

[0568]

以下,举出实施例来对本发明的特征进行更具体说明。以下实施例所示的材料、试剂、物质量及其比例以及操作等能够在不脱离本发明的主旨的范围内进行适当变更。因此,本发明的范围并不限定于以下实施例。

[0569]

在本实施例中,制作了实施例1~实施例5的各向异性导电性部件及比较例1~比较例4的各向异性导电性部件。针对实施例1~实施例5的各向异性导电性部件及比较例1~比较例4的各向异性导电性部件,评价了异常部频度、上下孔径、缺陷频度及接合。将异常部频度、上下孔径、缺陷频度及接合的评价结果示于下述表2。

[0570]

以下,对异常部频度、上下孔径、缺陷频度及接合的各评价项目进行说明。

[0571]

对异常部频度的评价进行说明。

[0572]

<异常部频度的评价>

[0573]

在通过阳极氧化处理获得的阳极氧化膜的表面照射光,用光学显微镜进行观察并试图发现反射点。然后,计数反射点,并求出了每单位面积的反射点。将反射点的每单位面积的数量评价为异常部频度。

[0574]

对上下孔径的评价进行说明。

[0575]

<上下孔径的评价>

[0576]

对所制造的各向异性导电性部件切出10个剖面,并获得了各剖面的fe

‑

sem(field emission scanning electron microscope:场发射扫描电子显微镜)图像。根据10个剖面的fe

‑

sem图像测定各微孔的表面及底部的直径,并求出了微孔的表面及底部的直径的平均值。将该平均值作为微孔的表面及底部的直径。

[0577]

另外,利用聚焦离子束(focused ion beam:fib)进行切削加工来获得剖面。

[0578]

对缺陷频度的评价进行说明。

[0579]

<缺陷频度的评价>

[0580]

研磨所制造的各向异性导电性部件的一面之后,用光学显微镜观察研磨面,试图发现缺陷。然后,计数缺陷,并求出每单位面积的缺陷数,以下述表1所示的评价基准评价了缺陷频度。在评价中,需要同时满足直径20~50μm的评价基准和直径超过50μm的评价基准。例如,将评价aa设为直径20~50μm满足0.001~0.1且未检测出直径超过50μm的缺陷。

[0581]

另外,如下实施了上述一面研磨。首先,用q

‑

chuck(注册商标)(maruishi sangyo co.,ltd.制)对4英寸晶片贴附所制造的各向异性导电性部件,用material automation(thailand)co.,ltd.制研磨装置将各向异性导电性部件研磨至算术平均粗糙度(jis(日本工业标准)b0601:2001)成为0.02μm。研磨中使用了包含氧化铝的磨粒。

[0582]

[表1]

[0583][0584]

对接合的评价进行说明。

[0585]

<接合的评价>

[0586]

准备了能够评价菊花链的teg芯片(test element group chip:测试元件组芯片)。teg芯片具有1000个菊花链。

[0587]

将各向异性导电性部件在2个teg芯片上层叠,并设置于晶片接合机(wafer bonder)的腔室内。暂且将腔室内设为10

‑3pa的真空之后,将含有5%氢的氮气气体导入腔室内并将腔室内的压力稳定在5kpa。之后,在压力20mpa、温度200℃的条件下进行加压加热,保持30分钟来进行了接合。

[0588]

接合按以下所示的评价基准进行了评价。

[0589]

评价基准

[0590]

a:在接合品的1000个菊花链中,全部相连。

[0591]

b:在接合品的1000个菊花链中,相连75%以上且未达100%。

[0592]

c:在接合品的1000个菊花链中,相连50%以上且未达75%。

[0593]

d:在接合品的1000个菊花链中,相连25%以上且未达50%。

[0594]

以下,对实施例1~实施例5及比较例1~比较例4进行说明。

[0595]

(实施例1)

[0596]

对实施例1的各向异性导电性部件进行说明。

[0597]

[各向异性导电性部件]

[0598]

<铝基板>

[0599]

使用了纯度99.999质量%的铝基板。

[0600]

<电解研磨处理>

[0601]

用以下组成的电解研磨液,在电压25v、液体温度65℃、液体流速3.0m/分钟的条件下,对上述铝基板实施了电解研磨处理。另外,将电解处理的处理面积设为0.12m2。

[0602]

阴极设为碳电极,电源使用了gp0110

‑

30r(takasagoltd.制)。并且,用涡流式流量监测器flm22

‑

10pcw(asonecorporation制)测量了电解液的流速。

[0603]

(电解研磨液组成)

[0604]

·

85质量%磷酸(fujifilmwakopurechemicalcorporation制试剂)660ml

[0605]

·

纯水160ml

[0606]

·

硫酸150ml

[0607]

·

乙二醇30ml

[0608]

<阳极氧化处理工序>

[0609]

接着,在以下所示的阳极氧化处理条件下,对电解研磨处理后的铝基板实施了阳极氧化处理。

[0610]

(电解液)

[0611]

草酸10%水溶液、液体温度15℃。对电解液实施了液体搅拌。

[0612]

(阳极氧化处理条件)

[0613]

实施了2次阳极氧化处理。

[0614]

在第1次初始阳极氧化处理中,在进行恒定电压控制至成为电压40v的恒定电压的状态下,实施了60分钟的阳极氧化处理。

[0615]

在第2次阳极氧化处理中,用可编程直流电源进行以下所示的电压控制,由此实施了阳极氧化处理。将电流增加期间设为6分钟。将电流维持期间设为400分钟。电流维持期间为400分钟的情况下,电流密度为72a/m2。

[0616]

关于电压控制,在电压20v保持4分钟、在电压30v保持1.5分钟、在电压35v保持0.5分钟,最终阶段性增加至电压40v。

[0617]

<阻挡层去除工序>

[0618]

接着,以与上述阳极氧化处理相同的处理液及处理条件,一边将电压以电压下降速度0.2v/sec从40v连续下降到0v,一边实施了电解处理(电解去除处理)。

[0619]

之后,实施在5质量%磷酸浸渍30℃、30分钟的蚀刻处理(蚀刻去除处理),去除在

阳极氧化膜的微孔的底部存在的阻挡层,并经由微孔暴露铝基板。

[0620]

存在于阳极氧化膜的微孔的密度为约1亿个/mm2。另外,利用日本特开2008

‑

270158号公报的[0168]及[0169]段中记载的方法测定并算出了微孔的密度。

[0621]

并且,存在于阳极氧化膜的微孔的规则度为92%。另外,通过fe

‑

sem拍摄表面照片(倍率20000倍),并利用日本特开2008

‑

270158号公报的[0024]~[0027]段中记载的方法测定并算出了规则度。

[0622]

<金属填充工序>

[0623]

接着,将铝基板作为阴极,将铂作为正极来实施了电解电镀处理。

[0624]

具体而言,通过使用以下所示的组成的铜电镀液来实施恒电流电解,制作了在微孔的内部填充有铜的各向异性导电性部件。

[0625]

其中,关于恒电流电解,利用yamamoto

‑

ms co.,ltd.制的电镀装置,用hokuto denko corporation.制的电源(hz

‑

3000),在电镀液中进行循环伏安法确认析出电位之后,在以下所示的条件下实施了处理。

[0626]

(铜电镀液组成及条件)

[0627]

·

硫酸铜 100g/l

[0628]

·

硫酸 50g/l

[0629]

·

盐酸 15g/l

[0630]

·

温度 25℃

[0631]

·

电流密度 10a/dm2[0632]

<基板去除工序>

[0633]

接着,通过在20质量%氯化汞水溶液(升汞)中以20℃浸渍3小时来溶解并去除铝基板,由此制作了各向异性导电性部件。

[0634]

<突出工序>

[0635]

将基板去除工序后的各向异性导电性部件浸渍于氢氧化钠水溶液(浓度:5质量%、液体温度:20℃),并调整浸渍时间至突出部分的高度成为300nm来选择性溶解铝的阳极氧化膜的表面,粘接进行水洗,干燥来使导电通路即铜圆柱突出。

[0636]

同样地,在铝的阳极氧化膜的背面,也使导电通路即铜圆柱突出,以使突出部分的高度成为300nm。

[0637]

(实施例2)

[0638]

相较于实施例1,实施例2的第2次阳极氧化处理不同,除此以外,将实施例2设为与实施例1相同。

[0639]

实施例2在第2次阳极氧化处理时进行了电流控制。在第2次阳极氧化处理中,用可编程直流电源,以所设定的增加速度使电流上升。增加处理期间经过后,在电流维持期间维持了增加处理期间的最大电流值。

[0640]

在实施例2中,将第2次阳极氧化处理中的电流增加量设为0.2(a/(m2·

秒)),将电流增加期间设为8分钟,将电流维持时间设为300分钟。在电流维持时间为300分钟的情况下,电流密度为96a/m2。

[0641]

(实施例3)

[0642]

相较于实施例2,实施例3在第2次阳极氧化处理中的电流增加量为0.15(a/(m2·

秒))、电流维持时间为400分钟这两点不同,除此以外,设为与实施例2相同。在电流维持时间为400分钟的情况下,电流密度为72a/m2。

[0643]

(实施例4)

[0644]

相较于实施例1,实施例4在电流增加量的控制方法中使用不锈钢板、将第2次阳极氧化处理中电流增加期间设为7分钟、电流维持时间为350分钟这三点不同,除此以外,设为与实施例1相同。在电流维持时间为350分钟的情况下,电流密度为84a/m2。

[0645]

在实施例4中,在第2次阳极氧化处理时,使用了与阳极氧化处理对象即铝基板电性并联连接的不锈钢板,而不是实施例1的电压控制。不锈钢板具有与铝基板的处理面积相同的面积,厚度设为0.2mm。在实施例4中,进行恒定电压控制来使成为电压40v的恒定电压。

[0646]

另外,在表2中,将不锈钢板标注为sus(steel use stainless:不锈钢)板。

[0647]

(实施例5)

[0648]

相较于实施例4,实施例5在使用ti板来代替不锈钢板这一点不同,除此以外,设为与实施例4相同。ti板具有与铝基板的处理面积相同的面积,厚度设为0.2mm。

[0649]

(比较例1)

[0650]

相较于实施例1,比较例1在阳极氧化处理时进行恒定电压控制至成为电压40v的恒定电压,但在电流增加期间不进行电压控制、电流维持时间为300分钟且电流密度为96a/m2这两点不同,除此以外,设为与实施例1相同。

[0651]

在比较例1中,在电流增加期间一栏中标注为“无”。在比较例1中,虽无电流增加期间,但电压达到40v所需的时间为1秒。

[0652]

(比较例2)

[0653]

相较于实施例2,比较例2在第2次阳极氧化处理中的电流增加量为1.0(a/(m2·

秒))且电流增加期间为1.6分钟这一点不同,除此以外,设为与实施例2相同。

[0654]

(比较例3)

[0655]

相较于实施例2,比较例3在第2次阳极氧化处理中的电流增加量为0.15(a/(m2·

秒))且电流增加期间为12分钟这一点不同,除此以外,设为与实施例2相同。

[0656]

(比较例4)

[0657]

相较于实施例1,在比较例4在电流增加期间为12分钟这一点不同,除此以外,设为与实施例1相同。

[0658]

[表2]

[0659][0660]

表2所示,相较于比较例1~比较例4,实施例1~实施例5在异常部频度、缺陷频度及接合上获得了良好的结果。

[0661]

在比较例1中,由于未控制电流增加量,因此异常部频度高,且缺陷频度也差,进而接合也不佳。

[0662]

在比较例2中,电流增加量超过每秒0.2安培每平方米,异常部频度高,且缺陷频度也差,进而接合也不佳。

[0663]

在比较例3及比较例4中,由于电流增加期间长,因此异常部频度高,且缺陷频度也差,进而接合也不佳。并且,表面侧的微孔的直径变大。

[0664]

根据实施例2和实施例3,关于异常部频度及缺陷频度,电流增加量更接近每秒0.2安培每平方米时获得了的良好的结果。

[0665]

根据实施例4和实施例5,设置导电性负载部件时,关于异常部频度、缺陷频度及接合,ti板比不锈钢获得了更良好的结果。

[0666]

符号说明

[0667]

10

‑

铝基板,10a

‑

表面,12

‑

微孔,13

‑

阻挡层,14

‑

阳极氧化膜,15

‑

金属,15a

‑

金属层,15b

‑

金属,16

‑

导电通路,16a

‑

突出部分,16b

‑

突出部分,17

‑

结构体,19

‑

树脂层,20

‑

各向异性导电性部件,20a

‑

表面,20b

‑

背面,21

‑

卷芯,28

‑

各向异性导电材料,30

‑

阳极氧化处理装置,32

‑

电解槽,34

‑

对置电极,35

‑

金属基板,36

‑

电源部,38

‑

控制部,40

‑

绝缘性基材,40a

‑

表面,40b

‑

背面,44

‑

树脂层,46

‑

支撑体,47

‑

剥离层,48

‑

支撑层,49

‑

剥离剂,60

‑

层叠装置,61

‑

pop基板,62、64、66、82

‑

半导体元件,70

‑

半导体元件部,71

‑

中介层基板,72、73

‑

电极,72a、74a、75a

‑

表面,74、75、88、97

‑

绝缘层,80

‑

半导体封装,80a、80b

‑

半导体封装基板,83、99

‑

树脂,84

‑

铸模树脂,85、95、108

‑

焊锡球,86、89

‑

孔,87

‑

配线,90

‑

配线基板,92、101、112、121

‑

绝缘性基材,94、100

‑

配线层,98、102

‑

配线,110

‑

印刷配线基板,114、125

‑

配线层,120

‑

线状导体,122

‑

信号配线,123

‑

接地配线,124

‑

绝缘层,130、130a、130b、130c、130d

‑

电子装置,134、136、138、140、146、147、151

‑

半导体元件,137

‑

中介层,142

‑

传感器芯片,144

‑

透镜,148

‑

电极,152

‑

孔,153

‑

光波导,155

‑

发光元件,156

‑

受光元件,aq

‑

电解液,b1‑

第1次阳极氧

化处理,b2‑

第2次阳极氧化处理,ds

‑

层叠方向,dt

‑

厚度方向,im

‑

最大值,ld

‑

射出光,lo

‑

光,pe

‑

区域,rs

‑

稳态部,ru

‑

上升部,t

‑

阳极氧化处理时间,tm

‑

期间,ts

‑

稳态时间,tu

‑

上升时间,vm

‑

最大值,h

‑

厚度,ht

‑

厚度,p

‑

中心间距离,x

‑

方向。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。