多射束用的消隐装置以及多带电粒子束描绘装置

1.相关申请

2.本技术享受以日本专利申请2020-047967号(申请日:2020年3月18日)为基础申请的优先权。本技术通过参照该基础申请而包含基础申请的全部内容。

技术领域

3.本发明涉及多射束用的消隐装置以及多带电粒子束描绘装置。

背景技术:

4.随着lsi的高集成化,半导体器件的电路的布线宽度与布线间距逐年细微化。为了形成这样的半导体器件的电路图案,采用了使用缩小投影型曝光装置,并使用arf等激光将形成在石英上的高精度的原版图案缩小转印到晶片上的方法(光刻)。近年来,为了形成更细微的图案,开始采用使用了极端紫外线的euv光刻。在euv光刻中,使用具有由多种材料构成的多层结构的掩模。在任一掩模中,在高精度的原版图案的制作中,使用由电子束描绘装置选择性地对掩模底版(mask blank,试样)上的抗蚀剂进行曝光而形成图案的所谓电子束光刻技术。

5.作为电子束描绘装置,已知有例如使用多射束而一次照射多个射束并提高生产率的多射束描绘装置。在该多射束描绘装置中,例如,从电子枪射出的电子束在具有多个开口的成形孔径阵列基板中穿过,从而形成多射束(多个电子束)。多射束在消隐板(消隐孔径阵列基板)的各个对应的消隐器内穿过。消隐板具有用于使射束单独地偏转的电极对(消隐器),在电极对之间形成有射束穿过用的开口。通过将消隐器的一个电极(接地电极)固定于接地电位,并将另一个电极(消隐电极)切换为接地电位和除此以外的电位,进行穿过的电子束的消隐偏转。被消隐器偏转的电子束被屏蔽而在试样上成为截止,未被偏转的电子束作为接通射束照射到试样上。

6.消隐板具备:形成有多个开口的基板、在各开口的周围形成的消隐器以及向消隐器施加电压的控制电路部。通常,在构成控制电路部的mos晶体管形成之后,与通常的半导体器件同样地在基板表面形成由氮化硅膜等绝缘膜构成的钝化膜(保护膜)。若绝缘膜在消隐板的表面露出,则在被照射了电子束的情况下,会存在如下问题:该绝缘膜带电,mos晶体管的栅极绝缘膜等被静电破坏而无法进行消隐控制,或者由于带电引起的电场而使在开口中穿过的射束的轨道变化,产生照射位置的偏移或散焦,描绘精度降低。

7.因此,在保护膜上设置防带电膜,防止保护膜的带电。该防带电膜在接地电极、消隐板端部与接地布线连接。但是,若由于某种原因而在防带电膜上产生接地连接不良,则由于散射电子等使防带电膜局部带电而产生电位梯度,另外,若产生与消隐电极的短路,则在对消隐电极施加了电压时,在防带电膜上产生局部的电位梯度。由于这些现象,电子束会向不希望的方向偏转,从而造成描绘精度降低等影响。

技术实现要素:

8.本发明提供一种能够防止在防带电膜上产生局部的带电以及电位梯度,并提高描绘精度的多射束用的消隐装置以及具备这样的消隐装置的多带电粒子束描绘装置。

9.本发明的一方式的多射束用的消隐装置具备:半导体基板;绝缘膜,设于所述半导体基板上;防带电膜,设于所述绝缘膜上;多个单元,分别具有消隐电极和接地电极,该消隐电极和接地电极与形成于所述半导体基板和所述绝缘膜的贯通孔对应地设置在该绝缘膜上;以及接地布线,设于所述绝缘膜中,所述防带电膜与所述接地布线通过连接部而连接,该连接部贯通所述接地布线上的所述绝缘膜而形成。

附图说明

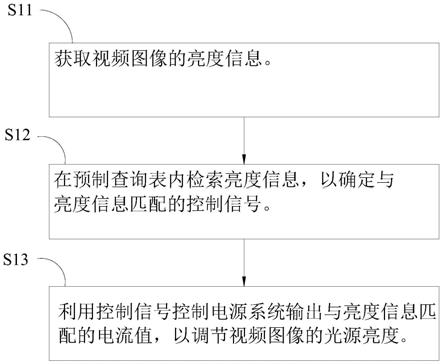

10.图1是本发明的实施方式的带电粒子束描绘装置的概略图。

11.图2是成形孔径阵列基板的概略图。

12.图3是表示消隐装置的构成的概念图。

13.图4是单元的示意图。

14.图5是单元的剖面图。

15.图6是单元阵列的概略构成图。

16.图7的(a)是比较例的单元阵列的等效电路图,图7的(b)是实施方式的单元阵列的等效电路图。

17.图8是单元的示意图。

18.图9是单元阵列的概略构成图。

19.图10的(a)是比较例的防带电膜的等效电路图,图10的(b)是实施方式的防带电膜的等效电路图。

20.图11是单元的剖面图。

具体实施方式

21.以下,基于附图对本发明的实施方式进行说明。

22.图1是安装了本实施方式的消隐装置的多带电粒子束描绘装置的概略图。在本实施方式中,作为带电粒子束的一个例子,对使用了电子束的构成进行说明。但是,带电粒子束并不限于电子束,也可以是离子束等其他带电粒子束。

23.图1所示的多电子束描绘装置具有电子镜筒2以及描绘室20。在电子镜筒2内配置有电子枪4、照明透镜6、成形孔径阵列基板8、消隐装置10、缩小透镜12、限制孔径部件14、物镜16以及偏转器18。在描绘室20内配置有xy工作台22。在xy工作台22上载置有成为描绘对象基板的掩模底版24。作为对象物,例如包括晶片和曝光用的掩模,所述曝光用的掩模在晶片上使用以准分子激光为光源的步进器或扫描仪等缩小投影型曝光装置或极端紫外线曝光装置(euv)来转印图案。另外,在描绘对象基板中例如也包括已形成有图案的掩模。例如,利文森(levenson)型掩模需要两次描绘,因此有时在被描绘一次并加工成掩模的物体上描绘第二次的图案。在xy工作台22上还配置有xy工作台22的位置测定用的反射镜26。

24.从电子枪4射出的电子束30通过照明透镜6大致垂直地对成形孔径阵列基板8进行照明。图2是表示成形孔径阵列基板8的构成的概念图。在成形孔径阵列基板8上,以规定的

排列间距矩阵状地形成有纵(y方向)m列

×

横(x方向)n列(m、n≥2)的开口80。各开口80均以相同的尺寸形状的矩形形成。各开口80也可以是相同外径的圆形。

25.电子束30对包含成形孔径阵列基板8的所有开口80在内的区域进行照明。电子束30的一部分分别穿过这些多个开口80,从而形成图1所示那样的多射束30a~30e。

26.如后述那样,在消隐装置10中,与成形孔径阵列基板8的各开口80的配置位置对应地形成贯通孔(图4、5中的贯通孔110),在各贯通孔中分别配置由成对的两个电极构成的消隐器(图5中的由接地电极102及消隐电极104构成的消隐器101)。在各贯通孔中穿过的多射束30a~30e分别独立地通过消隐器施加的电压而偏转。通过该射束偏转来进行消隐控制。利用消隐装置10,对在成形孔径阵列基板8的多个开口80穿过的多射束的每一个进行消隐偏转。

27.穿过了消隐装置10的多射束30a~30e利用缩小透镜12来缩小各自的射束尺寸以及排列间距,朝向形成于设置在交叉处的限制孔径部件14的中心的开口前进。这里,被消隐装置10的消隐器偏转后的射束,其轨道发生位移,位置从限制孔径部件14的中心的开口偏离,被限制孔径部件14屏蔽。另一方面,未被消隐装置10的电极偏转的射束穿过限制孔径部件14的中心的开口。

28.限制孔径部件14对被消隐装置10的消隐器偏转为射束切断的状态的各射束进行屏蔽。从射束接通起到射束切断为止穿过了限制孔径部件14的射束成为一次发射的射束。穿过了限制孔径部件14的多射束30a~30e被物镜16聚焦,成为所希望的缩小率的图案像。穿过了限制孔径部件14的各射束(多射束整体)通过偏转器18向相同方向集中偏转,照射到各射束的掩模底版24上的各个照射位置。

29.一次照射的多射束理想的是,以成形孔径阵列基板8的多个开口80的排列间距乘以上述所希望的缩小率而得的间距来排列。该描绘装置以连续地依次照射发射射束的光栅扫描方式进行描绘动作,在描绘所希望的图案时,根据图案,通过消隐控制将所需的射束控制为射束接通。在xy工作台22连续移动时,以使射束的照射位置追随xy工作台22的移动的方式通过偏转器18进行控制。

30.多电子束描绘装置的各部由未图示的控制装置进行控制。控制装置对描绘数据进行多级的数据转换处理而生成装置固有的发射数据。在发射数据中定义各发射的照射量以及照射位置坐标等。控制装置将各发射的照射量除以电流密度而求出照射时间t,在进行对应的发射时,以使射束接通照射时间t的方式,对消隐装置10的对应的消隐器施加偏转电压。

31.另外,控制装置对偏转量进行运算,以使各射束向发射数据所示的位置(坐标)偏转,并对偏转器18施加偏转电压。由此,将那一次发射的多射束集中偏转。

32.接下来,使用图3~图5对消隐装置10的构成进行说明。如图3所示,消隐装置10具备单元阵列区域100、设于单元阵列区域100的周围的控制电路150以及设于周缘部的焊盘部160。另外,控制电路150并不限于放置在单元阵列区域100的周缘部,也可以配置于不妨碍消隐装置10制作的范围内。

33.控制电路150经由布线152、焊盘部160以及未图示的外部布线从外部控制装置接收消隐控制信号。布线152在形成mos晶体管时形成,因此配置在钝化膜之下。控制电路150在接收到消隐控制信号时,经由消隐控制信号用布线142对消隐电极104(参照图5)施加电

压,进行消隐偏转。控制电路150由mos等构成电路,在最终级作为驱动器而设置cmos逆变器。

34.焊盘部160包含接地电极焊盘。接地电极102经由接地布线140(参照图5)、布线152而与接地电极焊盘连接。

35.在单元阵列区域100中,形成有多组如图4所示的单元c,一组的单元c具有贯通孔110和隔着贯通孔110而对置的一对接地电极102及消隐电极104。多组单元c以贯通孔110与成形孔径阵列基板8的各开口80的配置位置对应的方式排列成矩阵状。

36.图5是消隐装置10的单元阵列区域100的剖面图。如图5所示,消隐装置10具有基板120、设于基板120上的绝缘膜128、设于绝缘膜128上的接地布线140和消隐控制信号用布线142、设于接地布线140和消隐控制信号用布线142上的绝缘膜130、设于绝缘膜130上的保护膜(钝化膜)132、设于保护膜132上的防带电膜134、以及接地电极102和消隐电极104。

37.基板120例如也可以使用在硅层122与硅层126之间插入了氧化硅膜124的soi(silicon on insulator,绝缘体上硅)基板。

38.绝缘膜128、130例如为氧化硅膜。保护膜132例如为氮化硅膜。接地布线140以及消隐控制信号用布线142例如为铝、铜、钴。防带电膜134例如能够使用包含金属薄膜、导电性聚合物的材料等公知的材料。

39.在单元阵列区域100中,与贯通了保护膜132、绝缘膜130、绝缘膜128以及基板120的贯通孔110邻接地,在保护膜132上对置地配置接地电极102及消隐电极104。

40.接地电极102贯通保护膜132以及绝缘膜130而与下层的接地布线140连接。消隐电极104贯通保护膜132以及绝缘膜130而与下层的消隐控制信号用布线142连接。

41.另外,在单元阵列区域100的外侧,在硅层126上形成构成控制电路150的cmos晶体管等。

42.在单元c中设有贯通保护膜132以及绝缘膜130而使下层的接地布线140露出的开口h(孔)。防带电膜134也设于开口h的侧面(侧壁)以及接地布线140的表面,经由开口h而与接地布线140连接。即,设于开口h的侧面的防带电膜134成为将保护膜132及接地布线140上的绝缘膜130贯通而形成的、将保护膜132上的防带电膜134与下层的接地布线140连接的连接部。

43.开口h在各单元c中设有一个或多个。即,防带电膜134与接地布线140的连接部按每个单元c而设置。由此,能够防止发生防带电膜134的接地连接不良,因此能够防止在防带电膜134上产生局部的电位梯度,能够提高描绘精度。

44.在消隐装置10的制作中,首先,通过公知的cmos工艺在基板120形成构成控制电路150的晶体管等,并在基板120上形成绝缘膜128。绝缘膜128是所谓的层间绝缘膜,也可以形成有多层。接下来,在绝缘膜128上形成布线层,进行图案加工,形成接地布线140以及消隐控制信号用布线142。也可以在接地布线140的表面形成势垒金属。

45.接下来,以覆盖接地布线140以及消隐控制信号用布线142的方式形成绝缘膜130。接下来,在绝缘膜130上形成保护膜132。接下来,对基板120进行蚀刻而形成多个贯通孔110。

46.接下来,形成贯通保护膜132以及绝缘膜130并使接地布线140的表面露出的开口h。例如,开口h在各贯通孔110的附近形成一处或两处左右。接下来,在保护膜132上形成防

带电膜134。此时,在开口h的侧面以及从开口h露出的接地布线140的表面都形成防带电膜134。由此,形成将接地布线140与保护膜132上的防带电膜134连接的连接部。接下来,对防带电膜134进行图案加工,将电极形成区域的防带电膜134去除。由此,使得之后制作的消隐电极104与防带电膜134不会短路。

47.接下来,形成贯通保护膜132以及绝缘膜130并使接地布线140以及消隐控制信号用布线142的表面露出的开口。接着,进行au等的电解镀,形成与接地布线140连接的接地电极102以及与消隐控制信号用布线142连接的消隐电极104(电解镀所需的籽晶层未图示)。

48.这样,能够制造按每个单元设置有防带电膜134与接地布线140的连接部的消隐装置10。

49.在单元阵列区域100中将单元c配置成阵列状时,如图6所示,也可以将邻接的单元c的接地电极102连结,成为在规定方向(图中左右方向)上延伸的线状的接地电极102。

50.在未按每个单元c设置防带电膜134与接地布线140的连接部的情况下,如图7的(a)所示,通过防带电膜134而在邻接的单元c的开口部、贯通孔110的侧壁出现电位e,存在电子束向不希望的方向偏转的隐患。另一方面,如本实施方式那样,在按每个单元c设有防带电膜134与接地布线140的连接部的情况下,如图7的(b)所示,能够防止邻接的单元c的电位发生变化。

51.接地电极102并不限定于在一个方向上延伸,也可以在第一方向以及与第一方向正交的第二方向上延伸。例如,也可以是如图8所示的俯视形状为l字状的接地电极102。

52.另外,在单元阵列区域100中将单元c配置成阵列状时,也可以将邻接的单元c的l字状的接地电极102连结,如图9所示,接地电极102成为格子状。在被接地电极102包围的区域内,设有消隐电极104、贯通孔110以及开口h,成为一组的单元c。

53.另外,即使被接地电极102包围,若在防带电膜134与接地电极102的连接中产生不良,则由于散射电子等而使防带电膜134带电,如图10的(a)所示,在防带电膜134上产生电位vc。存在由于该带电产生的电场而使得邻接的单元的电子束向不希望的方向偏转的隐患。另一方面,如本实施方式那样,在按每个单元c设有防带电膜134与接地布线140的连接部的情况下,如图10的(b)所示,防带电膜134能够按每个单元可靠地得到接地电位。

54.在上述实施方式中,防带电膜134与接地布线140的连接部采用了通过在开口h的侧壁也形成防带电膜134而将防带电膜134与下层的接地布线140直接连接的构成,但如图11所示,也可以在开口h埋入钨等金属插塞106,并在保护膜132以及金属插塞106上形成防带电膜134。防带电膜134经由成为连接部的金属插塞106而与接地布线140电连接。另外,连接部只要是在开口h埋入导体而成者即可,作为导体,例如能够使用cu(铜)、al(铝)、多晶硅等。

55.另外,防带电膜134与接地布线140也可以不一定仅由连接部连接。在接地电极102、绝缘膜上形成的接地布线上设置防带电膜134的构成中,防带电膜134与接地布线140经由接地电极102等通过连接部连接。

56.形成于开口h的连接部优选在单元内设置一个以上,但不一定需要在单元内设置一个以上,若能够将局部的带电以及电位梯度充分地抑制到不会对描绘精度造成影响的程度,则也可以有不具有连接部的单元。另外,在单元内也可以设有多个连接部。

57.作为防带电膜134,也可以使用比接地电极102及消隐电极104的电阻高、且比保护

膜132、绝缘膜130的电阻低的高电阻膜,在形成接地电极102以及消隐电极104之后,在消隐装置10的整个面上形成该高电阻膜。

58.该高电阻膜具有如下程度的电阻值:使电极间不短路、且电子经由高电阻膜而从接地布线140流出,不积存负的电荷。高电阻膜也可以与消隐电极104连接。

59.在高电阻膜中,例如能够使用au(金)、ag(银)、cu(铜)、fe(铁)、cr(铬)、crn(氮化铬)、ti(钛)、tin(氮化钛)、tan(氮化钽)、tic(碳化钛)、pt(白金)等金属薄膜。金属薄膜在其膜厚达到几十nm左右时,电阻值随着膜厚的减少而急剧地升高。在高电阻膜中使用膜厚为几十nm、优选为几nm的金属薄膜。

60.另外,本发明并不原样地限定于上述实施方式,在实施阶段,能够在不脱离其主旨的范围内对构成要素进行变形而具体化。另外,能够通过上述实施方式所公开的多个构成要素的适当组合来形成各种发明。例如,也可以从实施方式所示的全部构成要素中删除几个构成要素。而且,也可以适当组合不同的实施方式中的构成要素。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。