1.本技术涉及显示技术领域,尤其涉及一种阵列基板、阵列基板的制造方法以及显示装置。

背景技术:

2.指纹识别技术已广泛应用于中小尺寸的显示屏中。指纹识别技术目前主要可以分为三种:电容式指纹识别技术、光学式指纹识别技术和超声波式指纹识别技术。光学指纹识别技术利用了光的折射和反射原理。当光照射到手指上,被手指反射到感光传感器上。由于指纹谷和脊对光的反射不同,感光传感器所接受到的谷和脊的反射光强不同。光信号被转换为电信号,从而进行指纹识别。光学指纹识别技术稳定性好,穿透能力强,造价成本相对较低,具有广阔的应用前景。然而,目前搭载有光学指纹识别功能的显示屏同层需要经过多道掩模制程,工艺复杂,成本高。

技术实现要素:

3.有鉴于此,本技术目的在于提供一种能够简化工艺,降低制造成本的阵列基板、阵列基板的制造方法以及显示装置。

4.本技术提供一种阵列基板,所述阵列基板包括指纹识别区,所述阵列基板包括:基板;金属电极层,位于所述基板的一面上,所述金属电极层包括第一电极;第一钝化层,覆盖于所述金属电极层远离所述基板的一面上,所述第一钝化层中开设有第一开口,所述第一开口位于所述指纹识别区,所述第一开口用于暴露所述第一电极;感光半导体层,设置于所述第一钝化层远离所述金属电极层的表面,所述感光半导体层覆盖所述第一开口,且与所述第一电极电连接;第一电极层,设于所述第一钝化层远离所述金属电极层的表面;第二钝化层,覆盖于所述感光半导体层和所述第一电极层远离所述第一钝化层的一面上,所述第二钝化层中开设有第二开口,所述第二开口用于暴露所述感光半导体层;第二电极层,设置于所述第二钝化层远离所述基板的一面上,所述第二电极层包括第二电极,所述第二电极延伸入所述第二开口中与所述感光半导体层电连接。

5.在一种实施方式中,所述第一钝化层中开设有第一通孔,所述第一通孔用于暴露所述金属电极层,所述第一电极层包括第一桥接电极,所述第一桥接电极延伸入所述第一通孔中与所述金属电极层电连接,所述第二钝化层中开设有第二通孔,所述第二通孔对应于所述第一通孔设置,所述第二通孔用于暴露所述第一桥接电极,所述第二电极层延伸入所述第二通孔中与所述第一桥接电极电连接,并经由所述第一桥接电极与所述金属电极层电连接。

6.在一种实施方式中,所述金属电极层包括指纹识别公共电极,所述指纹识别公共电极位于所述指纹识别区,且与所述第一电极间隔设置;

7.所述第一通孔包括第一子通孔,所述第一子通孔用于暴露所述指纹识别公共电极;

8.所述第一桥接电极包括第一子桥接电极,所述第一子桥接电极延伸入所述第一子通孔中与所述指纹识别公共电极电连接;

9.所述第二通孔包括第二子通孔,所述第二子通孔对应于所述第一子通孔设置,所述第二子通孔用于暴露所述第一子桥接电极,所述第二电极延伸入所述第二子通孔中与所述第一子桥接电极电连接,并经由所述第一子桥接电极与所述指纹识别公共电极电连接。

10.在一种实施方式中,所述阵列基板包括主显示区,所述主显示区与所述指纹识别区相邻设置;所述阵列基板还包括晶体管层,所述晶体管层设置于所述基板与所述金属电极层之间;所述金属电极层包括第二桥接电极,所述第二桥接电极位于所述主显示区,所述第二桥接电极电连接于所述晶体管层;所述第一通孔包括第三子通孔,所述第三子通孔位于所述主显示区,所述第三子通孔用于暴露所述第二桥接电极;所述第一桥接电极包括第二子桥接电极,所述第二子桥接电极延伸入所述第三子通孔中与所述第二桥接电极电连接;所述第二电极层包括像素电极,所述像素电极位于所述主显示区;所述第二通孔包括第四子通孔,所述第四子通孔与所述第三子通孔对应设置,所述像素电极延伸入所述第四子通孔中与所述第二子桥接电极电连接,并经由所述第二子桥接电极和所述第二桥接电极与所述晶体管层电连接。

11.在一种实施方式中,所述第一钝化层与所述第二钝化层中开设有第三通孔,所述第三通孔贯穿所述第一钝化层与所述第二钝化层,所述第三通孔用于暴露所述金属电极层,所述第二电极层延伸入所述第三通孔中与所述金属电极层电连接。

12.在一种实施方式中,所述第一电极层还包括中间电极,所述中间电极位于所述第一开口中,且电连接于所述第一电极与所述感光半导体层之间,所述感光半导体层在所述中间电极所在平面上的正投影与所述中间电极重叠。

13.在一种实施方式中,所述阵列基板还包括主显示区,所述主显示区与所述指纹识别区相邻设置,所述第一电极层包括显示公共电极,所述显示公共电极设置于所述第一钝化层远离所述金属电极层的表面,所述显示公共电极位于所述主显示区,所述第二电极层包括像素电极,所述像素电极位于所述主显示区,且与所述显示公共电极相对设置。

14.在一种实施方式中,所述阵列基板还包括晶体管层,所述晶体管层设置于所述基板与所述金属电极层之间,所述晶体管层包括第一晶体管,所述第一晶体管位于所述指纹识别区,所述第一晶体管与所述第一电极电连接,所述第一电极、所述感光半导体以及所述第二电极对应于所述第一晶体管设置。

15.在一种实施方式中,所述第一电极层包括指纹识别电容极板,所述指纹识别电容极板位于所述指纹识别区,所述第二电极还与所述指纹识别电容极板相对。

16.本技术还提供一种阵列基板的制造方法,所述阵列基板的制造方法包括以下步骤:提供基板,所述基板包括第一区域;在所述基板的一面上形成金属电极层,其中,所述金属电极层包括第一电极;在所述金属电极层远离所述基板的一面上形成第一钝化层,所述第一钝化层覆盖所述金属电极层;在所述第一钝化层中开设第一开口,所述第一开口位于所述第一区域,所述第一开口用于暴露所述第一电极;在所述第一钝化层远离所述金属电极层的表面形成第一电极层和感光半导体层,其中,所述感光半导体层覆盖所述第一开口,且与所述第一电极电连接;在所述感光半导体层和所述第一电极层远离所述第一钝化层的一面上形成第二钝化层,所述第二钝化层覆盖所述感光半导体层和所述第一电极层;在所

述第二钝化层中开设第二开口,所述第二开口用于暴露所述感光半导体层;在所述第二钝化层远离所述基板的一面上形成第二电极层,其中,所述第二电极层包括第二电极,所述第二电极延伸入所述第二开口中与所述感光半导体层电连接。

17.在一种实施方式中,所述在所述第一钝化层中开设第一开口的步骤包括:在所述第一钝化层中开设第一通孔,其中,所述第一通孔用于暴露所述金属电极层;

18.在所述第一钝化层远离所述金属电极层的表面形成第一电极层和感光半导体层的步骤包括:形成第一桥接电极,其中,所述第一桥接电极延伸入所述第一通孔中与所述金属电极层电连接;

19.所述在所述第二钝化层中开设第二开口的步骤包括:在所述第二钝化层中开设第二通孔,其中,所述第二通孔对应于所述第一通孔设置,所述第二通孔用于暴露所述第一桥接电极,所述第二电极层延伸入所述第二通孔中与所述第一桥接电极电连接,并经由所述第一桥接电极与所述金属电极层电连接。

20.在一种实施方式中,利用灰阶掩模或者半色调掩模经过一道掩模制程完成所述在所述第一钝化层远离所述金属电极层的表面形成第一电极层和感光半导体层的步骤,其中,所述第一电极层还包括中间电极,所述中间电极位于所述第一开口中,且电连接于所述第一电极与所述感光半导体层之间,所述感光半导体层在所述中间电极所在平面上的正投影与所述中间电极重叠。

21.本技术还提供一种显示装置,其包括如上任一项所述的阵列基板。

22.本技术提供一种阵列基板、阵列基板的制造方法以及显示装置。阵列基板包括指纹识别区。阵列基板包括:基板、金属电极层、第一钝化层、第一电极层、感光半导体层、第二钝化层以及第二电极层。金属电极层位于基板的一面上。金属电极层包括第一电极。第一钝化层覆盖于金属电极层远离基板的一面上。第一钝化层中开设有第一开口。第一开口位于指纹识别区。第一开口用于暴露第一电极。感光半导体层设置于第一钝化层远离金属电极层的表面。感光半导体层覆盖第一开口,且与第一电极电连接。第一电极层设置于第一钝化层远离金属电极层的表面。第二钝化层覆盖于感光半导体层和第一电极层远离第一钝化层的一面上。第二钝化层中开设有第二开口。第二开口用于暴露感光半导体层。第二电极层设置于第二钝化层远离基板的一面上。第二电极层包括第二电极。第二电极延伸入第二开口中与所述感光半导体层电连接。

23.根据本技术的阵列基板、阵列基板的制造方法和显示面板,通过将第一电极层与感光半导体层二者设置于第一钝化层远离金属电极层的表面,能够省略现有技术中第一电极层与感光半导体层之间的钝化层,从而简化了结构和制程。

附图说明

24.为了更清楚地说明本技术中的技术方案,下面将对实施方式描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施方式,对于本领域技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

25.图1为本技术实施方式提供的显示装置的平面示意图。

26.图2为本技术实施方式提供的显示装置的结构示意图。

27.图3(a)和图3(b)为图1的显示装置的阵列基板沿a

‑

a线的截面示意图。

28.图4为本技术另一实施方式的阵列基板的截面示意图。

29.图5为本技术又一实施方式的阵列基板的结构示意图。

30.图6为本技术提供的阵列基板的制造方法的流程图。

31.图7(a)至图7(m)为本技术一实施方式的阵列基板的制造方法的示意图。

32.图8(a)至图8(e)为本技术另一实施方式的阵列基板的制造方法的在第一钝化层远离金属电极层的表面形成第一电极层和感光半导体层的步骤的示意图。

具体实施方式

33.下面将结合本技术实施方式中的附图,对本技术中的技术方案进行清楚、完整地描述。显然,所描述的实施方式仅仅是本技术一部分实施方式,而不是全部的实施方式。基于本技术中的实施方式,本领域技术人员在没有做出创造性劳动前提下所获得的所有其他实施方式,都属于本技术保护的范围。

34.在本技术中,除非另有明确的规定和限定,第一特征在第二特征之“上”或之“下”可以包括第一和第二特征直接,也可以包括第一和第二特征不是直接接触而是通过它们之间的另外的特征接触。而且,第一特征在第二特征“之上”、“上方”和“上面”包括第一特征在第二特征正上方和斜上方,或仅仅表示第一特征水平高度高于第二特征。第一特征在第二特征“之下”、“下方”和“下面”包括第一特征在第二特征正下方和斜下方,或仅仅表示第一特征水平高度小于第二特征。

35.请参考图1至图2,图1为本技术实施方式提供的显示装置的平面示意图。图2为本技术实施方式提供的显示装置的结构示意图。本技术提供一种具有指纹识别功能的显示装置1000。在一个实施方式中,显示装置1000还具有触控功能。

36.显示装置1000可以为手机、平板电脑、笔记本、游戏机、数码相机、车载导航仪或自动取款机等。

37.本技术的显示装置1000为液晶显示装置。本技术不限定显示装置1000的显示类型,其可以为垂直电场型显示装置,例如,扭曲向列(twisted nematic,tn)型显示装置,多畴垂直配向(multi

‑

domain vertical alignment,mva)型显示装置,也可以是水平电场型显示装置,例如,边缘场开关(fringe field switching,ffs)型显示装置或者面内转换(in

‑

plane switching,ips)型显示装置。

38.显示装置1000包括阵列基板100、对向基板200以及液晶层300。阵列基板100和对向基板200相对设置。液晶层设置于阵列基板100和对向基板200之间。在本实施方式中,对向基板200为彩膜基板。在本技术其他实施方式中,阵列基板100可以为coa(color filter on array)型的阵列基板。此时,对向基板200不包括彩膜层。可以理解,显示装置1000还可以包括未提及的其他显示用部件,例如背光模组,胶框、边框、上下偏光片等。

39.请参考图3(a)和图3(b),图3(a)和图3(b)为图1的显示装置的阵列基板沿a

‑

a线的截面示意图。阵列基板100包括指纹识别区100a和主显示区100b。主显示区100b与指纹识别区100a相邻设置。在一种实施方式中,主显示区100b包围指纹识别区100a。指纹识别区100a用于指纹识别。指纹识别区100a也能进行显示。主显示区100b与指纹识别区100a相互配合显示完整画面。

40.阵列基板100包括:基板10、晶体管层20、平坦化层30、金属电极层40、第一钝化层

50、第一电极层60、感光半导体层70、第二钝化层80以及第二电极层90。晶体管层20、平坦化层30、金属电极层40、第一钝化层50、第一电极层60、感光半导体层70、第二钝化层80以及第二电极层90依次设置于基板10上。

41.基板10可以为玻璃基板或者塑料基板等。

42.晶体管层20设置于基板10的一面上。

43.晶体管层20为显示器件和指纹识别功能的驱动层。晶体管层20包括第一晶体管t1和第二晶体管t2。第一晶体管t1位于指纹识别区100a,用作指纹识别传感器的开关元件。第二晶体管t2位于主显示区100b,用作显示像素的开关元件。在本实施方式中,第一晶体管t1和第二晶体管t2均为顶栅型薄膜晶体管。具体地,晶体管层20包括依次层叠设置于基板10上的有源层21、栅极绝缘层22、栅极金属层23、层间绝缘层24以及源漏极金属层25。具体地,有源层21位于基板10的一面上。有源层21包括第一沟道部al1和第二沟道部al2。第一沟道部al1和第二沟道部al2排列设置在基板10的一面上。第一沟道部al1位于指纹识别区100a。第二沟道部al2位于主显示区100b。第一沟道部al1与第二沟道部al2的材料包括低温多晶硅。低温多晶硅通过在基板10上沉积非晶硅层,利用准分子激光退火将非晶硅层转变为多晶硅层而形成。其中,第一沟道部al1包括通道区211和位于通道区211两侧的两个轻掺杂区212。第一沟道部al1还包括两个重掺杂区213。每一重掺杂区213位于轻掺杂区212远离通道区211一侧。轻掺杂区212和重掺杂区213可以是n型掺杂区。在一个实施方式中,轻掺杂区212通过在低温多晶硅材料中掺杂磷离子形成。重掺杂区213通过在第一栅极ge1形成之后,在第一栅极ge1的遮挡下再次掺杂磷离子形成。第二沟道部al2的结构与第一沟道部al1相同,在此不再赘述。

44.栅极绝缘层22覆盖有源层21。栅极金属层23位于栅极绝缘层22远离基板10的一面上。栅极金属层23包括第一栅极ge1和第二栅极ge2。第一栅极ge1和第二栅极ge2排列设置在栅极绝缘层22远离基板10的一面上。第一栅极ge1对应于第一沟道部al1设置。第二栅极ge2对应于第二沟道部al2设置。层间绝缘层24覆盖栅极金属层23。源漏极金属层25位于层间绝缘层24远离栅极金属层23的一面上。源漏极金属层25包括第一源极se1、第一漏极de1、第二源极se2以及第二漏极de2。第一源极se1、第一漏极de1、第二源极se2以及第二漏极de2从指纹识别区100a到主显示区100b依次排列设置在层间绝缘层24远离栅极金属层23的一面上。第一源极se1和第一漏极de1对应于第一沟道部al1的两端设置,并经由开设于层间绝缘层24中的连接孔24a与第一沟道部al1的两端连接。第二源极se2和第二漏极de2对应于第二沟道部al2的两端设置,经由开设于层间绝缘层24中的连接孔24a与第二沟道部al2的两端连接。

45.其中,第一晶体管t1包括第一沟道部al1、第一栅极ge1、第一源极se1以及第一漏极de1。第二晶体管t2包括第二沟道部al2、第二栅极ge2、第二源极se2以及第二漏极de2。

46.栅极金属层23和源漏极金属层25的材料例如可以为钽(ta)、钨(w)、钼(mo)、铝(al)、钛(ti)、铜铌(cunb)合金等,也可以为例如铜(cu)和钼(mo)的叠层、铜(cu)和钼钛(moti)合金的叠层、铜(cu)和钛(ti)的叠层、铝(al)和钼(mo)的叠层以及钼(mo)和钽(ta)的叠层、钼(mo)和钨(w)的叠层、钼(mo)

‑

铝(al)

‑

钼(mo)的叠层等。栅极绝缘层22和层间绝缘层24的材料可以选自二氧化硅、二氧化氮、氮氧化硅及其叠层。

47.可以理解,本技术不限定晶体管层20中所包含的晶体管的结构,其可以为顶栅型

薄膜晶体管,也可以为底栅型薄膜晶体管,也可以为双栅极型薄膜晶体管。

48.可以理解,在一个实施方式中,基板10与晶体管层20之间还设置有用于对第一沟道部al1和第二沟道部al2进行遮光的遮光层ls。遮光层ls对应于第一沟道部al1和第二沟道部al2设置。遮光层ls的材料可以为金属材料,例如,钼(mo)或者铝(al)。遮光层ls靠近有源层21的一面上覆盖有缓冲层bl。缓冲层bl的材料可以选自二氧化硅、二氧化氮、氮氧化硅及其叠层。

49.平坦化层30覆盖在晶体管层20远离层间绝缘层24的一面上。平坦化层30中开设有多个过孔。多个过孔用于连接金属电极层40与晶体管层20。具体地,多个过孔包括第一过孔30a和第二过孔30b。第一过孔30a位于指纹识别区100a。第一过孔30a用于暴露第一晶体管t1的第一漏极de1。第二过孔30b位于主显示区100b。第二过孔30b用于暴露第二晶体管t2的第二漏极de2。平坦化层30的材料可以选自二氧化硅、二氧化氮、氮氧化硅及其叠层,或者有机材料,例如丙烯酸树脂(acrylic resin)或者全氟烷氧基树脂(pfa)。

50.金属电极层40位于平坦化层30远离晶体管层20的一面上。金属电极层40包括第一电极41、指纹识别公共电极42、触控走线43以及第二桥接电极44。在本实施方式中,第一电极41、指纹识别公共电极42、触控走线43以及第二桥接电极44彼此间隔排列在平坦化层30远离晶体管层20的一面上,且彼此之间相互绝缘。在本技术其他实施方式中,并不限制它们的排列方式。其中,第一电极41和指纹识别公共电极42位于指纹识别区100a。第一电极41通过开设于平坦化层30中的第一过孔30a电连接于第一晶体管t1的第一漏极de1。触控走线43以及第二桥接电极44位于主显示区100b。触控走线43为触控模组传输信号。第二桥接电极44通过开设于平坦化层30中的第二过孔30b电连接于第二晶体管t2的第二漏极de2。

51.金属电极层40的材料可以选自钽(ta)、钨(w)、钼(mo)、铝(al)、钛(ti)、铜铌(cunb)合金等,也可以为例如铜(cu)和钼(mo)的叠层、铜(cu)和钼钛(moti)合金的叠层、铜(cu)和钛(ti)的叠层、铝(al)和钼(mo)的叠层以及钼(mo)和钽(ta)的叠层、钼(mo)和钨(w)的叠层、钼(mo)

‑

铝(al)

‑

钼(mo)的叠层等。

52.第一钝化层50覆盖于金属电极层40远离平坦化层30的一面上。第一钝化层50中开设有第一开口50a。第一开口50a位于指纹识别区100a,第一开口50a用于暴露第一电极41。第一钝化层50中还开设有多个第一通孔51。多个第一通孔51的深度一致,并且在同一掩模制程中形成。第一通孔51用于暴露金属电极层40。具体地,多个第一通孔51包括第一子通孔501、第三子通孔502、第五子通孔503以及第六子通孔504。第五子通孔503、第一子通孔501、第六子通孔504以及第三子通孔502依次排列于金属电极层40远离基板10的一面上。其中,第一子通孔501和第五子通孔503位于指纹识别区100a。第一子通孔501用于暴露指纹识别公共电极42。第五子通孔503位于第一开口50a与第一子通孔501之间。第五子通孔503用于暴露第一电极41。第三子通孔502和第六子通孔504位于主显示区100b。第三子通孔502用于暴露第二桥接电极44。第六子通孔504用于暴露触控走线43。

53.第一电极层60也设置于第一钝化层50远离金属电极层40的表面。第一电极层60包括第一桥接电极601、指纹识别电容极板63、触控电极64以及公共电极65。其中,第一桥接电极601包括第一子桥接电极61和第二子桥接电极62。在本实施方式中,指纹识别电容极板63、第一子桥接电极61、公共电极65、触控电极64以及第二子桥接电极62依次排列于第一钝化层50远离金属电极层40的表面上。在本技术中,并不限制它们的排列方式。第一子桥接电

极61和指纹识别电容极板63位于指纹识别区100a。第一子桥接电极61延伸入第一子通孔501中与指纹识别公共电极42电连接。指纹识别电容极板63位于感光半导体层70与第一子桥接电极61之间,并延伸入第五子通孔503与第一电极41电连接。第二子桥接电极62、触控电极64以及公共电极65位于主显示区100b。第二子桥接电极62延伸入第三子通孔502中与第二桥接电极44电连接。触控电极64与触控走线43对应设置。触控电极64延伸入第六子通孔504中与触控走线43电连接。公共电极65用于对显示像素施加电压,从而控制液晶偏转。

54.感光半导体层70设置于第一钝化层50远离金属电极层40的表面上。感光半导体层70覆盖第一开口50a,且与第一电极41电连接。感光半导体层70作为指纹识别传感器的感光层,用于接收指纹反射回来的光信号,并将光信号转换层电信号。在一个实施方式中,感光半导体层70包括依次层叠设置于第一电极41远离晶体管层20的一面上的第一非晶硅层71、第二非晶硅层72以及第三非晶硅层73。第一非晶硅层71的材料包括n型掺杂的非晶硅。第二非晶硅层72的材料包括本征非晶硅。第三非晶硅层73的材料包括p型掺杂的非晶硅。在另一个实施方式中,感光半导体层70也可以仅包括层叠设置的第一非晶硅层71和第二非晶硅层72,即本征非晶硅和p型掺杂的非晶硅。

55.第二钝化层80覆盖于感光半导体层70和第一电极层60远离第一钝化层50的一面上。第二钝化层80中开设有第二开口80a。第二开口80a用于暴露感光半导体层70。第二钝化层80中开设有多个第二通孔81。第二通孔81对应于第一通孔51设置。第二通孔81用于暴露第一桥接电极601。具体地,第二通孔81包括第二子通孔801和第四子通孔802。第二子通孔801对应于第一子通孔501设置。第二子通孔801用于暴露第一子桥接电极61。第四子通孔802对应于第三子通孔502设置,第四子通孔802用于暴露第二子桥接电极62。

56.第二电极层90设置于第二钝化层80远离基板10的一面上。第二电极层90延伸入第二通孔81中与第一桥接电极601电连接,并经由第一桥接电极601与金属电极层40电连接。第二电极层90包括第二电极91和像素电极92。像素电极92位于主显示区100b。像素电极92的一部分与公共电极65相对设置,用于与公共电极65共同作用,控制液晶偏转。像素电极92的另一部分延伸入第四子通孔802中与第二子桥接电极62电连接,并经由第二子桥接电极62和第二桥接电极44与第二漏极de2电连接。第二电极91的一部分延伸入第二开口80a中与感光半导体层70电连接。第二电极91的另一部分延伸入第二子通孔801中与第一子桥接电极61电连接,并经由第一子桥接电极61与指纹识别公共电极42电连接。第二电极91还与指纹识别电容极板63相对。第二电极91与指纹识别电容极板63共同构成指纹识别电容极板63。

57.本技术的指纹识别传感器包括第一电极41、感光半导体层70以及第二电极91。第一电极41作为指纹识别传感器的下电极,第二电极91作为指纹识别传感器的上电极与感光半导体层70共同构成非晶硅pin二极管。非晶硅pin二极管具有较高的指纹识别的精度。在一个实施方式中,第一电极41、感光半导体层70以及第二电极91对应于第一晶体管t1设置。第一电极41、感光半导体层70以及第二电极91可以位于第一晶体管t1正上方。由此,能够提高开口率。

58.本技术提供一种阵列基板和显示装置。阵列基板包括指纹识别区。阵列基板包括:基板、金属电极层、第一钝化层、第一电极层、感光半导体层、第二钝化层以及第二电极层。金属电极层位于基板的一面上。金属电极层包括第一电极。第一钝化层覆盖于金属电极层

远离基板的一面上。第一钝化层中开设有第一开口。第一开口位于指纹识别区。第一开口用于暴露第一电极。感光半导体层设置于第一钝化层远离金属电极层的表面。感光半导体层覆盖第一开口,且与第一电极电连接。第一电极层设置于第一钝化层远离金属电极层的表面。第二钝化层覆盖于感光半导体层和第一电极层远离第一钝化层的一面上。第二钝化层中开设有第二开口。第二开口用于暴露感光半导体层。第二电极层设置于第二钝化层远离基板的一面上。第二电极层包括第二电极。第二电极延伸入第二开口中与所述感光半导体层电连接。

59.根据本技术的阵列基板和显示面板,通过将第一电极层与感光半导体层二者设置于第一钝化层远离金属电极层的表面,能够省略现有技术中第一电极层与感光半导体层之间的钝化层,从而简化了结构,并节省了第一道掩模制程。

60.另一方面,通过利用第一电极层作为第二电极层与金属电极层的桥接结构,使第二钝化层中开孔的深度为同一深度。相较于现有技术中,第二钝化层中的开孔深度不一,本技术的第二钝化层采用一道掩模制程即可完成开孔,可以节约第二道掩模制程,同时降低了曝光和蚀刻过程中由于开孔深度不同导致的工艺风险,提升了制程稳定性和工艺可行性,并提高了产品良率。

61.本技术的金属电极层直接设置于平坦化层上。相较于现有技术中,省略了金属电极层与平坦化层之间的钝化层,能够节省第三道掩模制程。现有技术中金属电极层与平坦化层之间的钝化层的作用是防止在刻蚀金属电极层时,损伤平坦化层,可以通过将金属电极层的材料替换为能够采用湿法刻蚀图案化的材料,例如mo/al/mo的叠层金属,利用湿法刻蚀图案化金属电极层来避免对平坦化层的损伤。由于省略了金属电极层与平坦化层之间的钝化层,用于连接金属电极层与源漏极金属层,第一电极41与第一漏极de1的第一过孔30a的深度变浅,降低蚀刻时锥角(taper)的底切(undercut)风险,提升了金属电极层与源漏极金属层的连接可靠性。同时,在现有技术中,需要在平坦化层与钝化层中形成套设的开孔,在平坦化层中开设的孔的面积更大,会导致开口率损失。

62.请参考图4,图4为本技术另一实施方式的阵列基板的截面示意图。图4的实施方式与图1的实施方式基本相同,不同点在于:第一钝化层50与第二钝化层80中开设有第三通孔52。第三通孔52贯穿第一钝化层50与第二钝化层80。第三通孔52用于暴露金属电极层40。第二电极层90延伸入第三通孔52中与金属电极层40电连接。

63.具体地,像素电极92的一部分与公共电极65相对设置,用于与公共电极65共同作用,控制液晶偏转。第三通孔52包括第七子通孔506和第八子通孔507。第七子通孔506对应于第二桥接电极44设置。像素电极92的另一部分延伸入第七子通孔506中第二桥接电极44电连接,并经由第二桥接电极44与第二晶体管t2电连接。第二电极91的一部分延伸入第二开口80a中与感光半导体层70电连接。第八子通孔507用于暴露指纹识别公共电极42。第二电极91的另一部分延伸入第八子通孔507中与指纹识别公共电极42电连接。

64.请参考图5,图5为本技术又一实施方式的阵列基板的结构示意图。图5的实施方式与图1的实施方式基本相同,不同点在于:第一电极层60还包括中间电极66。中间电极66位于第一开口50a中,且电连接于第一电极41与感光半导体层70之间。中间电极66位于感光半导体层70的正下方。中间电极66与感光半导体层70的形状完全一致。换句话说,感光半导体层70在中间电极66所在平面上的正投影与中间电极66重叠。中间电极66位于感光半导体层

70通过同一道掩模制程形成。通过在感光半导体层70与第一电极41之间形成有中间电极66,且中间电极66与第一桥接电极601、指纹识别电容极板63、触控电极64以及公共电极65采用相同材料制成,能够通过一道掩模制程同时完成第一电极层60和感光半导体层70的制造,为本技术的阵列基板省略了第四道掩模制程。

65.本实施方式的阵列基板制程中,第一电极层与感光半导体层可以在同一制程中制造,由此简化制程,减少制程中所需要的掩模数。

66.本技术还提供一种阵列基板的制造方法。

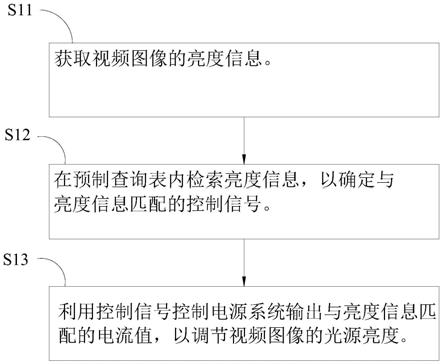

67.请参考图6,图6为本技术提供的阵列基板的制造方法的流程图。

68.本技术提供的阵列基板的制造方法包括以下步骤:

69.101:提供基板,其中,基板包括第一区域。

70.102:在基板的一面上形成金属电极层,其中,金属电极层包括第一电极。

71.103:在金属电极层远离基板的一面上形成第一钝化层,第一钝化层覆盖金属电极层。

72.104:在第一钝化层中开设第一开口,第一开口位于第一区域,第一开口用于暴露第一电极。

73.在一个实施方式中,步骤104还包括:在第一钝化层中开设第一通孔,其中,第一通孔用于暴露金属电极层。

74.105:在第一钝化层远离金属电极层的表面形成第一电极层和感光半导体层,其中,感光半导体层覆盖第一开口,且与第一电极电连接。

75.在一个实施方式中,步骤105还包括:形成第一桥接电极,其中,第一桥接电极延伸入第一通孔中与金属电极层电连接。

76.106:在感光半导体层和第一电极层远离第一钝化层的一面上形成第二钝化层,第二钝化层覆盖感光半导体层和第一电极层;

77.107:在第二钝化层中开设第二开口,第二开口用于暴露感光半导体层;

78.在一个实施方式中,步骤107还包括:在第二钝化层中开设第二通孔,其中,第二通孔对应于第一通孔设置,第二通孔用于暴露第一桥接电极。

79.108:在第二钝化层远离基板的一面上形成第二电极层,其中,第二电极层包括第二电极,第二电极延伸入第二开口中与感光半导体层电连接。

80.在一个实施方式中,第二电极层延伸入第二通孔中与第一桥接电极电连接,并经由第一桥接电极与金属电极层电连接。

81.请参考图7(a)至图7(m),图7(a)至图7(m)为本技术一实施方式的阵列基板的制造方法的示意图。

82.本技术一实施方式的阵列基板的制造方法具体包括以下步骤:

83.201:请参考图7(a),提供基板10。基板10可以为玻璃基板10或者塑料基板10等。基板10包括第一区域10a和第二区域10b。第一区域10a和第二区域10b相邻设置。第一区域10a为用于形成阵列基板的指纹识别区的区域。第一区域10a为用于形成阵列基板的主显示区。

84.在基板10上形成遮光层ls。形成遮光层ls的方法包括在基板10上沉积遮光金属层,通过曝光、显影和刻蚀对遮光金属层进行图案化,得到遮光层ls。遮光层ls的一部分位于第一区域10a,另一部分位于第二区域10b。

85.202:请参考图7(a)至图7(b),在遮光层ls远离基板10的一面上形成缓冲层bl。缓冲层bl覆盖遮光层ls。在缓冲层bl远离遮光层ls的一面上形成第一半导体图案sl1和第二半导体图案sl2。第一半导体图案sl1位于第一区域10a。第二半导体图案sl2位于第二区域10b。

86.形成第一半导体图案sl1和第二半导体图案sl2的步骤包括在缓冲层bl远离遮光层ls的一面上沉积半导体材料层,通过曝光、显影和刻蚀对半导体材料层进行图案化,得到第一半导体图案sl1和第二半导体图案sl2。

87.在一个实施方式中,第一半导体图案sl1和第二半导体图案sl2的材料为低温多晶硅材料。第一半导体图案sl1和第二半导体图案sl2通过在基板10上沉积非晶硅层,利用准分子激光退火将非晶硅层转变为多晶硅层,并图案化多晶硅层形成。

88.203:请参考图7(c),利用掩模对第一半导体图案sl1和第二半导体图案sl2进行第一次掺杂。掺杂后的第一半导体图案sl1包括本征半导体区sl11和掺杂区sl12。掺杂区sl12位于本征半导体区sl11的相对两侧。掺杂后的第二半导体图案sl2与第一半导体图案sl1结构相同,在此不再赘述。第一次掺杂可以使用磷离子进行掺杂。

89.204:请参考图7(d),在第一次掺杂后的第一半导体图案sl1和第二半导体图案sl2远离基板10的一面上形成栅极绝缘层22。栅极绝缘层22覆盖掺杂后的半导体层sl。栅极绝缘层22远离基板10的一面形成栅极金属层23。栅极金属层23包括第一栅极ge1和第二栅极ge2。第一栅极ge1对应于第一半导体图案sl1设置。第二栅极ge2对应于第二半导体图案sl2设置。以第一栅极ge1和第二栅极ge2作为遮挡层,对第一半导体图案sl1和第二半导体图案sl2进行第二次掺杂,得到第一沟道部al1和第二沟道部al2。其中,第一沟道部al1包括通道区211和位于通道区211两侧的两个轻掺杂区212。第一沟道部al1还包括两个重掺杂区213。每一重掺杂区213位于轻掺杂区212远离通道区211一侧。轻掺杂区212和重掺杂区213可以是n型掺杂区。

90.205:请参考图7(e),在第一栅极ge1和第二栅极ge2远离栅极绝缘层22的一面形成层间绝缘层24。层间绝缘层24覆盖栅极金属层23。在层间绝缘层24中形成连接孔24a。连接孔24a位于第一沟道部al1和第二沟道部al2的两侧。

91.206:请参考图7(e)和7(f),在层间绝缘层24远离栅极金属层23的一面形成第一源极se1、第一漏极de1、第二源极se2以及第二漏极de2。第一源极se1和第一漏极de1对应于第一沟道部al1的两端设置,并经由开设于层间绝缘层24中的连接孔24a与第一沟道部al1的两端连接。第二源极se2和第二漏极de2对应于第二沟道部al2的两端设置,经由开设于层间绝缘层24中的连接孔24a与第二沟道部al2的两端连接。

92.在第一源极se1、第一漏极de1、第二源极se2以及第二漏极de2远离层间绝缘层24的一面上形成平坦化层30。平坦化层30覆盖第一源极se1、第一漏极de1、第二源极se2以及第二漏极de2。

93.207:请参考图7(f)和7(g),平坦化层30中开设有多个过孔。具体地,多个过孔包括第一过孔30a和第二过孔30b。第一过孔30a用于暴露第一晶体管t1的第一漏极de1。第二过孔30b用于暴露第二晶体管t2的第二漏极de2。

94.208:请参考图7(a)、7(g)和图7(h),在平坦化层30远离第一源极se1的一面上形成金属电极层40。金属电极层40包括第一电极41、指纹识别公共电极42、触控走线43以及第二

桥接电极44。其中,第一电极41和指纹识别公共电极42位于第一区域10a。第一电极41通过开设于平坦化层30中的第一过孔30a电连接于第一晶体管t1的第一漏极de1。触控走线43以及第二桥接电极44位于第二区域10b。触控走线43为触控模组传输信号。第二桥接电极44通过开设于平坦化层30中的第二过孔30b电连接于第二晶体管t2的第二漏极de2。

95.209:请一并参考图7(h)和图7(i),金属电极层40远离平坦化层30的一面上形成第一钝化层50。第一钝化层50中开设有第一开口50a。第一开口50a位于第一区域10a,第一开口50a用于暴露第一电极41。第一钝化层50中还开设有多个第一通孔51。多个第一通孔51的深度一致,并且在同一掩模制程中形成。第一通孔51用于暴露金属电极层40。具体地,多个第一通孔51包括第一子通孔501、第三子通孔502、第五子通孔503以及第六子通孔504。第五子通孔503、第一子通孔501、第六子通孔504以及第三子通孔502依次排列于金属电极层40远离基板10的一面上。其中,第一子通孔501和第五子通孔503位于指纹识别区100a。第一子通孔501用于暴露指纹识别公共电极42。第五子通孔503位于第一开口50a与第一子通孔501之间。第五子通孔503用于暴露第一电极41。第三子通孔502和第六子通孔504位于主显示区100b。第三子通孔502用于暴露第二桥接电极44。第六子通孔504用于暴露触控走线43。

96.210:请参考图7(i)至7(j),在第一钝化层50远离金属电极层40的表面形成感光半导体层70。感光半导体层70覆盖第一开口50a,且与第一电极41电连接。在一个实施方式中,感光半导体层70包括依次层叠设置于第一电极41远离晶体管层20的一面上的第一非晶硅层71、第二非晶硅层72以及第三非晶硅层73。第一非晶硅层71的材料包括n型掺杂的非晶硅。第二非晶硅层72的材料包括本征非晶硅。第三非晶硅层73的材料包括p型掺杂的非晶硅。在另一个实施方式中,感光半导体层70也可以只包括层叠设置的第一非晶硅层71和第二非晶硅层72,即本征非晶硅和p型掺杂的非晶硅。

97.211:请参考图7(i)至图7(k),在第一钝化层50远离金属电极层40的表面上形成第一电极层60。第一电极层60包括第一桥接电极601、指纹识别电容极板63、触控电极64以及公共电极65。第一桥接电极601包括第一子桥接电极61和第二子桥接电极62。在本实施方式中,指纹识别电容极板63、第一子桥接电极61、公共电极65、触控电极64以及第二子桥接电极62依次排列于第一钝化层50远离金属电极层40的表面上。在本技术中,并不限制它们的排列方式。第一子桥接电极61和指纹识别电容极板63位于第一区域10a。第一子桥接电极61延伸入第一子通孔501中与指纹识别公共电极42电连接。指纹识别电容极板63位于感光半导体层70与第一子桥接电极61之间,并延伸入第五子通孔503与第一电极41电连接。第二子桥接电极62、触控电极64以及公共电极65位于第二区域10b。第二子桥接电极62延伸入第三子通孔502中与第二桥接电极44电连接。触控电极64与触控走线43对应设置。触控电极64延伸入第六子通孔504中与触控走线43电连接。公共电极65用于对显示像素施加电压,从而控制液晶偏转。

98.212:请参考图7(i)至7(l),在感光半导体层70和第一电极层60远离第一钝化层50的一面上形成第二钝化层80。在第二钝化层80中还开设第二开口80a。第二开口80a用于暴露感光半导体层70。第二钝化层80中开设多个第二通孔81。第二通孔81对应于第一通孔51设置。第二通孔81用于暴露第一桥接电极601。具体地,第二通孔81包括第二子通孔801和第四子通孔802。第二子通孔801对应于第一子通孔501设置。第二子通孔801用于暴露第一子桥接电极61。第四子通孔802对应于第三子通孔502设置,第四子通孔802用于暴露第二子桥

接电极62。

99.213:请参考图7(h)至7(m),在第二钝化层80远离基板10的一面上形成第二电极层90。第二电极层90延伸入第二通孔81中与第一桥接电极601电连接,并经由第一桥接电极601与金属电极层40电连接。第二电极层90包括第二电极91和像素电极92。像素电极92位于第二区域10b。像素电极92的一部分与公共电极65相对设置,用于与公共电极65共同作用,控制液晶偏转。像素电极92的另一部分延伸入第四子通孔802中与第二子桥接电极62电连接,并经由第二子桥接电极62和第二桥接电极44与第二漏极de2电连接。第二电极91的一部分延伸入第二开口80a中与感光半导体层70电连接。第二电极91的另一部分延伸入第二子通孔801中与第一子桥接电极61电连接,并经由第一子桥接电极61与指纹识别公共电极42电连接。第二电极91还与指纹识别电容极板63相对。第二电极91与指纹识别电容极板63共同构成指纹识别电容极板63。

100.根据本技术的阵列基板的制造方法,通过将第一电极层与感光半导体层二者设置于第一钝化层远离金属电极层的表面,能够省略现有技术中第一电极层与感光半导体层之间的钝化层,从而简化了结构,并节省了第一道掩模制程。

101.另一方面,通过利用第一电极层作为第二电极层与金属电极层的桥接结构,使第二钝化层中开孔的深度为同一深度。相较于现有技术中,第二钝化层中的开孔深度不一,本技术的第二钝化层采用一道掩模制程即可完成开孔,可以节约第二道掩模制程,同时降低了曝光和蚀刻过程中由于开孔深度不同导致的工艺风险,提升了制程稳定性和工艺可行性,并提高了产品良率。本技术的金属电极层直接设置于平坦化层上。相较于现有技术中,省略了金属电极层与平坦化层之间的钝化层,能够节省第三道掩模制程。现有技术中金属电极层与平坦化层之间的钝化层的作用是防止在刻蚀金属电极层时,损伤平坦化层,可以通过将金属电极层的材料替换为能够采用湿法刻蚀图案化的材料,例如mo/al/mo的叠层金属,利用湿法刻蚀图案化金属电极层来避免对平坦化层的损伤。由于省略了金属电极层与平坦化层之间的钝化层,用于连接金属电极层与源漏极金属层,第一电极41与第一漏极de1的第一过孔30a的深度变浅,降低蚀刻时锥角(taper)的底切(undercut)风险,提升了金属电极层与源漏极金属层的连接可靠性。同时,在现有技术中,需要在平坦化层与钝化层中形成套设的开孔,在平坦化层中开设的孔的面积更大,会导致开口率损失。

102.本技术的另一个实施方式中,请参考图4,在步骤212中,不形成第一子桥接电极61和第二子桥接电极62。在步骤213中,也不形成第二子通孔801和第四子通孔802。蚀刻第一钝化层50与第二钝化层80,形成第三通孔52。第三通孔52贯穿第一钝化层50与第二钝化层80。第三通孔52用于暴露金属电极层40。在步骤214中,第二电极层90延伸入第三通孔52中与金属电极层40电连接。

103.具体地,像素电极92的一部分与公共电极65相对设置,用于与公共电极65共同作用,控制液晶偏转。第三通孔52包括第七子通孔506和第八子通孔507。第七子通孔506对应于第二桥接电极44设置。像素电极92的另一部分延伸入第七子通孔506中第二桥接电极44电连接,并经由第二桥接电极44与第二晶体管t2电连接。第二电极91的一部分延伸入第二开口80a中与感光半导体层70电连接。第八子通孔507用于暴露指纹识别公共电极42。第二电极91的另一部分延伸入第八子通孔507中与指纹识别公共电极42电连接。

104.在一种实施方式中,步骤105:在第一钝化层远离金属电极层的表面形成第一电极

层和感光半导体层的步骤可以利用灰阶掩模或者半色调掩模经过一道掩模制程完成,其中,第一电极层还包括中间电极,中间电极位于第一开口中,且电连接于第一电极与感光半导体层之间。

105.具体地,请参考图8(a)至图8(e),图8(a)至图8(e)为本技术另一实施方式的阵列基板的制造方法的在第一钝化层远离金属电极层的表面形成第一电极层和感光半导体层的步骤的示意图。

106.步骤301:请参考图8(a),在第一钝化层50远离金属电极层40的表面形成第一电极材料层600和感光半导体材料层700,在第一电极材料层600和感光半导体材料层700远离第一钝化层50的表面形成蚀刻阻挡层400;利用灰阶掩模或者半色调掩模对蚀刻阻挡层400进行曝光和显影,在第一位置形成第一蚀刻阻挡图案401,第一位置对应于感光半导体层。在第二位置形成第二蚀刻阻挡图案402,第二位置对应于金属电极层。其中,第一蚀刻阻挡图案401的厚度大于第二蚀刻阻挡图案402的厚度。

107.步骤302:请参考图8(a)和图8(b),刻蚀除去没有被第一蚀刻阻挡图案401和第二蚀刻阻挡图案402覆盖的感光半导体材料层700。这一步蚀刻可以采用干法蚀刻。

108.步骤303:请参考图8(a)至图8(c),刻蚀除去没有被第一蚀刻阻挡图案401和第二蚀刻阻挡图案402覆盖的第一电极材料层600。这一步蚀刻可以采用湿法蚀刻。

109.步骤304:请参考图8(c)和图8(d),灰化除去第二蚀刻阻挡图案402,保留第一蚀刻阻挡图案401。由于第一蚀刻阻挡图案401的厚度大于第二蚀刻阻挡图案402的厚度,可以控制灰化工艺,保留第一蚀刻阻挡图案401,只是减少第一蚀刻阻挡图案401的厚度。

110.步骤305:请参考图5、图8(d)和图8(e),蚀刻除去没有被第一蚀刻阻挡图案401覆盖的感光半导体材料700,并剥离第一蚀刻阻挡图案401,得到第一电极层60和感光半导体层70。其中,第一电极层60还包括中间电极66,中间电极66位于第一开口50a中,且电连接于第一电极41与感光半导体层70之间。中间电极66位于感光半导体层70的正下方。中间电极66与感光半导体层70的形状完全一致。换句话说,感光半导体层70在中间电极66所在平面上的正投影与中间电极66重叠。

111.本实施方式可以利用灰阶掩模或者半色调掩模经过一道掩模制程完成在第一钝化层远离金属电极层的表面形成第一电极层和感光半导体层的步骤,为本技术的阵列基板的制造方法省略了第四道掩模制程。

112.可以理解,本实施方式的阵列基板的制造方法的步骤201至步骤205可以替换图7(a)至图7(i)所示的阵列基板的制造方法中的步骤208至210,除步骤208至210之外的其他步骤均可采用与图7(a)至图7(i)所示的阵列基板的制造方法中的步骤,在此不再赘述。

113.本实施方式的阵列基板制程中,第一电极层与感光半导体层可以在同一制程中制造,由此简化制程,减少制程中所需要的掩模数。以上对本技术实施方式提供了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施方式的说明只是用于帮助理解本技术。同时,对于本领域的技术人员,依据本技术的思想,在具体实施方式及应用范围上均会有改变之处,综上所述,本说明书内容不应理解为对本技术的限制。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。