技术特征:

1.一种芯片设计中基于综合网表提取时钟树的方法,其特征在于包括步骤:在逻辑综合步骤中,获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息;根据前述获取的信息拼接全芯片的时钟结构,从时钟约束文件中获取时钟定义的点作为初始时钟源;基于全芯片的时钟结构信息,从初始时钟源开始采用递归算法逐级往后循迹以形成全芯片时钟树网络;在所述循迹的过程中,根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点;循迹结束,对顶层时钟树和子模块时钟树的时钟结构信息进行归类以形成时钟树实现指导文件。2.根据权利要求1所述的方法,其特征在于:从初始时钟源开始采用递归算法逐级往后循迹的步骤如下,s310,将前述初始时钟源作为顶层时钟源;s320,获取顶层时钟源,判断时钟是否从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口或者连接到一个子模块内部的触发器的时钟端;判定为是时,执行步骤s331;否则,执行步骤s332;s331,判定时钟从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口时执行步骤s3311,判定时钟从前述时钟源连接到一个子模块内部的触发器的时钟端时执行步骤s3312;s3311,将此段时钟配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将前述模拟ip端口或者芯片输出端口配置为此段时钟树的终点,执行步骤s340;s3312,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到内部的触发器配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块内部的触发器配置为此段时钟树的终点,执行步骤s340;s332,判断时钟是否从时钟源穿入一个子模块并从该子模块穿出,判定为是时,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到该子模块的输出端配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块的输出端配置为此段时钟树的终点;以及,将该子模块的输出端配置为顶层下一级时钟源,返回到步骤s320进行下一级往后循迹;s340,结束循迹。3.根据权利要求1所述的方法,其特征在于:所述时钟树实现指导文件包括顶层时钟树实现指导文件和子模块时钟树实现指导文件,所述顶层时钟树实现指导文件包括顶层时钟树的起点和终点信息,所述子模块时钟树实现指导文件包括各子模块时钟树的起点和终点信息。4.根据权利要求3所述的方法,其特征在于:获取时钟树实现人员的通信账户信息,根据前述通信账户信息将前述顶层时钟树实现指导文件和子模块时钟树实现指导文件发送给时钟树实现人员。

5.根据权利要求1所述的方法,其特征在于:通过时序分析工具分析芯片顶层和芯片各子模块的逻辑综合网表和时钟约束文件信息后,拼接全芯片的时钟结构。6.根据权利要求1所述的方法,其特征在于:所述模块信息为子模块列表。7.一种芯片设计方法,至少包括时钟设计步骤、逻辑综合步骤、布局步骤、时钟树实现步骤和布线步骤,其特征在于:在逻辑综合步骤中,通过权利要求1

‑

5中任一项所述的方法获取时钟树实现指导文件,作为后期的时钟树实现步骤的指导信息。8.一种芯片设计系统,至少包括时钟设计单元、逻辑综合单元、布局单元、时钟树实现单元和布线单元,其特征在于:所述逻辑综合单元包括时钟分析模块,所述时钟分析模块被配置为:通过权利要求1

‑

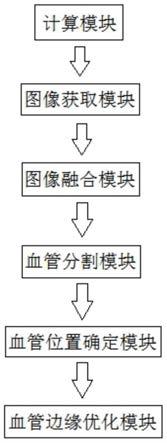

5中任一项所述的方法获取时钟树实现指导文件,并将所述时钟树实现指导文件发送至前述时钟树实现单元。9.一种芯片设计中基于综合网表提取时钟树的装置,其特征在于包括如下结构:信息采集模块,用于在逻辑综合步骤中,获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息;初始化模块,用于根据前述获取的信息拼接全芯片的时钟结构,从时钟约束文件中获取时钟定义的点作为初始时钟源;时钟树循迹模块,用于基于全芯片的时钟结构信息,从初始时钟源开始采用递归算法逐级往后循迹以形成全芯片时钟树网络;在所述循迹的过程中,根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点;结果处理模块,用于在循迹结束后,对顶层时钟树和子模块时钟树的时钟结构信息进行归类以形成时钟树实现指导文件。10.根据权利要求9所述的方法,其特征在于:所述时钟树循迹模块被配置为执行如下步骤:s310,将前述初始时钟源作为顶层时钟源;s320,获取顶层时钟源,判断时钟是否从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口或者连接到一个子模块内部的触发器的时钟端;判定为是时,执行步骤s331;否则,执行步骤s332;s331,判定时钟从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口时执行步骤s3311,判定时钟从前述时钟源连接到一个子模块内部的触发器的时钟端时执行步骤s3312;s3311,将此段时钟配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将前述模拟ip端口或者芯片输出端口配置为此段时钟树的终点,执行步骤s340;s3312,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到内部的触发器配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块内部的触发器配置为此段时钟树的终点,执行步骤s340;s332,判断时钟是否从时钟源穿入一个子模块并从该子模块穿出,判定为是时,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起

点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到该子模块的输出端配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块的输出端配置为此段时钟树的终点;以及,将该子模块的输出端配置为顶层下一级时钟源,返回到步骤s320进行下一级往后循迹;s340,结束循迹。

技术总结

本发明公开了芯片设计中基于综合网表提取时钟树的方法及应用,涉及集成电路设计技术领域。所述方法包括步骤:在逻辑综合步骤,获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息;根据获取的信息拼接全芯片的时钟结构,从时钟约束文件中获取时钟源;基于全芯片的时钟结构信息,从时钟源开始采用递归算法逐级往后循迹以形成全芯片时钟树网络;在循迹过程中,根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点;循迹结束,对顶层和子模块的时钟结构进行归类以形成时钟树实现指导文件。本发明缩短了时钟树验证周期,提高了时钟树实现工作的效率和正确性。作的效率和正确性。作的效率和正确性。

技术研发人员:吴帅帅 郑立青 杨睿 孙一

受保护的技术使用者:眸芯科技(上海)有限公司

技术研发日:2021.07.29

技术公布日:2021/10/29

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。