1.本发明涉及集成电路设计技术领域,尤其涉及芯片设计中提取时钟树的方法。

背景技术:

2.随着5g和人工智能技术的日渐成熟,发展的过程中对芯片功能的需求越来越多,芯片的规模也越来越大,但期望的芯片设计周期却越来越短,如何优化芯片设计流程以提高芯片设计过程中的设计效率、减少设计资源的浪费是当前主要研究方向之一。典型的芯片设计的主要流程一般包括以下几个步骤:规格制定,架构设计,时钟设计,代码编写,仿真验证,逻辑综合,形式验证,可测性设计,布局规划(或称布局),时钟树实现(或称时钟树综合),布线规划(或称布线),形式验证,寄生参数抽取,时序验证和物理版图验证。其中,在逻辑综合步骤中,是使用逻辑综合工具(比如synopsys的design compile)根据设定的工艺库、设计约束等信息将寄存器传输级硬件描述语言代码转换为针对特定工艺的逻辑门级网表。所述设计约束中包括了集成电路的时序约束。所述逻辑门级网表记录了各逻辑模块之间的连接关系。在布局规划步骤中,是根据时序、利用率、拥挤度、功耗等约束条件将各个逻辑模块进行物理布局。在时钟树实现步骤中,是设计出从原始时钟源到目标时序逻辑模块的路径,以满足设计约束中的时序约束。

3.在芯片的工作过程中,时钟是芯片同步工作系统的同步节拍。它向人体的神经系统一样,用来指挥保障芯片中各种功能模块的正常工作,因此芯片时钟树的正确性和稳定性在芯片的设计过程中尤为重要。

4.层次化设计是一种最常用的大规模芯片的设计方法,该方法将要设计的芯片被划分成了很多子模块,每个子模块单独设计,然后被顶层模块调用,由于对各个子模块单独进行时钟树平衡,全芯片只需要关注子模块接口处的寄存器的时钟延迟即可,这样能使设计的周期显著提高,并使时序问题局部化。基于这种设计方法,目前大规模芯片的物理实现采用自下而上的方式,把芯片整体切分成多个子模块分别实现然后由顶层集成在一起。对于时钟树的设计同样采用自下而上的方式,首先顶层和子模块各自实现时钟树设计,然后顶层拼接验证时钟的连通性。如果连通性不满足,则模块重新时钟树实现;如果逻辑上存在问题或者子模块存在时钟漏定义的问题,则反馈给芯片时钟设计者重新规划。

5.然而,一方面,由于时钟树设计处于芯片设计的前期,而时钟树分析和实现处于芯片设计的后期,在芯片设计流程中两者之间存在大量的其他设计分析工作,如果时钟树分析和实现阶段发现时钟树存在问题,往往需要修改设计前期的方案,导致两个阶段之间大量工作可能无效,增加了迭代时间,延长了芯片设计周期。另一方面,当前大规模芯片的时钟实现工作通常是采用自下而上的、子模块独立实现,随后再通过顶层拼接验证连通性和正确性的方式,该方式对子模块的约束文件的依赖性高,如果子模块约束文件中的时钟树存在问题,子模块本身往往无法发现,只能等到后期顶层拼接时才能发现上述问题,由于延误了解决上述问题的时间,增加了迭代风险。

技术实现要素:

6.本发明的目的在于:克服现有技术的不足,提供了一种芯片设计中基于综合网表提取时钟树的方法及应用。本发明在芯片设计流程的逻辑综合步骤进行时钟树分析,同时在确定全芯片时钟网络的连贯性的情况下把时钟结构切分到每个模块中,并形成后期时钟树实现步骤的时钟树实现指导文件,减少了时钟树验证的迭代过程从逻辑综合阶段到时钟树实现阶段之间的工作,提高了时钟树实现工作的效率和正确性。

7.为实现上述目标,本发明提供了如下技术方案:一种芯片设计中基于综合网表提取时钟树的方法,包括如下步骤:在逻辑综合步骤中,获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息;根据前述获取的信息拼接全芯片的时钟结构,从时钟约束文件中获取时钟定义的点作为初始时钟源;基于全芯片的时钟结构信息,从初始时钟源开始采用递归算法逐级往后循迹以形成全芯片时钟树网络;在所述循迹的过程中,根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点;循迹结束,对顶层时钟树和子模块时钟树的时钟结构信息进行归类以形成时钟树实现指导文件。

8.进一步,从初始时钟源开始采用递归算法逐级往后循迹的步骤如下,s310,将前述初始时钟源作为顶层时钟源;s320,获取顶层时钟源,判断时钟是否从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口或者连接到一个子模块内部的触发器的时钟端;判定为是时,执行步骤s331;否则,执行步骤s332;s331,判定时钟从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口时执行步骤s3311,判定时钟从前述时钟源连接到一个子模块内部的触发器的时钟端时执行步骤s3312;s3311,将此段时钟配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将前述模拟ip端口或者芯片输出端口配置为此段时钟树的终点,执行步骤s340;s3312,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到内部的触发器配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块内部的触发器配置为此段时钟树的终点,执行步骤s340;s332,判断时钟是否从时钟源穿入一个子模块并从该子模块穿出,判定为是时,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到该子模块的输出端配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块的输出端配置为此段时钟树的终点;以及,将该子模块的输出端配置为顶层下一级时钟源,返回到步骤s320进行下一级往后循迹;s340,结束循迹。

9.进一步,所述时钟树实现指导文件包括顶层时钟树实现指导文件和子模块时钟树

实现指导文件,所述顶层时钟树实现指导文件包括顶层时钟树的起点和终点信息,所述子模块时钟树实现指导文件包括各子模块时钟树的起点和终点信息。

10.进一步,获取时钟树实现人员的通信账户信息,根据前述通信账户信息将前述顶层时钟树实现指导文件和子模块时钟树实现指导文件发送给时钟树实现人员。

11.进一步,通过时序分析工具分析芯片顶层和芯片各子模块的逻辑综合网表和时钟约束文件信息后,拼接全芯片的时钟结构。

12.进一步,所述模块信息为子模块列表。

13.本发明还提供了一种芯片设计方法,至少包括时钟设计步骤、逻辑综合步骤、布局步骤、时钟树实现步骤和布线步骤;在逻辑综合步骤中,通过前述任一项所述的方法获取时钟树实现指导文件,作为后期的时钟树实现步骤的指导信息。

14.本发明还提供了一种芯片设计系统,至少包括时钟设计单元、逻辑综合单元、布局单元、时钟树实现单元和布线单元;所述逻辑综合单元包括时钟分析模块,所述时钟分析模块被配置为:通过前述任一项所述的方法获取时钟树实现指导文件,并将所述时钟树实现指导文件发送至前述时钟树实现单元。

15.本发明还提供了一种芯片设计中基于综合网表提取时钟树的装置,包括如下结构:信息采集模块,用于在逻辑综合步骤中,获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息;初始化模块,用于根据前述获取的信息拼接全芯片的时钟结构,从时钟约束文件中获取时钟定义的点作为初始时钟源;时钟树循迹模块,用于基于全芯片的时钟结构信息,从初始时钟源开始采用递归算法逐级往后循迹以形成全芯片时钟树网络;在所述循迹的过程中,根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点;结果处理模块,用于在循迹结束后,对顶层时钟树和子模块时钟树的时钟结构信息进行归类以形成时钟树实现指导文件。

16.进一步,所述时钟树循迹模块被配置为执行如下步骤:s310,将前述初始时钟源作为顶层时钟源;s320,获取顶层时钟源,判断时钟是否从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口或者连接到一个子模块内部的触发器的时钟端;判定为是时,执行步骤s331;否则,执行步骤s332;s331,判定时钟从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口时执行步骤s3311,判定时钟从前述时钟源连接到一个子模块内部的触发器的时钟端时执行步骤s3312;s3311,将此段时钟配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将前述模拟ip端口或者芯片输出端口配置为此段时钟树的终点,执行步骤s340;s3312,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块

的输入端到内部的触发器配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块内部的触发器配置为此段时钟树的终点,执行步骤s340;s332,判断时钟是否从时钟源穿入一个子模块并从该子模块穿出,判定为是时,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到该子模块的输出端配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块的输出端配置为此段时钟树的终点;以及,将该子模块的输出端配置为顶层下一级时钟源,返回到步骤s320进行下一级往后循迹;s340,结束循迹。

17.本发明由于采用以上技术方案,与现有技术相比,作为举例,具有以下的优点和积极效果:将时钟树分析步骤从芯片设计流程的布局规划步骤之后调整到芯片设计流程的逻辑综合步骤中进行,一方面,可以在逻辑综合步骤就验证时钟树的正确性,相比于在芯片设计流程后期的时钟树实现步骤中再验证时钟树的正确性,可以显著地减少时钟树验证的迭代过程从逻辑综合阶段到时钟树实现阶段之间的工作量,从而缩短时钟树验证周期,进而减少了设计资源的浪费和缩短了芯片设计周期。

18.另一方面,可以利用时序分析工具基于综合网表提取时钟树网络,时钟树的分析过程采用自上而下的方式,先确定全芯片时钟结构的连贯性,再根据模块划分信息把时钟结构切分到每个子模块,作为芯片设计后期时钟树实现阶段的指导文件,提高了时钟树实现阶段的工作效率和正确性。同时,由于芯片顶层和子模块可以在保证连通性的前提下进行时钟树设计,不再完全依赖模块的约束文件,同时使得子模块和顶层的设计无需迭代,缩短了芯片物理验证的迭代时间。

附图说明

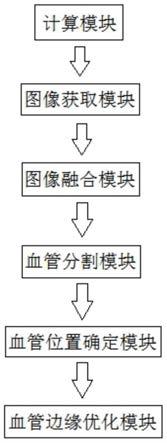

19.图1为本发明实施例提供的芯片设计中基于综合网表提取时钟树的方法的基本流程图。

20.图2为本发明实施例提供的芯片设计中基于综合网表提取时钟树的方法的详细流程图。

21.图3为本发明实施例提供的全芯片时钟树网络的结构示例图。

具体实施方式

22.以下结合附图和具体实施例对本发明公开的芯片设计中基于综合网表提取时钟树的方法及应用作进一步详细说明。应当注意的是,下述实施例中描述的技术特征或者技术特征的组合不应当被认为是孤立的,它们可以被相互组合从而达到更好的技术效果。在下述实施例的附图中,各附图所出现的相同标号代表相同的特征或者部件,可应用于不同实施例中。因此,一旦某一项在一个附图中被定义,则在随后的附图中不需要对其进行进一步讨论。

23.需说明的是,本说明书所附图中所绘示的结构、比例、大小等,均仅用以配合说明书所揭示的内容,以供熟悉此技术的人士了解与阅读,并非用以限定发明可实施的限定条

件,任何结构的修饰、比例关系的改变或大小的调整,在不影响发明所能产生的功效及所能达成的目的下,均应落在发明所揭示的技术内容所能涵盖的范围内。本发明的优选实施方式的范围包括另外的实现,其中可以不按所述的或讨论的顺序,包括根据所涉及的功能按基本同时的方式或按相反的顺序,来执行功能,这应被本发明的实施例所属技术领域的技术人员所理解。

24.对于相关领域普通技术人员已知的技术、方法和设备可能不作详细讨论,但在适当情况下,所述技术、方法和设备应当被视为说明书的一部分。在这里示出和讨论的所有示例中,任何具体值应被解释为仅仅是示例性的,而不是作为限制。因此,示例性实施例的其它示例可以具有不同的值。

实施例

25.参见图1所示,提供了一种芯片设计中基于综合网表提取时钟树的方法。

26.所述方法包括如下步骤:s100,获取综合网表,时钟约束文件和模块列表。

27.在芯片设计流程的逻辑综合步骤中,会产生逻辑综合网表,所述逻辑综合网表记录了芯片中各逻辑模块之间的连接关系。本实施例中,在逻辑综合步骤中,获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息。

28.所述芯片切分的模块信息优选的采用子模块列表。

29.s200,根据综合网表和时钟约束文件,拼接全芯片时钟结构,获取时钟源。

30.具体的,可以使用时序分析工具分别读入顶层和子模块的逻辑综合网表和时钟约束文件后,拼接全芯片的时钟结构。

31.同时,可以从时钟约束文件中获取时钟定义的点作为初始时钟源。

32.s300,从时钟源开始采用递归算法逐级往后循迹;在所述循迹的过程中,根据时钟树循迹路径确定顶层和模块时钟树的起点和终点。

33.该步骤中,是基于全芯片的时钟结构信息,从初始时钟源开始采用递归算法逐级往后循迹,通过逐级循迹形成全芯片时钟树网络。在所述循迹的过程中,就可以根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点。

34.结合图2所示,在循迹的过程中,从顶层时钟源开始,顶层时钟树和各子模块时钟树的起点和终点的确定方式如下。

35.a)如果时钟从前述时钟源直接连接到模拟ip端口,或者时钟从前述时钟源直接连接到芯片输出端口,则把此段时钟配置为顶层时钟树。此时,将前述时钟源作为此段时钟树(该顶层时钟树)的起点,将前述模拟ip端口或者芯片输出端口作为此段时钟树的终点。

36.b)如果时钟从前述时钟源穿入到某个子模块,并最终连接到该子模块内部的触发器的时钟端,则把前述时钟源到该子模块的输入端这段时钟配置为顶层时钟树,将前述时钟源作为此段时钟树的起点,将该子模块的输入端为此段时钟树的终点。

37.同时,把该子模块的输入端到内部触发器这段时钟配置为子模块时钟树,该子模块的输入端为此段时钟树(该子模块时钟树)的起点——即此段时钟树的时钟源,模块内触发器为此段时钟树的终点。

38.c)如果时钟从前述时钟源穿过某个子模块——即时钟穿入该子模块并从该子模

块穿出,则把前述时钟源到该子模块的输入端配置为顶层时钟树,前述时钟源为此段时钟树的起点,该子模块的输入端为此段时钟树的终点。

39.同时,把该子模块的输入端到该子模块的输出端作为子模块时钟树,该子模块的输入端作为此段时钟树的起点,该子模块的输出端作为此段时钟树的终点。

40.然后,将该子模块的输出端作为顶层下一级时钟源(即顶层下一级时钟树的时钟起点),继续逐级循迹,直到时钟连接到触发器的时钟端或者模拟ip的端口或者芯片的输出端口为止,结束循迹。通过前述逐级循迹过程可以形成全芯片时钟树网络。

41.据此,本实施例中,从初始时钟源开始采用递归算法逐级往后循迹的步骤可以如下。

42.s310,将前述初始时钟源作为顶层时钟源。

43.s320,获取顶层时钟源,判断时钟是否从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口或者连接到一个子模块内部的触发器的时钟端。判定为是时,执行步骤s331;否则,执行步骤s332。

44.s331,判定时钟从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口时执行步骤s3311。判定时钟从前述时钟源连接到一个子模块内部的触发器的时钟端时执行步骤s3312。

45.s3311,将此段时钟配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将前述模拟ip端口或者芯片输出端口配置为此段时钟树的终点;执行步骤s340。

46.s3312,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到内部的触发器配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块内部的触发器配置为此段时钟树的终点;执行步骤s340。

47.s332,判断时钟是否从时钟源穿入一个子模块并从该子模块穿出;判定为是时,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到该子模块的输出端配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块的输出端配置为此段时钟树的终点。

48.以及,将该子模块的输出端配置为顶层下一级时钟源,返回到步骤s320进行下一级往后循迹,此时,前述顶层下一级时钟源即作为步骤s320中的顶层时钟源。

49.s340,结束循迹。

50.现结合图3来详细描述通过上述循迹过程形成一个全芯片时钟树网络的过程。

51.图3中,顶层c表示芯片的顶层部分,模块a和模块b属于芯片划分的子模块部分,模拟ip为芯片内部ip,所述模块a的内部设置有触发器m和触发器n。其中,端口a、e、f为芯片端口;端口b为模块a的端口;端口c、d为模块b的端口,端口g为模拟ip端口。

52.根据前述循迹规则,可知时钟路径a

→

b,a

→

c,a

→

g,a

→

e 为顶层时钟树;b

→

触发器m和触发器n为模块a时钟树;c

→

d为模块b时钟树。

53.s400,循迹结束,归类顶层和子模块的时钟结构,形成时钟树实现指导文件。

54.本实施例中,在循迹结束后,可以对顶层时钟树和子模块时钟树的时钟结构信息进行归类,以形成时钟树实现指导文件。

55.具体的,可以通过归类分别把顶层和子模块的所有时钟源和终点信息作为时钟树实现指导文件。此时,所述时钟树实现指导文件可以包括顶层时钟树实现指导文件和子模块时钟树实现指导文件。

56.所述顶层时钟树实现指导文件包括顶层时钟树的起点和终点信息。

57.所述子模块时钟树实现指导文件包括各子模块时钟树的起点和终点信息。

58.前述时钟树实现指导文件可以发送给后期时钟树实现工程师以作为芯片后期时钟树实现的指导文件。具体的,还可以获取时钟树实现人员(包括但不限于钟树实现工程师,还可以是其他相关人员)的通信账户信息,根据前述通信账户信息将前述顶层时钟树实现指导文件和子模块时钟树实现指导文件发送给时钟树实现人员。

59.本实施例提供的上述技术方案,将时钟树分析步骤从芯片设计流程后期的布局步骤之后调整到芯片设计流程中的逻辑综合步骤中,利用时序分析工具基于逻辑综合网表提取时钟信息形成时钟树网络,然后对时钟树进行归类以形成时钟树实现指导文件,以作为后期钟树实现步骤的指导信息。一方面,由于在逻辑综合步骤就分析验证了时钟树的正确性,相比常规的芯片设计流程中的在时钟树实现步骤分析验证时钟树的正确性,上述技术方案可以显著减少时钟树验证的迭代过程从逻辑综合到时钟树实现之间的工作,缩短了时钟树验证周期,减少了设计资源的浪费和缩短了芯片设计周期。另一方面,从逻辑综合网表中提取全芯片时钟树网络,时钟树的分析过程采用自上而下的方式,先确定全芯片时钟结构的连贯性,然后根据模块划分信息把时钟结构切分到每个子模块中,并形成时钟树实现指导文件,可以提高后期时钟树实现工作的效率和正确性。同时,芯片顶层和子模块可以在保证连通性的前提下进行时钟树设计,不再完全依赖约束文件,同时无需迭代,提高了时钟树设计的效率。

60.本发明的另一实施例,还提供了一种芯片设计方法。

61.所述芯片设计方法至少包括时钟设计步骤、逻辑综合步骤、布局步骤、时钟树实现步骤和布线步骤。优选的,所述芯片设计方法可以包括规格制定步骤,架构设计步骤,时钟设计步骤,代码编写步骤,仿真验证步骤,逻辑综合步骤,形式验证步骤,可测性设计步骤,布局步骤,时钟树实现步骤,布线步骤,形式验证步骤,寄生参数抽取步骤,时序验证步骤和物理版图验证步骤。

62.在前述逻辑综合步骤中,可以通过如下方法获取时钟树实现指导文件:获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息;根据前述获取的信息拼接全芯片的时钟结构,从时钟约束文件中获取时钟定义的点作为初始时钟源;基于全芯片的时钟结构信息,从初始时钟源开始采用递归算法逐级往后循迹以形成全芯片时钟树网络;在所述循迹的过程中,根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点;循迹结束,对顶层时钟树和子模块时钟树的时钟结构信息进行归类以形成时钟树实现指导文件。将前述时钟树实现指导文件作为后期的时钟树实现步骤的指导信息。

63.其它技术特征参考在前实施例,在此不再赘述。

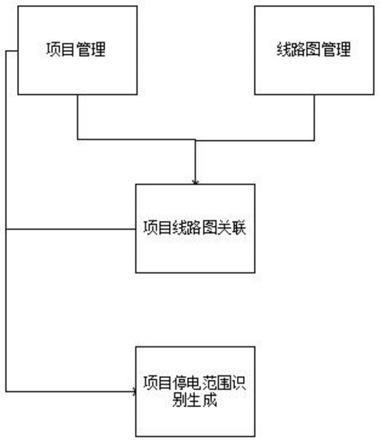

64.本发明的另一实施例,还提供了一种芯片设计系统。

65.所述芯片设计系统至少包括时钟设计单元、逻辑综合单元、布局单元、时钟树实现单元和布线单元。优选的,所述芯片设计方法可以包括规格制定单元,架构设计单元,时钟

设计单元,代码编写单元,仿真验证单元,逻辑综合单元,形式验证单元,可测性设计单元,布局单元,时钟树实现单元,布线单元,形式验证单元,寄生参数抽取单元,时序验证单元和物理版图验证单元。

66.其中,所述逻辑综合单元包括时钟分析模块。所述时钟分析模块被配置为:获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息;根据前述获取的信息拼接全芯片的时钟结构,从时钟约束文件中获取时钟定义的点作为初始时钟源;基于全芯片的时钟结构信息,从初始时钟源开始采用递归算法逐级往后循迹以形成全芯片时钟树网络;在所述循迹的过程中,根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点;循迹结束,对顶层时钟树和子模块时钟树的时钟结构信息进行归类以形成时钟树实现指导文件;以及,将所述时钟树实现指导文件发送至前述时钟树实现单元。

67.其它技术特征参考在前实施例,所述逻辑综合单元可以包括相应的处理模块以进行对应的信息处理,在此不再赘述。

68.本发明的另一实施例,还提供了一种芯片设计中基于综合网表提取时钟树的装置。

69.所述装置包括信息采集模块,初始化模块,时钟树循迹模块和结果处理模块。

70.所述信息采集模块,用于在逻辑综合步骤中,获取芯片顶层和子模块的逻辑综合网表信息,以及芯片切分的模块信息和时钟约束文件信息。

71.所述初始化模块,用于根据前述获取的信息拼接全芯片的时钟结构,从时钟约束文件中获取时钟定义的点作为初始时钟源。

72.所述时钟树循迹模块,用于基于全芯片的时钟结构信息,从初始时钟源开始采用递归算法逐级往后循迹以形成全芯片时钟树网络;在所述循迹的过程中,根据时钟树循迹路径确定顶层时钟树和子模块时钟树的起点和终点。

73.所述结果处理模块,用于在循迹结束后,对顶层时钟树和子模块时钟树的时钟结构信息进行归类以形成时钟树实现指导文件。

74.本实施例中,所述时钟树循迹模块被配置为执行如下步骤:s310,将前述初始时钟源作为顶层时钟源。

75.s320,获取顶层时钟源,判断时钟是否从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口或者连接到一个子模块内部的触发器的时钟端;判定为是时,执行步骤s331;否则,执行步骤s332。

76.s331,判定时钟从前述时钟源直接连接到模拟ip端口或者直接连接到芯片输出端口时执行步骤s3311,判定时钟从前述时钟源连接到一个子模块内部的触发器的时钟端时执行步骤s3312。

77.s3311,将此段时钟配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将前述模拟ip端口或者芯片输出端口配置为此段时钟树的终点,执行步骤s340。

78.s3312,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到内部的触发器配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块内部的触发器配置为此段时钟树的终点,执行步骤s340。

79.s332,判断时钟是否从时钟源穿入一个子模块并从该子模块穿出,判定为是时,将前述时钟源到该子模块的输入端配置为顶层时钟树,并将前述时钟源配置为此段时钟树的起点,将该子模块的输入端配置为此段时钟树的终点;以及,将该子模块的输入端到该子模块的输出端配置为子模块时钟树,并将该子模块的输入端配置为此段时钟树的起点,将该子模块的输出端配置为此段时钟树的终点;以及,将该子模块的输出端配置为顶层下一级时钟源,返回到步骤s320进行下一级往后循迹。

80.s340,结束循迹。

81.其它技术特征参见在前实施例的描述,在此不再赘述。

82.在上面的描述中,本发明的公开内容并不旨在将其自身限于这些方面。而是,在本公开内容的目标保护范围内,各组件可以以任意数目选择性地且操作性地进行合并。另外,像“包括”、“囊括”以及“具有”的术语应当默认被解释为包括性的或开放性的,而不是排他性的或封闭性,除非其被明确限定为相反的含义。所有技术、科技或其他方面的术语都符合本领域技术人员所理解的含义,除非其被限定为相反的含义。在词典里找到的公共术语应当在相关技术文档的背景下不被太理想化或太不实际地解释,除非本公开内容明确将其限定成那样。本发明领域的普通技术人员根据上述揭示内容做的任何变更、修饰,均属于权利要求书的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。