1.本发明涉及具备电路模块和安装有电路模块的主基板的半导体装置。

背景技术:

2.例如,在由多个元件构成的电路模块等(包含系统lsi、微型计算机的系统电路模块)中,存在需要多种电力供给的情况。因此,在安装有电路模块的电路基板(主基板)等中常常形成有从主电源生成多种类型的电力的辅助电源电路。在日本特开2009

‑

38950号公报中,示例出了作为这种辅助电源电路的微电源模块(102)。需要说明的是,背景技术中的括号内的附图标记是参考文献的附图标记。该微电源模块(102)构成为具有内置有开关元件(6、7)的电源ic(101)、第一噪声吸收用电容器(4)以及第二噪声吸收用电容器(5)。在该微电源模块(102)中,第一噪声吸收用电容器(4)、电源ic(101)和第二噪声吸收用电容器(5)沿着部件的配置面排列配置(参照该公报的图1等)。

3.现有技术文献

4.专利文献

5.专利文献1:日本特开2009

‑

38950号公报

技术实现要素:

6.发明要解决的问题

7.由于该微电源模块(102)沿着部件的配置面排列配置有电源ic(102)和电容器(4、5),因此沿着部件的配置面的面积具有变大的倾向。因此,在安装有电路模块的电路基板(主基板)等上安装该微电源模块(102)的情况下,该主基板的面积具有变大的可能性。即,妨碍主基板和具有主基板的半导体装置的小型化,从而具有导致成本增加的可能性。

8.鉴于上述背景,期望提供更小型地形成具备电源电路的半导体装置的技术,该电源电路向形成在搭载有电路模块的主基板的电路供给电力。

9.用于解决问题的手段

10.鉴于上述的半导体装置,作为一个实施方式,具备电路模块以及安装有所述电路模块的主基板,所述电路模块包括模块基板和安装于所述模块基板的电路元件,其中,所述半导体装置包括电源电路,至少向在所述模块基板上形成的电路供给电力,所述电源电路具有输出预先规定的输出电压的电压生成电路、第一电容器以及比所述第一电容器容量大的第二电容器,所述电压生成电路和所述第一电容器安装于所述模块基板,所述第二电容器安装于所述主基板。

11.由于电容器通常会根据容量增加体积,与第一电容器相比,第二电容器的体积更大。根据本结构,由于体积大的第二电容器不安装于模块基板,从而能够抑制电路模块的尺寸。例如,安装于主基板的电路模块的模块基板与主基板相比,具有部件安装的自由度变低的倾向。然而,通过使体积大的第二电容器不安装于模块基板,能够更有效地进行布线。因此,能够使电路模块小型化,从而能够使具备电路模块的半导体装置小型地形成。需要说明

的是,由于第二电容器在安装有电路模块的主基板上安装,从而也能够避免第二电容器与电压生成电路之间的布线距离显著变长。这样,根据本结构,能够更小型地形成具备向形成于搭载有电路模块的主基板的电路供给电力的电源电路的半导体装置。

12.半导体装置的进一步特征和优点,通过以下的记载对参照附图说明的实施方式进行了明确。

附图说明

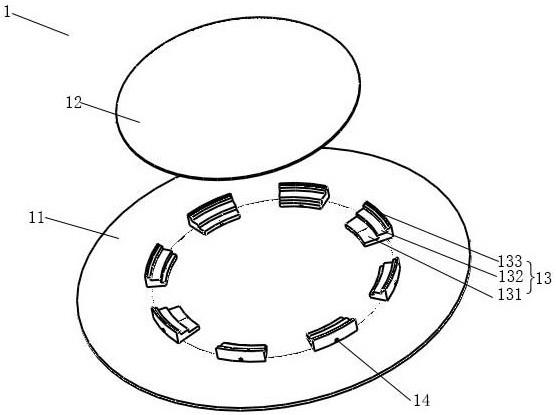

13.图1是半导体装置的示意性分解立体图

14.图2是电路模块的部件配置图

15.图3是电源电路的结构的示意性电路框图

16.图4是表示半导体装置的一例的示意性剖视图

17.图5是示意性地表示电源生成电路和第二电容器之间的布线路径的一例的图

18.图6是表示半导体装置的另一例的示意性剖视图

19.图7是表示半导体装置的比较例的示意性剖视图

具体实施方式

20.以下,基于附图说明半导体装置的实施方式。如图1的示意性分解立体图所示,半导体装置10构成为包括主基板5和电路模块1。在主基板5的第一面(主基板第一面5a)上至少安装有电路模块1。在此,电路模块1包括系统lsi(处理器)2、与系统lsi2协作的存储器3、电源电路9的一部分(第一电容器6、电压生成电路8(电源ic81)))以及将这些安装于模块基板第一面4a的模块基板4。

21.在本实施方式中,如图2的部件配置图所示,在模块基板4上安装有作为系统lsi2的片上系统(system on a chip,soc)、作为存储器3的两个同步动态随机存取存储器(synchronous dynamic random access memory,sdram)、作为电源电路9的一部分的电源ic81(pic:power ic)、作为同一电源电路9的一部分的两个电感器82以及作为同一电源电路9的一部分的两个第一电容器6。如后述,在本实施方式中,由电源ic81和电感器82形成电压生成电路8。在与电路模块1的模块基板第一面4a相反的一侧的模块基板第二面4b(与主基板第一面5a相向的相向面)上规则地配置有与主基板5连接的半球状的多个连接端子t(参照图4、图6等)。即,电路模块1构成为包括球栅阵列(ball grid array,bga)型的连接端子t,并安装于主基板第一面5a。

22.如上所述,在此,作为系统lsi2示出了soc。然而,系统lsi2也可以为封装系统(system in a package,sip)。另外,在soc中也包括半定制lsi的专用集成电路(application specific integrated circuit,asic)和通用lsi的专用标准处理器(application specific standard processor,assp)等。另外,asic不限于门阵列、基于单元的ic(标准单元),也包括现场可编程门阵列(field programmable gate array,fpga)、可编程逻辑阵列(programmable logic array,pla)等的可编程逻辑设备(programmable logic device,pld)。

23.另外,sdram例如优选为ddr3(double data rate 3,第三代双倍数据速率)sdram、ddr4(double data rate 4,第四代双倍数据速率)sdram等。在此,作为存储器3示出了

sdram,但不妨碍其为闪速存储器(flash memory)、静态随机存取存储器(static ram,sram)等其他结构的存储器。

24.如上所述,存储器3与系统lsi2协作。因此,存储器3的信号端子(地址端子、数据端子、控制端子等)在模块基板4上仅与系统lsi2连接。另外,在本实施方式中,用于驱动存储器3的电力以及在系统lsi2中与存储器3连接的输入输出部(端子的输入输出焊盘等)的驱动电力也由安装于模块基板4的电压生成电路8生成。

25.图3示出了包含电压生成电路8的电源电路9的示意性电路框图。电源电路9至少向在模块基板4上形成的电路供给电力。需要说明的是,电源电路9能够向在模块基板4和在主基板5上形成的电路供给电力。在此,在主基板5上形成的电路包括形成于电路模块1中的电路、形成于主基板5上的除电路模块1以外的位置的电路以及形成于电路模块1和主基板5上的电路。如图3所示,电源电路9为具有包括电源ic81和电感器82的电压生成电路8、第一电容器6和第二电容器7的开关调节器(开关电源电路)。在此,“电力”包括“电压”和“电流”,电源电路9(电压生成电路8)在预先规定的最大输出电流的范围内,输出预先规定的恒定的输出电压vout。

26.电源ic81形成内置有开关元件的开关电源电路的一部分,与电感器82协作,并根据输入电压vcc输出预先规定的输出电压vout。开关元件基于来自开关控制电路(未图示)的开关控制信号而被控制。开关控制电路基于输入电压vcc和目标输出电压(理想的输出电压vout)设定开关控制信号的占空比。优选为,将输出电压vout反馈至开关控制电路,并且开关元件由开关控制电路进行反馈控制。

27.第一电容器6为用于吸收因电源ic81的开关而产生的高频(例如相当于开关频率中高次谐波分量的频率)的输入电压vcc的变动的电容器(旁路电容器)。例如,第一电容器6的容量为0.01[μf]~0.1[μf]左右,在大多数情况下使用陶瓷电容器。第二电容器7为用于使因电源ic81的开关而产生的输出电压vout的低频(例如开关频率)纹波分量平滑化的电容器(平滑电容器)。第二电容器7的容量为10[μf]以上,第二电容器7为比第一电容器6容量大的电容器。第二电容器7使用电解电容器、陶瓷电容器等。通常来说,若电容器为相同物性,则容量越大体积越大,因此第二电容器7比第一电容器6大型。

[0028]

在本实施方式中,如图1和图2所示,电压生成电路8和第一电容器6安装于模块基板4,如图1所示,第二电容器7安装于主基板5。即,通过将容量大且体积尺寸也大的第二电容器7安装于主基板5而非模块基板4,得以抑制模块基板4大型化,从而也抑制电路模块1大型化。模块基板第一面4a的电压生成电路8和第二电容器7经由形成于模块基板4和主基板5的未图示的通孔电连接。

[0029]

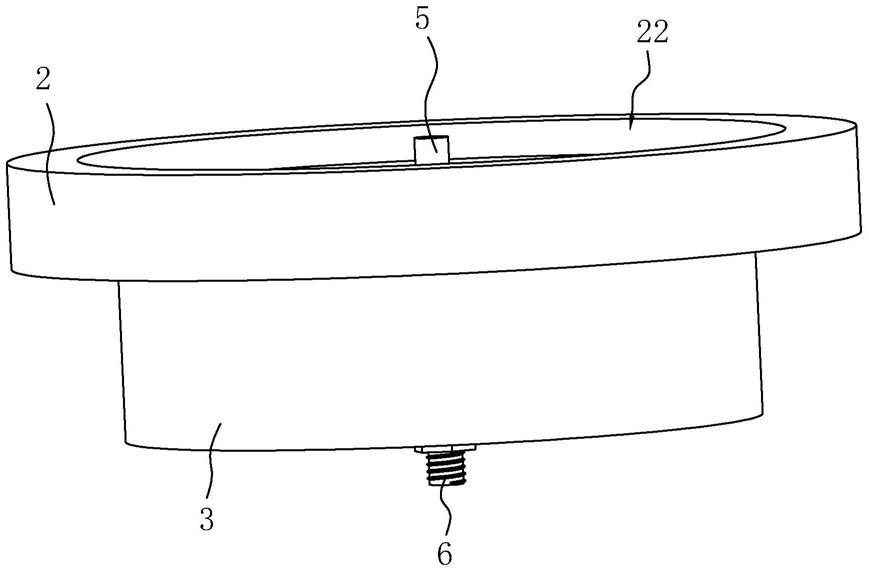

更优选为,如图4的示意性剖视图所示,可以将在模块基板4上安装有电压生成电路8和第一电容器6的电路模块1安装于主基板第一面5a,并将第二电容器7安装于主基板第二面5b。而且,如图4所示,若在从与主基板第一面5a正交的方向z观察的俯视(z方向观察)下将电路模块1和第二电容器7重叠,则能够抑制从z方向观察时电源电路9所占的面积(安装面积s)。

[0030]

而且,在图4所示的实施方式中,从z方向观察时,电压生成电路8和第二电容器7重叠。因此,能够进一步抑制从z方向观察时电源电路9所占的面积(安装面积s),并且能够在与主基板5和模块基板4正交的方向z上,以短距离连接电压生成电路8和第二电容器7。在图

4中,电源ic81也为bga型,并在与模块基板第一面4a相向的面上具有多个半球状的连接端子b,并在与主基板5和模块基板4正交的方向z上经由电源ic81的连接端子b、电路模块1的连接端子t将电压生成电路8和第二电容器7连接。

[0031]

图5示意性地表示电压生成电路8和第二电容器7之间的布线路径的一例。电压生成电路8和第一电容器6例如通过模块基板第一面4a的第一布线图案w4a连接。在配置于模块基板第二面4b的连接端子t内的与主基板第一面5a的第二布线图案w5a连接的一部分连接端子t和第一布线图案w4a由将模块基板第一面4a和模块基板第二面4b连接的第一通孔v4连接。需要说明的是,该连接端子t与模块基板第二面4b的连接端子用图案w4b连接。第一布线图案w4a和连接端子用图案w4b通过第一通孔v4连接,由此将该连接端子t和第一布线图案w4a连接。在主基板第二面5b上,连接第二电容器7的第三布线图案w5b和第二布线图案w5a通过将主基板第一面5a和主基板第二面5b连接的第二通孔v5连接。

[0032]

这样,即使第二电容器7安装于主基板5,也能够在与主基板5的基板面正交的方向z上短距离地设置布线,而无需在沿着主基板5的基板面的方向上迂回布线、或在主基板5的内层布线层上设置布线。即,即使第二电容器7安装于主基板5,也能够在不增加主基板5的布线层的情况下,将第二电容器7与电压生成电路8连接。

[0033]

在本实施方式中,示出了电源电路9生成一种电力的实施方式,但电源电路9也可以生成多种电力。需要说明的是,在电源电路9生成多种电力的情况下,在不同的电力之间,输出电压vout也可以为相同的电压。即使电力的供给对象的额定电压相同,在总消耗电力多的情况下,考虑到电源电路9的负荷,也存在期望供给不同类型的电力的情况。另外,即使电力的供给对象的额定电压相同,为了抑制因某个供给对象的动作而产生的电源噪声对其他供给对象产生影响,也存在优选各自的供给对象以不同的电力进行动作的情况。

[0034]

另外,在图4中,示出了电源ic81具有多个半球状的连接端子b的球栅阵列(ball grid array,bga)型的方式。然而,在电源ic81的主体(封装)与模块基板第一面4a之间具有连接端子的实施方式并不限于bga型。例如,电源ic81也可以是在ic主体的下部(与模块基板第一面4a相向的面)具有将电源ic81的连接端子与模块基板4连接的连接部的qfj(quad flat j

‑

leaded package,四侧j形引脚扁平封装)、soj(small outline j

‑

leaded package,j形引脚小外型封装)。另外,如图6所示,电源ic81也可以是在ic主体的侧面而不在ic主体的下部具有l字型的连接端子ld的sop(small outline l

‑

leaded package,l形引脚小外型封装)、qfp(quad flat gull wing leaded package,四侧鸥翼形引脚扁平封装)。

[0035]

图7示出了表示半导体装置10的比较例的示意性剖视图。如图1、图4、图6所示,在本实施方式的半导体装置10中,电压生成电路8和第一电容器6安装于模块基板4,第二电容器7安装于主基板5。然而,在图7所示的比较例的半导体装置10中,电源电路9的全部均安装于模块基板4。具体来说,在比较例的半导体装置10中,电压生成电路8、第一电容器6和第二电容器7安装于模块基板4。因此,从z方向观察时,电源电路9所占的面积(安装面积s)变大,存在模块基板4大型化,从而电路模块1大型化的可能性。从以具备bga型的电源ic81的电路模块1作为示例的图4和图7之间的比较中可以明白,与图4所示的本实施方式的电路模块1中的电源电路9的安装面积s(第一安装面积s1)相比,比较例的电路模块1中的电源电路9的安装面积s(第二安装面积s2)较大。

[0036]

这样,根据参照图1、图4、图6等说明的本实施方式,由于体积大的第二电容器7不

安装于模块基板4,从而能够抑制电路模块1的尺寸。而且,由于能够使电路模块1小型化,从而具备电路模块1的半导体装置10也能够小型地形成。即,根据本实施方式,对于具备向形成于搭载电路模块1的主基板5的电路供给电力的电源电路9的半导体装置10,能够使其更小型地形成。

[0037]

(其他实施方式)

[0038]

以下,说明其他实施方式。需要说明的是,以下说明的各实施方式的结构不限于各自单独应用的情况,只要在不产生矛盾的情况下,也能够与其他的实施方式的结构组合应用。

[0039]

(1)在上述中,示出了电路模块1包括模块基板4、电压生成电路8和被供给由电压生成电路8生成的电力的系统lsi2(处理器),并且系统lsi2安装于模块基板第一面4a的多芯片模块(系统多芯片模块)的实施方式。然而,电路模块1不限于该方式,也可以为具备模块基板4和电压生成电路8的多芯片模块(电源多芯片模块)。即,也可以为由电压生成电路8生成的电力的供给对象不搭载于同一模块基板4的多芯片模块。

[0040]

在电路模块1为这种电源多芯片模块的情况下,优选具有多个电压生成电路8,并能够输出多种电力。能够构成集成有对主基板5供给多种电力的电路的电路模块1。需要说明的是,如上所述,“电力”包含“电压”和“电流”,电源电路9(电压生成电路8)在预先规定的最大输出电流的范围内,输出预先规定的恒定的输出电压vout。并且,多种电力也可以包括输出电压vout相同的电力。

[0041]

需要说明的是,参照图1、图4、图6等,如上所述,在电路模块1为具备模块基板4、电压生成电路8以及被供给由电压生成电路8生成的电力的系统lsi2的系统多芯片模块的情况下,作为电源电路9的电力的供给对象的电路(在主基板5上形成的电路)优选限定为在电路模块1中形成的电路。即,能够在电路模块1中包括专用的电源电路9。但是,在本实施方式中,仅电源电路9中的第二电容器7被排除在电路模块1之外。由此,能够在电路模块1中包括作为专用的电源电路9的核心的电路(电压生成电路8),并使电路模块1小型化。

[0042]

另外,在许多情况下,传输电力的布线设置于基板的内层布线层,但通过在电路模块1中设置专用的电源电路9,不需要在主基板5上设置这样的内层电力布线。因此,也能够简化主基板5的结构。需要说明的是,尽管第二电容器7需要通过主基板5连接至电压生成电路8,但通孔和第二电容器7的安装焊盘足以用作该连接的布线。因此,即使在将第二电容器7安装于主基板5的情况下,在主基板5上也不需要进行用于传输形成于电路模块1的电压生成电路8的输出电压vout的内层电力布线。

[0043]

但是,当然,在电路模块1为具备模块基板4、电压生成电路8以及被供给由电压生成电路8生成的电力的系统lsi2的系统多芯片模块的情况下,作为由电源电路9产生的电力的供给对象的电路(在主基板5上形成的电路)不限于在电路模块1中形成的电路,可以是在电路模块1和主基板5上形成的电路。即,具备电压生成电路8的电路模块1(系统多芯片模块)也可以向在该电路模块1中形成的电路和不在该电路模块1中形成而是形成于主基板5的电路双方供给电力。

[0044]

另一方面,在电路模块1为具有模块基板4和电压生成电路8,而不具有被供给由电压生成电路8生成的电力的系统lsi2的电源多芯片模块的情况下,作为由电源电路9产生的电力的供给对象的电路(在主基板5上形成的电路)为在电路模块1(电源多芯片模块)以外

形成于主基板5上的电路。例如,搭载于主基板5的系统电路(由系统多芯片模块、单一的系统lsi构成)存在根据产品而变更的情况。并且,系统电路通常需要多种电力,但例如电力的种类、每种电力的消耗电流等的电源规格根据系统电路的不同而不同。因此,优选根据系统电路而将适当的电源多芯片模块安装于主基板5。电源多芯片模块能够根据产品而提供灵活的电源。

[0045]

当然,不具备电压生成电路8的系统多芯片模块和电源多芯片模块(电路模块1)也可以安装于主基板5。另外,多个电路模块1也可以安装于主基板5,例如,电源多芯片模块(电路模块1)也可以多个地安装。另外,也可以是具备电压生成电路8的系统多芯片模块(电路模块1)和电源多芯片模块(电路模块1)安装于主基板5。

[0046]

(2)在上述中,如图1、图4、图6等所示,示出了第二电容器7安装于主基板第二面5b的方式。然而,不妨碍第二电容器7安装于主基板第一面5a。在这种情况下,从z方向观察时电路模块1和第二电容器7不重叠。然而,在主基板5的安装密度低,部件的配置、布线有富余的情况下,第二电容器7也可以安装于主基板第一面5a。在这种情况下,从z方向观察时,电压生成电路8和第二电容器7之间的布线距离与电路模块1和第二电容器7重叠的方式相比更长。然而,第二电容器7平滑化的电压以低于第一电容器6的频率变化。因此,较长的布线距离对第二电容器7的影响小于对第一电容器6的影响。

[0047]

在第二电容器7安装于主基板第一面5a的情况下,在包括主基板5的情况下,从z方向观察时电源电路9所占的面积(安装面积s)与图7所示的比较例相同。然而,与比较例不同的是,由于第二电容器7未安装于模块基板4,从而能够抑制模块基板4大型化。因此,在主基板5的安装密度低,从而部件的配置、布线有富余的情况下,即使第二电容器7安装于主基板第一面5a,也能够抑制半导体装置10大型化。

[0048]

另外,对于比第一电容器6容量大的第二电容器7,常常使用电解电容器。存在具有贯通主基板5的引线的分立部件、例如连接器安装于主基板第一面5a的情况。在这种情况下,对主基板第二面5b进行的部件的安装大多不是通过回流焊而是通过流动熔焊进行。并且,表面安装型的电场电容器也通常不能通过流动熔焊进行安装。另外,大多大容量产品不用作表面安装型的电场电容器。然而,将分立部件的电解电容器配置于主基板第一面5a时,能够在主基板第二面5b侧通过流动焊接安装引线端子。也不需要考虑上述那样的容量的制限。因此,不妨碍第二电容器7安装于主基板第一面5a。在任何情况下,均能够促进未安装有第二电容器7的电路模块1的小型化。

[0049]

(3)在上述中,作为电压生成电路8,示出了所谓的斩波器型的开关电源电路,但电压生成电路8并不限于本方式。例如,也可以将使用变压器的绝缘侧的电压转换电路(dc

‑

dc转换器)作为电压生成电路8。

[0050]

(实施方式的概要)

[0051]

以下,简单地说明在上述说明的半导体装置(10)的概要。

[0052]

半导体装置(10)具备电路模块(1)以及安装有所述电路模块(1)的主基板(5),所述电路模块(1)包括模块基板(4)和安装于所述模块基板(4)的电路元件(2、3、6、81),作为一个实施方式,其中,包括至少向在所述模块基板(4)上形成的电路供给电力的电源电路(9),所述电源电路(9)具有输出预先规定的输出电压(vout)的电压生成电路(8)、第一电容器(6)以及比所述第一电容器(6)容量大的第二电容器(7),所述电压生成电路(8)和所述第

一电容器(6)安装于所述模块基板(4),所述第二电容器(7)安装于所述主基板(5)。

[0053]

由于电容器通常会根据容量增加体积,与第一电容器(6)相比,第二电容器(7)的体积更大。根据本结构,由于体积大的第二电容器(7)不安装于模块基板(4),从而能够抑制电路模块(1)的尺寸。例如,安装于主基板(5)的电路模块(1)的模块基板(4)与主基板(5)相比,具有部件安装的自由度变低的倾向。然而,通过使体积大的第二电容器(7)不安装于模块基板(4),能够更有效地布线。因此,能够使电路模块(1)小型化,从而能够使具备电路模块(1)的半导体装置(10)小型地形成。需要说明的是,由于第二电容器(7)在安装有电路模块(1)的主基板(5)上安装,从而也能够避免第二电容器(7)与电压生成电路(8)之间的布线距离显著变长。这样,根据本结构,能够更小型地形成具备向形成于搭载有电路模块(1)的主基板(5)的电路供给电力的电源电路(9)的半导体装置(10)。

[0054]

在此,优选为,所述电路模块(1)安装于所述主基板(5)的第一面(5a),所述第二电容器(7)安装于所述主基板(5)的与所述第一面(5a)相反的一侧的面即第二面(5b),在从与所述主基板(5)的所述第一面(5a)正交的方向(z)观察的俯视下,所述电路模块(1)和所述第二电容器(7)重叠。

[0055]

在俯视下,电路模块1和第二电容器7重叠时,能够抑制在半导体装置(10)中,在俯视下电源电路9所占的面积(安装面积(s))。因此,能够小型地形成半导体装置(10)。

[0056]

在所述电路模块(1)安装于所述主基板(5)的第一面(5a),所述第二电容器(7)安装于与所述主基板(5)的所述第一面(5a)相反的一侧的面即第二面(5b)的情况下,优选为,所述电压生成电路(8)和所述第一电容器(6)安装于所述模块基板(4)的一侧的面即模块基板第一面(4a),多个连接端子(t)配置于与所述模块基板第一面(4a)相反的一侧的面即模块基板第二面(4b),在所述俯视下,所述电压生成电路(8)和所述第二电容器(7)重叠。

[0057]

根据该结构,能够将电压生成电路(8)和第二电容器(7)沿着与主基板(5)的第一面(5a)正交的方向(z)以短距离连接。即,即使电压生成电路(8)和第二电容器(7)安装于不同的基板,也能够在与模块基板(4)和主基板(5)的基板面正交的方向(z)上以短距离布线,而不会在沿着模块基板(4)和主基板(5)的基板面的方向上迂回布线从而使布线距离变长。

[0058]

在此,优选为,通过所述模块基板第一面(4a)的第一布线图案(w4a),将所述电压生成电路(8)和所述第一电容器(6)连接,并通过连接所述模块基板第一面(4a)和所述模块基板第二面(4b)的第一通孔(v4),将配置于所述模块基板第二面(4b)的所述连接端子(t)内的与所述主基板(5)的所述第一面(5a)的第二布线图案(w5a)连接的一部分所述连接端子(t)和所述第一布线图案(w4a)连接,通过连接所述主基板(5)的所述第一面(5a)和所述第二面(5b)的第二通孔(v5),将在所述第二面(5b)上连接所述第二电容器(7)的第三布线图案(w5b)和所述第二布线图案(w5a)连接。

[0059]

根据该结构,即使第二电容器(7)安装于主基板(5),也能够在与主基板(5)的基板面正交的方向(z)上以短距离设置布线,而不会在沿着主基板(5)的基板面的方向上迂回布线、或者在主基板(5)的内层布线层上设置布线。即,即使第二电容器(7)安装于主基板(5),也能够在不增加主基板(5)的布线层的情况下,将第二电容器(7)与电源生成电路(8)连接。

[0060]

在此,优选为,所述电路模块(1)为包括所述模块基板(4)和被供给由所述电压生成电路(8)生成的电力的处理器(2)的多芯片模块。

[0061]

根据该结构,能够在模块基板(4)中以短的布线距离向处理器(2)供给电力。另外,

通过使体积大的第二电容器(7)未安装于模块基板(4),能够使多芯片模块小型化,并且能够高效地进行处理器(2)的布线。

[0062]

另外,优选为,所述电压生成电路(8)和所述第一电容器(6)安装于所述模块基板(4)的一侧的面即模块基板第一面(4a),多个连接端子(t)配置于所述模块基板第二面(4b),在所述电路模块(1)为具有所述模块基板(4)和被供给由所述电压生成电路(8)生成的电力的处理器(2)的多芯片模块的情况下,在所述模块基板第一面(4a)上还安装有所述处理器(2)。

[0063]

根据该结构,能够提供在模块基板第一面(4a)具备处理器(2)、电压生成电路(8)和第一电容器(6)并在模块基板(4)中能够将电力供给至处理器(2)的高效的多芯片模块。由于在该多芯片模块中不包含体积大的第二电容器(7),从而能够使多芯片模块小型化,并且高效地进行处理器(2)的布线。

[0064]

在此,优选为,所述电压生成电路(8)为开关电源电路,所述第一电容器(6)为所述电压生成电路(8)的旁路电容器,所述第二电容器(8)为使所述电压生成电路(8)的所述输出电压(vout)平滑化的平滑电容器。

[0065]

开关电源电路例如与线性调节器等相比,电压的转换效率较好且发热较小,从而能够构成优异的电压生成电路(8)。另一方面,在电压生成中,由于伴随着开关元件的开关动作,容易在输入侧的电压(vcc)上叠加开关频率的高次谐波分量的噪声,从而在输出电压(vout)中容易产生开关频率的纹波。因此,在开关电源电路中,在输入侧和输出侧连接电容器,从而进行噪声的除去、纹波的平滑化。在输入侧,除去开关频率的高次谐波分量的噪声的旁路电容器优选配置在比平滑化输出电压(vout)的平滑电容器更靠近电压生成电路(8)的位置。另外,与平滑电容器相比,与高频相对应的旁路电容器比平滑电容器容量小且体积也小。因此,旁路电容器优选为与电压生成电路(8)一起安装于模块基板(4)的第一电容器(6)。另一方面,与旁路电容器相比,与低频相对应的平滑电容器比旁路电容器容量大且体积也大。因此,平滑电容器优选为与电路模块(1)分开安装于的主基板(5)的第二电容器(7)。

[0066]

附图标记说明:

[0067]

1:电路模块

[0068]

2:系统lsi(处理器、安装于模块基板的电路元件)

[0069]

3:存储器(安装于模块基板的电路元件)

[0070]

4:模块基板

[0071]

4a:模块基板第一面

[0072]

4b:模块基板第二面

[0073]

5:主基板

[0074]

5a:主基板第一面(主基板的第一面)

[0075]

5b:主基板第二面(主基板的第二面)

[0076]

6:第一电容器(安装于模块基板的电路元件)

[0077]

7:第二电容器

[0078]

8:电压生成电路

[0079]

9:电源电路

[0080]

10:半导体装置

[0081]

81:电源ic(电压生成电路、安装于模块基板的电路元件)

[0082]

t:连接端子

[0083]

v4:第一通孔

[0084]

v5:第二通孔

[0085]

vout:输出电压

[0086]

w4a:第一布线图案

[0087]

w5a:第二布线图案

[0088]

w5b:第三布线图案

[0089]

z:与主基板的第一面正交的方向

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。