1.本发明涉及数字预失真技术领域,具体涉及一种基于记忆多项式的功放模型及其硬件实现方法。

背景技术:

2.研究数字预失真技术的关键在于对功放行为模型的拟合,只有通过准确的数学模型才能使得硬件电路描述准确的功放行为,使得数字预失真技术在实际应用中,能够获得最佳的预失真效果。

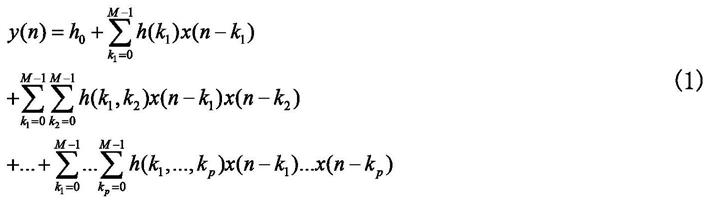

3.目前的功率放大器的模型包括volterra级数模型、记忆多项式模型(memory polynomial,mp)、广义记忆多项式模型(generalized memory polynomial)等。其中,volterra级数是在仿真软件中使用得最多的数学模型,因为它包含了许多交叉项与次方项,其中交叉项的定义是,输入信号的当前时刻和先前的某个时刻相乘项,在描述非线性度更大的系统时经常需要交叉项的拟合。volterra级数的表达式为

[0004][0005]

其中y(n)与x(n)分别为通信系统的输出信号与输入信号,m为模型的记忆深度,p为非线性阶数,k

p

为对应的记忆项系数。volterra级数对于实际功放的拟合度非常高,但由于其超高的复杂度,使得它并不会被应用在硬件实现上。

[0006]

mp模型是volterra级数的简化版,它只取volterra级数的基函数的核心项,同时在算法结构上比volterra级数模型简单得多,在硬件实现上复杂度大大降低了,mp的复基带模型如下

[0007][0008]

其中,k为非线性阶数,q为记忆深度,a

kq

为复增益系数。

[0009]

gmp模型是volterra级数的另一种简化版,由于包含交叉项,且模型系数相较于mp模型更多,故拟合度较高,但由于gmp模型的交叉项包含了对于输入信号的滞后项和超前项的累加,故其复杂度也较高,gmp的复基带模型为

[0010][0011]

其中,k

a

和l

a

分别为对齐部分阶数和记忆深度,k

b

和l

b

分别为滞后部分阶数和记忆深度,k

c

和l

c

分别为超前部分阶数和记忆深度,m

b

和m

c

分别为滞后度和超前度。

[0012]

在对比了以上几种功放模型之后,对于数字预失真的硬件实现时,可以看出记忆多项式模型是最佳的选择,是一种更易于硬件实现的功放数字模型,为数字预失真系统的实现方面提供了更加简洁的数学模型和更简单的硬件实现方式。

[0013]

目前,mp模型的实现方式主要包括查找表法和多项式法,其中,多项式法是根据mp模型的数学公式,直接搭建其硬件逻辑,以非线性阶数k=2,记忆深度q=2为例,其多项式法的硬件实现框图请参考图2。可以看出,在上述条件下,此方法所消耗的硬件乘法器较多,其中实数乘法器为7个,复数乘法器为3个。由于fpga内部的硬件乘法器逻辑资源较为宝贵,故在工程实现中常常采用查找表法,其硬件实现框图请参考图3。查找表的项数由输入信号幅度的量化位宽而决定,若量化位宽为n,则查找表项数为2

n

个。查找表的原理如下,以mp模型为例,由该公式结构可以看出,其前半部分可以单独看成一个关于|x(n)|的函数,即

[0014][0015]

则记忆多项式的表达式可以重写为

[0016][0017]

故g(|x(n)|)可以看作一个函数,|x(n)|为其索引,由图3所示。由于fpga内部包含了丰富的ram资源,故查找表法更适用于硬件平台上,此方法消耗了3个复数乘法器和3块ram,相对于多项式法减少了7个实数乘法器。但是,此模块需要求取信号的幅值|x(n)|,此运算为非线性运算,需要利用cordic核来求取输入信号,故会消耗较多的逻辑资源,并且由于查找表内的数据需要实时更新,对于包含自适应算法的预失真系统,每次预失真模块复增益系数a

kq

的迭代替换都会产生巨大的数据流,在工程实践中,一般采用乒乓操作的方式,将上下行查找表的深度均设置为2的次方数,在读取上部分ram(随机存取存储器)的同时,将更新的复增益值写入下部分ram,以保证数据迭代替换不出错。较深的ram会使得数据的更新速度变慢,导致系统整体工作频率的降低。

技术实现要素:

[0018]

本发明的目的在于提供一种基于记忆多项式的功放模型及其硬件实现方法,以至少解决现有基于记忆多项式的功放模型的硬件实现方法由于查找表内的数据需要实时更

新,对于包含自适应算法的预失真系统,每次预失真模块复增益系数a

kq

的迭代替换都会产生巨大的数据流,导致数据的更新速度变慢,系统整体工作频率降低的技术问题。

[0019]

本发明通过下述技术方案实现:

[0020]

一方面,本发明提供一种基于记忆多项式的功放模型,包括:

[0021]

lut模块,用于接收输入信号x(n),信号x(n)输入lut模块进行联合寻址,寻找到lut模块存储的与该输入信号相应的查找表内容,即信号x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

,所述lut模块将信号x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

并行输出至卷积模块;

[0022]

卷积模块,用于接收输入信号x(n),并将信号x(n),x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

与外部输入的复增益系数a

kq

进行卷积运算,得到输出信号y(n),所述输出信号为记忆多项式复基带模型,该模型被拆分成公式和公式其中,k为非线性阶数,q为记忆深度,两个公式分别通过所述lut模块和卷积模块实现。

[0023]

进一步,输入lut模块的信号x(n)为经过归一化处理和量化处理的信号x(n)。

[0024]

进一步,所述信号x(n)由i路信号和q路信号组成。

[0025]

进一步,所述lut模块包括k个双端口rom,所述工路和q路信号输入到所述k个双端口rom进行联合寻址。

[0026]

进一步,所述卷积模块采用fir滤波器。

[0027]

另一方面,本发明提供一种基于记忆多项式的功放模型的硬件实现方法,包括:

[0028]

将记忆多项式复基带模型拆分成公式和公式其中,k为非线性阶数,q为记忆深度,两个公式分别通过lut模块和卷积模块实现;

[0029]

将信号x(n)输入卷积模块;

[0030]

将信号x(n)输入lut模块进行联合寻址,寻找到lut模块存储的与该输入信号相应的查找表内容,即信号x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

;

[0031]

lut模块将信号x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

并行输出至卷积模块;

[0032]

通过卷积模块将信号x(n),x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

与外部输入的复增益系数a

kq

进行卷积运算,得到输出信号y(n)。

[0033]

进一步,将信号x(n)输入lut模块进行联合寻址之前,还包括:对输入lut模块的信号x(n)进行归一化处理和量化处理。

[0034]

进一步,所述信号x(n)由i路信号和q路信号组成。

[0035]

进一步,所述lut模块包括k个双端口rom,所述i路和q路信号输入到所述k个双端口rom进行联合寻址。

[0036]

进一步,所述卷积模块采用fir滤波器。

[0037]

本发明与现有技术相比,具有如下的优点和有益效果:

[0038]

本发明提供一种基于记忆多项式的功放模型及其硬件实现方法,首先分析了记忆多项式数学结构,将多项式分解成查找表结构与卷积结构,其次,结合matlab实现了对查找表结构内部元素的检索,x(n)|x(n)|2,x(n)|x(n)|4,

…

,x(n)|x(n)|

2k

为查找表的所有非线性项输出,最后,输出的非线性项通过卷积结构,与外部输入的复增益系数进行卷积运算。与其它常用的基于记忆多项式的功放模型的硬件实现方式相比,本发明所提出的基于记忆多项式的功放模型的低复杂度硬件实现方法能够消耗更少的硬件乘法器,而且硬件设计更为简单,不需要过多的地址控制逻辑与时序控制逻辑,至少解决了现有基于记忆多项式的功放模型的硬件实现方法由于查找表内的数据需要实时更新,对于包含自适应算法的预失真系统,每次预失真模块复增益系数a

kq

的迭代替换都会产生巨大的数据流,导致数据的更新速度变慢,系统整体工作频率降低的技术问题。

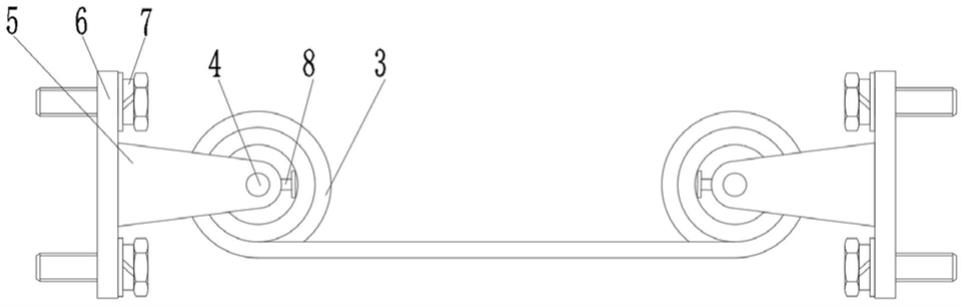

附图说明

[0039]

此处所说明的附图用来提供对本发明实施例的进一步理解,构成本技术的一部分,并不构成对本发明实施例的限定。在附图中:

[0040]

图1为预失真技术的原理图;

[0041]

图2为现有技术采用多项式法实现的mp模型的原理结构示意图;

[0042]

图3为现有技术采用查找表法实现的mp模型的原理结构示意图;

[0043]

图4为本发明实施例一种基于记忆多项式的功放模型及其硬件实现方法的原理结构示意图;

[0044]

图5为本发明实施例一种基于记忆多项式的功放模型及其硬件实现方法中卷积模块的原理结构示意图;

[0045]

图6为本发明实施例一种基于记忆多项式的功放模型及其硬件实现方法的查找表的分布图;

[0046]

图7为本发明实施例一种基于记忆多项式的功放模型及其硬件实现方法的查找表的仿真图;

具体实施方式

[0047]

为使本发明的目的、技术方案和优点更加清楚明白,下面结合实施例和附图,对本发明作进一步的详细说明,本发明的示意性实施方式及其说明仅用于解释本发明,并不作为对本发明的限定。

[0048]

实施例一

[0049]

请参考图1至图7,本发明实施例提供的一种基于记忆多项式的功放模型的硬件实现方法,包括:

[0050]

将记忆多项式复基带模型拆分成公式

和公式其中,k为非线性阶数,q为记忆深度,两个公式分别通过lut(显示查找表)模块和卷积模块实现;

[0051]

将信号x(n)输入卷积模块;

[0052]

将信号x(n)输入lut模块进行联合寻址,寻找到lut模块存储的与该输入信号相应的查找表内容,即信号x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

;

[0053]

lut模块将信号x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

并行输出至卷积模块;

[0054]

通过卷积模块将信号x(n),x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

与外部输入的复增益系数a

kq

进行卷积运算,得到输出信号y(n)。

[0055]

作为具体实施方式,将信号x(n)输入lut模块进行联合寻址之前,还包括:对输入lut模块的信号x(n)进行归一化处理和量化处理。

[0056]

作为具体实施方式,所述信号x(n)由i路信号和q路信号组成。

[0057]

作为具体实施方式,所述lut模块包括k个双端口rom,所述i路和q路信号输入到所述k个双端口rom进行联合寻址。

[0058]

作为具体实施方式,所述卷积模块采用fir滤波器(非递归型滤波器)。

[0059]

本发明实施例提供的一种基于记忆多项式的功放模型的硬件实现方法,首先分析了记忆多项式数学结构,将多项式分解成查找表结构与卷积结构,其次,结合matlab实现了对查找表结构内部元素的检索,x(n)|x(n)|2,x(n)|x(n)|4,

…

,x(n)|x(n)|

2k

为查找表的所有非线性项输出,最后,输出的非线性项通过卷积结构,与外部输入的复增益系数进行卷积运算。与其它常用的基于记忆多项式的功放模型的硬件实现方式相比,本发明实施例所提出的基于记忆多项式的功放模型的低复杂度硬件实现方法能够消耗更少的硬件乘法器,而且硬件设计更为简单,不需要过多的地址控制逻辑与时序控制逻辑,至少解决了现有基于记忆多项式的功放模型的硬件实现方法由于查找表内的数据需要实时更新,对于包含自适应算法的预失真系统,每次预失真模块复增益系数a

kq

的迭代替换都会产生巨大的数据流,导致数据的更新速度变慢,系统整体工作频率降低的技术问题。

[0060]

具体的,本发明实施例提供的一种基于记忆多项式的功放模型的低复杂度硬件实现方法,以非线性阶数k=2,记忆深度q=2为例,将式(2)拆成如下的公式

[0061][0062]

观察可得,式(6)可以分解成以下两个式子

[0063][0064][0065]

可以看出,式(8)是一个标准的卷积和形式,故可以采用类似于fir滤波器的结构形式,简化了记忆多项式的实现方式。式(7)是输入基带信号的查找表内容,具体实现方式

是,首先对输入端的归一化基带信号进行量化。对于数字基带信号的量化位宽,在工程应用上一般采用3~5,本实施例选取的量化位宽为5,则构成的查找表深度为25*25,完全满足系统的精度需求。量化方式为均匀量化,令输入端的复信号为

[0066]

x(n)=a bj

ꢀꢀꢀ

(9)

[0067]

故输出信号的幅度为a2 b2。根据所提出的结构,由输入信号进行统一寻址,查找表一共有k个输出值,分别为x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

,所以lut模块一共需要k个rom,这些rom均由输入的i路和q路信号联合寻址。由上面的式子可以得到查找表的输出值的实部和虚部分别为(a2 b2)a、(a2 b2)2a、(a2 b2)

k

a

…

和(a2 b2)b、(a2 b2)2b、

…

、(a2 b2)

k

b,可以得到,实部和虚部的查找表输出值是关于a=b对称的,故在硬件实现方面,可以只根据输入的实信号检索查找表,因为复信号就是实信号的镜像对称。经过量化后的查找表内部数据请参考图6所示(k=1)。

[0068]

查找表的行列数均为256,所以对查找表的检索只需要简单的移位逻辑和加法逻辑即可实现,例如,对于行数为5,列数为7的实部数据,可以将列数左移5位并加上行数,即可得到本数据对应的输出,其虚部数据则是将行数左移5位并加上列数。这样的设计大大简化了检索查找表的复杂度,提高了查找速度。

[0069]

由于不包含复增益系数a

kq

,故在硬件实现时不需要进行实时的数据替换,故只需要利用fpga内部的双端口rom即可实现查找表,这样做既省略了时序控制电路的设计,又节约了硬件资源。

[0070]

利用vivado自带的仿真软件,通过编写testbench代码,实现对查找表的仿真,仿真结果请参考图7。

[0071]

本次仿真在rom的前后端均添加了寄存器同步模块,故地址输入与输出之间产生了2个时钟周期的延迟,根据数据对比,可以看出,i路和q路的信号保持了图7所示的对称关系,仿真结果正确。

[0072]

由于需要迭代替换的数据变成了复增益系数的总个数,为(q 1)(k 1),大大降低了所需的存储单元,所以对于复增益系数的迭代替换可以利用寄存器实现。卷积模块可以利用直接型fir结构,仅采用一个复数乘法器即可实现卷积功能,大大减少了硬件乘法器的消耗。卷积模块的具体实现方式请参考图5。

[0073]

综上所示,本发明实施例提出的一种基于记忆多项式的功放模型的硬件实现方法的实现模块与其它记忆多项式实现模块的资源消耗对比表如下所示,其中假定乘法器和加法器的周期都为p,且cordic核的周期为m。

[0074][0075]

根据上表所示,本发明实施例提出的一种基于记忆多项式的功放模型的硬件实现方法的实数乘法器消耗比多项式法减少了2q 3个,利用直接型fir实现方法的复数乘法器只消耗了一个,均比多项式法和查找表法少,加法器消耗均比多项式法和查找表法少,且rom消耗是根据输入信号的量化位宽而定的,具有可控性。对于运算周期,可以看出,新提出的结构比多项式法减少了(3k

‑

1)p个周期,并且比查找表法减少了m个周期,提高了预失真器的工作频率。

[0076]

本发明实施例提出的一种基于记忆多项式的功放模型的硬件实现方法可以应用在拟合甲乙类功率放大器上,实现数字预失真的功能,根据实际功放的非线性特性,可以适当调节功放模型的非线性项数与记忆深度,以满足建模的精度。

[0077]

实施例二

[0078]

请参考图1

‑

图7,本发明实施例提供的一种基于记忆多项式的功放模型,包括:

[0079]

lut模块,用于接收输入信号x(n),信号x(n)输入lut模块进行联合寻址,寻找到lut模块存储的与该输入信号相应的查找表内容,即信号x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

,所述lut模块将信号x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

并行输出至卷积模块;

[0080]

卷积模块,用于接收输入信号x(n),并将信号x(n),x(n)|x(n)|2,x(n)|x(n)|4…

x(n)|x(n)|

2k

与外部输入的复增益系数a

kq

进行卷积运算,得到输出信号y(n),所述输出信号为记忆多项式复基带模型,该模型被拆分成公式和公式其中,k为非线性阶数,q为记忆深度,两个公式分别通过所述lut模块和卷积模块实现。

[0081]

作为具体实施方式,输入lut模块的信号x(n)为经过归一化处理和量化处理的信号x(n)。

[0082]

作为具体实施方式,所述信号x(n)由i路信号和q路信号组成。

[0083]

作为具体实施方式,所述lut模块包括k个双端口rom,所述i路和q路信号输入到所述k个双端口rom进行联合寻址。

[0084]

作为具体实施方式,所述卷积模块采用fir滤波器。

[0085]

本发明实施例提供的一种基于记忆多项式的功放模型的具体实现过程,由于在实施例一一种基于记忆多项式的功放模型的硬件实现方法中已有详细说明,故此处不再赘述。

[0086]

本领域普通技术人员可以理解实现上述事实和方法中的全部或部分步骤是可以通过程序来指令相关的硬件来完成,涉及的程序或者所述的程序可以存储于一计算机所可读取存储介质中,该程序在执行时,包括如下步骤:此时引出相应的方法步骤,所述的存储介质可以是rom/ram、磁碟、光盘等等

[0087]

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。