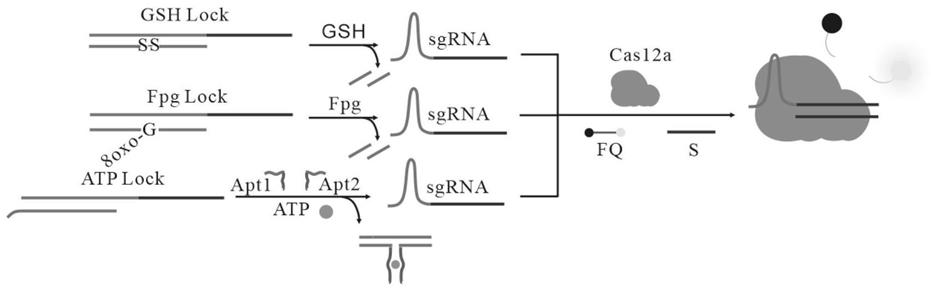

1.本发明涉及全球卫星导航系统接收机中时钟源的传输链路中时钟信号的阻抗匹配以及谐波抑制系统和方法,来提升接收机的捕获效果。

背景技术:

2.当前全球卫星导航系统发展迅速,北斗三号全面组网成功,助力全球导航定位系统发展,目前全球卫星导航系统主要分为北斗(bds)、gps、伽利略、格洛纳斯在内的四大卫星导航系统。而目前高精度的卫星接收机板卡的定位精度和其时钟信号质量密切相关,板载高精度时钟主要有tcxo(温补晶振)、ocxo(恒温晶振),ocxo虽然精度更高,但是体积较大,难以集成在基带板卡上,所以目前常用的为tcxo晶振。

3.目前射频和基带芯片的时钟输入要求基本为大于0.8vpp,所以为了提高精度同时降低功耗,目前tcxo输出多为削峰正弦波(clippedsin),而削峰正弦波的输出则会增加输出的谐波分量,同时tcxo输出的占空比因为晶振厂商生产工艺和pcb设计干扰影响,占空比难以达到完美的50%,所以会产生偶次谐波,结合以上原因影响,tcxo输出的5次谐波内能量增加,会干扰到基带捕获效果,最终影响定位精度,而目前高精度定位接收机的时钟源缺乏对有效处理,时钟链路大多数都是通过10nf电容连接至时钟接收端。

技术实现要素:

4.针对现有技术的不足,本发明提供了一种基于导航接收机时钟链路的匹配及谐波抑制系统及方法,来提升接收机的捕获效果。

5.本发明通过低相噪tcxo输出削峰正弦波,通过π型滤波电路、磁珠以及三端电容器组成的组合滤波电路进行滤波,然后通过调压电路,将信号调整至lvcmos电平输出至时钟驱动clockbuffer芯片5pb1216和5pb1214,通过时钟驱动芯片输出10路时钟信号,然后通过组合滤波电路进行滤波衰减,其中8路输出至射频芯片max2771,1路输出至zynqxc7z035,通过xc7z035pll倍频输出,经过组合滤波电路,将同步时钟信号输出至采样adc ad9268,至此完成整个高精度导航接收机的时钟链路的处理。

6.术语解释:

7.1、lvcmos电平,是一种常用的电平标准、是一种平方波,lvttl也是点评标准的一种,由于lvttl输出不能驱动cmos输入,所以对应3.3v lvttl,出现了lvcmos,可以与3.3v的lvttl直接相互驱动。相对ttl有了更大的噪声容限,输入阻抗远大于ttl输入阻抗。

8.2、clockbuffer芯片,是一种时钟驱动芯片,5pb1216(14)是一个高性能的tcxo/lvcmos时钟扇形缓冲区系列,每个输出都具有单独的oe引脚。clkin引脚可以接受平方波(lvcmos)或剪切正弦波(如tcxo剪切正弦波输出)作为输入。有3种不同的风扇输出版本:1:3、1:4和1:6。5pb1216(14)具有业界领先的低抖动和极低的电流消耗。主要应用于射频和基带外围时钟分布电路。

9.本发明的技术方案为:

10.一种基于导航接收机时钟链路的匹配及谐波抑制系统,包括tcxo、电平转换电路、组合滤波电路、clockbuffer时钟驱动电路、射频、adc、信号处理端;

11.通过tcxo输出削峰正弦波,削峰正弦波通过电平转换电路进行电平转换,并通过组合滤波电路进行滤波,再通过调压电路将信号调整至lvcmos电平输出至clockbuffer时钟驱动电路,输出10路时钟信号,10路时钟信号分别通过组合滤波电路进行滤波衰减,输出的其中8路时钟信号输出至射频,1路时钟信号输出至信号处理端,从信号处理端倍频输出后经过组合滤波电路,将同步时钟信号输出至采样adc,完成整个高精度导航接收机的时钟链路的处理。

12.根据本发明优选的,tcxo的型号为rpt5032a,射频的型号为max2771,信号处理端的型号为zynq xc7z035,adc的型号为ad9628。

13.根据本发明优选的,电平转换电路包括电源3v3_cb、电阻r4、电阻r5;

14.电阻r4一端连接电源3v3_cb,另一端连接电阻r5的一端,电阻r5另一端与地网络gnd_cb连接,电阻r4与电阻r5相连端耦合直流信号(1.65dc)。

15.根据本发明优选的,组合滤波电路包括t型滤波电路和π型电路;t型滤波电路包括磁珠和三端多层陶瓷电容器;π型电路连接t型滤波电路;

16.通过π型电路对信号进行衰减处理,同时进行阻抗匹配,调整负载功率和抑制信号反射,通过磁珠抑制衰减时钟脉冲信号中的高次谐波,同时连接三端多层陶瓷电容器。

17.根据本发明优选的,在π型电路中,通过平衡式π电路衰减公式如式(ⅰ)、式(ⅱ)所示:

[0018][0019][0020]

式(ⅰ)、式(ⅱ)中,z是指特性阻抗,k是指衰减系数,代入式(ⅰ)、式(ⅱ),求取电阻r1、电阻r2、电阻r3;π型电路包括电阻r1、电阻r2、电阻r3;

[0021]

功率衰减通过式(ⅲ)得到:

[0022][0023]

式(ⅲ)中,s

11

为信号输入反射系数,即输入回波损耗;s

12

为信号反向传输系数;s

21

为正向传输系数,也就是插损;s

22

为输出反射系数,也就是输出回波损;a为衰减系数,s1′1为接入π衰减电路后的s

11

参数,s1′2为接入π衰减电路后的s

12

参数,s

′

21

为接入π衰减电路后的s

21

参数,s

′

22

即为s

22

参数;s

′

为接入π衰减电路后的功率衰减结果;rl是指负载阻抗,rs为信号源阻抗;

[0024]

通过π型电路连接磁珠u1,通过磁珠u1连接三端电容器z1,通过磁珠u1减弱信号的emi干扰的同时,与三端电容器z1串联构成t型滤波器电路进行信号滤波,当电感和电容并

联时,谐振频率为:l为电路磁珠等效电感大小,c为电路中三端电容器等效电容大小。

[0025]

根据本发明优选的,clockbuffer时钟驱动电路中,晶振产生的时钟信号clk_b1通过组合滤波电路输入至clockbuffer芯片,3v3_cb为clockbuffer芯片提供3.3v电源,clockbuffer芯片的oe端通过4.7k上拉电阻接至3v3_cb,使clockbuffer芯片输出时钟信号,时钟信号的输出端通过组合滤波电路分别连接xtal_rf1、xtal_rf2、xtal_rf3、xtal_rf4,为射端max2771提供时钟信号,时钟信号通过连接组滤波电路连接clockbuffer芯片。

[0026]

根据本发明优选的,通过组合滤波电路后将滤波后的时钟信号输入至clockbuffer时钟驱动电路中的clockbuffer芯片,通过clockbuffer芯片输出10路16.369mhz时钟信号,10路时钟信号输出通过组合滤波电路后,其中8路时钟信号输出至射频,1路时钟信号输出至信号处理端,通过射频进行下变频混频,将下变频的模拟i中频信号输出至adc,其中adc的采样时钟通过信号处理端将clockbuffer芯片输出时钟信号进行pll倍频至65.476mhz,将倍频后的信号通过三端多层陶瓷电容器进行滤波,由adc将模拟i中频信号转换为12位数字i中频信号后传递至信号处理端,最终由信号处理端进行信号的捕获跟踪或者中频信号的传输处理。

[0027]

进一步优选的,clockbuffer芯片的型号为5pb1214或5pb1216。

[0028]

上述基于导航接收机时钟链路的匹配及谐波抑制系统的工作方法,包括步骤如下:

[0029]

(1)通过低相噪tcxo输出削峰正弦波;

[0030]

(2)削峰正弦波通过电平转换电路进行电平转换,并通过组合滤波电路进行滤波,生成时钟信号;

[0031]

(3)通过调压电路将步骤(2)生成的时钟信号调整至lvcmos电平输出至clockbuffer时钟驱动电路,输出10路时钟信号;

[0032]

(4)步骤(3)输出的10路时钟信号通过组合滤波电路进行滤波衰减;

[0033]

(5)经过滤波衰减的10路时钟信号,8路时钟信号发送到射频,1路时钟信号发送到信号处理端;

[0034]

(6)从信号处理端倍频输出后经过组合滤波电路,将同步时钟信号输出至采样adc,完成整个高精度导航接收机的时钟链路的处理。

[0035]

本发明的有益效果为:

[0036]

1、与传统tcxo输出的削峰正弦波(clippedsin)相比,选用增加组合滤波电路的tcxo替代传统输出削峰正弦波tcxo来实现时钟信号的传输,提高了tcxo时钟输出信号的质量和减少本振信号的谐波。虽然会衰减一定功率,但是会把其他高次谐波衰减至不影响信号处理的水平。

[0037]

2、本发明在xc7z035 pll倍频时钟环路输出使用三端多层陶瓷电容器进行谐波,降低高次谐波对adc采样的影响。为导航接收机提供一个高精度的时钟链路。

[0038]

3、本发明不仅可以用于卫星导航中的基带通信领域,对其它通信领域的数据传输也同样适用,本发明结构简单,实现方便,能够实现多层次、大规模的应用。

附图说明

[0039]

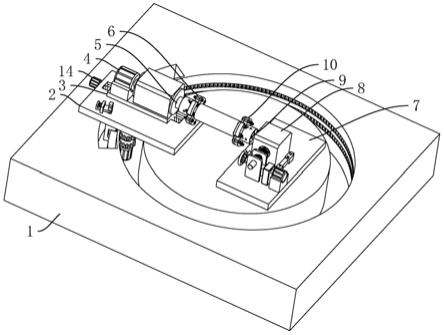

图1为基于导航接收机时钟链路的匹配及谐波抑制系统的结构示意图;

[0040]

图2为组合滤波电路示意图;

[0041]

图3(a)为单三端多层陶瓷电容器对插损的影响的示意图;

[0042]

图3(b)为磁珠三端多层陶瓷电容器组合滤波对插损的影响的示意图;

[0043]

图4为clockbuffer时钟驱动电路示意图;

[0044]

图5为基于导航接收机时钟链路的匹配及谐波抑制方法的流程示意图;

[0045]

图6为射频时钟输入组合滤波前频谱波形示意图;

[0046]

图7为射频时钟输入组合滤波后频谱波形示意图;

[0047]

图8为实际采集数字中频未滤波数据频域波形示意图;

[0048]

图9为实际采集数字中频滤波后数据频域波形示意图。

具体实施方式

[0049]

下面结合说明书附图和实施例对本发明作进一步限定,但不限于此。

[0050]

实施例1

[0051]

一种基于导航接收机时钟链路的匹配及谐波抑制系统,实现提升时钟优化进而提升接收机的捕获效果,如图1所示,包括tcxo、电平转换电路、组合滤波电路、clockbuffer时钟驱动电路、射频、adc、信号处理端;

[0052]

通过tcxo输出削峰正弦波,削峰正弦波通过电平转换电路进行电平转换,并通过组合滤波电路进行滤波,再通过调压电路将信号调整至lvcmos电平输出至clockbuffer时钟驱动电路,输出10路时钟信号,10路时钟信号分别通过组合滤波电路进行滤波衰减,输出的其中8路时钟信号输出至射频,1路时钟信号输出至信号处理端,从信号处理端倍频输出后经过组合滤波电路,将同步时钟信号输出至采样adc,完成整个高精度导航接收机的时钟链路的处理。

[0053]

实施例2

[0054]

根据实施例1所述的一种基于导航接收机时钟链路的匹配及谐波抑制系统。

[0055]

tcxo的型号为rpt5032a,其相位噪声小于

‑

160dbc/hz,相位抖动小于0.13ps,频率稳定度最低可达0.05ppm;射频的型号为max2771,信号处理端的型号为zynq xc7z035,adc的型号为ad9628。

[0056]

电平转换电路包括电源3v3_cb、电阻r4、电阻r5;

[0057]

电阻r4(1kω)一端连接电源3v3_cb(3.3v),另一端连接电阻r5(1kω)的一端,电阻r5另一端与地网络gnd_cb连接,电阻r4与电阻r5相连端耦合直流信号(1.65dc)。

[0058]

组合滤波电路包括t型滤波电路和π型电路;t型滤波电路包括磁珠和三端多层陶瓷电容器;π型电路连接t型滤波电路;

[0059]

tcxorpt5032a输出的电平为0.8vpp(clipped sin),通过lvcmos

‑

3.3调压电路,其中通过电阻r4(1kω)一端连接电源3v3_cb(3.3v)一端连接r5(1kω),r5另一端与地网络gnd_cb相连,r4与r5相连端耦合1.65dc(直流)信号,输出至组合滤波电路,组合滤波电路如图2所示,其中,3v3_cb为组合滤波电路提供3.3v电源,电容c1和c2作为滤波电容连接gnd_cb到地,起到滤波作用,同时使得电源和地之间为低阻抗,电源接近理想电压源。clk_b1和

tg2520smn的out端通过连接的电容c3,再连接由电阻r1、r2、r3组成的π型电路进行滤波。之后连接三端电容器z1和磁珠u1组成的t型滤波电路。t型滤波电路和π型滤波电路构成组合滤波电路。其中电阻r5和r4通过连接3v3_cb组成调压电路,把0.8vpp时钟信号加入直流偏置。

[0060]

通过π型电路对信号进行衰减处理,同时进行阻抗匹配,调整负载功率和抑制信号反射,通过磁珠抑制衰减时钟脉冲信号中的高次谐波,同时连接三端多层陶瓷电容器。但由于三端多层陶瓷电容器的插入损耗在2次谐波到5次谐波之间频率变化较小,为了避免这个问题,采用磁珠和三端多层陶瓷电容器结合构成阻抗匹配的t型滤波电路。

[0061]

在π型电路中,通过平衡式π电路衰减公式如式(ⅰ)、式(ⅱ)所示:

[0062][0063][0064]

式(ⅰ)、式(ⅱ)中,z是指特性阻抗,k是指衰减系数,代入式(ⅰ)、式(ⅱ),求取电阻r1、电阻r2、电阻r3;π型电路包括电阻r1、电阻r2、电阻r3;

[0065]

已知特性阻抗z为10kω,衰减系数k为1.3,代入式(ⅰ)、式(ⅱ)得到:r2=2.65k,r1=r3=76.6k,0.8vpp信号衰减至0.6vpp:

[0066]

功率衰减通过式(ⅲ)得到:

[0067]

功率衰减为4.5db通过式(ⅲ)得到:s

11

反射损耗降低为原来的a平方分一:

[0068][0069]

式(ⅲ)中,s

11

为信号输入反射系数,即输入回波损耗;s

12

为信号反向传输系数;s

21

为正向传输系数,也就是插损;s

22

为输出反射系数,也就是输出回波损;a为衰减系数,s

′

11

为接入π衰减电路后的s

11

参数,s

′

12

为接入π衰减电路后的s

12

参数,s

′

21

为接入π衰减电路后的s

21

参数,s

′

22

即为s

22

参数;s

′

为接入π衰减电路后的功率衰减结果;

[0070]

s

11

反射损耗s11为:s11=20logτ=20logs

11

=

‑

72db

[0071]

假设rl=10kω,rs=10.05kω;rl是指负载阻抗,rs为信号源阻抗;

[0072]

由此可得4.5db的衰减可以让反射损耗降低25.9db;

[0073]

通过π型电路连接磁珠u1(blm03ag100sn1),通过磁珠u1连接三端电容器z1(nfm21cc221r1h3d),通过磁珠u1减弱信号的emi干扰的同时,与三端电容器z1串联构成t型滤波器电路进行信号滤波,当电感和电容并联时,谐振频率为:l为电路磁珠等效电感大小,c为电路中三端电容器等效电容大小。磁珠主要用来抑制衰减时钟脉冲信号中的高次谐波。

[0074]

通过测试对比(图3(a)和图3(b))可以得出结论:当使用三端电容器进行滤波时,二次谐波的输入损耗在2.2db/dec,在五次谐波输入损耗降低至1.4db/dec,当使用磁珠和

三端电容器构成的t型滤波器电路对高次谐波的衰减可以达到7db/dec,相比较可以从2db/dec衰减到7db/dec,在时钟五次谐波衰减量可达28.3db,谐波抑制效果明显。

[0075]

clockbuffer时钟驱动电路如图4所示,图4中,接收输入时钟信号,晶振产生的时钟信号clk_b1通过组合滤波电路输入至clockbuffer(5pb1214),3v3_cb为clockbuffer提供3.3v电源,r1和r2电阻连接3v3_cb组成调压电路,把0.8vpp时钟信号clk_b1加入直流偏置。clockbuffer的oe端通过4.7k上拉电阻接至3v3_cb,使能clockbuffer时钟输出信号,时钟信号的输出端通过组合滤波电路分别连接xtal_rf(1

‑

4),为max2771提供时钟信号。时钟信号通过连接组滤波电路连接clockbuffer时钟驱动芯片5pb1216(14)。3v3_cb为vdd提供3.3v电源,其中通过连接c59和c71接地,起到滤波作用。

[0076]

clockbuffer时钟驱动电路中,晶振产生的时钟信号clk_b1通过组合滤波电路输入至clockbuffer芯片(5pb1214),3v3_cb为clockbuffer芯片提供3.3v电源,clockbuffer芯片的oe端通过4.7k上拉电阻接至3v3_cb,使clockbuffer芯片输出时钟信号,时钟信号的输出端通过组合滤波电路分别连接xtal_rf1、xtal_rf2、xtal_rf3、xtal_rf4,为射端max2771提供时钟信号,时钟信号通过连接组滤波电路连接clockbuffer芯片。

[0077]

通过组合滤波电路后将滤波后的时钟信号输入至clockbuffer时钟驱动电路中的clockbuffer芯片,通过clockbuffer芯片输出10路16.369mhz时钟信号,10路时钟信号输出通过组合滤波电路后,其中8路时钟信号输出至射频,1路时钟信号输出至信号处理端,通过射频进行下变频混频,将下变频的模拟i中频信号输出至adc,其中adc的采样时钟通过信号处理端将clockbuffer芯片输出时钟信号进行pll倍频至65.476mhz,将倍频后的信号通过三端多层陶瓷电容器进行滤波,由adc将模拟i中频信号转换为12位数字i中频信号后传递至信号处理端,最终由信号处理端进行信号的捕获跟踪或者中频信号的传输处理。

[0078]

clockbuffer芯片的型号为5pb1214或5pb1216。

[0079]

与传统tcxo输出的削峰正弦波(clippedsin)相比,选用增加组合滤波电路的tcxo替代传统输出削峰正弦波tcxo来实现时钟信号的传输,提高了tcxo时钟输出信号的质量和减少本振信号的谐波。虽然会衰减一定功率,但是会把其他高次谐波衰减至不影响信号处理的水平。同时,同时本发明在xc7z035 pll倍频时钟环路输出使用三端多层陶瓷电容器进行谐波,降低高次谐波对adc采样的影响。为导航接收机提供一个高精度的时钟链路。

[0080]

图6为射频时钟输入组合滤波前频谱波形示意图;图6中,横坐标为信号频率,纵坐标为信号的功率,对于五次谐波时钟信号功率由

‑

4dbm。图7为射频时钟输入组合滤波后频谱波形示意图;图7中,射频时钟输入组合滤波后的频谱波形,横坐标为信号频率,纵坐标为信号的功率,对于五次谐波时钟信号功率由

‑

20dbm。五次谐波抑制达到16db,相较于图6组合滤波前的效果,滤除高次谐波非常明显。

[0081]

通过实际测试,图8为实际采集数字中频未滤波数据频域波形示意图;图8中,(a)为未滤波时中频数据频域示意图,其中横坐标为频率,纵坐标为频率幅度。(b)为未滤波时中频数据时域示意图,其中横坐标为时间,纵坐标为振幅。(c)为未滤波时中频数据的adc量化图,横坐标为频率谱线信号,纵坐标为量化值。图8可以看到未滤波前射频输入端的时钟信号频谱中,时钟信号的高次谐波明显,11次谐波的功率仍然可以达到

‑

11dbm,导航信号通过射频进行下变频后由adc转换的数字信号(测试仅使用了其中高3位进行模数转换)进行频域转换后如图8所示。

[0082]

图9为实际采集数字中频滤波后数据频域波形示意图;图9中,(a)为滤波后中频数据频域示意图,其中横坐标为频率,纵坐标为频率幅度。(b)为滤波后中频数据时域示意图,其中横坐标为时间,纵坐标为振幅。(c)为滤波后中频数据的adc量化图,横坐标为频率谱线信号,纵坐标为量化值。在中频中心频点3.996mhz的附近产生了较多频率分量值,通过组合滤波后数字中频信号频域转换后如图9所示,频率分量值基本被滤除,最后捕获跟踪后观测信号的载噪比,时钟链路未优化前,捕获跟踪到卫星信号的平均载噪比为43.46db(表1),表1为实际捕获跟踪后卫星载噪比(时钟链路未滤波);时钟链路未优化后捕获跟踪到卫星信号的平均载噪比为45.46db(表2),提升了2db,表2为实际捕获跟踪后卫星载噪比(时钟链路滤波后),本发明不仅可以用于卫星导航中的基带通信领域,对其它通信领域的数据传输也同样适用,本发明结构简单,实现方便,能够实现多层次、大规模的应用。

[0083]

表1

[0084][0085]

表2

[0086][0087]

实施例3

[0088]

实施例1或2基于导航接收机时钟链路的匹配及谐波抑制系统的工作方法,如图5所示,包括步骤如下:

[0089]

(1)通过低相噪tcxo输出削峰正弦波;

[0090]

(2)削峰正弦波通过电平转换电路进行电平转换,并通过组合滤波电路进行滤波,生成时钟信号;

[0091]

(3)通过调压电路将步骤(2)生成的时钟信号调整至lvcmos电平输出至clockbuffer时钟驱动电路,输出10路时钟信号;

[0092]

(4)步骤(3)输出的10路时钟信号通过组合滤波电路进行滤波衰减;

[0093]

(5)经过滤波衰减的10路时钟信号,8路时钟信号发送到射频,1路时钟信号发送到信号处理端;

[0094]

(6)从信号处理端倍频输出后经过组合滤波电路,将同步时钟信号输出至采样adc,完成整个高精度导航接收机的时钟链路的处理。

[0095]

本发明的保护范围,并不仅限于上述实施例的记载,所有基于本发明发明思想的技术方法,皆在本发明保护范围内。新型发明思想的技术方法,皆在本发明保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。