1.本实用新型涉及半导体封装技术领域,具体涉及一种带有电磁屏蔽的芯片封装结构。

背景技术:

2.在半导体封装技术领域,利用多芯片封装(mcp,multi

‑

chip package)技术将不同功能、不同频段的多颗芯片封装于同一个封装件中,可以以较低的功耗实现性能更高的高密度、高性价比解决方案。

3.由于芯片产生的电磁波对封装件内部或者外部容易造成不期望的电磁干扰(emi,electromagnetic interference),导致电路功能受到影响,因此,为解决电磁干扰问题,需要设置电磁屏蔽结构。现有技术通常在封装工艺完成后,在封装件外表面利用溅射工艺形成一层金属层,该金属层与芯片位置相对应,从而达到电磁屏蔽效果。然而,这种方式由于仅有一层金属层,其屏蔽效果有待进一步提升。

技术实现要素:

4.发明目的:为了解决现有技术中芯片封装结构的电磁屏蔽效果差的问题,本实用新型提供一种带有电磁屏蔽的芯片封装结构。

5.技术方案:本实用新型提供一种带有电磁屏蔽的芯片封装结构,包括芯片、重布线层、塑封层、第一屏蔽层及第二屏蔽层;塑封层位于芯片四周,包裹所述芯片;第一屏蔽层嵌入在塑封层内,且包围所述芯片;芯片包括正面和背面,重布线层位于芯片正面,第二屏蔽层位于芯片背面,重布线层上设置有接地端,第一屏蔽层与第二屏蔽层、接地端相连接,第一屏蔽层与第二屏蔽层均为金属材质。第一屏蔽层与第二屏蔽层组成五面的半封闭屏蔽结构。

6.进一步地,还包括凸块下金属层、焊球及第三屏蔽层,焊球位于封装结构边缘位置,重布线层的开口位置设有凸块下金属层,凸块下金属层与所述焊球连接;焊球围成的区域内设有第三屏蔽层,第三屏蔽层为金属材质,所述第三屏蔽层与重布线层连接。第一屏蔽层、第二屏蔽层、第三屏蔽层组成六面的屏蔽结构,屏蔽效果更好。

7.进一步地,所述第一屏蔽层包括多个金属柱,金属柱的中心线与芯片所在平面垂直,金属柱至少绕芯片一周。

8.进一步地,相邻金属柱紧密排列,均匀分布。

9.进一步地,所述第一屏蔽层为金属墙。

10.进一步地,所述第二屏蔽层远离芯片的一侧依次设置有粘结层和保护层,所述粘结层的材料为味之素堆积膜,保护层的材料为硅。

11.进一步地,所述芯片有多个,多个芯片位于同一平面,第一屏蔽层包围至少一个芯片,不同芯片之间填充有塑封层。

12.进一步地,所述芯片有多个,多个芯片堆叠设置,芯片至少包括第一层芯片和第二

层芯片,塑封层包括第一塑封层和第二塑封层,所述第一塑封层包裹第一层芯片,第二塑封层包裹第二层芯片,所述第一屏蔽层贯穿第一塑封层及第二塑封层,且包围至少一个芯片。

13.进一步地,所述塑封层采用味之素堆积膜。

14.进一步地,所述第一屏蔽层与第二屏蔽层的材料为ti、cu、al、ni中的一种或多种。

15.有益效果:本实用新型提供一种带有电磁屏蔽的芯片封装结构,相比较现有技术,在芯片四周及背面形成至少半封闭的电磁屏蔽结构,甚至在芯片外部六个面设有电磁屏蔽结构,从而实现电磁屏蔽。相对于传统仅在塑封层外部设置一层金属层的结构而言,本技术的电磁屏蔽结构将芯片包围在半封闭的空间内,电磁屏蔽效果更好,降低电磁干扰,减少对芯片性能的影响。

附图说明

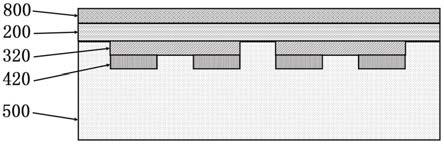

16.图1为实施例一带有电磁屏蔽的芯片封装结构的截面图;

17.图2为实施例一带有电磁屏蔽的芯片封装结构的剖视图;

18.图3为实施例二带有电磁屏蔽的芯片封装结构的剖视图;

19.图4为实施例三带有电磁屏蔽的芯片封装结构的截面图;

20.图5为实施例四带有电磁屏蔽的芯片封装结构的截面图;

21.图6为实施例四增加第三屏蔽层的带有电磁屏蔽的芯片封装结构的截面图。

具体实施方式

22.下面结合附图与具体实施方式,对本实用新型做进一步解释说明。

23.实施例一:

24.如图1所示,一种带有电磁屏蔽的芯片封装结构,包括芯片1、重布线层(rdl,redistribution layer)2、塑封层3、凸块下金属层(ubm,under bump metallurgy)4、焊球5、第一屏蔽层6及第二屏蔽层7。

25.芯片1可以有一个或多个,多个芯片1位于同一平面,芯片1外包裹塑封料,形成塑封层3,多个芯片1之间也填充有塑封料,所述塑封料为abf(ajinomoto build

‑

up film,味之素堆积膜)。

26.第一屏蔽层6嵌入在塑封层3内,且包围所述芯片1。若芯片有多个,第一屏蔽层6至少包围一个芯片,可根据需要对其中一个芯片或多个芯片进行电磁屏蔽。所述第一屏蔽层6包括多个金属柱,金属柱的中心线与芯片1所在平面垂直,金属柱至少绕芯片一周,如图2所示为图1a

‑

a方向的剖视图。相邻金属柱紧密排列,均匀分布,金属柱的间距、数量可控,间距越小,数量越多,则电磁屏蔽效果越好。所述金属柱可以采用在塑封层打孔,通过电镀、磁控溅射等方式向孔内填充金属而形成。

27.芯片1包括正面和背面,重布线层2位于芯片1正面,第二屏蔽层7位于芯片1背面,重布线层2上设置有接地端。所述第二屏蔽层7远离芯片1的一侧依次设置有粘结层8和保护层9,所述粘结层8的材料为abf,保护层9的材料为硅。

28.第一屏蔽层6与第二屏蔽层7、接地端相连接,第一屏蔽层6与第二屏蔽层7均为金属材质,可采用ti、cu、al、ni中的一种或多种制成。第一屏蔽层6与第二屏蔽层7共同形成五个面的半封闭的电磁屏蔽结构。相对于传统仅在塑封层外部设置一层金属层的结构,该电

磁屏蔽结构将芯片包围在五个面的半封闭的空间内,电磁屏蔽效果更好。

29.实施例二:

30.实施例二与实施例一的区别在于,第一屏蔽层6为金属墙,如图3所示,可以采用在塑封料中开凹槽,通过电镀、磁控溅射等方式向凹槽内填充金属而形成。其他内容与实施例一相同。

31.实施例三:

32.为了进一步加强电磁屏蔽效果,实施例三在实施例一或实施例二的基础上增加了第三屏蔽层,已达到更优的屏蔽效果:

33.还包括第三屏蔽层10,重布线层2可以根据实际需求设置开口区域的位置,开口位置用于设置凸块下金属层4,在此情况下,凸块下金属层4分散设置,焊球5可任意排布于封装结构表面。本实施例焊球5位于封装结构边缘位置,重布线层2根据焊球5的位置设置开口位置,开口位置上设有凸块下金属层4,凸块下金属层4与所述焊球5连接;焊球5围成的区域内设有第三屏蔽层10,第三屏蔽层10为金属材质,利用rdl布线将第三屏蔽层10与重布线层2连接。第三屏蔽层10可采用电镀、磁控溅射等方式制作而成。

34.所述第一屏蔽层6通过重布线层2与第三屏蔽层10连通,从而形成第一屏蔽层6、第二屏蔽层7及第三屏蔽层10的六面屏蔽结构,以实现更好的电磁屏蔽效果。

35.实施例四:

36.带有电磁屏蔽的芯片封装结构同样适用于多芯片堆叠的封装,如图5所示,实施例四与实施例一或实施例二的区别在于,多个芯片堆叠设置,以两层芯片为例,芯片包括第一层芯片11、第二层芯片12,塑封层包括第一塑封层31和第二塑封层32,所述第一塑封层31包裹第一层芯片11,第二塑封层32包裹第二层芯片12,所述第一屏蔽层6贯穿第一塑封层31及第二塑封层32,且包围第一层芯片11及第二层芯片12。实际应用中,可根据需要对多层芯片中一个芯片或多个芯片进行电磁屏蔽。所述第一屏蔽层6包括嵌入在第一塑封层31的第一部分和嵌入在第二塑封层32的第二部分,这两部分的具体实现方式可以自由组合,如可以均为金属柱或金属墙,也可以一部分为金属柱一部分为金属墙。对于多芯片堆叠的封装结构,同样也可以增加实施例三中的第三屏蔽层10以实现更好的电磁屏蔽效果,如图5。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。