1.本发明涉及集成电路设计,尤其涉及一种比较器及判决反馈均衡电路(decision feedback equalization,dfe)。

背景技术:

2.随着计算机技术的不断发展,越来越多的产品经由计算机控制,实现了智能化。然而,伴随着应用场景的不断扩大,人们也对计算机的性能提出了越来越高的要求,包括更快的运行速度和更低的功耗。

3.存储器件是计算机硬件系统中不可缺少的部分,能够存放计算机运行期间的指令和数据,以保证计算机的正常运行。其中,比较器是常用存储器件中的重要组成部分,提升比较器的性能有助于对计算机整体性能的提升。

技术实现要素:

4.本发明实施例期望提出一种比较器及判决反馈均衡电路,能够消除码间串扰的影响、提高比较器的工作速率。

5.本发明的技术方案是这样实现的:

6.本技术实施例提供一种比较器,所述比较器包括:第二级电路、第一输入电路、第二输入电路、第一交叉耦合电路和第二交叉耦合电路;

7.所述第一交叉耦合电路连接所述第一输入电路;所述第二交叉耦合电路连接所述第二输入电路;

8.所述第一输入电路和所述第二输入电路还均与所述第二级电路连接;

9.所述第二级电路连接电源端或接地端;其中,

10.所述第一输入电路,用于在导通时的采样阶段根据输入信号和第一参考信号生成第一数据端电压和第一参考端电压;

11.所述第一交叉耦合电路,用于将所述第一数据端电压和所述第一参考端电压相互正反馈,生成所述第一差分信号;

12.所述第二输入电路,用于在导通时的采样阶段根据所述输入信号和第二参考信号生成第二数据端电压和第二参考端电压;

13.所述第二交叉耦合电路,用于将所述第二数据端电压和所述第二参考端电压相互正反馈,生成所述第二差分信号;

14.所述第二级电路,用于在重生阶段对所述第一差分信号或所述第二差分信号进行放大处理和锁存处理,以输出比较信号。

15.上述方案中,所述第一交叉耦合电路包括:第一耦合晶体管和第二耦合晶体管;所述第一差分信号包括:第一参考端输出信号和第一数据端输出信号;

16.所述第一耦合晶体管的第一端连接所述第二耦合晶体管的控制端,并连接到所述第一输入电路的第一输出端;所述第一耦合晶体管的控制端连接所述第二耦合晶体管的第

一端,并连接到所述第一输入电路的第二输出端;所述第一耦合晶体管的第二端连接所述第二耦合晶体管的第二端,并连接到所述第一输入电路;

17.所述第一耦合晶体管和所述第二耦合晶体管为nmos或pmos;其中,

18.所述第一耦合晶体管,用于在采样阶段根据所述第一参考端电压对所述第一数据端电压正反馈,以得到所述第一数据端输出信号;

19.所述第二耦合晶体管,用于在采样阶段根据所述第一数据端电压对所述第一参考端电压正反馈,以得到所述第一参考端输出信号。

20.上述方案中,所述第二交叉耦合电路包括:第三耦合晶体管和第四耦合晶体管;所述第二差分信号包括:第二参考端输出信号和第二数据端输出信号;

21.所述第三耦合晶体管的第一端连接所述第四耦合晶体管的控制端,并连接到所述第二输入电路的第一输出端;所述第三耦合晶体管的控制端连接所述第四耦合晶体管的第一端,并连接到所述第二输入电路的第二输出端;所述第三耦合晶体管的第二端连接所述第四耦合晶体管的第二端,并连接到所述第二输入电路;

22.所述第三耦合晶体管和所述第四耦合晶体管为nmos或pmos;其中,

23.所述第三耦合晶体管,用于在采样阶段根据所述第二参考端电压对所述第二数据端电压正反馈,以得到所述第二数据端输出信号;

24.所述第四耦合晶体管,用于在采样阶段根据所述第二数据端电压对所述第二参考端电压正反馈,以得到所述第二参考端输出信号。

25.上述方案中,所述第一输入电路包括:第一输入晶体管、第二输入晶体管和第三输入晶体管;

26.所述第一输入晶体管的第一端和所述第二输入晶体管的第一端分别连接所述第二级电路;

27.所述第一输入晶体管的第二端和所述第二输入晶体管的第二端均与所述第三输入晶体管的第一端连接;

28.所述第一输入晶体管至第三输入晶体管为nmos或pmos;其中,

29.所述第一输入晶体管的控制端接收所述输入信号;所述第二输入晶体管的控制端接收所述第一参考信号;所述第三输入晶体管的控制端接收第一反馈信号;

30.当所述第三输入晶体管受到所述第一反馈信号触发为导通状态时,所述第一输入晶体管根据所述输入信号产生所述第一数据端电压,并作用于第二耦合晶体管的控制端;所述第二输入晶体管根据所述第一参考信号产生所述第一参考端电压,并作用于第一耦合晶体管的控制端。

31.上述方案中,所述第二输入电路包括:第四输入晶体管、第五输入晶体管和第六输入晶体管;

32.所述第四输入晶体管的第一端和所述第五输入晶体管的第一端分别连接所述第二级电路;

33.所述第四输入晶体管的第二端和所述第五输入晶体管的第二端均与所述第六输入晶体管的第一端连接;

34.所述第四输入晶体管至第六输入晶体管为nmos或pmos;其中,

35.所述第四输入晶体管的控制端接收所述输入信号;所述第五输入晶体管的控制端

接收所述第二参考信号;所述第六输入晶体管的控制端接收第二反馈信号;

36.当所述第六输入晶体管受到所述第二反馈信号触发为导通状态时,所述第四输入晶体管根据所述输入信号产生所述第二数据端电压,并作用于第四耦合晶体管的控制端;所述第五输入晶体管根据所述第二参考信号产生所述第二参考端电压,并作用于第三耦合晶体管的控制端。

37.上述方案中,所述比较器还包括:第一复位电路和时钟开关电路;

38.通过所述第一复位电路连接所述第一输入电路与所述第二输入电路;所述第一复位电路还连接所述电源端或所述接地端;

39.所述时钟开关电路连接所述第一输入电路与所述第二输入电路;所述时钟开关电路还连接所述接地端或所述电源端;其中,

40.所述第一复位电路,用于在复位阶段对所述第一输入电路和所述第二输入电路复位;

41.所述时钟开关电路,用于在时钟信号的触发下,控制所述比较器的导通。

42.上述方案中,所述第一复位电路包括:第一复位晶体管和第二复位晶体管;

43.所述第一复位晶体管的第一端和所述第二复位晶体管的第一端连接所述电源端或所述接地端;所述第一复位晶体管的第二端连接所述第一输入电路;所述第二复位晶体管的第二端连接所述第二输入电路;

44.所述第一复位晶体管和所述第二复位晶体管为pmos或nmos;其中,

45.所述第一复位晶体管和所述第二复位晶体管的控制端均接收所述时钟信号;

46.当所述时钟信号触发所述第一复位晶体管和所述第二复位晶体管为导通状态时,所述第一输入电路通过所述第一复位晶体管连接到所述电源端或所述接地端以复位,所述第二输入电路通过所述第二复位晶体管连接到所述电源端或所述接地端以复位。

47.上述方案中,所述时钟开关电路包括:时钟开关晶体管;

48.所述时钟开关晶体管的第一端连接所述第一输入电路和所述第二输入电路;所述时钟开关晶体管的第二端连接所述接地端或所述电源端;

49.所述时钟开关晶体管为nmos或pmos;其中,

50.所述时钟开关晶体管的控制端接收所述时钟信号;

51.当所述时钟开关晶体管在所述时钟信号的触发下处于导通状态时,所述第一输入电路和所述第二输入电路通过所述时钟开关晶体管连接到所述接地端或所述电源端,以导通所述比较器。

52.上述方案中,所述第二级电路包括:输出电路和第二复位电路;

53.所述第二复位电路连接所述输出电路;所述输出电路还连接所述电源端或所述接地端;所述第二复位电路还连接所述电源端或所述接地端;其中,

54.所述输出电路,用于在重生阶段对所述第一差分信号或所述第二差分信号进行放大处理和锁存处理,以输出比较结果;

55.所述第二复位电路,用于在复位阶段对所述输出电路复位。

56.上述方案中,所述第二复位电路包括:第三复位晶体管和第四复位晶体管;

57.所述第三复位晶体管的第一端和第四复位晶体管的第一端均连接所述电源端或所述接地端;所述第三复位晶体管的第二端和所述第四复位晶体管的第二端分别连接所述

输出电路;所述第三复位晶体管和所述第四复位晶体管为pmo s或nmos;其中,

58.所述第三复位晶体管和所述第四复位晶体管的控制端均接收所述时钟信号;

59.当所述时钟信号触发所述第三复位晶体管和所述第四复位晶体管为导通状态时,所述输出电路通过所述第三复位晶体管和所述第四复位晶体管连接到所述电源端或所述接地端以复位。

60.上述方案中,所述输出电路包括:第一输出晶体管、第二输出晶体管、第三输出晶体管、第四输出晶体管、第五输出晶体管和第六输出晶体管;

61.所述第一输出晶体管的控制端、所述第二输出晶体管的第一端、所述第三输出晶体管的控制端、所述第四输出晶体管的第二端和所述第六输出晶体管的第二端均连接到所述输出电路的第一输出端;

62.所述第一输出晶体管的第一端、所述第二输出晶体管的控制端、所述第三输出晶体管的第二端、所述第四输出晶体管的控制端和所述第五输出晶体管的第二端均连接到所述输出电路的第二输出端;

63.所述第一输出晶体管的第二端和所述第二输出晶体管的第二端分别连接所述第一输入电路、所述第二输入电路和所述第二复位电路;

64.所述第三输出晶体管的第一端、所述第四输出晶体管的第一端、所述第五输出晶体管的第一端和所述第六输出晶体管的第一端均连接所述电源端或所述接地端;

65.所述第一输出晶体管和所述第二输出晶体管为nmos或pmos;所述第三输出晶体管至第六输出晶体管为pmos或nmos;其中,

66.所述第五输出晶体管的控制端和所述第六输出晶体管的控制端均接收所述时钟信号。

67.上述方案中,所述第一参考信号的电压大于或小于所述第二参考信号的电压。

68.本技术实施例还提供一种判决反馈均衡电路,所述电路包括:n级如权利要求1至12中任意一项所述的比较器;其中,n为大于1的正整数;

69.每级比较器的第一输入端接收输入信号;所述每级比较器的第二输入端接收第一参考信号;所述每级比较器的第三输入端接收第二参考信号;

70.所述第1级比较器的第四输入端与所述第n级比较器的输出端连接,接收所述第n级比较器输出的第n级比较信号;所述第1级比较器的第五输入端接收第1时钟信号;

71.所述第i级比较器的第四输入端与所述第i

‑

1级比较器的输出端连接,接收所述第i

‑

1级比较器输出的第i

‑

1级比较信号;所述第i

‑

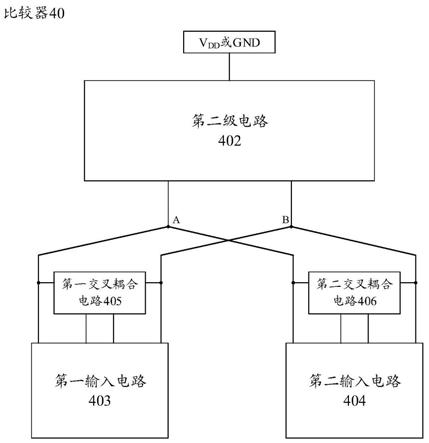

1级比较器的第五输入端接收第i时钟信号;其中,i大于1,且小于等于n;其中,

72.所述每级比较器在每级时钟信号的触发下,根据所述每级比较器的第四输入端对应的比较信号,将所述输入信号与所述第一参考信号进行比较,或者,将所述输入信号与第二参考信号进行比较,以输出每级比较信号。

73.上述方案中,所述第i时钟信号的相位比所述第i

‑

1时钟信号的相位晚360

°

/n。

74.上述方案中,当n=4时,所述第1级比较器的第四输入端与第4级比较器的输出端连接,接收所述第4级比较器输出的第4级比较信号;所述第1级比较器的第五输入端接收第1时钟信号。

75.上述方案中,所述判决反馈均衡电路还包括:n个锁存器;

76.每个锁存器的输入端对应连接每级比较器的输出端,以接收每级比较信号;

77.其中,

78.每个锁存器,用于将每级比较信号保存,以输出每级锁存信号。

79.由此可见,本技术实施例提供了一种比较器及判决反馈均衡电路,比较器包括:第二级电路、第一输入电路、第二输入电路、第一交叉耦合电路和第二交叉耦合电路。第一交叉耦合电路连接第一输入电路;第二交叉耦合电路连接第二输入电路;第一输入电路和第二输入电路还均与第二级电路连接;第二级电路连接电源端或接地端。其中,第一输入电路,用于在导通时的采样阶段根据输入信号和第一参考信号生成第一数据端电压和第一参考端电压;第一交叉耦合电路,用于将第一数据端电压和第一参考端电压相互正反馈,生成第一差分信号;第二输入电路,用于在导通时的采样阶段根据输入信号和第二参考信号生成第二数据端电压和第二参考端电压;第二交叉耦合电路,用于将第二数据端电压和第二参考端电压相互正反馈,生成第二差分信号;第二级电路,用于在重生阶段对第一差分信号或第二差分信号进行放大处理和锁存处理,以输出比较信号。这样,通过控制第一输入电路和第二输入电路的导通,在第一参考信号和第二参考信号中选用更合适的一个来和输入信号进行比较,从而消除码间串扰的影响;同时,第一交叉耦合电路和第二交叉耦合电路分别缩短了比较器在采样阶段生成第一差分信号和第二差分信号的时间,从而提高了比较器的工作速率。

附图说明

80.图1为相关技术方案中提供的一种比较器的结构示意图;

81.图2为相关技术方案中比较器的工作过程示意图;

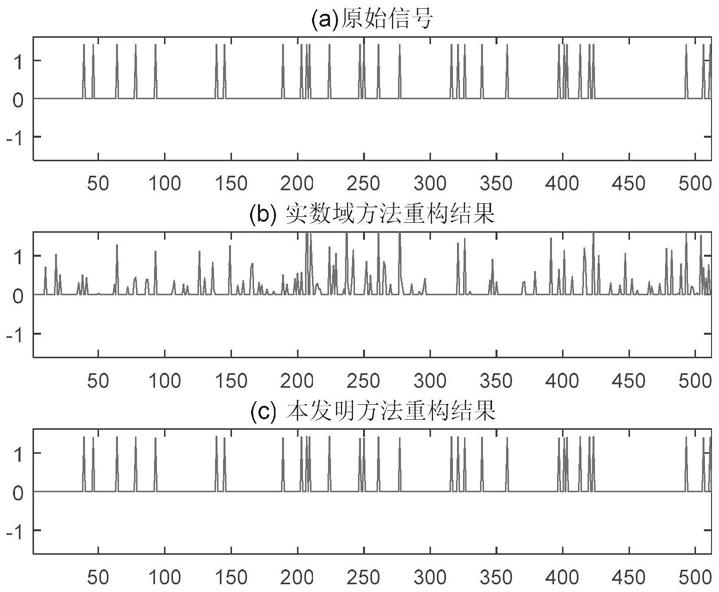

82.图3为相关技术方案中的码间干扰示意图;

83.图4为本技术实施例提供的一种比较器的结构示意图一;

84.图5为本技术实施例提供的一种比较器的结构示意图二;

85.图6为本技术实施例提供的一种比较器的结构示意图三;

86.图7为本技术实施例提供的一种比较器的结构示意图四;

87.图8为本技术实施例提供的一种比较器的结构示意图五;

88.图9为本技术实施例提供的一种判决反馈均衡电路的结构示意图一;

89.图10为本技术实施例提供的一种判决反馈均衡电路的结构示意图二;

90.图11为本技术实施例提供的一种判决反馈均衡电路的效果示意图一;

91.图12为本技术实施例提供的一种判决反馈均衡电路的效果示意图二;

92.图13为本技术实施例提供的一种判决反馈均衡电路的效果示意图三;

93.图14为本技术实施例提供的一种判决反馈均衡电路的效果示意图四。

具体实施方式

94.图1是相关技术中比较器的结构示意图,如图1所示,比较器10包括输入电路101、输出电路102和复位电路103。其中,输入电路101与输出电路102的输入端连接;复位电路103也与输出电路102连接。

95.输入电路101包括nmos(n

‑

metal

‑

oxide

‑

semiconductor,n型金属

‑

氧化物

‑

半导

体)晶体管n1、nmos晶体管n2以及nmos晶体管n3。其中,n1和n2的源极均连接n3的漏极;n3的源极连接接地端。n1的栅极作为比较器10的第一输入端inp,以接收输入信号;n2的栅极作为比较器10的第二输入端inn,以接收参考信号;n3的栅极接收时钟信号clk。n1和n2是产生与差分输入电平(即输入信号和参考信号)对应的差分电流的输入对。

96.输出电路102包括pmos(p

‑

metal

‑

oxide

‑

semiconductor,p型金属

‑

氧化物

‑

半导体)晶体管p1、pmos晶体管p2、nmos晶体管n4以及nmos晶体管n5。其中,p1的栅极、p2的漏极、n4的栅极和n5的漏极均连接到比较器10的第一输出端outp;p1的漏极、p2的栅极、n4的漏极和n5的栅极均连接到比较器10的第二输出端outn;p1的源极和p2的源极均连接电源端;n4的源极连接n1的漏极;n5的源极连接n2的漏极。

97.复位电路103包括pmos晶体管p3和pmos晶体管p4。其中,p3的漏极连接到比较器10的第二输出端outn;p4的漏极连接到比较器10的第一输出端outp;p3的源极和p4的源极均连接电源端。p3的栅极和p4的栅极分别接收时钟信号clk。

98.比较器10的工作过程分为四个阶段,分别为复位阶段、采样阶段、再生阶段以及决策阶段。图2是比较器10的一种工作时序图,下面结合图2描述比较器10的工作过程:

99.复位阶段,也就是t1时刻前。此时,时钟信号clk为低电平,n3被时钟信号clk触发为截止状态,输入电路101和输出电路102停止工作;同时,p3和p4被时钟信号clk触发为导通状态,复位电路103工作,将第一输出端outp和第二输出端outn的电压保持在高电平。

100.采样阶段,也就是t1时刻至t2时刻。在采样阶段开始时(即t1时刻),时钟信号clk变换为高电平,此时,p3和p4被时钟信号clk触发为截止状态,复位电路停止工作;同时,n3被时钟信号clk触发为导通状态,输入电路101和输出电路102工作,第一输入端inp采集输入信号,第二输入端inn采集参考信号。而后,第一输出端outp和第二输出端outn的电压因输入信号和参考信号的影响而逐渐降低为低电平。到采样阶段结束时(即t2时刻),p1被第一输出端outp的低电平触发为导通状态,p2被第二输出端outn的低电平触发为导通状态。

101.需要说明的是,在采样阶段,由于输入信号和参考信号的电压不同,使得第一输出端outp和第二输出端outn的电压降低的速率不同,从而使得第一输出端outp和第二输出端outn之间存在电压差。在图2中,由于输入信号高于参考信号,使得第二输出端outn的电压比第一输出端outp的电压降低得更快,第二输出端outn的电压低于第一输出端outp的电压。可以理解的是,当输入信号低于参考信号时,即第一输入端inp所采集的信号电压低于第二输入端inn时,第一输出端outp的电压会比第二输出端outn的电压降低得更快,第一输出端outp的电压会低于第二输出端outn的电压;反之,当输入信号高于参考信号时,即第一输入端inp所采集的信号电压高于第二输入端inn时,第一输出端outp的电压会高于第二输出端outn的电压。

102.再生阶段,也就是t2时刻至t3时刻。在再生阶段开始时(即t2时刻),p1和p2被触发为导通状态,由p1和p2组成的交叉耦合逆变器通过正反馈作用对第一输出端outp和第二输出端outn之间在采样阶段所形成的电压差进行放大。同时,n1和n2感测差分输入电平(即输入信号和参考信号)并产生差分漏极电流,对v

midp

和v

midn

进行充电,使其相对于输入极性具有大的信号摆幅。到再生阶段结束时(即t3时刻),第一输出端outp和第二输出端outn之间的电压差被放大到足够的程度,从而,第一输出端outp和第二输出端outn分别再生形成高电平和低电平。若输入信号高于参考信号,即如图2所示,第一输出端outp再生形成高电平,

第二输出端outn再生形成低电平;若输入信号低于参考信号,第一输出端outp再生形成低电平,第二输出端outn再生形成高电平。

103.决策阶段,也就是t3时刻至t4时刻。输出电路102对第一输出端outp和第二输出端outn的电平进行锁存,以对电平进行保持,并将锁存的电平作为比较信号以输出。

104.在下一个工作周期到来时(即t4时刻),时钟信号转换为低电平,n3被时钟信号clk触发为截止状态,输入电路101和输出电路102停止工作;同时,p3和p4被时钟信号clk触发为导通状态,复位电路103工作,将第一输出端outp和第二输出端outn的电压重新拉升到高电平。

105.由此可见,比较器的工作过程就是将输入信号与参考信号进行比较,若输入信号大于参考信号,则输出比较信号一;若输入信号小于参考信号,则输出与比较信号一反相的比较信号二;以此,对输入信号的电平高低进行判定。

106.需要说明的是,在比较器的运行过程中,存在码间串扰(inter

‑

symbol int erference,isi)。码间串扰是由于系统传输总特性不理想,导致前后时间节点信号的波形畸变、展宽,并使前面波形出现很长的拖尾,蔓延到当前时间节点信号的抽样时刻上,从而对当前时间节点信号的判决造成干扰。图3是码间串扰的示意图,如图3所示,信号1、信号2和信号3在其峰值后的波形都产生了很长的拖尾,经过了数个时间节点后才缓慢下降到0,因此,峰值后时间节点信号的判决受到了影响,原本被判决为低电平的码元可能会被判决为高电平。

107.在数字集成电路中,通常采用二进制数字信号“1”和“0”来实现其功能。比较器可以用于判定输入信号为数字信号“1”或是“0”。当输入信号的电平大于参考信号时,输入信号被判定为数字信号“1”(即高电平信号);当输入信号的电平小于参考信号时,输入信号被判定为数字信号“0”(即低电平信号)。那么,在前一个时间节点的输入信号为数字信号“1”时,由于其为高电平,会拉升后一个时间节点的实际输入信号的电平高于应有的电平;若此时后一个时间节点的输入信号为数字信号“0”,即应有的电平为低电平,则实际的电平可能被拉升至大于参考信号,从而被判定为数字信号“1”,造成信号失真。同理,在前一个时间节点的输入信号为数字信号“0”时,由于其为低电平,会降低后一个时间节点的实际输入信号的电平低于应有的电平;若此时后一个时间节点的输入信号为数字信号“1”,即应有的电平为高电平,则实际的电平可能被降低至小于参考信号,从而被判定为数字信号“0”,造成信号失真。

108.图4是本技术实施例提供的一种比较器的结构示意图,如图4所示,比较器40包括:第二级电路402、第一输入电路403、第二输入电路404、第一交叉耦合电路405和第二交叉耦合电路406。

109.第一交叉耦合电路405连接第一输入电路403;第二交叉耦合电路406连接第二输入电路404;第一输入电路403和第二输入电路404还均与第二级电路402连接;第二级电路402连接电源端v

dd

或接地端gnd。

110.需要说明的是,根据比较器40所采用的电子元件的不同,第二级电路402所连接的接地端或电源端会发生变化。当比较器40采用一种电子元件方案时,第二级电路402连接电源端。当比较器40采用另一种电子元件方案时,第二级电路402连接接地端。在此不做限制。

111.本技术实施例中,第一输入电路403接收输入信号dq和第一参考信号v

ref

_1,用于

在导通时的采样阶段根据输入信号dq和第一参考信号v

ref

_1生成第一数据端电压和第一参考端电压。第一交叉耦合电路405,用于将第一数据端电压和第一参考端电压相互正反馈,生成第一差分信号。第二输入电路404接收输入信号dq和第二参考信号v

ref

_2,用于在导通时的采样阶段根据输入信号dq和第二参考信号v

ref

_2生成第二数据端电压和第二参考端电压。第二交叉耦合电路406,用于将第二数据端电压和第二参考端电压相互正反馈,生成第二差分信号。第二级电路402,用于在重生阶段对第一差分信号或第二差分信号进行放大处理和锁存处理,以输出比较信号;其中,比较信号包括了第一比较子信号f

i

和第二比较子信号f

i

b,f

i

和f

i

b互为反相信号。

112.本技术实施例中,比较器40采用了两个不同的参考信号,即第一参考信号vref_1和第二参考信号vref_2。其中,v

ref

_1大于或小于v

ref

_2,对应的,本技术实施例所提供的比较器40可以采用两种电路方案。同时,v

ref

_1和vref_2均小于输入信号dq的高电平,且大于输入信号dq的低电平。两个参考信号vref_1和vref_2具体的电压可以根据实际需要设定,在此不做限制。

113.以比较器40采用v

ref

_1大于v

ref

_2对应的电路方案为例,当上一个时间节点的dq为高电平时,在当前时间节点的dq采样阶段,第一输入电路403受到第一反馈信号f

i

‑1触发而导通,第二输入电路404受到第一反馈信号f

i

‑1b触发而关断,采用v

ref

_1与dq进行比较;进而,若当前时间节点的dq为低电平,由于v

ref

_1较高,当前时间节点的dq被拉升后仍然不会大于v

ref

_1,仍可以被判定为数字信号“0”,信号不失真;若当前时间节点的dq为高电平,由于v

ref

_1小于dq的高电平,当前时间节点的dq在被拉升后仍然大于v

ref

_1,仍可以被判定为数字信号“1”,信号不失真。同理,当上一个时间节点的dq为低电平时,在当前时间节点的dq采样阶段,第一输入电路403受到第一反馈信号f

i

‑1触发而关断,第二输入电路404受到第一反馈信号f

i

‑1b触发而导通,采用v

ref

_2与当前时间节点的dq进行比较;进而,若当前时间节点的dq为高电平,由于v

ref

_2较低,当前时间节点的dq在被降低后仍然不会小于v

ref

_2,当前时间节点的dq仍被判定为数字信号“1”,信号不失真;若当前时间节点的dq为低电平,由于v

ref

_2大于dq的低电平,当前时间节点的dq在被降低后仍然小于v

ref

_2,仍被判定为数字信号“0”,信号不失真。

114.对应的,比较器40若采用v

ref

_1小于v

ref

_2的电路方案,那么,当上一个时间节点的dq为高电平时,在当前时间节点的dq采样阶段,第一输入电路403受到第一反馈信号f

i

‑1触发而关断,第二输入电路404受到第一反馈信号f

i

‑1b触发而导通,采用vref_2与当前时间节点的dq进行比较;当上一个时间节点的dq为低电平时,在当前时间节点的dq采样阶段,第一输入电路403受到第一反馈信号f

i

‑1触发而导通,第二输入电路404受到第一反馈信号f

i

‑1b触发而关断,采用第一参考信号vref_1与当前时间节点的dq进行比较。从而,保证当前时间节点的dq不失真。

115.本技术实施例中,第一交叉耦合电路405和第二交叉耦合电路406均连接了点a和点b。在比较器40的采样阶段中,若第一输入电路403导通,则第一交叉耦合电路405会根据此时的点a处电压(即第一数据端电压)对此时的点b处电压(即第一参考端电压)进行正反馈,同时,根据此时的点b处电压(即第一参考端电压)对此时的点a处电压(即第一数据端电压)进行正反馈,从而加快采样阶段点a处电压和点b处电压的变化速率,更快地得到第一差分信号,减少了采样阶段的时间消耗。对应的,在比较器40的采样阶段中,若第二输入电路

404导通,则第二交叉耦合电路406会根据此时的点a处电压(即第二数据端电压)对此时的点b处电压(即第二参考端电压)进行正反馈,同时,根据此时的点b处电压(即第二参考端电压)对此时的点a处电压(即第二数据端电压)进行正反馈,从而加快采样阶段点a处电压和点b处电压的变化速率,更快地得到第二差分信号,减少了采样阶段的时间消耗。

116.可以理解的是,本技术实施例所采用的比较器40能够根据上一个时间节点的输入信号,对应采用更合适的参考信号来与当前时间节点的输入信号进行比较,从而消除码间串扰带来的问题,使得比较结果不受码间串扰的影响,保证输入信号不失真。同时,第一交叉耦合电路405和第二交叉耦合电路406提高了比较器40在采样阶段中的电压变化速率,减少了采样阶段的时间消耗,从而提高了工作速率。

117.在本技术的一些实施例中,如图5所示,在比较器40中,第一输入电路403、第二输入电路404、第一交叉耦合电路405和第二交叉耦合电路406组成了第一级电路401;第一级电路401还包括:时钟开关电路407和第一复位电路408。

118.第一输入电路403与第二输入电路404通过第一复位电路408连接;第一复位电路408还连接电源端v

dd

或接地端gnd。时钟开关电路407连接第一输入电路403与第二输入电路404;时钟开关电路407还连接接地端gnd或电源端v

dd

。其中,时钟开关电路407和第一复位电路408均接收时钟信号。时钟开关电路407,用于在时钟信号的触发下,控制比较器40的导通,以进入采样阶段。第一复位电路408,用于在复位阶段对第一输入电路403和第二输入电路404复位。

119.本技术实施例中,在时钟信号的触发下,第一复位电路408可以在复位阶段将第一输入电路403的连接点c和第二输入电路404的连接点d分别与电源端v

dd

或接地端gnd导通,从而将连接点c和连接点d的电压拉升到高电平,以完成对第一输入电路403和第二输入电路404的复位。或者,在时钟信号的触发下,第一复位电路408可以在复位阶段将第一输入电路403的连接点c和第二输入电路404的连接点d分别与接地端导通,从而将连接点c和连接点d的电压降低到低电平,以完成对第一输入电路403和第二输入电路404的复位。

120.本技术实施例中,在时钟信号的触发下,时钟开关电路407可以在采样阶段将第一输入电路403和第二输入电路404分别与接地端gnd或电源端v

dd

导通,从而将比较器40导通,使比较器40开始运行。

121.需要说明的是,根据比较器40所采用的电子元件的不同,时钟开关电路407所连接的接地端或电源端,以及第一复位电路408所连接的电源端或接地端会发生变化。当比较器40采用一种电子元件方案时,时钟开关电路407连接接地端,第一复位电路408连接电源端;当比较器40采用另一种电子元件方案时,时钟开关电路407连接电源端,第一复位电路408连接接地端,在此不做限制。

122.可以理解的是,时钟开关电路407控制比较器40进入采样阶段,保证比较器40的正常运行。采用第一复位电路408对比较器40的局部电路进行复位,能够使比较器40更快地完成复位阶段,提高比较器40的运行速度。

123.在本技术的一些实施例中,如图5所示,第二级电路402包括:输出电路409和第二复位电路410。

124.第二复位电路410连接输出电路409;输出电路409还连接电源端v

dd

或接地端gnd;第二复位电路410还连接电源端v

dd

或接地端gnd。其中,输出电路409,用于在再生阶段对第

一差分信号或第二差分信号进行放大处理和锁存处理,以输出比较信号。第二复位电路410,接收时钟信号,用于根据时钟信号,在复位阶段对输出电路409复位。

125.需要说明的是,根据比较器40所采用的电子元件的不同,输出电路409和第二复位电路410所连接的电源端或接地端会发生变化。当比较器40采用一种电子元件方案时,输出电路409和第二复位电路410均连接电源端;当比较器40采用另一种电子元件方案时,输出电路409和第二复位电路410均连接接地端,在此不做限制。

126.本技术实施例中,在时钟信号的触发下,第二复位电路410可以将输出电路409的连接点a和连接点b分别与电源端导通,从而将连接点a和连接点b的电压拉升到高电平,以完成对输出电路409的复位。或者,在时钟信号wck的触发下,第二复位电路410可以将输出电路409的连接点a和连接点b分别与接地端导通,从而将连接点a和连接点b的电压降低到低电平,以完成对输出电路409的复位。

127.可以理解的是,采用第二复位电路410对比较器40的局部电路进行复位,能够使比较器40更快地完成复位阶段,提高比较器40的运行速度。

128.在本技术的一些实施例中,第一交叉耦合电路包括:第一耦合晶体管和第二耦合晶体管;第一差分信号包括:第一参考端输出信号和第一数据端输出信号;

129.第一耦合晶体管的第一端连接第二耦合晶体管的控制端,并连接到第一输入电路的第一输出端;第一耦合晶体管的控制端连接第二耦合晶体管的第一端,并连接到第一输入电路的第二输出端;第一耦合晶体管的第二端连接第二耦合晶体管的第二端,并连接到第一输入电路。第一耦合晶体管和第二耦合晶体管为nmos或pmos。其中,第一耦合晶体管,用于在采样阶段根据第一参考端电压对第一数据端电压正反馈,以得到第一数据端输出信号;第二耦合晶体管,用于在采样阶段根据第一数据端电压对第一参考端电压正反馈,以得到第一参考端输出信号。

130.本技术实施例中,第一耦合晶体管和第二耦合晶体管选用nmos还是pmos由比较器的电路结构决定。图7和图8分别示出了本技术实施例所提供的比较器的两种不同电路结构,下面结合图7和图8分别说明。

131.如图7所示,第一交叉耦合电路705包括第一耦合晶体管mn0和第二耦合晶体管mn1。mn0和mn1为nmos;nmos的栅极为控制端,其漏极为第一端,其源极为第二端。mn0的漏极连接mn1的栅极,并连接到第一输入电路703的第一输出端(即点a);mn0的栅极连接mn1的漏极,并连接到第一输入电路703的第二输出端(即点b);mn0的源极连接mn1的源极,并连接到第一输入电路703。在运行状态下,mn0根据其栅极电压(即第一参考端电压)的变化对其漏极电压(即第一数据端电压)正反馈,以加速其漏极电压的变化,最终得到采样阶段结束时的其漏极电压(即第一数据端输出信号);mn1根据其栅极电压(即第一数据端电压)的变化对其漏极电压(即第一参考端电压)正反馈,以加速其漏极电压的变化,最终得到采样阶段结束时的其漏极电压(即第一参考端输出信号)。

132.如图8所示,第一交叉耦合电路805包括第一耦合晶体管mp0和第二耦合晶体管mp1。mp0和mp1为pmos;pmos的栅极为控制端,其漏极为第一端,其源极为第二端。mp0的漏极连接mp1的栅极,并连接到第一输入电路803的第一输出端(即点a);mp0的栅极连接mp1的漏极,并连接到第一输入电路803的第二输出端(即点b);mp0的源极连接mp1的源极,并连接到第一输入电路803。在运行状态下,mp0根据其栅极电压(即第一参考端电压)的变化对其漏

极电压(即第一数据端电压)正反馈,以加速其漏极电压的变化,最终得到采样阶段结束时的其漏极电压(即第一数据端输出信号);mp1根据其栅极电压(即第一数据端电压)的变化对其漏极电压(即第一参考端电压)正反馈,以加速其漏极电压的变化,最终得到采样阶段结束时的其漏极电压(即第一参考端输出信号)。

133.在本技术的一些实施例中,第二交叉耦合电路包括:第三耦合晶体管和第四耦合晶体管;第二差分信号包括:第二参考端输出信号和第二数据端输出信号;

134.第三耦合晶体管的第一端连接第四耦合晶体管的控制端,并连接到第二输入电路的第一输出端;第三耦合晶体管的控制端连接第四耦合晶体管的第一端,并连接到第二输入电路的第二输出端;第三耦合晶体管的第二端连接第四耦合晶体管的第二端,并连接到第二输入电路。第三耦合晶体管和第四耦合晶体管为nmos或pmos。其中,第三耦合晶体管,用于在采样阶段根据第二参考端电压对第二数据端电压正反馈,以得到第二数据端输出信号;第四耦合晶体管,用于在采样阶段根据第二数据端电压对第二参考端电压正反馈,以得到第二参考端输出信号。

135.本技术实施例中,第三耦合晶体管和第四耦合晶体管选用nmos还是pmos由比较器的电路结构决定。图7和图8分别示出了本技术实施例所提供的比较器的两种不同电路结构,下面结合图7和图8分别说明。

136.如图7所示,第二交叉耦合电路706包括第三耦合晶体管mn2和第四耦合晶体管mn3。mn2和mn3为nmos;nmos的栅极为控制端,其漏极为第一端,其源极为第二端。mn2的漏极连接mn3的栅极,并连接到第二输入电路704的第一输出端(即点a);mn2的栅极连接mn3的漏极,并连接到第二输入电路704的第二输出端(即点b);mn2的源极连接mn3的源极,并连接到第二输入电路704。在运行状态下,mn2根据其栅极电压(即第二参考端电压)的变化对其漏极电压(即第二数据端电压)正反馈,以加速其漏极电压的变化,最终得到采样阶段结束时的其漏极电压(即第二数据端输出信号);mn3根据其栅极电压(即第二数据端电压)的变化对其漏极电压(即第二参考端电压)正反馈,以加速其漏极电压的变化,最终得到采样阶段结束时的其漏极电压(即第二参考端输出信号)。

137.如图8所示,第二交叉耦合电路806包括第三耦合晶体管mp2和第四耦合晶体管mp3。mp2和mp3为pmos;pmos的栅极为控制端,其漏极为第一端,其源极为第二端。mp2的漏极连接mp3的栅极,并连接到第二输入电路804的第一输出端(即点a);mp2的栅极连接mp3的漏极,并连接到第二输入电路804的第二输出端(即点b);mp2的源极连接mp3的源极,并连接到第二输入电路804。在运行状态下,mp2根据其栅极电压(即第二参考端电压)的变化对其漏极电压(即第二数据端电压)正反馈,以加速其漏极电压的变化,最终得到采样阶段结束时的其漏极电压(即第二数据端输出信号);mp3根据其栅极电压(即第二数据端电压)的变化对其漏极电压(即第二参考端电压)正反馈,以加速其漏极电压的变化,最终得到采样阶段结束时的其漏极电压(即第二参考端输出信号)。

138.在本技术的一些实施例中,第一输入电路包括:第一输入晶体管、第二输入晶体管和第三输入晶体管;

139.第一输入晶体管的第一端和第二输入晶体管的第一端分别连接第二级电路;第三输入晶体管的第二端连接接地端或电源端;第一输入晶体管的第二端和第二输入晶体管的第二端均与第三输入晶体管的第一端连接。第一输入晶体管至第三输入晶体管为nmos或

pmos。其中,第一输入晶体管的控制端接收输入信号;第二输入晶体管的控制端接收第一参考信号;第三输入晶体管的控制端接收第一反馈信号。当第三输入晶体管受到第一反馈信号触发为导通状态时,第一输入晶体管根据输入信号产生第一数据端电压,并作用于第二耦合晶体管的控制端;第二输入晶体管根据第一参考信号产生第一参考端电压,并作用于第一耦合晶体管的控制端。

140.本技术实施例中,第一输入晶体管、第二输入晶体管和第三输入晶体管选用nmos还是pmos由比较器的电路结构决定。图7和图8分别示出了本技术实施例所提供的比较器的两种不同电路结构,下面结合图7和图8分别说明。

141.如图7所示,比较器70中包括了第一输入电路703;第一输入电路703包括:第一输入晶体管mn4、第二输入晶体管mn5和第三输入晶体管mn6。mn4、mn5和mn6为nmos;nmos的栅极为控制端,其漏极为第一端,其源极为第二端。mn4的漏极在连接点a与第二级电路702连接,mn5的漏极在连接点b与第二级电路702连接。mn6的源极连接时钟开关电路707。mn4的源极和mn5的源极均与mn6的漏极连接。mn4的栅极接收输入信号dq;mn5的栅极接收第一参考信号v

ref

_p;mn6的栅极接收第一反馈信号f

i

‑1。在运行状态下,当时钟信号wck_i变换为高电平时,即比较器70进入采样阶段时,若第一反馈信号f

i

‑1为高电平,则mn6被f

i

‑1触发为导通状态,第一输入电路703被导通。进而,mn4根据所接收到的dq,将点a处的电压变化,得到第一数据端电压,并作用于第二耦合晶体管mn1的栅极;mn5根据所接收到的v

ref

_p将点b处的电压变化,得到第一参考端电压,并作用于第一耦合晶体管mn0的栅极。

142.如图8所示,比较器80中包括了第一输入电路803;第一输入电路803包括:第一输入晶体管mp4、第二输入晶体管mp5和第三输入晶体管mp6。mp4、mp5和mp6为pmos;pmos的栅极为控制端,其漏极为第一端,其源极为第二端。mp4的漏极在连接点a与第二级电路802连接,mp5的漏极在连接点b与第二级电路802连接。mp6的源极连接时钟开关电路807。mp4的源极和mp5的源极均与mp6的漏极连接。mp4的栅极接收输入信号dq;mp5的栅极接收第一参考信号v

ref

_n;mp6的栅极接收第一反馈信号f

i

‑1。在运行状态下,当时钟信号wck_ib变换为低电平时,即比较器80进入采样阶段时,若第一反馈信号f

i

‑1为低电平,则mp6被f

i

‑1触发为导通状态,第一输入电路803被导通。进而,mp4根据所接收到的dq,将点a处的电压变化,得到第一数据端电压,并作用于第二耦合晶体管mp1的栅极;mp5根据所接收到的v

ref

_n将点b处的电压变化,得到第一参考端电压,并作用于第一耦合晶体管mp0的栅极。

143.需要说明的是,v

ref

_p和v

ref

_n用于表示两个参考信号之间的大小关系:v

ref

_p大于v

ref

_n。在图7示出的比较器70中,由于第一参考信号大于第二参考信号,因此,第一参考信号采用v

ref

_p,第二参考信号采用v

ref

_n。在图8示出的比较器80中,由于第一参考信号小于第二参考信号,因此,第一参考信号采用v

ref

_n,第二参考信号采用v

ref

_p。

144.在本技术的一些实施例中,第二输入电路包括:第四输入晶体管、第五输入晶体管和第六输入晶体管;

145.第四输入晶体管的第一端和第五输入晶体管的第一端分别连接第二级电路;第四输入晶体管的第二端和第五输入晶体管的第二端均与第六输入晶体管的第一端连接。第四输入晶体管至第六输入晶体管为nmos或pmos。其中,第四输入晶体管的控制端接收输入信号;第五输入晶体管的控制端接收第二参考信号;第六输入晶体管的控制端接收第二反馈信号。当第六输入晶体管受到第二反馈信号触发为导通状态时,第四输入晶体管根据输入

信号产生第二数据端电压,并作用于第四耦合晶体管的控制端;第五输入晶体管根据第二参考信号产生第二参考端电压,并作用于第三耦合晶体管的控制端。

146.本技术实施例中,第四输入晶体管、第五输入晶体管和第六输入晶体管选用nmos还是pmos由比较器的电路结构决定。图7和图8分别示出了本技术实施例所提供的比较器的两种不同电路结构,下面结合图7和图8分别说明。

147.如图7所示,比较器70中包括了第二输入电路704;第二输入电路704包括:第四输入晶体管mn7、第五输入晶体管mn8和第六输入晶体管mn9。mn7、mn8和mn9为nmos;nmos的栅极为控制端,其漏极为第一端,其源极为第二端。mn7的漏极在连接点a与第二级电路702连接,mn8的漏极在连接点b与第二级电路702连接。mn9的源极连接时钟开关电路707。mn7的源极和mn8的源极均与mn9的漏极连接。mn7的栅极接收输入信号dq;mn8的栅极接收第二参考信号v

ref

_n;mn9的栅极接收第二反馈信号f

i

‑1b,第二反馈信号f

i

‑1b与第一反馈信号f

i

‑1互为反相信号。在运行状态下,当时钟信号wck_i变换为高电平时,即比较器70进入采样阶段时,若第一反馈信号f

i

‑1为低电平,则第二反馈信号f

i

‑1b为高电平,mn9被f

i

‑1b触发为导通状态,第二输入电路704被导通。进而,mn7根据所接收到的dq,将点a处的电压变化,得到第二数据端电压,并作用于第四耦合晶体管mn3的栅极;mn8根据所接收到的v

ref

_n将点b处的电压变化,得到第二参考端电压,并作用于第三耦合晶体管mn2的栅极。

148.如图8所示,比较器80中包括了第二输入电路804;第二输入电路804包括:第四输入晶体管mp7、第五输入晶体管mp8和第六输入晶体管mp9。mp7、mp8和mp9为pmos;pmos的栅极为控制端,其漏极为第一端,其源极为第二端。

149.mp7的漏极在连接点a与第二级电路802连接,mp8的漏极在连接点b与第二级电路802连接。mp9的源极连接时钟开关电路807。mp7的源极和mp8的源极均与mp9的漏极连接。mp7的栅极接收输入信号dq;mp8的栅极接收第二参考信号v

ref

_p;mp9的栅极接收第二反馈信号f

i

‑1b,第二反馈信号f

i

‑1b与第一反馈信号f

i

‑1互为反相信号。在运行状态下,当时钟信号wck_ib变换为低电平时,即比较器80进入采样阶段时,若第一反馈信号f

i

‑1为高电平,则第二反馈信号f

i

‑1b为低电平,mp9被f

i

‑1b触发为导通状态,第二输入电路804被导通。进而,mp7根据所接收到的dq,将点a处的电压变化,得到第二数据端电压,并作用于第四耦合晶体管mp3的栅极;mp8根据所接收到的v

ref

_p将点b处的电压变化,得到第二参考端电压,并作用于第三耦合晶体管mp2的栅极。

150.需要说明的是,v

ref

_p和v

ref

_n用于表示两个参考信号之间的大小关系:v

ref

_p大于v

ref

_n。在图7示出的比较器70中,由于第一参考信号大于第二参考信号,因此,第一参考信号采用v

ref

_p,第二参考信号采用v

ref

_n。在图8示出的比较器80中,由于第一参考信号小于第二参考信号,因此,第一参考信号采用v

ref

_n,第二参考信号采用v

ref

_p。

151.在本技术的一些实施例中,第一复位电路包括:第一复位晶体管和第二复位晶体管。

152.第一复位晶体管的第一端和第二复位晶体管的第一端均连接电源端或接地端;第一复位晶体管的第二端连接第一输入电路;第二复位晶体管的第二端连接第二输入电路。第一复位晶体管和第二复位晶体管为pmos或nmos。其中,第一复位晶体管和第二复位晶体管的控制端均接收时钟信号。当时钟信号触发第一复位晶体管和第二复位晶体管为导通状态时,第一输入电路通过第一复位晶体管连接到电源端或接地端以复位,第二输入电路通

过第二复位晶体管连接到电源端或接地端以复位。

153.本技术实施例中,第一复位晶体管和第二复位晶体管选用pmos还是nmos由比较器的电路结构决定。图7和图8分别示出了本技术实施例所提供的比较器的两种不同电路结构,下面结合图7和图8分别说明。

154.如图7所示,比较器70中包括了第一复位电路708;第一复位电路708包括:第一复位晶体管mp5和第二复位晶体管mp6。mp5和mp6为pmos;pmos的栅极为控制端,其源极为第一端,其漏极为第二端。mp5的源极和mp6的源极均连接电源端;mp5的漏极连接第一输入电路703;mp6的漏极连接第二输入电路704。mp5和mp6的栅极均接收时钟信号wck_i。在运行状态下,当时钟信号wck_i变换为低电平时,即比较器70进入复位阶段时,mp5和mp6被wck_i触发为导通状态;第一输入电路703和第二输入电路704分别通过mp5和mp6连接到电源端,其各自连接点的电压由于被连接到电源端而被拉升至高电平,从而完成了第一输入电路703和第二输入电路704的复位。

155.如图8所示,比较器80中包括了第一复位电路808;第一复位电路808包括:第一复位晶体管mn5和第二复位晶体管mn6。mn5和mn6为nmos;nmos的栅极为控制端,其漏极为第一端,其源极为第二端。mn5的漏极和mn6的漏极均连接接地端;mn5的源极连接第一输入电路803;mn6的源极连接第二输入电路804。mn5和mn6的栅极均接收时钟信号wck_ib。在运行状态下,当时钟信号wck_ib变换为高电平时,即比较器80进入复位阶段时,mn5和mn6被wck_ib触发为导通状态;第一输入电路803和第二输入电路804分别通过mn5和mn6连接到接地端,其各自连接点的电压由于被连接到接地端而被降低至低电平,从而完成了第一输入电路803和第二输入电路804的复位。

156.在本技术的一些实施例中,时钟开关电路包括:时钟开关晶体管;

157.时钟开关晶体管的第一端连接第一输入电路和第二输入电路;时钟开关晶体管的第二端连接接地端或电源端。时钟开关晶体管为nmos或pmos。其中,时钟开关晶体管的控制端接收时钟信号;当时钟开关晶体管在时钟信号的触发下处于导通状态时,第一输入电路和第二输入电路通过时钟开关晶体管连接到接地端或电源端,以导通比较器。

158.本技术实施例中,时钟开关晶体管选用nmos还是pmos由比较器的电路结构决定。图7和图8分别示出了本技术实施例所提供的比较器的两种不同电路结构,下面结合图7和图8分别说明。

159.如图7所示,比较器70中包括了时钟开关电路707;时钟开关电路707包括:时钟开关晶体管mn10。mn10为nmos;nmos的栅极为控制端,其漏极为第一端,其源极为第二端。mn10的漏极连接第一输入电路703和第二输入电路704;mn10的源极连接接地端;mn10的栅极接收时钟信号wck_i。在运行状态下,wck_i变换为高电平时,mn10在wck_i的触发下处于导通状态,第一输入电路703和第二输入电路704通过mn10连接到接地端,比较器70被导通进入采样阶段。

160.如图8所示,比较器80中包括了时钟开关电路807;时钟开关电路807包括:时钟开关晶体管mp10。mp10为pmos;pmos的栅极为控制端,其漏极为第一端,其源极为第二端。mp10的漏极连接第一输入电路803和第二输入电路804;mp10的源极连接电源端;mp10的栅极接收时钟信号wck_ib。在运行状态下,wck_ib变换为低电平时,mp10在wck_ib的触发下处于导通状态,第一输入电路803和第二输入电路804通过mp10连接到电源端,比较器80被导通进

入采样阶段。

161.在本技术的一些实施例中,第二复位电路包括:第三复位晶体管和第四复位晶体管。

162.第三复位晶体管的第一端和第四复位晶体管的第一端均连接电源端或接地端;第三复位晶体管的第二端和第四复位晶体管的第二端分别连接输出电路。第三复位晶体管和第四复位晶体管为pmos或nmos。其中,第三复位晶体管和第四复位晶体管的控制端均接收时钟信号。当时钟信号触发第三复位晶体管和第四复位晶体管为导通状态时,输出电路通过第三复位晶体管和第四复位晶体管连接到电源端或接地端以复位。

163.本技术实施例中,第三复位晶体管和第四复位晶体管选用pmos还是nmos由比较器的电路结构决定。图7和图8分别示出了本技术实施例所提供的比较器的两种不同电路结构,下面结合图7和图8分别说明。

164.如图7所示,比较器70中包括了第二复位电路710;第二复位电路710包括:第三复位晶体管mp7和第四复位晶体管mp8。mp7和mp8为pmos;pmos的栅极为控制端,其源极为第一端,其漏极为第二端。mp7的源极和mp8的源极均连接电源端;mp7的漏极经过连接点a连接输出电路,mp8的漏极经过连接点b连接输出电路。mp7和mp8的栅极均接收时钟信号wck_i。在运行状态下,当时钟信号wck_i变换为低电平时,即比较器70进入复位阶段时,mp7和mp8被wck_i触发为导通状态;输出电路709分别经过连接点a和连接点b被连接到电源端,连接点a和连接点b的电压由于被连接到电源端而被拉升至高电平,从而完成了输出电路709的复位。

165.如图8所示,比较器80中包括了第二复位电路810;第二复位电路810包括:第三复位晶体管mn7和第四复位晶体管mn8。mn7和mn8为nmos;nmos的栅极为控制端,其源极为第一端,其漏极为第二端。mn7的源极和mn8的源极均连接接地端;mn7的漏极经过连接点a连接输出电路,mn8的漏极经过连接点b连接输出电路。mn7和mn8的栅极均接收时钟信号wck_ib。在运行状态下,当时钟信号wck_ib变换为高电平时,即比较器80进入复位阶段时,mn7和mn8被wck_ib触发为导通状态;输出电路809分别经过连接点a和连接点b被连接到接地端,连接点a和连接点b的电压由于被连接到接地端而被降低至低电平,从而完成了输出电路809的复位。

166.在本技术的一些实施例中,输出电路包括:第一输出晶体管、第二输出晶体管、第三输出晶体管、第四输出晶体管、第五输出晶体管和第六输出晶体管。

167.第一输出晶体管的控制端、第二输出晶体管的第一端、第三输出晶体管的控制端、第四输出晶体管的第二端和第六输出晶体管的第二端均连接到输出电路的第一输出端。第一输出晶体管的第一端、第二输出晶体管的控制端、第三输出晶体管的第二端、第四输出晶体管的控制端和第五输出晶体管的第二端均连接到输出电路的第二输出端。第一输出晶体管的第二端和第二输出晶体管的第二端分别连接第一输入电路、第二输入电路和第二复位电路。第三输出晶体管的第一端、第四输出晶体管的第一端、第五输出晶体管的第一端和第六输出晶体管的第一端均连接电源端或接地端。第一输出晶体管和第二输出晶体管为nmos或pmos;第三输出晶体管至第六输出晶体管为pmos或nmos。其中,第五输出晶体管的控制端和第六输出晶体管的控制端均接收时钟信号。

168.本技术实施例中,第一输出晶体管和第二输出晶体管选用nmos还是pmos,第三输

出晶体管至第六输出晶体管选用pmos还是nmos,均由比较器的电路结构决定。图7和图8分别示出了本技术实施例所提供的比较器的两种不同电路结构,下面结合图7和图8分别说明。

169.如图7所示,比较器70中包括了输出电路709;输出电路709包括:第一输出晶体管mn10、第二输出晶体管mn11、第三输出晶体管mp1、第四输出晶体管mp2、第五输出晶体管mp3和第六输出晶体管mp4。mn10和mn11为nmos;nmos的栅极为控制端,其漏极为第一端,其源极为第二端。mp1、mp2、mp3和mp4为pmos;pmos的栅极为控制端,其源极为第一端,其漏极为第二端。mn10的栅极、mn11的漏极、mp1的栅极、mp2的漏极和mp4的漏极均连接到输出电路709的第一输出端,输出电路709的第一输出端输出比较信号中的f

i

信号。mn10的漏极、mn11的栅极、mp1的漏极、mp2的栅极和mp3的漏极均连接到输出电路709的第二输出端,输出电路709的第二输出端输出比较信号中的f

i

b信号,f

i

b为f

i

的反相信号。mn10的源极经过连接点a连接了第一输入电路703、第二输入电路704和第二复位电路710;mn11的源极经过连接点b连接了第一输入电路703、第二输入电路704和第二复位电路710。mp1的源极、mp2的源极、mp3的源极和mp4的源极均连接电源端。mp3的栅极和mp4的栅极均接收时钟信号wck_i。

170.在时钟信号wck_i为低电平时,即在比较器70的复位阶段,mp3和mp4被wck_i触发保持为导通状态,此时,第一输出端和第二输出端的电压保持在高电平。当时钟信号wck_i变换为高电平时,即比较器70的采样阶段开始时,mp3和mp4被wck_i触发变换为截止状态,此时,输出电路709接收到的第一差分信号或者第二差分信号;第一输出端和第二输出端的电压受到第一差分信号或者第二差分信号的影响开始逐渐降低为低电平,直至触发mp1和mp2变换为导通状态,则比较器70的采样阶段结束,再生阶段开始。在比较器70的再生阶段开始时,由mp1和mp2组成的交叉耦合逆变器通过正反馈作用对第一输出端和第二输出端之间在采样阶段所形成的电压差进行放大;直至电压差被放大到足够的程度时,输出电路709对第一输出端和第二输出端的电压进行锁存,并将锁存的电平作为比较信号以输出,即输出f

i

和f

i

b。

171.如图8所示,比较器80中包括了输出电路809;输出电路809包括:第一输出晶体管mp10、第二输出晶体管mp11、第三输出晶体管mn1、第四输出晶体管mn2、第五输出晶体管mn3和第六输出晶体管mn4。mp10和mp11为pmos;pmos的栅极为控制端,其漏极为第一端,其源极为第二端。mn1、mn2、mn3和mn4为nmos;nmos的栅极为控制端,其源极为第一端,其漏极为第二端。mp10的栅极、mp11的漏极、mn1的栅极、mn2的漏极和mn4的漏极均连接到输出电路809的第一输出端,输出电路809的第一输出端输出比较信号中的f

i

信号。mp10的漏极、mp11的栅极、mn1的漏极、mn2的栅极和mn3的漏极均连接到输出电路809的第二输出端,输出电路809的第二输出端输出比较信号中的f

i

b信号,f

i

b为f

i

的反相信号。mp10的源极经过连接点a连接了第一输入电路803、第二输入电路804和第二复位电路810;mp11的源极经过连接点b连接了第一输入电路803、第二输入电路804和第二复位电路810。mn1的源极、mn2的源极、mn3的源极和mn4的源极均连接接地端。mn3的栅极和mn4的栅极均接收时钟信号wck_ib。

172.在时钟信号wck_ib为高电平时,即在比较器80的复位阶段,mn3和mn4被wck_ib触发保持为导通状态,此时,第一输出端和第二输出端的电压保持在低电平。当时钟信号wck_ib变换为低电平时,即比较器80的采样阶段开始时,mn3和mn4被wck_ib触发变换为截止状态,此时,输出电路809接收到的第一差分信号或者第二差分信号;第一输出端和第二输出

端的电压受到第一差分信号或者第二差分信号的影响开始逐渐拉升为高电平,直至触发mn1和mn2变换为导通状态,则比较器80的采样阶段结束,再生阶段开始。在比较器80的再生阶段开始时,由mn1和mn2组成的交叉耦合逆变器通过正反馈作用对第一输出端和第二输出端之间在采样阶段所形成的电压差进行放大;直至电压差被放大到足够的程度时,输出电路809对第一输出端和第二输出端的电压进行锁存,并将锁存的电平作为比较信号以输出,即输出fi和fib。

173.图9是本技术实施例提供的一种判决反馈均衡电路的结构示意图,如图9所示,判决反馈均衡电路90中包括n级如上述实施例中的比较器;其中,n为大于1的正整数。

174.每级比较器的第一输入端接收输入信号dq;每级比较器的第二输入端接收第一参考信号v

ref

_1;每级比较器的第三输入端接收第二参考信号v

ref

_2。

175.第1级比较器901的第四输入端与第n级比较器904的输出端连接,接收第n级比较器904输出的第n级比较信号f

n

/f

n

b;第1级比较器901的第五输入端接收第1时钟信号wck_1。

176.第i级比较器903的第四输入端与第i

‑

1级比较器902的输出端连接,接收第i

‑

1级比较器902输出的第i

‑

1级比较信号f

i

‑1/f

i

‑1b;第i级比较器903的第五输入端接收第i时钟信号wck_i;其中,i大于1,且小于等于n。

177.每级比较器在每级时钟信号的触发下,根据每级比较器的第四输入端对应的比较信号,将输入信号dq与第一参考信号v

ref

_1进行比较,或者,将输入信号dq与第二参考信号v

ref

_2进行比较,以输出每级比较信号。

178.本技术实施例中,判决反馈均衡电路90中的每级比较器均具有五个输入端和一个输出端;每级比较器的五个输入端依次分别接收输入信号dq、第一参考信号v

ref

_1、第二参考信号v

ref

_2、上一级比较信号(第1级比较器则接收第n级比较信号)以及每级比较器对应的时钟信号;每级比较器的输出端则输出每级比较信号。

179.本技术实施例中,每级比较信号中包含了两个互为反相的信号,这两个互为反相的信号分别作为上述实施例中的第一反馈信号和第二反馈信号,以输入下一级比较器中(第1级比较器则接收第n级比较信号),例如,f

i

‑1和f

i

‑1b互为反相信号,f

i

‑1作为第一反馈信号输入第i级比较器,f

i

‑1b作为第二反馈信号输入第i级比较器。这样,可以根据每级比较器的输出结果,控制下一级比较器在采样阶段选择第一参考信号v

ref

_1还是第二参考信号v

ref

_2。

180.本技术实施例中,第i时钟信号wck_i的相位比第i

‑

1时钟信号wck_i

‑

1的相位晚360

°

/n,即每级比较器对应的时钟信号的相位比上一级比较器晚n分之一时钟周期,如此,第1时钟信号wck_1的相位则比第n时钟信号wck_n的相位同样晚了n分之一时钟周期。这样,由于比较器进入采样阶段受到时钟信号控制,因此,各时钟信号间的相位延迟,会使得各级比较器依次在各时间节点进入采样阶段,即各级比较器依次对输入信号dq在一个时钟周期中的各时间节点上的电平进行采样,并输出各级比较信号,其中,各时间节点之间依次间隔n分之一时钟周期。也就是说,判决反馈均衡电路90中的各级比较器依次获取了输入信号dq的码元。

181.例如,第i

‑

1级比较器902受第i

‑

1时钟信号wck_i

‑

1控制在第i

‑

1时间节点进入采样阶段,对输入信号dq在第i

‑

1时间节点的电平进行采样,并输出了第i

‑

1级比较信号f

i

‑1/f

i

‑1b;则在第i

‑

1时间节点之后n分之一时钟周期的第i时间节点,第i级比较器903受第i时

钟信号wck_i控制进入采样阶段,对输入信号dq在第i时间节点的电平进行采样,并输出第i级比较信号f

i

/f

i

b;依次类推,到第n时间节点,第n级比较器904受第n时钟信号wck_n控制进入采样阶段,对输入信号dq在第n时间节点的电平进行采样,并输出第n级比较信号;而在第n时间节点之后,则进入了下一个时钟周期,在第n时间节点之后n分之一时钟周期的第n 1时间节点,重新由第1级比较器进入采样阶段对输入信号的电平进行采样。

182.如此,每级比较器所接收到的上一级比较信号,反映了前一个时间节点输入信号dq的电平。以第i级比较器为例,第i级比较器会在第i时间节点对dq进行采样,而其接收到f

i

‑1/f

i

‑1b信号则反映了第i

‑

1时间节点dq的电平。由于码间串扰的存在,第i

‑

1时间节点dq的电平会对第i时间节点dq的电平产生干扰,而第i级比较器则可以将所接收到的f

i

‑1/f

i

‑1b信号作为第一反馈信号和第二反馈信号,根据f

i

‑1/f

i

‑1b信号在两个参考信号中对应选择合适的参考信号与第i时间节点dq的电平进行比较;具体而言,当第i

‑

1时间节点dq的电平为高电平时,则选择电平较高的参考信号进行比较,当第i

‑

1时间节点dq的电平为低电平时,则选择电平较低的参考信号进行比较;从而消除码间串扰的影响。

183.需要说明的是,判决反馈均衡电路90采用上述实施例中的比较器时,需要根据所采用比较器的电路结构进行相应的调整。当判决反馈均衡电路90采用图7示出的比较器70作为第i级比较器时,可以将第一参考信号v

ref

_1设定为电平相对较高的参考信号v

ref

_p,将第二参考信号v

ref

_2设定为电平相对较低的参考信号v

ref

_n,输入时钟信号wck_i;而当判决反馈均衡电路90采用图8示出的比较器80作为第i级比较器时,若要达到与比较器70相同的效果,则需要将第一参考信号v

ref

_1设定为电平相对较低的参考信号v

ref

_n,将第二参考信号v

ref

_2设定为电平相对较高的参考信号v

ref

_p,并输入与wck_i反相的时钟信号wck_ib。也即是说,图7示出的比较器70和图8示出的比较器80可以在判决反馈均衡电路90中互相等效替换。

184.可以理解的是,图9示出的判决反馈均衡电路90能够采用多级比较器对输入信号dq在各个时间节点进行采样,每级比较器在对一个时间节点的dq进行采样时,能够依据dq在上一个时间节点的电平对应选择合适的参考信号,从而消除了码间串扰的影响,提高了输出结果的准确性。

185.在本技术的一些实施例中,如图9所示,判决反馈均衡电路90还包括:n个锁存器。

186.每个锁存器的输入端对应连接每级比较器的输出端,以接收每级比较信号;其中,每个锁存器,用于将每级比较信号保存,以输出每级锁存信号。

187.本技术实施例中,判决反馈均衡电路90所包括的每个锁存器,受到触发后,会接收每级比较信号,并将每级比较信号保存并输出。例如,第i锁存器907,受到触发后,会接收第i级比较信号f

i

/f

i

b,并将f

i

/f

i

b保存,并输出锁存信号d

i

。

188.在本技术的一些实施例中,如图10所示,当n=4时,判决反馈均衡电路100中包括4级如上述实施例中的比较器:第1级比较器1001、第2级比较器1002、第3级比较器1003和第4级比较器1004。

189.每级比较器的第一输入端接收输入信号dq;每级比较器的第二输入端接收第一参考信号v

ref

_1;每级比较器的第三输入端接收第二参考信号v

ref

_2。

190.第1级比较器1001的第四输入端与第4级比较器1004的输出端连接,接收第4级比较器1004输出的第4级比较信号f4/f4b;第1级比较器1001的第五输入端接收第1时钟信号

wck_1。

191.第2级比较器1002的第四输入端与第1级比较器1001的输出端连接,接收第1级比较器1001输出的第1级比较信号f1/f1b;第2级比较器1002的第五输入端接收第2时钟信号wck_2。

192.第3级比较器1003的第四输入端与第2级比较器1002的输出端连接,接收第2级比较器1002输出的第2级比较信号f2/f2b;第3级比较器1003的第五输入端接收第3时钟信号wck_3。

193.第4级比较器1004的第四输入端与第3级比较器1003的输出端连接,接收第3级比较器1003输出的第3级比较信号f3/f3b;第4级比较器1004的第五输入端接收第4时钟信号wck_4。

194.每级比较器在每级时钟信号的触发下,根据每级比较器的第四输入端对应的比较信号,将输入信号dq与第一参考信号v

ref

_1进行比较,或者,将输入信号dq与第二参考信号v

ref

_2进行比较,以输出每级比较信号。

195.本技术实施例中,每级比较器对应的时钟信号的相位比上一级比较器晚90

°

(即四分之一时钟周期)。因此,各级比较器依次对输入信号dq在一个时钟周期中的各时间节点上的电平进行采样,并输出各级比较信号,其中,各时间节点之间依次间隔四分之一时钟周期。每级比较器根据前一个时间节点dq的电平,在两个参考信号中对应选择合适的参考信号与当前时间节点dq的电平进行比较,从而消除码间串扰的影响。

196.在本技术的一些实施例中,如图10所示,判决反馈均衡电路100还包括:4个锁存器:第1锁存器1005、第2锁存器1006、第3锁存器1007和第4锁存器1008。

197.每个锁存器的输入端对应连接每级比较器的输出端,以接收每级比较信号;其中,每个锁存器,用于将每级比较信号保存,以输出每级锁存信号。

198.本技术实施例中,判决反馈均衡电路100所包括的每个锁存器,受到触发后,会接收每级比较信号,并将每级比较信号保存并输出。

199.图11至图14为本技术提供的判决反馈均衡电路(dfe)的效果示意图。

200.如图11所示,未使用dfe时,信号在时间节点0的电压对时间节点1和时间节点2的电压造成了码间串扰,时间节点1和时间节点2的低电平被拉高,无法采样到准确的电压;而在时间节点1和时间节点2使用dfe后,所采样的电压受到dfe的补偿,被降低到原有的低电平,从而消除了码间串扰的影响。

201.如图12所示,在时间节点1

‑

4使用dfe后,将信号由原本的虚线部分拉低到实线部分,消除了前时间节点的高电平所带来码间串扰的影响。

202.图13和图14分别示出了未使用dfe和使用dfe这两种情况下的眼图(eye diagram)。眼图是将扫描所得的每一个码元波形重叠在一起而形成的,从眼图上可以观察出码间串扰和噪声的影响。眼图中的“眼睛”张的越大,且眼图越端正,表示码间串扰越小;反之表示码间串扰越大。未使用dfe时,如图13所示,眼图中的“眼睛”已经无法看见,每一个码元波形相互串扰而没有明显的界限,码间串扰很严重,这样,容易造成码元判决失误。而使用dfe后,如图14所示,眼图中形成了清晰的“眼睛”,各码元波形有清晰的界限,码间串扰的影响被消除,这样,码元判决会更加准确。

203.需要说明的是,在本技术中,术语“包括”、“包含”或者其任何其他变体意在涵盖非

排他性的包含,从而使得包括一系列要素的过程、方法、物品或者装置不仅包括那些要素,而且还包括没有明确列出的其他要素,或者是还包括为这种过程、方法、物品或者装置所固有的要素。在没有更多限制的情况下,由语句“包括一个

……”

限定的要素,并不排除在包括该要素的过程、方法、物品或者装置中还存在另外的相同要素。

204.上述本技术实施例序号仅仅为了描述,不代表实施例的优劣。本技术所提供的几个方法实施例中所揭露的方法,在不冲突的情况下可以任意组合,得到新的方法实施例。本技术所提供的几个产品实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的产品实施例。本技术所提供的几个方法或设备实施例中所揭露的特征,在不冲突的情况下可以任意组合,得到新的方法实施例或设备实施例。

205.以上所述,仅为本技术的具体实施方式,但本技术的保护范围并不局限于此,任何熟悉本技术领域的技术人员在本技术揭露的技术范围内,可轻易想到变化或替换,都应涵盖在本技术的保护范围之内。因此,本技术的保护范围应以所述权利要求的保护范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。