技术特征:

1.一种比较器,其特征在于,包括:第二级电路、第一输入电路、第二输入电路、第一交叉耦合电路和第二交叉耦合电路;所述第一交叉耦合电路连接所述第一输入电路;所述第二交叉耦合电路连接所述第二输入电路;所述第一输入电路和所述第二输入电路还均与所述第二级电路连接;所述第二级电路连接电源端或接地端;其中,所述第一输入电路,用于在导通时的采样阶段根据输入信号和第一参考信号生成第一数据端电压和第一参考端电压;所述第一交叉耦合电路,用于将所述第一数据端电压和所述第一参考端电压相互正反馈,生成所述第一差分信号;所述第二输入电路,用于在导通时的采样阶段根据所述输入信号和第二参考信号生成第二数据端电压和第二参考端电压;所述第二交叉耦合电路,用于将所述第二数据端电压和所述第二参考端电压相互正反馈,生成所述第二差分信号;所述第二级电路,用于在重生阶段对所述第一差分信号或所述第二差分信号进行放大处理和锁存处理,以输出比较信号。2.根据权利要求1所述的比较器,其特征在于,所述第一交叉耦合电路包括:第一耦合晶体管和第二耦合晶体管;所述第一差分信号包括:第一参考端输出信号和第一数据端输出信号;所述第一耦合晶体管的第一端连接所述第二耦合晶体管的控制端,并连接到所述第一输入电路的第一输出端;所述第一耦合晶体管的控制端连接所述第二耦合晶体管的第一端,并连接到所述第一输入电路的第二输出端;所述第一耦合晶体管的第二端连接所述第二耦合晶体管的第二端,并连接到所述第一输入电路;所述第一耦合晶体管和所述第二耦合晶体管为nmos或pmos;其中,所述第一耦合晶体管,用于在采样阶段根据所述第一参考端电压对所述第一数据端电压正反馈,以得到所述第一数据端输出信号;所述第二耦合晶体管,用于在采样阶段根据所述第一数据端电压对所述第一参考端电压正反馈,以得到所述第一参考端输出信号。3.根据权利要求1所述的比较器,其特征在于,所述第二交叉耦合电路包括:第三耦合晶体管和第四耦合晶体管;所述第二差分信号包括:第二参考端输出信号和第二数据端输出信号;所述第三耦合晶体管的第一端连接所述第四耦合晶体管的控制端,并连接到所述第二输入电路的第一输出端;所述第三耦合晶体管的控制端连接所述第四耦合晶体管的第一端,并连接到所述第二输入电路的第二输出端;所述第三耦合晶体管的第二端连接所述第四耦合晶体管的第二端,并连接到所述第二输入电路;所述第三耦合晶体管和所述第四耦合晶体管为nmos或pmos;其中,所述第三耦合晶体管,用于在采样阶段根据所述第二参考端电压对所述第二数据端电压正反馈,以得到所述第二数据端输出信号;所述第四耦合晶体管,用于在采样阶段根据所述第二数据端电压对所述第二参考端电

压正反馈,以得到所述第二参考端输出信号。4.根据权利要求1所述的比较器,其特征在于,所述第一输入电路包括:第一输入晶体管、第二输入晶体管和第三输入晶体管;所述第一输入晶体管的第一端和所述第二输入晶体管的第一端分别连接所述第二级电路;所述第一输入晶体管的第二端和所述第二输入晶体管的第二端均与所述第三输入晶体管的第一端连接;所述第一输入晶体管至第三输入晶体管为nmos或pmos;其中,所述第一输入晶体管的控制端接收所述输入信号;所述第二输入晶体管的控制端接收所述第一参考信号;所述第三输入晶体管的控制端接收第一反馈信号;当所述第三输入晶体管受到所述第一反馈信号触发为导通状态时,所述第一输入晶体管根据所述输入信号产生所述第一数据端电压,并作用于第二耦合晶体管的控制端;所述第二输入晶体管根据所述第一参考信号产生所述第一参考端电压,并作用于第一耦合晶体管的控制端。5.根据权利要求1所述的比较器,其特征在于,所述第二输入电路包括:第四输入晶体管、第五输入晶体管和第六输入晶体管;所述第四输入晶体管的第一端和所述第五输入晶体管的第一端分别连接所述第二级电路;所述第四输入晶体管的第二端和所述第五输入晶体管的第二端均与所述第六输入晶体管的第一端连接;所述第四输入晶体管至第六输入晶体管为nmos或pmos;其中,所述第四输入晶体管的控制端接收所述输入信号;所述第五输入晶体管的控制端接收所述第二参考信号;所述第六输入晶体管的控制端接收第二反馈信号;当所述第六输入晶体管受到所述第二反馈信号触发为导通状态时,所述第四输入晶体管根据所述输入信号产生所述第二数据端电压,并作用于第四耦合晶体管的控制端;所述第五输入晶体管根据所述第二参考信号产生所述第二参考端电压,并作用于第三耦合晶体管的控制端。6.根据权利要求1所述的比较器,其特征在于,所述比较器还包括:第一复位电路和时钟开关电路;通过所述第一复位电路连接所述第一输入电路与所述第二输入电路;所述第一复位电路还连接所述电源端或所述接地端;所述时钟开关电路连接所述第一输入电路与所述第二输入电路;所述时钟开关电路还连接所述接地端或所述电源端;其中,所述第一复位电路,用于在复位阶段对所述第一输入电路和所述第二输入电路复位;所述时钟开关电路,用于在时钟信号的触发下,控制所述比较器的导通。7.根据权利要求6所述的比较器,其特征在于,所述第一复位电路包括:第一复位晶体管和第二复位晶体管;所述第一复位晶体管的第一端和所述第二复位晶体管的第一端连接所述电源端或所述接地端;所述第一复位晶体管的第二端连接所述第一输入电路;所述第二复位晶体管的

第二端连接所述第二输入电路;所述第一复位晶体管和所述第二复位晶体管为pmos或nmos;其中,所述第一复位晶体管和所述第二复位晶体管的控制端均接收所述时钟信号;当所述时钟信号触发所述第一复位晶体管和所述第二复位晶体管为导通状态时,所述第一输入电路通过所述第一复位晶体管连接到所述电源端或所述接地端以复位,所述第二输入电路通过所述第二复位晶体管连接到所述电源端或所述接地端以复位。8.根据权利要求6所述的比较器,其特征在于,所述时钟开关电路包括:时钟开关晶体管;所述时钟开关晶体管的第一端连接所述第一输入电路和所述第二输入电路;所述时钟开关晶体管的第二端连接所述接地端或所述电源端;所述时钟开关晶体管为nmos或pmos;其中,所述时钟开关晶体管的控制端接收所述时钟信号;当所述时钟开关晶体管在所述时钟信号的触发下处于导通状态时,所述第一输入电路和所述第二输入电路通过所述时钟开关晶体管连接到所述接地端或所述电源端,以导通所述比较器。9.根据权利要求1所述的比较器,其特征在于,所述第二级电路包括:输出电路和第二复位电路;所述第二复位电路连接所述输出电路;所述输出电路还连接所述电源端或所述接地端;所述第二复位电路还连接所述电源端或所述接地端;其中,所述输出电路,用于在重生阶段对所述第一差分信号或所述第二差分信号进行放大处理和锁存处理,以输出比较结果;所述第二复位电路,用于在复位阶段对所述输出电路复位。10.根据权利要求9所述的比较器,其特征在于,所述第二复位电路包括:第三复位晶体管和第四复位晶体管;所述第三复位晶体管的第一端和第四复位晶体管的第一端均连接所述电源端或所述接地端;所述第三复位晶体管的第二端和所述第四复位晶体管的第二端分别连接所述输出电路;所述第三复位晶体管和所述第四复位晶体管为pmos或nmos;其中,所述第三复位晶体管和所述第四复位晶体管的控制端均接收所述时钟信号;当所述时钟信号触发所述第三复位晶体管和所述第四复位晶体管为导通状态时,所述输出电路通过所述第三复位晶体管和所述第四复位晶体管连接到所述电源端或所述接地端以复位。11.根据权利要求9所述的比较器,其特征在于,所述输出电路包括:第一输出晶体管、第二输出晶体管、第三输出晶体管、第四输出晶体管、第五输出晶体管和第六输出晶体管;所述第一输出晶体管的控制端、所述第二输出晶体管的第一端、所述第三输出晶体管的控制端、所述第四输出晶体管的第二端和所述第六输出晶体管的第二端均连接到所述输出电路的第一输出端;所述第一输出晶体管的第一端、所述第二输出晶体管的控制端、所述第三输出晶体管的第二端、所述第四输出晶体管的控制端和所述第五输出晶体管的第二端均连接到所述输出电路的第二输出端;

所述第一输出晶体管的第二端和所述第二输出晶体管的第二端分别连接所述第一输入电路、所述第二输入电路和所述第二复位电路;所述第三输出晶体管的第一端、所述第四输出晶体管的第一端、所述第五输出晶体管的第一端和所述第六输出晶体管的第一端均连接所述电源端或所述接地端;所述第一输出晶体管和所述第二输出晶体管为nmos或pmos;所述第三输出晶体管至第六输出晶体管为pmos或nmos;其中,所述第五输出晶体管的控制端和所述第六输出晶体管的控制端均接收所述时钟信号。12.根据权利要求1至11任一项所述的比较器,其特征在于,所述第一参考信号的电压大于或小于所述第二参考信号的电压。13.一种判决反馈均衡电路,其特征在于,包括:n级如权利要求1至12中任意一项所述的比较器;其中,n为大于1的正整数;每级比较器的第一输入端接收输入信号;所述每级比较器的第二输入端接收第一参考信号;所述每级比较器的第三输入端接收第二参考信号;所述第1级比较器的第四输入端与所述第n级比较器的输出端连接,接收所述第n级比较器输出的第n级比较信号;所述第1级比较器的第五输入端接收第1时钟信号;所述第i级比较器的第四输入端与所述第i

‑

1级比较器的输出端连接,接收所述第i

‑

1级比较器输出的第i

‑

1级比较信号;所述第i

‑

1级比较器的第五输入端接收第i时钟信号;其中,i大于1,且小于等于n;其中,所述每级比较器在每级时钟信号的触发下,根据所述每级比较器的第四输入端对应的比较信号,将所述输入信号与所述第一参考信号进行比较,或者,将所述输入信号与第二参考信号进行比较,以输出每级比较信号。14.根据权利要求13所述的判决反馈均衡电路,其特征在于,所述第i时钟信号的相位比所述第i

‑

1时钟信号的相位晚360

°

/n。15.根据权利要求13或14所述的判决反馈均衡电路,其特征在于,当n=4时,所述第1级比较器的第四输入端与第4级比较器的输出端连接,接收所述第4级比较器输出的第4级比较信号;所述第1级比较器的第五输入端接收第1时钟信号。16.根据权利要求13或14所述的判决反馈均衡电路,其特征在于,所述判决反馈均衡电路还包括:n个锁存器;每个锁存器的输入端对应连接每级比较器的输出端,以接收每级比较信号;其中,每个锁存器,用于将每级比较信号保存,以输出每级锁存信号。

技术总结

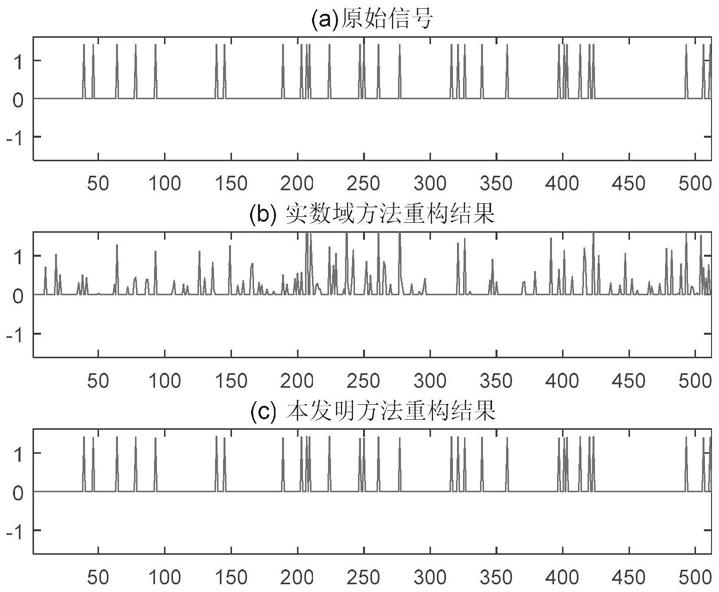

本申请提供了一种比较器及判决反馈均衡电路,比较器包括:第二级电路、第一输入电路、第二输入电路、第一交叉耦合电路和第二交叉耦合电路。其中,第一输入电路,用于在导通时的采样阶段生成第一数据端电压和第一参考端电压;第一交叉耦合电路,用于将第一数据端电压和第一参考端电压相互正反馈,生成第一差分信号;第二输入电路,用于在导通时的采样阶段生成第二数据端电压和第二参考端电压;第二交叉耦合电路,用于将第二数据端电压和第二参考端电压相互正反馈,生成第二差分信号;第二级电路,用于在重生阶段对第一差分信号或第二差分信号进行放大处理和锁存处理,以输出比较信号。本申请能够消除码间串扰的影响、提高比较器的工作速率。作速率。作速率。

技术研发人员:谷银川

受保护的技术使用者:长鑫存储技术有限公司

技术研发日:2021.07.12

技术公布日:2021/10/26

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。