用于增强型gan hemt的高频智能半桥栅驱动电路

技术领域

1.本发明涉及一种属于集成电路技术领域,具体涉及一种用于增强型gan hemt的高频智能半桥栅驱动电路。

背景技术:

2.随着超结金属-氧化物半导体场效晶体管(mosfet)和绝缘栅双极晶体管(igbt)的出现和普及,特别是以碳化硅sic和氮化镓gan为代表的宽禁带功率半导体器件的兴起,新一代电力电子应用系统对功率半导体器件驱动技术要求日益提高,这其中最核心的因素就是对功率半导体器件功能进行控制的高压栅驱动芯片。新一代电力电子整机系统为了进一步提高整机可靠性,并降低整机系统设计复杂度,对高压栅驱动芯片的智能化提出了更高的需求。

3.根据不同的栅极结构,gan器件可以分为两类,耗尽型ga n器件和增强型ga n器件。gan器件的特性决定了,该类器件在驱动设计考虑时有一些需要特别注意的因素:如vth低、vgs上限低、寄生参数对高di/dt和dv/dt敏感以及无反向导通二极管等问题,很大程度上限制了ga n器件在各种高频功率拓扑中的应用。

4.在诸多栅驱动芯片中,半桥栅驱动芯片是一种最常用的芯片架构,现有的半桥栅驱动芯片由高侧和低侧驱动电路构成。通常高低侧驱动电路之间有高低压隔离区,必须使用高压电平移位电路将低压输入hi信号传输给高侧输出驱动电路。现有技术中,高压电平移位电路必须使用耐高压的ldmos来实现信号传输,而高压ldmos存在很大的寄生电容,会严重限制高压电平移位电路的信号处理速度,采用该技术的650v高侧驱动电路的速度通常被限制在200khz以下,无法满足以gan和sic为代表的宽禁带功率器件超过mhz的处理速度要求。

5.此外,现有的半桥栅驱动芯片当被设计定型之后,其高/低侧输出控制信号的输出驱动能力将被固化。在实际应用中,为防止输出电流对负载功率开关的栅极造成损坏,通常在高/低侧输出端串接一个电阻,以抑制栅极电压过冲影响。串接保护电阻会带来2个问题,一是电阻上的开关损坏变大,降低驱动电路的效率;二是增加了驱动延时,最终降低系统开关频率。

6.gan器件由于具有较小的ciss电容,交叠损耗下降,但开关速度的提升使其在高压大电流应用下di/dt和dv/dt性能变差,功率驱动级产生的电磁干扰(emi)问题严重阻碍gan电源模块的系统集成。高的开关频率会导致较大的di/dt和dv/dt,从而将高频emi噪声引入,这会在关键的安全系统中产生不必要的噪声甚至故障。这些寄生效应所产生的电流和电压尖峰,可能会导致gan器件损坏或者导致相关的低压逻辑电路损坏。

7.虽然ga n器件没有体二极管,但有其独特的反向导通机理,其反向导通电压高于si mosfet。这种特性使其在某些功率转换电路中(例如死区时间内)导致更高的导通损耗。随着死区时间的增大,系统的功率损失和转换效率都会退化,在高频情况下会更加严重。同时,当采用负压关断的技术来实现耗尽型ga n器件的驱动时,关断电压会叠加在死区时间

的负压上,进一步增加死区时间的损耗。

技术实现要素:

8.为解决上述问题,提供一种用于增强型gan hemt的高频智能半桥栅驱动电路,可以减小电平移位电路的延迟,提高整体驱动电路速度同时降低电路功耗,本发明采用了如下技术方案:

9.本发明提供了一种用于增强型gan hemt的高频智能半桥栅驱动电路,用于对外部的低压数字输入信号hi和li进行处理并输出高侧输出信号ho和低侧输出信号lo,其特征在于,包括:输入接收电路、数控高精度死区时间产生电路、低侧数控延时电路、低侧高效率输出驱动电路l、高侧预驱动电路、低延时高压电平移位电路、高侧高效率输出驱动电路h、栅压钳位电路、短路保护电路以及欠压保护电路,其中,输入接收电路与中压电源电压vcc以及低压电源电压vcl连接,接收低压数字输入信号hi和li并进行信号电平判别和逻辑电平高压转换从而获得中压信号h和l,短路保护电路与数控高精度死区时间产生电路连接,用于实时监测中压电源电压vcc的电流状态,并向数控高精度死区时间产生电路输出短路保护信号oc,欠压保护电路与数控高精度死区时间产生电路连接,用于实时监测中压电源电压vcc的电压状态,并向该数控高精度死区时间产生电路输出欠压保护信号uv,低侧高效率输出驱动电路l输出频率判别码dfin,用于控制数控高精度死区时间产生电路和低侧数控延时电路内部的延迟电路的延时长短,数控高精度死区时间产生电路与中压电源电压vcc接,用于在短路保护信号oc、欠压保护信号uv以及频率判别码dfin的控制下,根据中压信号h获得高侧差分预输入数据hp和hn,同时根据中压信号l获得低侧差分输入数据lip和lin,高侧预驱动电路与数控高精度死区时间产生电路连接,用于接收高侧差分预输入数据hp和hn并对其进行处理,从而获得高侧差分输入数据hip和hin,低延时高压电平移位电路与高侧预驱动电路连接,用于接收高侧差分输入数据hip和hin并对其进行处理,从而获得低电位浮动的驱动数据din,高侧高效率输出驱动电路h与低延时高压电平移位电路连接,用于接收驱动数据din并对其进行放大处理,从而获得高侧预输出信号voutp栅压钳位电路与高侧高效率输出驱动电路h连接,用于接收高侧预输出信号voutp并对其进行处理,从而获得高侧输出信号ho并输出,低侧数控延时电路与数控高精度死区时间产生电路连接,用于接收低侧差分输入数据lip和lin并对其进行处理,从而获得低侧驱动数据,低侧高效率输出驱动电路l与低侧数控延时电路连接,用于接收低侧驱动数据并对其进行放大处理,从而获得低侧输出信号lo并输出,低延时高压电平移位电路同时使用低压地vss和浮动地sw,高侧高效率输出驱动电路h和高侧栅压钳位电路仅使用浮动地sw,输入接收电路、数控高精度死区时间产生电路、低侧数控延时电路、低侧高效率输出驱动电路l、短路保护电路和欠压保护电路共同使用低压地vss,高效率输出驱动电路的驱动能力受控制时钟信号clk-ctrl和上电信号start-up控制。

10.本发明提供的用于增强型gan hemt的高频智能半桥栅驱动电路,还可以具有这样的特征,其中,数控高精度死区时间产生电路和低侧数控延时电路内部的延迟电路采用数字控制延时电路,数字控制延时电路包括输入rs触发器、由多个反相器级联组成的反相器链、编码转换电路、n个延迟电容和n个电容选择开关,n为正整数,n个延迟电容的一端同时连接到低压地vss,另一端分别连接到n个电容选择开关,n个电容选择开关的另一端同时连

接到反相器链中任意一个反相器的输出端,编码转换电路将频率判别码dfin转换成n个电容选择开关的开关选择信号b1~bn,输入rs触发器的输入端接收低侧差分输入数据lip和lin,输出端连接到反相器链的输入端。

11.本发明提供的用于增强型gan hemt的高频智能半桥栅驱动电路,还可以具有这样的特征,其中,低延时高压电平移位电路具有第一高压ldmos晶体管md1、第二高压ldmos晶体管md2、第一保护二极管d1、第二保护二极管d2、第三电阻r3、第四电阻r4、第一电阻r1、第二电阻r2、第一耦合mos管m1、第二耦合mos管m2、第一速度增强晶体管me1、第二速度增强晶体管me2、误差迟滞过滤电路以及信号翻转检测电路,第一高压ldmos晶体管md1和第二高压ldmos晶体管md2的源极与低压地vss连接,第一高压ldmos晶体管md1的漏极同时连接到第一耦合mos管m1的源极、第一保护二极管d1的阳极、第三电阻r3的下端以及第二耦合mos管m2的栅极,第二高压ldmos晶体管md2的漏极同时连接到第二耦合mos管m2的源极、第二保护二极管d2的阳极、第四电阻r4的下端以及第一耦合mos管m1的栅极,第一耦合mos管m1的漏极同时连接到第一电阻r1的上端、误差迟滞过滤电路的数据输入p端lsp以及第一速度增强晶体管me1的漏极,第二耦合mos管m2的漏极同时连接到第二电阻r2的上端、误差迟滞过滤电路的数据输入n端lsn以及第二速度增强晶体管me2的漏极,第一电阻r1和第二电阻r2的下端与浮动地sw连接,误差迟滞过滤电路输出驱动数据din,并发送给信号翻转检测电路作为信号翻转检测电路的输入信号,信号翻转检测电路的2个输出端分别连接第一速度增强晶体管me1和第二速度增强晶体管me2的栅极,第一保护二极管d1的阴极、第二保护二极管d2的阴极、第三电阻r3的上端、第四电阻r4的上端、第一速度增强晶体管me1的源极和第二速度增强晶体管me2的源极同时连接到高压电源电压。

12.本发明提供的用于增强型gan hemt的高频智能半桥栅驱动电路,还可以具有这样的特征,其中,高可靠误差迟滞过滤电路具有p端耦合反相器、p端去毛刺电路、p端或门、p端数据选择器、n端耦合反相器、n端去毛刺电路、n端或门以及n端数据选择器电路,p端去毛刺电路和n端去毛刺电路的结构相同,其内部包含3个2输入与非门和一个2输入或门。

13.本发明提供的用于增强型gan hemt的高频智能半桥栅驱动电路,还可以具有这样的特征,其中,高效率输出驱动电路具有p端反相器链、n端反相器链、n(n为任意正整数)个p端输出反相器、n个n端输出反相器、n个p端输出pmos管、n个n端输出nmos管、n个p端输出反相器控制开关、n个n端输出反相器控制开关、采样开关sw、输入数据开关kin、测试数据开关kcal、高速比较器阵列、误差过滤电路、负载判别电路、驱动电流选择电路、输入脉冲频率判别电路以及控制器电路,p端反相器链具有k(k为任意正整数)个级联的p端输入缓冲反相器,该p端输入缓冲反相器的驱动能力从前级到后级逐步增大,n端反相器链的输入端与p端反相器链的输入端、输入数据开关kin、测试数据开关kcal连接,输出端与n个n端输出反相器控制开关连接,具有一个延迟单元和k-1个级联的n端输入缓冲反相器,延迟单元的延迟时间与最前端的p端输入缓冲反相器的延迟时间相等,n端输入缓冲反相器的驱动能力从前级到后级逐步增大,输入数据开关kin的输入端接收驱动数据din,n个p端输出反相器开关的一端均与p端反相器链的输出端连接,另一端分别与n个p端输出pmos管的栅极连接,n个n端输出反相器开关的一端均与n端反相器链的输出端连接,另一端分别与n个n端输出nmos管的栅极连接,n个p端输出pmos管的源极均连接到电源电压,n个n端输出nmos管的源极均连接到地,n个p端输出pmos管的漏极与n个n端输出nmos管的漏极以及驱动电路输出vout连

接,采样开关sw一端与驱动电路的输出vout连接,另一端与高速比较器阵列的输入端连接,高速比较器阵列的输出端与误差过滤电路的输入端连接,误差过滤电路的输出端与负载判别电路的输入端连接,负载判别电路的输出端与驱动电流选择电路的输入端连接,输入脉冲频率判别电路的输出端与负载判别电路的输入端连接,采样开关sw一端与驱动电路的输出vout连接对其进行采样,另一端与高速比较器阵列的输入端连接,高速比较器阵列的输出端与误差过滤电路的输入端连接,用于将驱动电路的输出vout与n个参考电压进行比较并将结果输出给误差过滤电路,误差过滤电路的输出端与负载判别电路的输入端连接,用于对高速比较器阵列输出的结果进行过滤获得负载检测码dtest并输出给负载判别电路,输入脉冲频率判别电路的输出端与负载判别电路的输入端连接,用于对驱动数据din的频率进行比较量化获得din的频率判别码dfin并输出给负载判别电路,负载判别电路的输出端与驱动电流选择电路的输入端连接,用于根据接收到的负载检测码dtest以及频率判别码dfin进行计算获得负载评估码dev并输出给驱动电流选择电路,驱动电流选择电路与n个p端输出反相器控制开关以及n个n端输出反相器控制开关,用于根据负载评估码dev向n个p端输出反相器控制开关以及n个n端输出反相器控制开关发送控制信号从而控制其通断,控制器电路的输出端与测试数据开关kcal、输入脉冲频率判别电路的控制信号输入端、高速比较器阵列的控制信号输入端、误差过滤电路的控制信号输入端、负载判别电路的控制信号输入端以及驱动电流选择电路的控制信号输入端连接,受控制时钟信号clk-ctrl和上电信号start-up控制,触发控制时钟信号clk-ctrl的频率为负载测试信号dcal频率的r倍,r为任意正整数。

14.本发明提供的用于增强型gan hemt的高频智能半桥栅驱动电路,还可以具有这样的特征,其中,控制器电路包括:频率判别控制产生电路,用于产生控制信号ctrl_fin并通过该控制信号ctrl_fin控制输入脉冲频率判别电路;开关信号产生电路,用于产生开关控制信号并通过该开关控制信号控制输入数据开关kin、测试数据开关kcal以及采样开关sw;负载测试控制产生电路,用于产生控制信号ctrl_test并通过该控制信号ctrl_test控制高速比较器阵列和误差过滤电路;负载判别控制产生电路,用于产生控制信号ctrl_ev并通过该控制信号ctrl_ev控制负载判别电路;驱动电流控制产生电路,用于产生控制信号ctrl_out并通过该控制信号ctrl_out控制驱动电流选择电路;测试码产生电路,用于产生负载测试信号dcal和测试时钟信号clkcal,通过负载测试信号dcal控制测试数据开关kcal,并通过测试时钟信号clkcal控制输入脉冲频率判别电路;以及计数器电路,用于根据控制时钟信号clk-ctrl和上电信号start-up按照预定顺序提供产生上述各信号所需的触发信号。

15.本发明提供的用于增强型gan hemt的高频智能半桥栅驱动电路,还可以具有这样的特征,其中,负载判别电路具有2个寄存器以及归一量化计算电路,2个寄存器分别用于存放负载检测码dtest和频率判别码dfin,归一量化计算电路用于根据负载检测码dtest和频率判别码dfin进行计算处理从而获得负载评估码dev。

16.本发明提供的用于增强型gan hemt的高频智能半桥栅驱动电路,还可以具有这样的特征,其中,栅压钳位电路具有第一pmos晶体管m1l、第二pmos晶体管m2l、nmos晶体管m3l、比较器、钳位反相器和2输入或门,第一pmos晶体管m1l和nmos晶体管m3l的栅极同时连接到高侧预输出信号voutp,漏极同时连接到高侧输出信号ho、比较器的正输入端、第二pmos晶体管m2l的漏极以及2输入或门的第一输入端,比较器的负输入端与高侧高压电源,

其输出连接到钳位反相器的输入端,钳位反相器的输出端连接到2输入或门的第二输入端,2输入或门的输出端连接到第二pmos晶体管m2l的栅极;第一pmos晶体管m1l和第二pmos晶体管m2l的源极同时连接到高侧高压电源。

17.发明作用与效果

18.根据本发明的用于增强型gan hemt的高频智能半桥栅驱动电路,通过正反馈驱动电流增强技术减小电平移位电路的延迟,提高整体驱动电路速度。设置数控高精度死区时间产生电路对死区时间进行自适应精确设定,根据输入pwm脉冲信号的工作频率自适应设定死区时间长度,实现死区时间功耗损失的最小化降低死区时间设定而引起的功耗损失。设置低侧和高侧高效率输出驱动电路,可以根据负载大小和输入控制脉冲的频率自适应调整驱动电流,从而最大程度上提高驱动电路的电源效率。采用短路保护电路和欠压保护电路对电路进行保护,在电路过流或电源电压异常时,可以锁定电路状态,提高驱动电路的可靠性。

附图说明

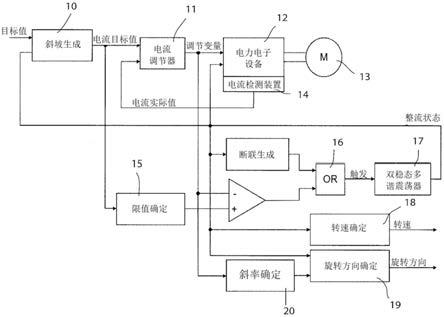

19.图1是本发明实施例的用于增强型gan hemt的高频智能半桥栅驱动电路结构图;

20.图2是本发明实施例的输入接收电路结构图;

21.图3是本发明实施例的数控高精度死区时间产生电路结构图;

22.图4是本发明实施例的错误逻辑处理电路结构图;

23.图5是本发明实施例的数字控制延时电路结构图;

24.图6是本发明实施例的高侧预驱动电路结构图;

25.图7是本发明实施例的低延时高压电平移位电路结构图;

26.图8是本发明实施例的低延时高压电平移位电路延时减小原理示意图;

27.图9是本发明实施例的高可靠误差迟滞过滤电路结构图;

28.图10是本发明实施例的高效率输出驱动电路结构框图;

29.图11是本发明实施例的驱动能力自适应调整过程流程图;

30.图12是本发明实施例的负载检测原理说明图;

31.图13是本发明实施例的负载判别电路框图;

32.图14是本发明实施例的控制器电路框图;

33.图15是本发明实施例的欠压保护电路结构图;

34.图16是本发明实施例的过流保护电路结构图;

35.图17是本发明实施例的输出栅压钳位电路结构图;

具体实施方式

36.以下结合附图以及实施例来说明本发明的具体实施方式。

37.<实施例>

38.图1是本发明实施例的用于增强型gan hemt的高频智能半桥栅驱动电路结构图。

39.如图1所示,本实施例提供一种用于增强型gan hemt的高频智能半桥栅驱动电路,用于对外部输入的低压数字输入信号hi和li进行处理并输出高侧输出信号ho和低侧输出信号lo,包括输入接收电路、数控高精度死区时间产生电路、低侧数控延时电路、低侧高效

率输出驱动电路l、高侧预驱动电路、低延时高压电平移位电路、高侧高效率输出驱动电路h、栅压钳位电路、短路保护电路以及欠压保护电路。

40.输入接收电路与中压电源电压vcc以及低压电源电压vcl连接,接收低压数字输入信号hi和li并进行信号电平判别和逻辑电平高压转换从而获得中压信号h和l。

41.短路保护电路与数控高精度死区时间产生电路连接,用于实时监测中压电源电压vcc的电流状态,并向数控高精度死区时间产生电路输出短路保护信号oc。

42.欠压保护电路与数控高精度死区时间产生电路连接,用于实时监测中压电源电压vcc的电压状态,并向该数控高精度死区时间产生电路输出欠压保护信号uv。

43.低侧高效率输出驱动电路l输出频率判别码dfin,用于控制数控高精度死区时间产生电路和低侧数控延时电路内部的延迟电路的延时长短。

44.数控高精度死区时间产生电路与中压电源电压vcc接,用于在短路保护信号oc、欠压保护信号uv以及频率判别码dfin的控制下,根据中压信号h获得高侧差分预输入数据hp和hn,同时根据中压信号l获得低侧差分输入数据lip和lin。

45.高侧预驱动电路与数控高精度死区时间产生电路连接,用于接收高侧差分预输入数据hp和hn并对其进行处理,从而获得高侧差分输入数据hip和hin。

46.低延时高压电平移位电路与高侧预驱动电路连接,用于接收高侧差分输入数据hip和hin并对其进行处理,从而获得低电位浮动的驱动数据din。

47.高侧高效率输出驱动电路h与低延时高压电平移位电路连接,用于接收驱动数据din并对其进行放大处理,从而获得高侧预输出信号voutp

48.栅压钳位电路与高侧高效率输出驱动电路h连接,用于接收高侧预输出信号voutp并对其进行处理,从而获得具有较大驱动能力的高侧输出信号ho并输出。

49.低侧数控延时电路与数控高精度死区时间产生电路连接,用于接收低侧差分输入数据lip和lin并对其进行处理,从而获得低侧驱动数据。

50.低侧高效率输出驱动电路l与低侧数控延时电路连接,用于接收低侧驱动数据并对其进行放大处理,从而获得具有较大驱动能力的低侧输出信号lo并输出。

51.低延时高压电平移位电路同时使用低压地vss和浮动地sw,高侧高效率输出驱动电路h和高侧栅压钳位电路仅使用浮动地sw,输入接收电路、数控高精度死区时间产生电路、低侧数控延时电路、低侧高效率输出驱动电路l、短路保护电路和欠压保护电路共同使用低压地vss。

52.高效率输出驱动电路的驱动能力受控制时钟信号clk-ctrl和上电信号start-up控制。

53.图2是本发明实施例的输入接收电路结构图。

54.如图2所示,输入接收电路包括相同的两个输入通道,每个通道包含输入esd保护、施密特触发器、或非门和中压电平移位电路。

55.输入接收电路在完成信号传输的同时,还需要对芯片内部的电路的esd保护,防止由于esd造成对电路内部的冲击而损毁电路。

56.施密特触发器用于识别外部输入电平是逻辑“0”还是“1”,由于外部信号存在很大干扰,施密特触发器必须具备足够的抗干扰噪声容限。根据驱动芯片驱动对象和输入逻辑信号的速度不同,施密特触发器的实现电路可能存在很大差异。

57.由于栅驱动芯片的供电电压vcc通常为10~20v的中压电平,而输入逻辑电平为低于5v的外部数字逻辑,为更精确地完成对输入逻辑电平的判断,输入esd、施密特触发器和或非门必须使用相对更低的低压电源电压vcl,通常为3-10v电压。

58.输入接收电路输出的逻辑信号需要经过一个中压电平移位电路将高电平为vcl的逻辑信号转换为高电平为vcc的逻辑信号,从而获得中压信号h和l。

59.输入接收电路在应用中,通常和保护信号联动使用,关断保护信号需要单独提供一组信号输入电路,同样由基本单元电路配套使用,由施密特触发器和rs锁存器组成。图2中sd信号支路即为关断保护功能输入控制电路。

60.图3是本发明实施例的数控高精度死区时间产生电路结构图。

61.如图3所示,数控高精度死区时间产生电路产生死区方式是采用延迟电路,使输入的两路信号产生相位差,再对输入信号进行逻辑运算,从而得到一个死区时间。死区时间的大小由延迟电路产生的延迟时间决定,因此延迟电路时死区电路的核心。

62.本实施例中,延迟电路采用高精度数字控制延迟电路实现,其延迟时间由频率码dfin控制。

63.输入接收电路输出的中压信号h和l进入输入逻辑电路,然后进入高精度数字控制延迟电路,最后结果缓冲器buff输出,得到数据输出。输入逻辑电路受错误逻辑处理电路的输出fault信号控制。

64.正常情况下fault为低电平,表示电路状态正常,数控高精度死区时间产生电路根据中压信号h得到高侧差分预输入数据hp和hn,根据中压信号l得到低侧差分输入数据lip和lin。

65.若fault为高电平,表示电路状态异常,fault信号此时将会锁定死区时间产生电路的信号输出。fault信号由错误逻辑处理电路根据上电信号start-up、短路保护信号oc和欠压保护信号uv,进行信号判断后获得。

66.图4是本发明实施例的错误逻辑处理电路结构图。

67.如图4所示,错误逻辑处理电路由前后级联的逻辑门电路和rc延迟电路构成。

68.图5是本发明实施例的数字控制延时电路结构图。

69.如图5所示,的数字控制延时电路由输入rs触发器、多个反相器级联组成的反相器链、编码转换电路、n个延迟电容和n个电容选择开关构成。

70.n个电容的下端同时接低压地vss,n个延迟电容的上端分别连接到n个电容选择开关的下端,n个电容选择开关的上端同时连接到反相器链中任意一个反相器的输出端。

71.编码转换电路将频率判别码dfin转换成n个电容选择开关的开关选择信号b1~bn。

72.输入rs触发器的输入端接收低侧差分输入数据lip和lin,输出端连接到反相器链的输入端。

73.数字控制延时电路通过改变连接到信号传输通路上的电容大小和个数,实现可精确设定的不同延时,该延时单元所产生的延时大小受频率判别码dfin码控制。

74.本实施例中,反相器链中反相器的个数根据系统延时特性综合选择。n个延迟电容容值权重大小的选择,可以采用二进制权重比例关系,也可以选择权值相等的方式,或者混合结构。n个电容选择开关的编码方式须和n个延迟电容容值权重关系对应,可以选择二进

制编码,也可以采用温度计编码,或者二进制和温度计编码的混合形式。

75.图5中所示的n个延迟电容容值权重为二进制比例关系,第1个电容为c,第2个电容为c/2,第n个电容为c/2

n-1

,实际应用中上述电容和选择开关编码方式取决于n的大小。

76.图6是本发明实施例的高侧预驱动电路结构图。

77.如图6所示,高侧预驱动电路的结构与图3所示的数控高精度死区时间产生电路的结构类似,采用图5所示的高精度数字控制延迟电路,其延迟时间由频率码dfin控制,使输入的两路信号产生相位差,再对输入高侧差分预输入数据hp和hn进行逻辑运算,得到高侧差分输入数据hip和hin。

78.由于高端信号经过电平位移电路后,相比于低端信号产生了一定的延迟,对于中高频的应用,这段时间已经造成了高低端信号相位的不匹配,会影响系统的正常工作,因此,必须在低端信号通路上加入延迟匹配电路也即本实施例中的高精度数字控制延迟电路,来实现高低端信号的相位的匹配。

79.图7是本发明实施例的低延时高压电平移位电路结构图。

80.如图7所示,低延时高压电平移位电路内部包括:第一高压ldmos晶体管md1、第二高压ldmos晶体管md2、第一保护二极管d1、第二保护二极管d2、第三电阻r3、第四电阻r4、第一电阻r1、第二电阻r2、第一耦合mos管m1、第二耦合mos管m2、第一速度增强晶体管me1、第二速度增强晶体管me2、误差迟滞过滤电路以及信号翻转检测电路。

81.第一高压ldmos晶体管md1和第二高压ldmos晶体管md2的源极与低压地vss连接。

82.第一高压ldmos晶体管md1的漏极同时连接到第一耦合mos管m1的源极、第一保护二极管d1的阳极、第三电阻r3的下端以及第二耦合mos管m2的栅极。

83.第二高压ldmos晶体管md2的漏极同时连接到第二耦合mos管m2的源极、第二保护二极管d2的阳极、第四电阻r4的下端以及第一耦合mos管m1的栅极。

84.第一耦合mos管m1的漏极同时连接到第一电阻r1的上端、误差迟滞过滤电路的数据输入p端lsp以及第一速度增强晶体管me1的漏极。

85.第二耦合mos管m2的漏极同时连接到第二电阻r2的上端、误差迟滞过滤电路的数据输入n端lsn以及第二速度增强晶体管me2的漏极。

86.第一电阻r1和第二电阻r2的下端与浮动地sw连接。

87.误差迟滞过滤电路输出驱动数据din,并发送给信号翻转检测电路作为信号翻转检测电路的输入信号。

88.信号翻转检测电路的2个输出端分别连接第一速度增强晶体管me1和第二速度增强晶体管me2的栅极。

89.第一保护二极管d1的阴极、第二保护二极管d2的阴极、第三电阻r3的上端、第四电阻r4的上端、第一速度增强晶体管me1的源极和第二速度增强晶体管me2的源极同时连接到高压电源电压。

90.图8是本发明实施例的低延时高压电平移位电路延时减小原理示意图。

91.如图8所示,假设高侧差分输入数据hip输入一个脉冲,经过一定时间的延迟驱动数据din将会由0开始上升,对于未采用延时优化的常规电平移位电路,din的上升延时时间为td。通过信号翻转检测电路检测驱动数据din的变化,当其超过一定阈值时加速驱动数据din的翻转速度。

92.t0时刻,lsp电压开始由0低变高,引起驱动数据din从浮动地sw(此时为vh电压)开始由低变高。

93.tdet时刻,当信号翻转检测电路确认驱动数据din是由低转高并且驱动数据din电压超过信号翻转检测电路的阈值vth-det时,信号翻转检测电路开启第二速度增强晶体管me2,加速误差迟滞过滤电路的数据输入p端lsp的电压上升速度,从而加速驱动数据din由阈值vth-det上升到高压电源vh vcc的电压上升过程。

94.tden时刻,驱动数据din即可完成由低到高电位的翻转。若如将阈值vth-det设置在中压电源电压vcc电压的20%,则驱动数据din由低到高的整体翻转时间tden可以为减小为原来td的30%,即高侧差分输入数据hip到驱动数据din的信号传输延时减小为30%,对应的驱动电路速度可以提高3倍以上。

95.显然将vth-det设置在不同的阈值,对于tden的先后有直接影响,阈值vth-det越小则tden越小,延时越短,但是对于误差迟滞过滤电路的数据输入p端lsp的误差波动越敏感,为此需要高抗干扰性能的误差迟滞过滤电路对其数据输入p端lsp和数据输入n端lsn上的各种误差干扰进行滤除。

96.图9是本发明实施例的高可靠误差迟滞过滤电路结构图。

97.如图9所示,高可靠误差迟滞过滤电路包括:p端耦合反相器、p端去毛刺电路、p端或门、p端数据选择器、n端耦合反相器、n端去毛刺电路、n端或门和n端数据选择器电路。

98.p端去毛刺电路和n端去毛刺电路的结构相同,其内部包含3个2输入与非门和一个2输入或门。

99.本实施例中,对于图7中信号翻转检测电路可以采用常规的组合逻辑电路实现,如采用反相器电路,或者加入控制功能的反相器电路,令反相器的翻转阈值为vth-det。也可以采用高速比较器实现,高速比较器的一端为阈值vth-det,另外一端为驱动数据din。

100.图10是本发明实施例的高效率输出驱动电路结构框图。

101.如图10所示,高效率输出驱动电路包括p端反相器链、n端反相器链、n(n为任意正整数)个p端输出反相器、n个n端输出反相器、n个p端输出pmos管mp1~mpn、n个n端输出nmos管mn1~mnn、n个p端输出反相器控制开关、n个n端输出反相器控制开关、采样开关sw、输入数据开关kin、测试数据开关kcal、高速比较器阵列、误差过滤电路、负载判别电路、驱动电流选择电路、输入脉冲频率判别电路以及控制器电路。

102.p端反相器链内部包含k(k为任意正整数)个级联的p端输入缓冲反相器invp0~invpk-1,k个p端输入缓冲反相器的驱动能力从前级到后级逐步增大。

103.n端反相器链包含k-1个级联的n端输入缓冲反相器invn1~invnk-1和一个延迟单元delay,k-1个n端输入缓冲反相器的驱动能力从前级到后级逐步增大,延迟单元delay的延迟时间等于最前端p端输入缓冲反相器的延时时间。

104.p端反相器链和n端反相器链的输入端连接在输入数据开关kin和测试数据开关kcal的右侧,p端反相器链的输出端同时连接到n个p端输出反相器控制开关的左侧,n端反相器链的输出端同时连接到n个n端输出反相器控制开关的左侧。

105.n个p端输出反相器控制开关的右侧分别与n个p端输出pmos管的栅极连接,n个n端输出反相器控制开关的右侧分别与n个n端输出nmos管的栅极连接。

106.n个p端输出pmos管的源极同时连接到电源电压,n个n端输出nmos管的源极同时连

接到地,n个p端输出pmos管的漏极同时连接到n个n端输出nmos管的漏极和驱动电路的输出vout。

107.采样开关sw一端与驱动电路的输出vout连接,另一端与高速比较器阵列的输入端连接,高速比较器阵列的输出端与误差过滤电路的输入端连接,误差过滤电路的输出端与负载判别电路的输入端连接,负载判别电路的输出端与驱动电流选择电路的输入端连接,输入脉冲频率判别电路的输出端与负载判别电路的输入端连接。

108.驱动电路输出vout经样开关sw采样后进入高速比较器阵列与n个参考电压进行比较,然后进入误差过滤电路后输出负载检测码dtest,输入脉冲频率判别电路对驱动数据din的频率进行比较量化获得din的频率判别码dfin,负载检测码dtest和频率判别码dfin进入负载判别电路计算得到负载评估码dev,驱动电流选择电路根据负载评估码dev的大小,输出n个p端输出反相器控制开关以及n个n端输出反相器控制开关的开关控制信号,从而选择输出控制n个p端输出反相器控制开关的开关控制信号kp1~kpn以及n个n端输出反相器控制开关的开关控制信号kn1~knn。

109.控制器电路输出的负载测试信号dcal连接到测试数据开关kcal的左侧,控制器电路输出的测试时钟信号clkcal连接到输入脉冲频率判别电路的时钟输入端,控制器电路输出的负载测试控制信号ctrl_test分别连接到高速比较器阵列和误差过滤电路的控制信号输入端,控制器电路输出的控制信号ctrl_ev连接到负载判别电路的控制信号输入端,控制器电路输出的控制信号ctrl_out连接到驱动电流选择电路的控制信号输入端,控制器电路输出的控制信号ctrl_fin连接到输入脉冲频率判别电路的控制信号输入端。

110.控制器电路受触发控制时钟信号clk-ctrl和上电信号start-up控制。触发控制时钟信号clk-ctrl的频率是负载测试信号dcal频率的r倍,其中,r为任意正整数。

111.高效率输出驱动电路具有驱动能力自适应调整和正常工作两种工作模式。当电源电压上电之后高效率输出驱动电路首先开始驱动能力自适应调整模式,然后进入正常工作模式。

112.图11是本发明实施例的驱动能力自适应调整过程流程图。

113.如图11所示,驱动电路进行驱动能力自适应调整的过程如下:

114.电源电压上电,产生上电信号start-up。

115.控制器电路关闭输入数据开关kin,并输出控制时钟信号clkcal,启动输入脉冲频率判别电路,输入脉冲频率判别电路基于控制时钟信号clkcal对输入数据din的频率进行比较量化并得到输入数据din的频率判别码dfin。

116.控制器电路开启测试数据开关kcal、p端输出反相器控制开关kp1和n端输出反相器控制开关kn1,并输出负载测试信号dcal。

117.控制器电路开启高速比较器阵列、误差过滤电路、负载判别电路和驱动电流选择电路。

118.在负载测试信号dcal输出之后的第m个控制时钟信号clk-ctrl时钟沿,当输出建立时间(即驱动电路输出vout的电压上升需要的时间)满足后,控制器电路开启采样开关sw对驱动电路输出vout的电压进行采样,并经高速比较器阵列和误差过滤电路处理得到负载检测码dtest。输出建立时间由m个clk-ctrl时钟周期组成,其时间跨度小于负载测试信号dcal的1个周期时间,其中,m为小于r的正整数。

119.负载判别电路根据负载检测码dtest和频率判别码dfin,计算得到负载评估码dev。

120.驱动电流选择电路根据负载评估码dev,对p端输出反相器控制开关kp2~kpn和n端输出反相器控制开关kn2~knn进行控制,并保持不变,然后结束驱动能力自适应调整模式。

121.控制器电路开启输入数据开关kin,关闭测试数据开关kcal以及负载测试信号dcal,从而让驱动电路进入正常工作模式。

122.输入脉冲频率判别电路对驱动数据din的频率进行比较量化的过程中,j个测试时钟信号clkcal周期的时间长度大于驱动数据din的整数周期。若输入数据din频率为100khz,测试时钟信号clkcal的频率为10mhz,则输入数据din和测试时钟信号clkcal对应信号周期分别为10us和0.1us,且j取值必须大于100。j数值越大输入数据din的数值越精确。

123.负载测试信号dcal输出之后的第m个控制时钟信号clk-ctrl时钟沿,其时间跨度小于负载测试信号dcal的1个周期时间。例如,负载测试信号dcal频率为200khz,控制时钟信号clk-ctrl的频率为5mhz,则负载测试信号dcal和控制时钟信号clk-ctrl对应信号周期分别为5us和0.2us,且m取值必须小于25,此时m数值越接近25则负载检测码dtest的数值越精确。

124.图12是本发明实施例的负载检测原理说明图。

125.如图12所示,假设输出驱动电路开启kp1和kn1后,n端输出nmos管mn1和p端输出pmos管mp1提供的输出电流为iout=0.5a,控制时钟信号clk-ctrl的频率为5mhz(对应信号周期为0.2us),选取m=5,则采样开关sw将在负载测试信号dcal高电平开始1us时对vout电压进行采样。对于固定的输出iout,可以看出驱动的负载电容越大,vout的上升斜率越低,1us时vout电压大小和负载电容成反比关系,即负载为0.5nf时的vout电压应该是负载为1.5nf时的vout电压的3倍。因此,在固定的驱动电流条件下,根据1us时驱动电路输出vout的电压的大小,即可确定输出驱动负载的大小,并且将驱动电路输出vout的电压与n个参考电压vr1~vrn进行比较,即可对输出驱动负载的大小进行量化,得到负载量化码dout。

126.在本实施例中,在固定的驱动电流条件下,1us时vout电压与n个参考电压vr1~vrn进行比较量化的工作由高速比较器阵列实现。根据负载检测量化速度的不同,比较器阵列的组合形式有很多种。可以采用n个比较器将驱动电路输出vout的电压与n个参考电压vr1~vrn进行比较量化,经过一个时钟周期的比较,即可得到负载量化码dout。还可以采用一个比较器,将驱动电路输出vout的电压与n个参考电压vr1~vrn进行逐次比较量化,从而得到负载量化码dout,与比较器组合策略配套设置的还有n个参考电压vr1~vrn的设置,可以采用温度计码均匀间隔设置,或者二进制不同权重设置。因此,实际实施时可根据驱动芯片应用系统需求,选择合适的比较器类型和组合策略。

127.由于高速比较器存在一定的失调,并且比较器工作速度越高,失调越严重,为此需要对负载量化码dout进行误差过滤得到负载检测码dtest,误差过滤电路的实现根据负载量化码dout的类型和前端高速比较器阵列电路的组合实现策略有很大差异性。如果比较器阵列电路的采用n个比较器并行工作,则需要采用flash adc比较器失调校准的数字算法进行误差滤除。

128.如果比较器阵列电路的采用1个比较器复用工作,则需要采用sar adc失调校准的数字算法进行误差滤除。

129.图13是本发明实施例的负载判别电路框图。

130.如图13所示,负载判别电路包含2个分别用于存放负载检测码dtest和频率判别码dfin的寄存器1和寄存器2,以及对负载检测码dtest和频率判别码dfin进行计算处理的归一量化计算电路。寄存器1和寄存器2的数据输出受juge信号控制。归一量化计算电路输出的负载评估码dev,由负载检测码dtest和频率判别码dfin计算得到,计算公式为:dev=g*dtest/dfin。其中,g为增益系数,为大于1的正数。

131.图14是本发明实施例的控制器电路框图。

132.如图14所示,控制器电路的功能在于根据外界触发控制时钟信号和上电信号提供其他电路工作需要的控制信号。

133.控制器电路的输入端于外部电路连接,受外部的控制时钟信号clk-ctrl以及上电信号start-up控制。控制器电路的输出端与测试数据开关kcal、高速比较器阵列的控制信号输入端、误差过滤电路控制信号输入端、负载判别电路控制信号输入端、驱动电流选择电路控制信号输入端以及输入脉冲频率判别电路控制信号输入端连接。

134.控制器电路包括频率判别控制产生电路、开关信号产生电路、负载测试控制产生电路、负载判别控制产生电路、驱动电流控制产生电路、测试码产生电路以及计数器电路。

135.频率判别控制产生电路用于产生控制信号ctrl_fin并通过该控制信号ctrl_fin控制输入脉冲频率判别电路。

136.开关信号产生电路用于产生开关控制信号并通过该开关控制信号控制输入数据开关kin、测试数据开关kcal以及采样开关sw。

137.负载测试控制产生电路用于产生控制信号ctrl_test并通过该控制信号ctrl_test控制高速比较器阵列和误差过滤电路。

138.负载判别控制产生电路用于产生控制信号ctrl_ev并通过该控制信号ctrl_ev控制负载判别电路。

139.驱动电流控制产生电路用于产生控制信号ctrl_out并通过该控制信号ctrl_out控制驱动电流选择电路。

140.测试码产生电路用于产生负载测试信号dcal和测试时钟信号clkcal,通过负载测试信号dcal控制测试数据开关kcal,并通过测试时钟信号clkcal控制输入脉冲频率判别电路。

141.计数器电路,用于根据控制时钟信号clk-ctrl和上电信号start-up按照预定顺序提供产生上述各信号所需的触发信号。

142.本实施例中,输入脉冲频率判别电路的电路功能为采用测试时钟信号clkcal对输入数据din的频率进行比较量化,该功能可以采用鉴相器电路实现。

143.图15是本发明实施例的欠压保护电路结构图。

144.如图15所示,欠压保护电路用于实时检测低压电源电压vcc和低压地vss之间的电压差。一旦检测到两者的电压差值低于设计的基准电压vref,则欠压保护电路就发出信号,锁定电路使其停止工作。

145.电源电压被分压电阻r1,r2和r3实时检测,检测到的电压值v输入到比较器的负

端,与比较器正端的基准电压vref进行比较。其中,r3电阻值为可变值,受欠压保护信号uv信号控制。

146.当低压电源电压vcc正常时,监测电压比基准电压vref高,比较器输出低电平,欠压保护信号uv电位为低,r3为大电阻。

147.当vcc不正常时,监测电压比基准电压vref低,比较器输出高电平,欠压保护信号uv电位为高,r3改为小电阻,当监测电压进一步降低并反馈到比较器后,欠压保护电路就锁定电路的状态,保持输出不变。

148.图16是本发明实施例的过流保护电路结构图。

149.如图6所示,过流保护电路对流过被驱动的gan功率管上的电流进行采样,再通过比较器将采样结果与设置的基准电压进行比较。本实施例中,采用采样电阻对流过被驱动的gan功率管上的电流进行采样。在其他实施例中,也可以采用传感晶体管进行采样。

150.图6中ml为被驱动的低端igbt器件,电阻r1和r2为外接的两个采样电阻,其中r2为可调电阻,通过调整r2的大小,可以限定流过m1的最大电流。

151.电路的核心部分是比较器,电容用于消除信号中的噪声和干扰,反相器链用于实现对信号的倒相和整形。

152.过流保护电路的工作过程如下:

153.当电路不过流时,采样电压sd小于基准电压vref,比较器输出高电平,经过反相器后,短路保护信号oc电位为低。

154.当流过hemt上的电流超过既定值,采样电压sd大于基准电压vref,比较器输出低电平,短路保护信号oc电位翻转为高。

155.图17是本发明实施例的输出栅压钳位电路结构图。

156.如图17所示,栅压钳位电路具有第一pmos晶体管m1l、第二pmos晶体管m2l、nmos晶体管m3l、比较器、钳位反相器和2输入或门。

157.第一pmos晶体管m1l和nmos晶体管m3l的栅极同时连接到高侧预输出信号voutp,漏极同时连接到高侧输出信号ho、比较器的正输入端、第二pmos晶体管m2l的漏极以及2输入或门的第一输入端,

158.比较器的负输入端与高侧高压电源,其输出连接到钳位反相器的输入端,钳位反相器的输出端连接到2输入或门的第二输入端,2输入或门的输出端连接到第二pmos晶体管m2l的栅极;

159.第一pmos晶体管m1l和第二pmos晶体管m2l的源极同时连接到高侧高压电源。当高侧输出信号ho输出高电平出现过冲后,比较器将输出高电平信号,经反相器和延迟或门,驱动m2l晶体管导通,强制将高侧输出信号ho的过冲电压拉回vboot,从而起到高电平钳位功能,降低输出过冲影响。

160.实施例作用与效果

161.本实施例的用于增强型gan hem的高频智能半桥栅驱动电路,通过正反馈驱动电流增强技术减小电平移位电路的延迟,提高整体驱动电路速度。设置数控高精度死区时间产生电路对死区时间进行自适应精确设定,根据输入pwm脉冲信号的工作频率自适应设定死区时间长度,实现死区时间功耗损失的最小化降低死区时间设定而引起的功耗损失。

162.本实施例的用于增强型gan hem的高频智能半桥栅驱动电路,设置低侧和高侧高

效率输出驱动电路,可以根据负载大小和输入控制脉冲的频率自适应调整驱动电流,从而最大程度上提高驱动电路的电源效率。

163.本实施例的用于增强型gan hem的高频智能半桥栅驱动电路,采用短路保护电路和欠压保护电路对电路进行保护,在电路过流或电源电压异常时,可以锁定电路状态,提高驱动电路的可靠性。

164.本实施例的用于增强型gan hem的高频智能半桥栅驱动电路,设置栅压钳位电路,强制将过冲的高侧输出信号ho拉回vboot,从而起到高电平钳位功能,降低输出过冲影响。

165.上述实施例仅用于举例说明本发明的具体实施方式,而本发明不限于上述实施例的描述范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。