1.本发明涉及半导体技术领域,尤其是涉及一种半导体器件及半导体器件的制备方法。

背景技术:

2.现有技术一般在n型衬底上依次生长n型包覆层、n型波导层、有源层、p型波导层、p型包覆层以及p型接触层。通过一系列的工艺,制作成半导体器件,然后进行p型接触层朝下的倒装封装(p

‑

down封装)。这种p

‑

down封装p型面靠近热沉,有源区也距离热沉很近,虽然有利于散热,但是,p型接触层与热沉之间是通过金锡焊料焊接或者in焊料焊接的,二者之间焊接很牢固,一旦出现可靠性问题,无法完整取下进行失效分析。

3.而在p型衬底上依次生长p型包覆层、p型波导层、有源层、n型波导层、n型包覆层以及n型接触层,通过一系列工艺加工成半导体器件后,进行p型衬底朝下的正装封装,虽然这种半导体器件封装后进行失效分析的那侧外露,方便进行后期的失效分析,但是,此种半导体器件的实际发热区距离热沉比较远,不利于散热。

技术实现要素:

4.本发明的目的在于提供一种半导体器件及半导体器件的制备方法,以缓解现有技术中存在的p型衬底朝下的正装封装的半导体器件不利于散热的技术问题。

5.基于上述目的,本发明提供了一种半导体器件,包括p型衬底,所述p型衬底的上表面设置有外延层,所述外延层的上表面设置有上电极,所述p型衬底的下表面设置有多个凹槽,所述凹槽的深度小于所述p型衬底的厚度,所述p型衬底的下表面以及所述凹槽的槽壁和槽底均设置有下电极。

6.进一步地,在某些可选的实施例中,所述半导体器件还包括热沉,所述热沉与所述下电极的下表面固定连接。

7.进一步地,在某些可选的实施例中,所述半导体器件还包括石墨烯层,所述石墨烯层位于所述下电极与所述热沉之间。

8.进一步地,在某些可选的实施例中,所述石墨烯层设置有多个第一通孔,多个所述第一通孔沿所述石墨烯层的长度方向间隔设置,和/或,所述石墨烯层设置有第二通孔,所述第二通孔的延伸方向与所述凹槽的长度方向之间呈夹角设置。

9.进一步地,在某些可选的实施例中,所述石墨烯层设置有多个所述第一通孔和所述第二通孔,所述第二通孔的延伸方向与所述凹槽的长度方向平行,且所述第二通孔与所述凹槽的槽口相对应。

10.进一步地,在某些可选的实施例中,所述石墨烯层设置有第二通孔,所述第二通孔的延伸方向与所述凹槽的长度方向垂直。

11.进一步地,在某些可选的实施例中,所述p型衬底的厚度为105~125μm,所述凹槽的深度为50~100μm。

12.进一步地,在某些可选的实施例中,所述外延层包括从下至上依次设置的p型包覆层、p型波导层、有源层、n型波导层、n型包覆层、n型接触层。

13.基于上述目的,本发明还提供了一种半导体器件的制备方法,所述制备方法包括以下步骤:提供一p型衬底;在所述p型衬底的上表面形成所述外延层;在所述p型衬底的下表面形成多个所述凹槽,其中,所述凹槽的深度小于所述p型衬底的厚度;在所述p型衬底的下表面以及所述凹槽的内壁和槽底均形成下电极;在所述外延层的上表面形成上电极。

14.可选地,采用湿法刻蚀工艺,利用混合溶液对所述p型衬底的下表面进行腐蚀,以形成多个所述凹槽,其中,腐蚀温度为20~24℃,腐蚀时间为3~5min,所述混合溶液包括氨水和双氧水,且所述氨水与所述双氧水的体积比为1:5。

15.与现有技术相比,本发明的有益效果主要在于:本发明提供的半导体器件,包括p型衬底,所述p型衬底的上表面设置有外延层,所述外延层的上表面设置有上电极,所述p型衬底的下表面设置有多个凹槽,所述凹槽的深度小于所述p型衬底的厚度,所述凹槽的槽壁和槽底均设置有下电极。

16.基于该结构,本发明提供的半导体器件,通过在p型衬底的下表面设置多个凹槽,且凹槽的深度小于p型衬底的厚度,即凹槽没有贯穿整个p型衬底,能够有效地防止在形成凹槽的过程中破坏外延层,同时,将下电极设置在p型衬底的下表面以及凹槽的槽壁和槽底,能够与上电极相对应,且凹槽为下电极提供了胀缩空间,当下电极与热沉接触时,能够有效地减小下电极与热沉之间的热应力,有利于改善半导体器件整体的散热效果。

17.本发明提供的半导体器件的制备方法,用于制备本发明提供的半导体器件,该制备方法在p型衬底的下表面形成的多个凹槽没有贯穿整个p型衬底,能够有效地防止在形成凹槽的过程中破坏外延层,同时,将下电极设置在p型衬底的下表面以及凹槽的槽壁和槽底,能够与上电极相对应,且凹槽为下电极提供了胀缩空间,当下电极与热沉接触时,能够有效地减小下电极与热沉之间的热应力,有利于改善半导体器件整体的散热效果。

附图说明

18.为了更清楚地说明本发明具体实施方式或现有技术中的技术方案,下面将对具体实施方式或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图是本发明的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

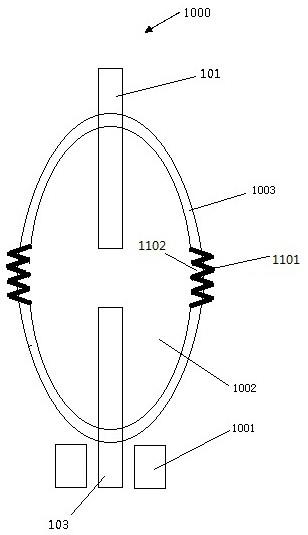

19.图1为本发明实施例一提供的半导体器件的结构示意图;图2为本发明实施例一提供的半导体器件的一种变形例的结构示意图;图3为本发明实施例一中的石墨烯层的俯视图;图4为本发明实施例一中的石墨烯层的一种变形例的俯视图;图5为本发明实施例一中的石墨烯层的另一种变形例的俯视图;图6为本发明实施例一提供的半导体器件另一种变形例的结构示意图;

图7为本发明实施例一中的石墨烯层的第三种变形例的俯视图;图8为本发明实施例三中的外延层的结构示意图;图9为本发明实施例三中的半导体器件的结构示意图;图10为本发明实施例三中的半导体器件的一种变形例的结构示意图。

20.图标:101

‑

p型衬底;102

‑

外延层;103

‑

凹槽;104

‑

上电极;105

‑

下电极;106

‑

石墨烯层;107

‑

第二通孔;108

‑

热沉;109

‑

p型包覆层;110

‑

p型波导层;111

‑

有源层;112

‑

n型波导层;113

‑

n型包覆层;114

‑

n型接触层;115

‑

第一通孔;116

‑

子层。

具体实施方式

21.下面将结合实施例对本发明的技术方案进行清楚、完整地描述,显然,所描述的实施例是本发明一部分实施例,而不是全部的实施例。基于本发明中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本发明保护的范围。

22.在本发明的描述中,需要说明的是,如出现术语“中心”、“上”、“下”、“左”、“右”、“竖直”、“水平”、“内”、“外”等,其指示的方位或位置关系为基于附图所示的方位或位置关系,仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此不能理解为对本发明的限制。此外,如出现术语“第一”、“第二”、“第三”仅用于描述目的,而不能理解为指示或暗示相对重要性。

23.在本发明的描述中,需要说明的是,除非另有明确的规定和限定,如出现术语“安装”、“相连”、“连接”应做广义理解,例如,可以是固定连接,也可以是可拆卸连接,或一体地连接;可以是机械连接,也可以是电连接;可以是直接相连,也可以通过中间媒介间接相连,可以是两个元件内部的连通。对于本领域的普通技术人员而言,可以具体情况理解上述术语在本发明中的具体含义。

24.实施例一参见图1至图7所示,本实施例提供了一种半导体器件,包括p型衬底101,p型衬底101的上表面设置有外延层102,外延层102的上表面设置有上电极104,p型衬底101的下表面设置有多个凹槽103,凹槽103的深度小于p型衬底101的厚度,p型衬底101的下表面以及凹槽103的槽壁和槽底均设置有下电极105。

25.基于该结构,本实施例提供的半导体器件,通过在p型衬底101的下表面设置多个凹槽103,且凹槽103的深度小于p型衬底101的厚度,即凹槽103没有贯穿整个p型衬底101,能够有效地防止在形成凹槽103的过程中破坏外延层102,同时,将下电极105设置在p型衬底101的下表面以及凹槽103的槽壁和槽底,能够与上电极104相对应,且凹槽103为下电极105提供了胀缩空间,当下电极105与热沉108接触时,能够有效地减小下电极105与热沉108之间的热应力,有利于改善半导体器件整体的散热效果。

26.p型衬底101的厚度过厚,不利于散热,p型衬底101的厚度过薄,不利于保证半导体器件的性能良好,同时,也不利于形成凹槽103,或者所形成的凹槽103的深度过浅,无法为下电极105提供足够的胀缩空间。因此,本实施例中的p型衬底101的厚度为105~125μm。

27.可选地,p型衬底101的厚度可以为但不限于105μm、110μm、115μm、120μm或125μm。

28.本实施例中,凹槽103为直槽。

29.需要说明的是,凹槽103不仅局限于直槽,还可以为其他形状的槽,例如:弧形槽。

30.本实施例中,凹槽103的深度为50~100μm。

31.凹槽103的深度过浅,无法为下电极105提供足够的胀缩空间。凹槽103的深度过深,在形成凹槽103的过程中破坏外延层102。在实际生产制作过程中,凹槽103的深度和p型衬底101的厚度相匹配,以改善半导体器件整体的散热效果。

32.可选地,凹槽103的深度可以为但不限于50μm、60μm、70μm、80μm、90μm或100μm。

33.为了保证半导体器件的性能,需要对半导体器件进行散热,因此,半导体器件还包括热沉108,热沉108的材质可以为铜,外延层102产生的热量从p型衬底101传导到热沉108上,通过热沉108实现散热。

34.本实施例中,参见图2所示,在下电极105与热沉108之间设置石墨烯层106,利用石墨烯的高横向导热率将外延层102传导到p型衬底101的热量分散开,再传导到热沉108,提高了半导体器件的散热效率,从而有效地降低了半导体器件功能区的结温,改善了半导体器件的性能。

35.在本实施例的一种可选的方案中,石墨烯层106完全覆盖热沉的上表面。

36.在该可选方案的一种可能的设计中,参见图3所示,石墨烯层106设置有多个第一通孔115,多个第一通孔115沿石墨烯层106的长度方向间隔设置。

37.本实施例中,石墨烯层106的长度方向与凹槽的长度方向一致。在该可能的设计中,第一通孔115设置在石墨烯层106与下电极105相贴合的位置。具体而言,参见图2所示,石墨烯层106与下电极105相贴合的位置有七个,每个位置均设置有多个第一通孔115,且每个位置上的多个第一通孔115沿石墨烯层106的长度方向间隔设置。通过设置第一通孔115,能够减小石墨烯层106与下电极105的接触面积,进而减小应变,使得半导体器件的热应力显著降低。

38.本实施例中,第一通孔115的形状为圆形。

39.需要说明的是,第一通孔115的形状不仅局限于圆形,还可以为矩形、三角形、椭圆形等形状。

40.在该可选方案的另一种可能的设计中,参见图4所示,石墨烯层设置有第二通孔107,第二通孔107的延伸方向与凹槽的长度方向之间呈夹角设置。

41.第二通孔107的延伸方向与凹槽103的长度方向之间呈夹角设置,优选地,在该另一种可能的设计中,夹角的角度不为零,这样的方式能够避免石墨烯层106与凹槽103的槽口正相对,使得石墨烯层106在减少石墨烯材料用量的情况下,确保更大的面积能够与下电极105直接接触,从而增加了散热面积,以便于实现导热功能,从而能够更有效地利用石墨烯层106。

42.该另一种可能的设计中,第二通孔107的延伸方向与凹槽103的长度方向垂直。这样的方式不仅便于生产加工,而且能够保证与p型衬底101的下表面相接触的下电极105与石墨烯层106之间是间断式接触,在保证对下电极105有效散热的基础上,尽可能地减小石墨烯层106与同一个下电极段的接触面积,使得半导体器件的热应力显著降低。

43.需要说明的是,当第二通孔107的延伸方向与凹槽103的长度方向之间所成的角为锐角时,也能够保证与p型衬底101的下表面相接触的下电极105与石墨烯层106之间是间断式接触,从而在保证对下电极105有效散热的基础上,减小石墨烯层106与同一个下电极段

的接触面积,使得半导体器件的热应力显著降低。

44.第二通孔107的数量为多个,可选地,第二通孔107的形状为矩形,第二通孔107的宽度为50~100μm,相邻两个第二通孔107之间的距离为50~100μm。

45.本实施例中,第二通孔107的宽度可以为但不限于50μm、60μm、70μm、80μm、90μm或100μm,相邻两个第二通孔107之间的距离为50μm、60μm、70μm、80μm、90μm或100μm。

46.可选地,相邻两个凹槽103之间的距离与相邻两个第二通孔107之间的距离大致相等,以使整个下电极105实现更加均匀的散热效果。

47.需要说明的是,第二通孔107的形状不仅局限于矩形,也可以为长圆形、椭圆形等形状。

48.在第三种可能的设计中,参见图5所示,石墨烯层106设置有多个第一通孔115和第二通孔107,多个第一通孔115沿石墨烯层106的长度方向间隔设置,第二通孔107的延伸方向与凹槽103的长度方向之间呈夹角设置。

49.该第三种可能的设计中,第二通孔107的延伸方向与凹槽103的长度方向平行,且第二通孔107与凹槽103的槽口相对应。也就是说,石墨烯层106是贴合在下电极105上的,以便于更好地散热,由于槽口处的石墨烯没有与下电极105接触,基本起不到散热作用,所以将第二通孔107设置在石墨烯层106的与凹槽103的槽口相对应的位置,能够在保证散热效果的前提下,减少石墨烯材料的用量。

50.在本实施例的另一种可选的方案中,参见图6所示,石墨烯层106包括多个子层116,每个子层116与贴合在p型衬底101的下表面的下电极105相贴合。为了清楚描述本实施例的技术方案,将贴合在p型衬底101的下表面的下电极105命名为下电极段,多个下电极段的宽度可以相等,也可以不相等;相邻两个下电极段之间为凹槽103的槽口,参见图6所示,本实施例中的下电极段的数量为七个。相应地,子层116的数量为七个,分别贴合在七个下电极段的下表面。

51.由于石墨烯在槽口处无法实现导热功能,该另一种可选的方案不在凹槽103的槽口处设置石墨烯,不仅能够减少石墨烯的用量,而且能够提高石墨烯的利用率。

52.参见图7所示,每个子层116均设置有多个第一通孔115,多个第一通孔115沿子层116的长度方向间隔设置。

53.进一步地,在某些可选的实施例中,石墨烯层106的厚度为100~1000μm。

54.本实施例中,石墨烯层106的厚度可以为但不限于100μm、200μm、300μm、400μm、500μm、600μm、700μm、800μm、900μm或1000μm。

55.本实施例还提供了一种用于制备本实施例提供的半导体器件的制备方法,该制备方法包括以下步骤:s1.提供一p型衬底101;p型衬底101可以根据所要制备的半导体器件的性能进行选择,例如p型砷化镓衬底。

56.s2.在p型衬底101的上表面形成外延层102;可选地,外延层102包括从下至上依次设置的p型包覆层109、p型波导层110、有源层111、n型波导层112、n型包覆层113、n型接触层114。

57.s3.在p型衬底101的下表面形成多个凹槽103,其中,凹槽103的深度小于p型衬底101的厚度;可选地,在步骤s3中,采用湿法刻蚀工艺对p型衬底101的下表面进行处理,以形

成多个凹槽103。

58.可选地,采用湿法刻蚀工艺对p型衬底101的下表面进行处理,包括以下步骤:利用混合溶液对p型衬底101的下表面进行腐蚀,腐蚀时间为4min,其中,混合溶液包括氨水和双氧水,且氨水与双氧水的体积比为1:5。

59.s4.在p型衬底101的下表面以及凹槽103的内壁和槽底均形成下电极105;s5.在外延层102的上表面形成上电极104。

60.本实施例提供的半导体器件的制备方法,用于制备本实施例提供的半导体器件,该制备方法在p型衬底101的下表面形成的多个凹槽103没有贯穿整个p型衬底101,能够有效地防止在形成凹槽103的过程中破坏外延层102,同时,将下电极105设置在凹槽103的槽壁和槽底,能够与上电极104相对应,且凹槽103为下电极105提供了胀缩空间,当下电极105与热沉108接触时,能够有效地减小下电极105与热沉108之间的热应力,有利于改善半导体器件整体的散热效果。

61.本实施例提供的半导体器件的制备方法,还包括步骤s6,采用金锡料填充焊接方式,将石墨烯层106焊接在下电极105的下表面。

62.可选地,在步骤s6中,先在石墨烯层106上设置第一通孔115,再将石墨烯层106焊接在下电极105的下表面。其中,第一通孔115设置在石墨烯层106与下电极105相贴合的位置。

63.可选地,在步骤s6中,先在石墨烯层106上设置第二通孔107,再将石墨烯层106焊接在下电极105的下表面。其中,第二通孔107的延伸方向与凹槽103的长度方向垂直。

64.可选地,在步骤s6中,先在石墨烯层106上设置第一通孔115和第二通孔107,再将石墨烯层106焊接在下电极105的下表面。其中,多个第一通孔115沿石墨烯层106的长度方向间隔设置,第二通孔107的延伸方向与凹槽103的长度方向平行,且第二通孔107与凹槽103的槽口相对应。

65.本实施例提供的半导体器件的制备方法,还包括步骤s7,采用金锡料填充焊接方式,将热沉108焊接在石墨烯层106的下表面。

66.需要说明的是,步骤s4和s5的顺序可以互换。

67.另外需要说明的是,步骤s6和s7的顺序也可以互换。

68.实施例二本实施例也提供了一种半导体器件,本实施例的半导体器件描述了石墨烯层106的另一种实现方案,除此之外的实施例一的技术方案也属于该实施例,在此不再重复描述。相同的零部件使用与实施例一相同的附图标记,在此参照对实施例一的描述。

69.在本实施例的一种可选的方案中,石墨烯层106完全覆盖热沉的上表面。这种方式无需在石墨烯层106上设置通孔,便于加工。

70.在本实施例的另一种可选的方案中,石墨烯层106包括多个子层116,每个子层116与贴合在p型衬底101的下表面的下电极105相贴合。

71.由于石墨烯在槽口处无法实现导热功能,该另一种可选的方案不在凹槽103的槽口处设置石墨烯,不仅能够减少石墨烯的用量,而且能够提高石墨烯层的利用率。

72.在本实施例的第三种可选的方案中,石墨烯层106包括多个子层116,多个子层116平行间隔设置,每个子层116的长度方向与凹槽103的长度方向之间所成的角的角度大于

0

°

,且小于等于90

°

,这样的方式不仅能够避免石墨烯层106与凹槽103的槽口正相对,使得石墨烯层106有更大的面积能够与下电极105直接接触,从而增加了散热面积,以便于实现导热功能,从而能够更有效地利用石墨烯层106,而且能够保证与p型衬底101的下表面相接触的下电极105与石墨烯层106之间是间断式接触,在保证对下电极105有效散热的基础上,尽可能地减小石墨烯层106与下电极105的接触面积,使得半导体器件的热应力显著降低。

73.该另一种可能的设计中,多个子层116平行且均匀间隔设置,子层116的长度方向与凹槽103的长度方向垂直。这样的方式不仅便于生产加工,而且能够使整个下电极105实现更加均匀的散热效果。

74.需要说明的是,多个子层116可以均不设置通孔,也可以保证至少一个子层116不设置通孔。

75.实施例三参见图8至图10所示,本实施例也提供了一种半导体器件,本实施例的半导体器件描述了外延层102的一种具体实现方案,除此之外的实施例一的技术方案也属于该实施例,在此不再重复描述。相同的零部件使用与实施例一相同的附图标记,在此参照对实施例一的描述。

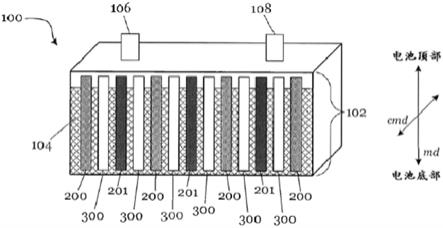

76.本实施例中,参见图8所示,外延层102包括从下至上依次设置的p型包覆层109、p型波导层110、有源层111、n型波导层112、n型包覆层113、n型接触层114。

77.进一步地,在某些可选的实施例中,p型包覆层109的厚度为500~1000μm,p型波导层110的厚度为100~500μm,有源层111的厚度为10~50μm,n型波导层112的厚度为100~1000μm,n型包覆层113的厚度为500~1000μm,n型接触层114的厚度为100~200μm。

78.参见图9所示,图9示出了包括本实施例中的外延层102的半导体器件。

79.参见图10所示,图10示出了包括本实施例中的外延层102以及石墨烯层106和热沉108的半导体器件。由于设置了石墨烯层106,该半导体器件的散热效率明显提高,有效地降低了有源层111的结温,改善了半导体器件的性能。

80.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。