1.本实用新型涉及多芯片封装技术领域,具体涉及一种多芯片封装结构及其微系统。

背景技术:

2.近年来,受到物理学上的限制,“摩尔定律”指导下的半导体技术在深亚微米阶段发展趋缓。为了满足计算机或电子系统朝着高带宽、高复杂度及功能多样性的方向发展,先进的多芯片封装技术成为持续优化系统性能和成本的关键创新路径,是“摩尔定律”在计算机或电子系统上的延续。

3.多芯片封装(multi

‑

chip package),即能将多个不同尺寸、不同制造工艺、不同材料的芯片集成整合到一个封装管壳里面,包括2d、2.5d、3d等芯片的堆叠方式,应用于先进的移动通信/计算、高带宽存储器等系统中。

4.由于在封装之前,多芯片封装中的各芯片之间并未通过互连线电性连接,或者即使多芯片封装完成后由于某一芯片未上电或者上电未完成,其输入输出电路处于悬空状态,导致芯片的工作状态不正确、漏电等情况的发生,进而干扰到故障芯片的筛查,影响多芯片封装的整个系统功能的调试。

5.因此,如何提高多芯片封装的系统功能调试效率,是目前亟需解决的技术问题。

技术实现要素:

6.本实用新型的目的是提供一种多芯片封装结构及其微系统,以提高多芯片封装的系统功能调试效率。

7.为实现上述目的,本实用新型实施例提供了以下方案:

8.第一方面,本实用新型实施例提供了一种多芯片封装结构,所述结构的内部包括第一芯片和第二芯片,所述结构还包括:

9.工作电压监测器,其输入端分别连接所述第一芯片的工作电压vdd1和所述第二芯片的工作电压vdd2,用以输出vdd1和vdd2的工作电压比较结果;

10.输入驱动器,其输入端连接所述工作电压监测器的输出端,用以根据所述工作电压比较结果,控制所述输入驱动器的工作模式,以使所述第一芯片工作在与所述输入驱动器的工作模式相适应的工作模式;其中,所述第二芯片通过所述输入驱动器接入所述第一芯片。

11.在一种可能的实施例中,所述工作电压监测器包括第一分压电路、第二分压电路、第一比较器、第二比较器、en_lvsft输出端和flag_vdd2on输出端;

12.所述第一分压电路,接于vdd2和地之间,包括第一分压点;

13.所述第二分压电路,接于vdd1和地之间,包括高压分压点和低压分压点;

14.所述第一分压点分别连接所述第一比较器的反向输入端和所述第二比较器的正向输入端;

15.所述高压分压点连接所述第一比较器的正向输入端;

16.所述低压分压点连接所述第二比较器的反向输入端;

17.所述第一比较器的输出端连接en_lvsft输出端;其中,所述en_lvsft输出端连接所述输入驱动器的en_ls输入端;

18.所述第二比较器的输出端连接flag_vdd2on输出端;其中,所述flag_vdd2on输出端连接所述输入驱动器的en_in输入端。

19.在一种可能的实施例中,所述输入驱动器中包括电平转换器levelshifter通路和缓冲器buffer通路;

20.其中,所述levelshifter通路用于在k

·

vdd1<vdd2≤vdd1时,将vdd2电压域输入信号转化为vdd1电压域输出信号,以使所述第一芯片工作在所述第二芯片上电完成的正常工作模式;所述buffer通路用于在vdd1<vdd2时,将vdd2电压域输入信号转化为vdd1电压域输出信号,以使所述第一芯片工作在所述正常工作模式;k为小于1的正数。

21.在一种可能的实施例中,所述levelshifter通路中:

22.所述输入驱动器的信号输入端依次经过第一反相器和第二反相器连接第一mos管的栅极;第二mos管和第三mos管并联在vdd1和第一mos管的源极之间;所述第一mos管的漏极接地;

23.第四mos管和第五mos管并联在第六mos管的漏极和地之间;第六mos管的源极接vdd1;第六mos管的栅极接第一mos管的源极;所述第三mos管的栅极连接所述第六mos管的漏极;第四mos管的栅极连接第一反相器的输出端;

24.第七mos管、第八mos管、第九mos管和第十mos管串接在vdd1和地之间;第六mos管的漏极分别连接第八mos管的栅极和第九mos管的栅极;

25.所述输入驱动器的en_in输入端连接第二mos管的栅极;所述en_in输入端还通过第三反相器连接第五mos管的栅极;

26.所述输入驱动器的en_ls输入端连接第七mos管的栅极;所述en_ls输入端还通过第四反相器连接第十mos管的栅极;

27.第八mos管的漏极通过第五反相器连接所述输入驱动器的信号输出端;

28.其中,第一mos管、第四mos管、第五mos管、第九mos管和第十mos管的沟道类型相同;第二mos管、第三mos管、第六mos管、第七mos管和第八mos管的沟道类型相同;第一mos管和第二mos管的沟道类型不同。

29.在一种可能的实施例中,所述buffer通路中:

30.第十一mos管、第十二mos管、第十三mos管和第十四mos管串接在vdd2和地之间;所述输入驱动器的信号输入端分别连接第十二mos管的栅极和第十三mos管的栅极;

31.所述en_ls输入端还连接第十一mos管的栅极;所述en_ls输入端还通过第四反相器连接第十四mos管的栅极;

32.第十二mos管的漏极通过第五反相器连接所述输入驱动器的信号输出端;

33.其中,第十一mos管和第十二mos管的沟道类型与第二mos管的沟道类型相同;第十三mos管和第十四mos管的沟道类型与第一mos管的沟道类型相同。

34.在一种可能的实施例中,所述输入驱动器还设有内部下拉模式或内部上拉模式,用于在vdd2≤k

·

vdd1时,输出下拉低平信号或上拉高平信号,以使所述第一芯片工作在所

述第二芯片未正常上电的默认工作模式。

35.在一种可能的实施例中,所述第一芯片通过输出驱动器接入所述第二芯片。

36.在一种可能的实施例中,所述输出驱动器包括第六反相器和第七反相器;

37.所述输出驱动器的信号输入端依次经第六反相器和第七反相器连接所述输出驱动器的信号输出端。

38.第二方面,本实用新型实施例提供了一种多芯片封装的微系统,包括:如第一方面中任一项所述的多芯片封装结构。

39.本实用新型与现有技术相比,具有如下的优点和有益效果:

40.本实用新型中的工作电压监测器能够获得第一工作电压vdd1和第二工作电压vdd2的工作电压比较结果,并能够根据该工作电压比较结果控制输入驱动器的工作模式,以使所述第一芯片工作在与所述输入驱动器的工作模式相适应的工作模式,减少了工作状态不正确、漏电等情况对芯片筛片等测试的干扰,提高了多芯片封装的系统功能调试效率。

附图说明

41.为了更清楚地说明本说明书实施例或现有技术中的技术方案,下面将对实施例中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本说明书的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

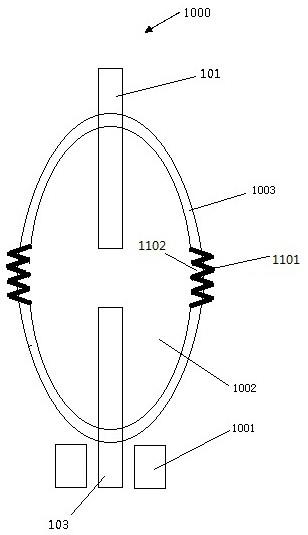

42.图1是一种典型的3d多芯片封装组成的微系统示意图;

43.图2是图1的微系统原理图;

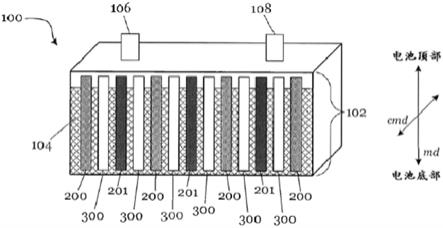

44.图3是本实用新型实施例提供的一种多芯片封装中芯片工作模式的控制方法的流程图;

45.图4是本实用新型实施例提供的一种多芯片封装结构的结构示意图;

46.图5是本实用新型实施例提供的一种多芯片封装结构的结构示意图;

47.图6是图5所示的多芯片封装结构中vdd2工作电压监测器的连接示意图;

48.图7是图5所示的多芯片封装结构中输入驱动器的连接示意图;

49.图8是图5所示的多芯片封装结构中输出驱动器的连接示意图;

50.图9是图5所示的多芯片封装结构的工作原理示意图;

51.图10是本实用新型实施例还提供了一种多芯片封装中芯片工作模式的控制装置。

52.附图标记说明:diea为第一芯片,dieb为第二芯片,100为工作电压监测器,101为第一比较器,102为第二比较器,103为第一分压电路,104为第二分压电路,200为输入驱动器,210为levelshifter通路,211为第一反相器,212为第二反相器,213为第三反相器,214为第四反相器,215为第五反相器,220为buffer通路,300为输出驱动器,301为第六反相器,302为第七反相器,m1为第一mos管,m2为第二mos管,m3为第三mos管,m4为第四mos管,m5为第五mos管,m6为第六mos管,m7为第七mos管,m8为第八mos管,m9为第九mos管,m10为第十mos管,m11为第十一mos管,m12为第十二mos管,m13为第十三mos管,m14为第十四mos管。

具体实施方式

53.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行

清楚、完整的描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例,基于本实用新型实施例,本领域普通技术人员所获得的所有其他实施例,都属于本实用新型实施例保护的范围。

54.图1是一种典型的3d多芯片封装组成的微系统示意图,其中包含有2颗芯片:芯片diea和dieb,其中两颗芯片的工作电压不同,芯片的功能可以相同也可以不同;信号互连线connector(例如硅通孔tsv、混合键合线hybridbonding等)可实现diea和dieb之间的电性连接,信号互连线bonding(例如普通键合线bonding wire、焊料凸点solder bump等)通过封装底座substrate中的金属走线实现芯片与芯片之间、芯片与外界之间的电性连接。

55.由于多芯片封装中的各个芯片工作在不同的电源域且实现相同或不同的功能,各个芯片需要合适的输入输出电路(即inputoutput电路,后文简称io电路),以实现不同芯片之间及芯片与外界之间的通信,从而实现一个完整的微系统功能。图2是图1的微系统原理图,diea由核心电路diea_core和输入输出电路ioa组成,实现如控制、计算等功能;dieb,由核心电路dieb_core和输入输出电路iob组成,实现如存储、数/模转换、数据交换等功能;输入输出电路ioa包含若干个输出驱动器和若干个输入驱动器,diea输出驱动器将diea_core处理后的信号增强驱动能力后通过互联线31输出到dieb的输入驱动器中,diea输入驱动器为vdd2到vdd1电平转换器(即levelshifter),将输入的vdd2电源域信号io_n转化到vdd1电源域后输送到diea_core121中。右侧的dieb工作在vdd2电源域,由核心电路dieb_core和输入输出电路iob组成;dieb_core实现其相应的功能(例如存储、数/模转换、数据交换等功能);输入输出电路iob包含若干个输出驱动器和输入驱动器,dieb输出驱动器将dieb_core处理后的信号增强驱动能力后通过互联线3n输出到diea11的输入驱动器,dieb输入驱动器为vdd1到vdd2电平转换器,将输入的vdd1电源域信号io_1转化到vdd2电源域后输送到dieb_core中。

56.本实用新型的实用新型人在对现有技术中多芯片封装的系统功能调试方案的效率不高的技术问题进行分析研究时,发现:

57.芯片封装前,各个芯片的io电路未通过互连线进行电性连接,其io电路的输入处于悬空状态,这可能导致芯片的工作状态不正确,同时存在漏电,从而干扰芯片的测试结果,不利于筛查坏的芯片。

58.即使多个芯片封装完成后,某一个die未上电或上电未完成,则与其相连的其他die中io电路的输入处于悬空状态,这可能导致其工作状态不确定,进而不利于整个系统功能的调试。

59.以上原因均影响了现有技术中多芯片封装的系统功能调试方案的效率。

60.另外,由于各个die工作在不同的电源域,有些die在不同工作模式下电源电压范围比较宽,由单个电平转换器(levelshifter)组成的输入驱动器,可能无法同时满足宽范围电源电压下的功能和性能的要求。

61.为此,本实用新型希望通过准确控制多芯片封装中芯片的工作模式,减少因为芯片不适当的工作模式对多芯片封装的系统功能调试的干扰,从而提高多芯片封装的系统功能的调试效率。

62.如图3所示为本实用新型实施例提供的一种多芯片封装中芯片工作模式的控制方法的流程图,该方法可以应用于下文所述多芯片封装结构中,具体包括步骤11至步骤12。

63.步骤11,获取第一工作电压vdd1和第二工作电压vdd2的工作电压比较结果。

64.其中,vdd1为第一芯片diea的工作电压;vdd2为第二芯片dieb的工作电压。

65.具体的,第一工作电压vdd1和第二工作电压vdd2的工作电压比较工作可以基于电压比较功能的工作电压监测器100来实现,具体包括步骤21。

66.步骤21,根据工作电压监测器100的输出信号,获取所述工作电压比较结果。

67.具体的,工作电压监测器100内部可以设置有电压比较器,以实现第一工作电压vdd1和第二工作电压vdd2的工作电压比较工作。

68.当然,还可以将第一工作电压vdd1和第二工作电压vdd2转换为对应的数字信号,直接使用该数字信号对应的数值大小来进行两者电压高低的比较,当然还可以基于本步骤的目的,使用其它方案来实现本步骤操作的方案,在此不予以限制。

69.步骤12,根据所述工作电压比较结果,控制输入驱动器200的工作模式,以使所述第一芯片diea工作在与所述输入驱动器200的工作模式相适应的工作模式。

70.其中,所述第二芯片dieb通过所述输入驱动器200接入所述第一芯片diea。

71.具体的,第一芯片diea与第二芯片dieb之间,由于输入输出线无法直接检测,第一芯片diea与第二芯片dieb之间可能未实现电连接;即使第一芯片diea与第二芯片dieb之间实现了电连接,第二芯片dieb可能处于未上电状态,也可能是处于上电未完成状态,此时第一芯片diea容易出现漏电、工作状态不正确等情形,影响多芯片封装的调试检测。

72.同时,有些情况下,输入信号的电压域范围过宽,由单个电平转换器(levelshifter)组成的输入驱动器200,可能无法同时满足功能和性能的要求,这就使得即使第一芯片diea以正常工作模式进行工作,也有可能出现性能不匹配等故障的发生。

73.本实施例中,将第一芯片diea的工作模式与输入驱动器200的工作模式相匹配,使第一芯片diea能够工作在正确的工作模式下,避免第一芯片diea工作在与输入驱动器200的工作模式不适应的工作模式,减少了工作状态不正确、漏电等情况对芯片探针测试的干扰,提高了多芯片封装的系统功能调试效率。

74.这里,本实施例还提供了输入驱动器200的控制方案,具体包括步骤31至步骤33。

75.步骤31,若所述工作电压比较结果中vdd1和vdd2满足vdd2≤k

·

vdd1,则将所述输入驱动器200调整为内部下拉模式或内部上拉模式,以使所述第一芯片diea工作在所述第二芯片dieb未正常上电的默认工作模式;其中,k为小于1的正数。

76.具体的,当所述工作电压比较结果中vdd1和vdd2满足vdd2≤k

·

vdd1时,说明第一芯片diea和第二芯片dieb之间出现了第一芯片diea与第二芯片dieb之间的电连接不正常或第二芯片dieb未上电或第二芯片dieb未完成上电或第二芯片dieb未正常上电情况,此时将输入驱动器200调整为内部下拉模式或内部上拉模式,直接向第一芯片diea输出下拉低电平信号或上拉高电平信号,触发第一芯片diea进入到应对第二芯片dieb未正常上电情况的默认工作模式。

77.具体的,k值的选取,可以基于实际应用场景的要求,灵活选择。

78.步骤32,若所述工作电压比较结果中vdd1和vdd2满足k

·

vdd1<vdd2≤vdd1,则控制所述输入驱动器200将vdd2电压域输入信号经levelshifter通路210转化为vdd1电压域输出信号,以使所述第一芯片diea工作在所述第二芯片dieb上电完成的正常工作模式。这里,levelshifter通路可以为一种电平转换电路,能够实现vdd1电压域与vdd2电压域之间

的转换。

79.具体的,当所述工作电压比较结果中vdd1和vdd2满足k

·

vdd1<vdd2≤vdd1时,本步骤直接采用输入驱动器200中的levelshifter通路210,对vdd2电压域输入信号进行转化,将该输入信号的电压限制在0至vdd1之间。levelshifter通路210可以采用现有的levelshifter电路来实现,在此不予以赘述。

80.步骤33,若所述工作电压比较结果中vdd1和vdd2满足vdd1<vdd2,则控制所述输入驱动器200将vdd2电压域输入信号经buffer通路220转化为vdd1电压域输出信号,以使所述第一芯片diea工作在所述正常工作模式。

81.具体的,当所述工作电压比较结果中vdd1和vdd2满足vdd1<vdd2时,本步骤直接采用输入驱动器200中的buffer通路220,对vdd2电压域输入信号进行转化,将该输入信号的电压限制在0至vdd1之间。buffer通路220可以采用现有的buffer电路来实现,在此不予以赘述。

82.本实施例通过步骤32和步骤33的配合,能够适应具有较宽电压域的vdd2电压域输入信号,提高了芯片的适应能力。

83.上述方法实施例可以基于下文所述的任一多芯片封装结构来实现,还可以使用其他多芯片封装结构来实现上述方法实施例,在此不予以限制。

84.基于与方法同样的实用新型构思,本实用新型实施例还提供了一种多芯片封装结构,该多芯片封装结构可以实现上述方法实施例。如图4所示为该多芯片封装结构的结构示意图,其中包含有2颗用以实现不同功能的第一芯片diea和第二芯片dieb。

85.该结构还包括:工作电压监测器100,其输入端分别连接第一芯片diea的工作电压vdd1和第二芯片dieb的工作电压vdd2,用以输出vdd1和vdd2的工作电压比较结果;输入驱动器200,其输入端连接工作电压监测器100的输出端,用以根据工作电压比较结果,控制输入驱动器200的工作模式,以使第一芯片diea工作在与输入驱动器200的工作模式相适应的工作模式;其中,第二芯片dieb通过输入驱动器200接入第一芯片diea。

86.具体的,第一芯片diea与第二芯片dieb之间,由于输入输出线无法直接检测,第一芯片diea与第二芯片dieb之间可能未实现电连接;即使第一芯片diea与第二芯片dieb之间实现了电连接,第二芯片dieb可能处于未上电状态,也可能是处于上电未完成状态,此时第一芯片diea容易出现漏电、工作状态不正确等情形,影响多芯片封装的调试检测。

87.同时,有些情况下,输入信号的电压域范围过宽,由单个电平转换器(levelshifter)组成的输入驱动器200,可能无法同时满足功能和性能的要求,这就使得即使第一芯片diea以正常工作模式进行工作,也有可能出现性能不匹配等故障的发生。

88.本实施例中,将第一芯片diea的工作模式与输入驱动器200的工作模式相匹配,使第一芯片diea能够工作在正确的工作模式下,避免第一芯片diea工作状态不正确、漏电等情况对芯片筛片测试的干扰,提高了多芯片封装的系统功能调试效率。

89.另外,本实施例通过电平转换器levelshifter通路210和缓冲器buffer通路220的配合,能够适应具有较宽电压域vdd2的输入信号,提高了芯片的适应能力。

90.如图5所示为本实用新型实施例提供的一种多芯片封装结构的结构示意图,图6是图5所示的多芯片封装结构中vdd2工作电压监测器的连接示意图的连接示意图。其中:工作电压监测器100为vdd2工作电压监测器,包括第一分压电路103、第二分压电路104、第一比

较器101、第二比较器102、en_lvsft输出端和flag_vdd2on输出端。

91.第一分压电路103,接于vdd2和地之间,包括第一分压点vr_vdd2。图5中采用了两个电阻串接的形式,构建了第一分压电路103,当然还可以使用其他分压电路的实现方式。

92.第二分压电路104,接于vdd1和地之间,包括高压分压点vrh_vdd1和低压分压点vrl_vdd1。vrh_vdd1的电压高于vrl_vdd1的电压,图6中采用三个电阻串接的形式,构建了第二分压电路104,当然还可以使用其他分压电路的实现方式。

93.第一分压点vr_vdd2分别连接第一比较器101的反向输入端和第二比较器102的正向输入端;高压分压点vrh_vdd1连接第一比较器101的正向输入端;低压分压点vrl_vdd1连接第二比较器的反向输入端。

94.第一比较器101的输出端连接en_lvsft输出端,其能够输出en_lvsft信号;其中,en_lvsft输出端连接输入驱动器200的en_ls输入端;第二比较器102的输出端连接flag_vdd2on输出端,其能够输出flag_vdd2on信号;其中,flag_vdd2on输出端连接输入驱动器200的en_in输入端。

95.en_lvsft信号为高电平信号或低电平信号,具体以en_lvsft信号的电压幅值来判断其为高电平信号或低电平信号,其中,高电平信号是指超过高压阈值的信号,低电平信号是指低于低压阈值的信号,例如当en_lvsft信号超过2.2v时,en_lvsft信号即为高电平信号,当en_lvsft信号低于0.5v时,en_lvsft信号即为低电平信号。

96.在图6所示的vdd2工作电压监测器的连接示意图中,当第一比较器101的正向输入端的电压大于其反向输入端的电压时,第一比较器101输出的en_lvsft信号为高电平信号;反之,第一比较器101输出的en_lvsft信号为低电平信号。

97.flag_vdd2on信号为高电平信号或低电平信号,具体以flag_vdd2on信号的电压幅值来判断其为高电平信号或低电平信号,其中,高电平信号是指超过高压阈值的信号,低电平信号是指低于低压阈值的信号,例如当flag_vdd2on信号超过2.2v时,flag_vdd2on信号即为高电平信号,当flag_vdd2on低于0.5v时,flag_vdd2on信号即为低电平信号。

98.在图6所示的vdd2工作电压监测器的连接示意图中,当第二比较器102的正向输入端的电压大于其反向输入端的电压时,第二比较器102输出的flag_vdd2on信号为高电平信号;反之,第二比较器102输出的flag_vdd2on信号为低电平信号。

99.本实施例中,基于en_lvsft信号的电平高低以及flag_vdd2on信号的电平高低,能够实现对vdd1和vdd2的比较,从而获得具体的工作电压比较结果。

100.如图7所示为图5所示的多芯片封装结构中输入驱动器的连接示意图,输入驱动器200中包括电平转换器levelshifter通路210和缓冲器buffer通路220;

101.其中,电平转换器levelshifter通路210用于在k

·

vdd1<vdd2≤vdd1时,将vdd2电压域输入信号转化为vdd1电压域输出信号,以使第一芯片diea工作在第二芯片dieb上电完成的正常工作模式;buffer通路220用于在vdd1<vdd2时,将vdd2电压域输入信号转化为vdd1电压域输出信号,以使第一芯片diea工作在正常工作模式;k为小于1的正数。

102.输入驱动器200还设有内部下拉模式或内部上拉模式,用于在所述工作电压比较结果中vdd1和vdd2满足vdd2≤k

·

vdd1时,输出下拉低平信号或上拉高平信号,以使第一芯片diea工作在第二芯片dieb未正常上电的默认工作模式。

103.具体的,当所述工作电压比较结果中vdd1和vdd2满足k

·

vdd1<vdd2≤vdd1时,本

步骤直接采用输入驱动器200中的levelshifter通路210,对vdd2电压域输入信号进行转化,将该输入信号的电压限制在0至vdd1之间。levelshifter通路210可以采用现有的levelshifter电路来实现,在此不予以赘述。

104.具体的,当所述工作电压比较结果中vdd1和vdd2满足vdd1<vdd2时,本步骤直接采用输入驱动器200中的缓冲器buffer通路220,对vdd2电压域输入信号进行转化,将该输入信号的电压限制在0至vdd1之间。buffer通路220可以采用现有的buffer电路来实现,在此不予以赘述。

105.具体的,k值的取值与第一分压电路103和第二分压电路104中的分压电阻的具体阻值有关,可以根据实际需要灵活设置。

106.图6的levelshifter通路210中:输入驱动器200的信号输入端依次经过第一反相器211和第二反相器212连接第一mos管m1的栅极;第二mos管m2和第三mos管m3并联在vdd1和第一mos管m1的源极之间;第一mos管m1的漏极接地。

107.第四mos管m4和第五mos管m5并联在第六mos管m6的漏极和地之间;第六mos管m6的源极接vdd1;第六mos管m6的栅极接第一mos管m1的源极;第三mos管m3的栅极连接第六mos管m6的漏极;第四mos管m4的栅极连接第一反相器211的输出端。

108.第七mos管m7、第八mos管m8、第九mos管m9和第十mos管m10串接在vdd1和地之间;第六mos管m6的漏极分别连接第八mos管m8的栅极和第九mos管m9的栅极。

109.输入驱动器200的en_in输入端连接第二mos管m2的栅极;en_in输入端还通过第三反相器213连接第五mos管m5的栅极。

110.输入驱动器200的en_ls输入端连接第七mos管m7的栅极;en_ls输入端还通过第四反相器214连接第十mos管m10的栅极。

111.第八mos管m8的漏极通过第五反相器215连接输入驱动器200的信号输出端。

112.其中,第一mos管m1、第四mos管m4、第五mos管m5、第九mos管m9和第十mos管m10的沟道类型相同;第二mos管m2、第三mos管m3、第六mos管m6、第七mos管m7和第八mos管m8的沟道类型相同;第一mos管m1和第二mos管m2的沟道类型不同。也即:第一mos管m1、第四mos管m4、第五mos管m5、第九mos管m9和第十mos管m10为pmos管时,第二mos管m2、第三mos管m3、第六mos管m6、第七mos管m7和第八mos管m8为nmos管;第一mos管m1、第四mos管m4、第五mos管m5、第九mos管m9和第十mos管m10为nmos管时,第二mos管m2、第三mos管m3、第六mos管m6、第七mos管m7和第八mos管m8为pmos管。

113.图6的buffer通路220中:第十一mos管m11、第十二mos管m12、第十三mos管m13和第十四mos管m14串接在vdd1和地之间;输入驱动器200的信号输入端分别连接第十二mos管m12的栅极和第十三mos管m13的栅极;en_ls输入端还连接第十一mos管m11的栅极;en_ls输入端还通过第四反相器214连接第十四mos管m14的栅极;第十二mos管m12的漏极通过第五反相器215连接输入驱动器200的信号输出端;其中,第十一mos管m11和第十二mos管m12的沟道类型与第二mos管m2的沟道类型相同;第十三mos管m13和第十四mos管m14的沟道类型与第一mos管m1的沟道类型相同。

114.第一芯片diea通过输出驱动器300接入第二芯片dieb。

115.具体的,输出驱动器300可以采用缓冲电路来实现。

116.这里提供一种典型的缓冲电路,来实现输出驱动器300,如图8所示为图5所示的多

芯片封装结构中输出驱动器的连接示意图,具体为:

117.输出驱动器300包括第六反相器301和第七反相器302;输出驱动器300的信号输入端依次经第六反相器301和第七反相器302连接输出驱动器300的信号输出端。

118.为了更清楚地说明本实施例提供的多芯片封装结构的工作过程,这里以图5所示的多芯片封装结构为例,说明本实施例的工作过程。

119.具体的,diea工作在vdd1电源域,diea_core实现其相应的功能(例如控制、计算等);diea的io电路ioa包含若干个输出驱动器300、若干个输入驱动器200和一个vdd2工作电压监测器100;输出驱动器300的输入端in连接至diea_core,输出端out连接至互联线31,将diea_core处理后的信号增强驱动能力后通过互联线31输出到dieb的输入驱动器中;diea的输入驱动器200的in输入端接互联线3n,en_in输入端和en_ls输入端分别接至vdd2工作电压监测器100的flag_vdd2on输出端和en_lvsft输出端,输出端out连接至diea_core,将输入的vdd2电源域信号io_n转化到vdd1电源域后输送到diea_core中;vdd2工作电压监测器100的pwrdet输入端通过电源互联线3ab2接至dieb的电源vdd2,输出信号flag_vdd2on和en_lvsft分别接至输入驱动器200的en_in输入端和en_ls输入端,通过监测vdd2的状态,控制输入驱动器200工作在不同的模式下。dieb的结构与diea相类似,在此不予以赘述。

120.vdd2工作电压监测器100由两组电阻分压串和两个比较器组成,其中vdd1经过电阻分压串分压后作为参考电压,与vdd2的分压值通过比较器比较,判断vdd2的电源状态,其输出信号flag_vdd2on信号和en_lvsft信号控制输入驱动器200工作在合适的模式下;输入驱动器200分levelshifter通路210和buffer通路220;输出驱动器300为由反相器组成的典型缓冲器。

121.如前所述,电压监测器通过监测对方电源的状态而控制输入驱动器200工作在不同的模式下,如图9所示为图5所示的多芯片封装结构的工作原理示意图,主要包含以下三种模式:(diea向dieb输出信号与dieb向diea输出信号相类似,这里以dieb向diea输出信号为例,说明本实施例的工作过程)

122.模式一:当dieb的电源电压vdd2低于k倍的diea的电源电压vdd1时(其中k为常数,例k=1/2),vdd2电压监测器的输出信号flag_vdd2on为低,en_lvsft为高,表明dieb未连接至diea(即多芯片封装前)或dieb未上电或上电未完成,则输入驱动电路内部默认下拉(或上拉),diea进入其默认工作模式。

123.模式二:当dieb的电源电压vdd2高于k倍的diea的电源电压vdd1且仍低于vdd1时,flag_vdd2on为高,en_lvsft为高,表明dieb已连接至diea(即多芯片封装后)或dieb上电已完成,则vdd2电源域的输入信号io_n经过输入驱动器200中levelshfiter通路转化成vdd1电源域的信号后送入diea_core,系统进入正常工作模式。

124.模式三:当dieb的电源电压vdd2高于diea的电源电压vdd1时,flag_vdd2on为高,en_lvsft为低,则vdd2电源域的输入信号io_n经过输入驱动器200中buffer通路220转化成vdd1电源域的信号后送入diea_core,系统进入正常工作模式。

125.本实施例与现有技术相比,具有如下的优点和有益效果:

126.1.各个die工作电源通过互联线(如电源互联线3ab1、3ab2)接入对方die,以监测对方die电源状态;根据各个电源的状态,自动控制输入驱动器200工作在合适的模式下,确

保io工作在正确的状态;

127.2.多芯片封装前,io电路中的输入驱动电路内部默认下拉(或上拉),芯片工作在默认的确定状态下,不存在漏电,便于通过芯片的探针(chip probing)测试而进行坏片筛查;

128.3.多芯片封装后,即使某一die的未上电或上电未完成,另外一个die的io工作状态亦确定,还可继续进行整个系统功能的调试;

129.4.各个die工作在不同的电压域,有些die不同工作模式下电源电压范围较宽,电源监测器根据电源状态控制输入驱动器200选择levelshifter通路210或buffer通路220,可同时满足功能和性能的要求;

130.5.以同样的方式,可扩展至第二芯片的控制方案;

131.6.以同样的方式,可扩展至多个die的封装方案,即每两个die之间均可采用相同或相似的连接及io信号处理方式。

132.基于与方法同样的实用新型构思,本实用新型实施例还提供了一种多芯片封装中芯片工作模式的控制装置,如图10所示为该装置的结构示意图,具体包括:

133.第一获取模块41,用于获取第一工作电压vdd1和第二工作电压vdd2的工作电压比较结果;其中,vdd1为第一芯片diea的工作电压;vdd2为第二芯片dieb的工作电压;

134.第一控制模块42,用于根据所述工作电压比较结果,控制输入驱动器200的工作模式,以使所述第一芯片diea工作在与所述输入驱动器200的工作模式相适应的工作模式;其中,所述第二芯片dieb通过所述输入驱动器200接入所述第一芯片diea。

135.在一种可能的实施例中,所述第一获取模块,包括:

136.第二获取模块,用于根据工作电压监测器100的输出信号,获取所述工作电压比较结果。

137.在一种可能的实施例中,所述第一控制模块,包括:

138.第二控制模块,用于在所述工作电压比较结果中vdd1和vdd2满足vdd2≤k

·

vdd1时,将所述输入驱动器200调整为内部下拉模式或内部上拉模式,以使所述第一芯片diea工作在所述第二芯片dieb未正常上电的默认工作模式;其中,k为小于1的正数;

139.第三控制模块,用于在所述工作电压比较结果中vdd1和vdd2满足k

·

vdd1<vdd2≤vdd1时,控制所述输入驱动器200将vdd2电压域输入信号经levelshifter通路210转化为vdd1电压域输出信号,以使所述第一芯片diea工作在所述第二芯片dieb上电完成的正常工作模式;

140.第四控制模块,用于在所述工作电压比较结果中vdd1和vdd2满足vdd1<vdd2时,控制所述输入驱动器200将vdd2电压域输入信号经buffer通路220转化为vdd1电压域输出信号,以使所述第一芯片diea工作在所述正常工作模式。

141.基于与方法同样的实用新型构思,本实用新型实施例还提供了一种多芯片封装的微系统,包括:如上文中任一项所述的多芯片封装结构。

142.基于与方法同样的实用新型构思,本实用新型实施例还提供了一种计算机系统,包括多芯片封装的微系统,所述多芯片封装的微系统执行上文任一所述的方法的步骤。

143.本实用新型实施例中提供的技术方案,至少具有如下技术效果或优点:

144.本实用新型实施例根据第一工作电压vdd1和第二工作电压vdd2的工作电压比较

结果,控制输入驱动器的工作模式,以使所述第一芯片工作在与所述输入驱动器的工作模式相适应的工作模式,减少了第一芯片工作状态不正确、漏电等情况对芯片探针测试的干扰,提高了多芯片封装的系统功能调试效率。

145.尽管已描述了本实用新型的优选实施例,但本领域内的技术人员一旦得知了基本创造概念,则可对这些实施例作出另外的变更和修改。所以,所附权利要求意欲解释为包括优选实施例以及落入本实用新型范围的所有变更和修改。

146.显然,本领域的技术人员可以对本实用新型进行各种改动和变型而不脱离本实用新型的精神和范围。这样,倘若本实用新型的这些修改和变型属于本实用新型权利要求及其等同技术的范围之内,则本实用新型也意图包括这些改动和变型在内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。