技术特征:

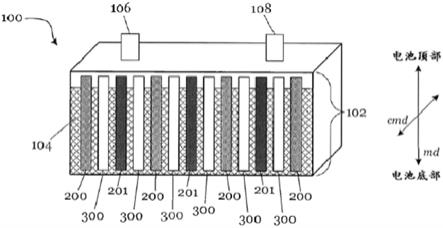

1.一种沟槽超级结功率mosfet器件,其特征在于,包括:n 衬底层;依次设置于所述n 衬底层上的第一缓冲层、第二缓冲层和第三缓冲层;其中,所述第一缓冲层、所述第二缓冲层和所述第三缓冲层的掺杂浓度依次递减;n

‑

漂移区,设置于所述第三缓冲层上;其中,所述n

‑

漂移区的掺杂浓度大于所述第三缓冲层的掺杂浓度,且小于所述第二缓冲层的掺杂浓度;至少两个p

‑

柱区,间隔设置于所述n

‑

漂移区内,其中,在所述n

‑

漂移区内形成有与所述p

‑

柱区相邻分布的若干n

‑

柱区,相邻所述n

‑

柱区和所述p

‑

柱区之间设置有第一绝缘层;若干第二绝缘层,分别设置于所述p

‑

柱区上;若干栅极,分别设置于所述第二绝缘层上;若干p

‑

体区,分别设置于所述栅极两侧;其中,相邻所述栅极和所述p

‑

体区之间设置有第三绝缘层;相邻所述p

‑

体区之间设置有第一沟槽;若干n 源区,分别设置于所述p

‑

体区上;其中,相邻所述栅极和所述n 源区之间设置有所述第三绝缘层;若干p 接触区,分别设置于所述n

‑

柱区上;若干第四绝缘层,分别设置于所述n 源区、所述栅极上;其中,所述n 源区12与所述第四绝缘层之间设置有所述第三绝缘层;源极,设置于所述第四绝缘层和所述第一沟槽上;漏极,设置于所述n 衬底层下表面,以构成超级结沟槽超级结功率mosfet器件。2.根据权利要求1所述的沟槽超级结功率mosfet器件,其特征在于,所述第一缓冲层的厚度为5μm~6μm、掺杂浓度为1

×

10

16

cm

‑3~5

×

10

16

cm

‑3。3.根据权利要求1所述的沟槽超级结功率mosfet器件,其特征在于,所述第二缓冲层的厚度为13μm~17μm、掺杂浓度为4

×

10

15

cm

‑3~5

×

10

15

cm

‑3。4.根据权利要求1所述的沟槽超级结功率mosfet器件,其特征在于,所述第三缓冲层的厚度为7μm~11μm、掺杂浓度为1

×

10

15

cm

‑3~1.5

×

10

15

cm

‑3。5.根据权利要求1所述的沟槽超级结功率mosfet器件,其特征在于,所述p

‑

柱区和所述n

‑

柱区厚度均为33μm~39μm、掺杂浓度均为3

×

10

15

cm

‑3~3.5

×

10

15

cm

‑3。6.一种沟槽超级结功率mosfet器件的制备方法,其特征在于,包括:在n 衬底层上生长掺杂浓度小于所述n 衬底层掺杂浓度的第一缓冲层;在所述第一缓冲层上生长掺杂浓度小于所述第一缓冲层掺杂浓度的第二缓冲层;在所述第二缓冲层上生长掺杂浓度小于所述第二缓冲层掺杂浓度的第三缓冲层;在所述第三缓冲层上生长掺杂浓度大于所述第三缓冲层掺杂浓度的p

‑

外延层;在所述p

‑

外延层上沉积第二绝缘层,并在所述第二绝缘层上沉积第一光刻胶;在所述第一光刻胶上形成第一掩膜,将未被所述第一掩膜覆盖的所述第一光刻胶、所述第二绝缘层和所述p

‑

外延层刻蚀掉直至所述第三缓冲层的上表面,形成至少两个p

‑

柱区,之后将剩余的所述第一光刻胶移除;在所述p

‑

柱区和所述第二绝缘层两侧沉积第一绝缘层;在所述第三缓冲层和所述第一绝缘层上生长n

‑

漂移区;在所述n

‑

漂移区沉积一层第二光刻胶,在所述第二光刻胶上形成第二掩膜,所述第二

掩膜的开口位置在所述p

‑

柱区正上方;将未被所述第二掩膜覆盖的所述n

‑

漂移区蚀掉直至所述第二绝缘层,形成第一沟槽,所述n

‑

漂移区未被刻蚀掉的部分形成n

‑

柱区,之后将剩余的所述第二光刻胶移除;在所述n

‑

柱区上和所述第一沟槽侧壁生长第三绝缘层;在所述第一沟槽内淀积栅极材料形成栅极;在所述n

‑

柱区顶部进行离子注入形成p

‑

体区;在所述p

‑

体区顶部进行离子注入形成n 源区;在所述栅极和所述第二绝缘层上生长第四绝缘层,在所述第四绝缘层表面沉积一层第三光刻胶,在所述第三光刻胶上形成第三掩膜,所述第三掩膜的开口位置与在所述n

‑

柱区正上方,将未被所述第三掩膜覆盖的所述第三光刻胶、所述第四绝缘层、所述第三绝缘层、所述n 源区和所述p

‑

体区直至所述n

‑

柱区上表面形成第二沟槽;在所述第二沟槽底部进行离子注入形成p 接触区,之后将剩余的所述第三光刻胶移除;在所述第二沟槽以及所述第四绝缘层上沉积源极金属作为源极,在所述n 衬底层下表面淀积漏极金属作为漏极,以完成沟槽超级结功率mosfet器件的制备。7.根据权利要求6所述的沟槽超级结功率mosfet器件的制备方法,其特征在于,所述在所述n 衬底层上生长第一缓冲层,包括:在所述n 衬底层上生长厚度为5μm~6μm、掺杂浓度为1

×

10

16

cm

‑3~5

×

10

16

cm

‑3的第一缓冲层。8.根据权利要求6所述的沟槽超级结功率mosfet器件的制备方法,其特征在于,所述在所述第一缓冲层上生长第二缓冲层,包括:在所述第一缓冲层上生长厚度为13μm~17μm、掺杂浓度为4

×

10

15

cm

‑3~5

×

10

15

cm

‑3的第二缓冲层。9.根据权利要求6所述的沟槽超级结功率mosfet器件的制备方法,其特征在于,所述在所述第二缓冲层上生长第三缓冲层,包括:在所述第二缓冲层上生长厚度为7μm~11μm、掺杂浓度为1

×

10

15

cm

‑3~1.5

×

10

15

cm

‑3的第三缓冲层。10.根据权利要求6所述的沟槽超级结功率mosfet器件的制备方法,其特征在于,所述在所述第三缓冲层上生长p

‑

外延层,包括:在所述第三缓冲层上生长厚度为33μm~39μm、掺杂浓度为3

×

10

15

cm

‑3~3.5

×

10

15

cm

‑3的p

‑

外延层。

技术总结

本发明公开了一种沟槽超级结功率MOSFET器件及其制造方法,该器件包括:N 衬底层;依次设置于N 衬底层上的第一、第二和第三缓冲层;N

技术研发人员:何艳静 赖建锟 袁嵩 江希 弓小武

受保护的技术使用者:西安电子科技大学

技术研发日:2021.06.18

技术公布日:2021/10/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。