技术特征:

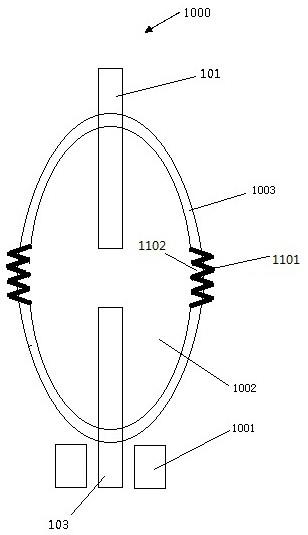

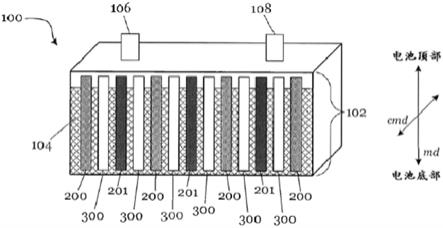

1.一种基于倒装焊的tsv多应力可靠性试验芯片结构,其特征在于,包括:硅衬底(11),所述硅衬底(11)上阵列设置有多个贯通所述硅衬底(11)上表面(111)和下表面(112)的tsv结构(113);顶部电极(12),位于所述硅衬底(11)的上表面上,并用于与所述tsv结构(113)的顶部相连接;底部电极(13),位于所述硅衬底(11)的下表面上,并用于与所述tsv结构(113)的底部相连接;在所述硅衬底(11)上,所述顶部电极(12)和所述底部电极(13)将选择的所述tsv结构(113)进行首尾相连形成菊花链互连结构,且在所述底部电极(13)远离所述tsv结构(113)的一侧相对应的设置有焊球(14)。2.根据权利要求1所述的tsv多应力可靠性试验芯片结构,其特征在于,在所述焊球(14)上设置有底部焊球电极(141);所述底部焊球电极(141)与所述底部电极(13)相对的分别位于所述焊球(14)的上下两侧;所述底部焊球电极(141)为规则片状结构,且其表面积大于所述焊球(14)的截面积。3.一种基于倒装焊的tsv多应力可靠性试验芯片结构,其特征在于,包括:硅衬底(11),所述硅衬底(11)上阵列设置有多个贯通所述硅衬底(11)上表面(111)和下表面(112)的tsv结构(113);顶部电极(12),位于所述硅衬底(11)的上表面上,并用于与所述tsv结构(113)的顶部相连接;焊球(14),所述焊球(14)与所述tsv结构(113)一一对应的设置在所述tsv结构(113)的底部;在所述硅衬底(11)上,所述顶部电极(12)将选择的所述tsv结构(113)的顶部同时连接形成开尔文链互连结构;所述开尔文链互连结构中的所述tsv结构(113)为三个。4.根据权利要求3所述的tsv多应力可靠性试验芯片结构,其特征在于,在所述焊球(14)上设置有底部焊球电极(141);所述底部焊球电极(141)与所述tsv结构(113)的底部相对的分别位于所述焊球(14)的上下两侧;所述底部焊球电极(141)为规则片状结构,且其表面积大于所述焊球(14)的截面积。5.一种用于权利要求1至4任一项所述的tsv多应力可靠性试验芯片结构的测试装置,其特征在于,包括:温湿度试验箱,用于对所述tsv多应力可靠性试验芯片结构(1)加载温度应力和湿度应力;振动台,用于对所述tsv多应力可靠性试验芯片结构(1)加载振动应力;电源及信号发生器,用于对所述tsv多应力可靠性试验芯片结构(1)加载电应力;测试电路板(2),用于对所述tsv多应力可靠性试验芯片结构(1)进行固定和电连接,以及对所述tsv多应力可靠性试验芯片结构(1)进行承载温度监测;测试夹具,用于固定所述测试电路板(2);

所述tsv多应力可靠性试验芯片结构(1)与所述测试电路板(2)焊接连接;信号采集装置,与所述测试电路板(2)电连接,用于采集电信号。6.根据权利要求5所述的测试装置,其特征在于,所述测试电路板(2)一侧的中间位置阵列设置有多个用于电连接的触点(21),以及与所述触点(21)相连接的接线端子(22);在所述测试电路板(2)上与所述触点(21)相邻的位置设置用于监测所述tsv多应力可靠性试验芯片结构(1)承载温度的热电偶;所述触点(21)与所述tsv多应力可靠性试验芯片结构(1)上的tsv结构(113)相对应的设置,且相互焊接连接。7.根据权利要求6所述的测试装置,其特征在于,所述测试电路板(2)还设置有固定安装位(23);所述固定安装位(23)在靠近所述测试电路板(2)边缘的位置设置有多个。8.根据权利要求6所述的测试装置,其特征在于,所述测试电路板(2)采用氧化铝陶瓷基板制成;所述测试夹具为矩形金属薄板;所述测试夹具上设置有用于安装所述测试电路板(2)的安装限位孔和用于可拆卸安装配重块的配重块安装位,以及与所述配重块安装位可拆卸连接的配重块;所述配重块安装位在所述安装限位孔的周围环绕设置有多个。9.一种用于权利要求5至8任一项所述的测试装置的测试方法,包括:s1.明确测试目标,即确定多应力类型及载荷参数、tsv多应力可靠性试验芯片结构(1)的类型、测试链路长度以及在所述测试电路板(2)上测试的接线端子(22);s2.确定tsv多应力可靠性试验芯片结构(1)的尺寸参数,设计掩膜版,并进行流片、测试和划片,获得用于测试的tsv多应力可靠性试验芯片结构(1)的裸片;s3.基于模态分析,并根据振动载荷频率范围确定测试电路板(2)的尺寸参数和所述测试夹具的尺寸参数,并设计制造所述测试电路板(2)和所述测试夹具;s4.选择链路类型,将具有相应链路类型的tsv多应力可靠性试验芯片结构(1)焊接到所述测试电路板(2)上;s5.将步骤s1中确定的接线端子(22)通过耐高温硅胶线连接到电源及信号发生器;s6.将所述测试电路板(2)安装在测试夹具上,对测试电路板(2)、所述测试夹具、tsv多应力可靠性试验芯片结构(1)组合体的固有频率进行测试,判断是否满足要求,若满足,则进行多应力可靠性试验与分析,否则,则重新调整所述测试夹具的结构。

技术总结

本发明涉及一种基于倒装焊的TSV多应力可靠性试验芯片结构、装置,芯片结构包括:硅衬底,硅衬底上阵列设置有多个贯通硅衬底上表面和下表面的TSV结构;顶部电极,位于硅衬底的上表面上,并用于与TSV结构的顶部相连接;底部电极,位于硅衬底的下表面上,并用于与TSV结构的底部相连接;在硅衬底上,将选择的TSV结构进行首尾相连形成菊花链或开尔文链互连结构,以及在与TSV结构相对应的位置设置有焊球。测试装置包括测试基板、试验夹具、多应力加载装置、信号采集装置等。本方案能够方便且全面地实现对实际的单个TSV或者多个TSV链路结构进行多应力加载,实现了通过试验手段科学全面且准确地评估TSV结构的可靠性。评估TSV结构的可靠性。评估TSV结构的可靠性。

技术研发人员:范政伟 陈循 刘泰成 蒋瑜 张书锋 汪亚顺

受保护的技术使用者:中国人民解放军国防科技大学

技术研发日:2021.07.09

技术公布日:2021/10/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。