基于倒装焊的tsv多应力可靠性试验芯片结构、装置

技术领域

1.本发明涉及半导体领域,尤其涉及一种基于倒装焊的tsv多应力可靠性试验芯片结构、装置。

背景技术:

2.随着先进芯片制程向3nm迈进,晶圆二维平面上晶体管密度逐渐接近物理极限,同时伴随着芯片研发成本的大幅度上升和研发周期的延长。因而,“摩尔定律”已经失灵。基于硅通孔(through silicon vias,tsv)结构的三维集成封装因此应运而生。三维集成封装通过tsv和堆叠的方式将晶圆进行垂直方向上的集成,从而获得更小尺寸、更高带宽、更低延迟、更高性能的封装芯片,并且还可以与微机电系统(mems)实现异构集成,获得功能集成、高性能、低成本的芯片产品。这种显著的优势使得三维封装芯片得到了学术界和工程界的重视,相关产品已经逐渐从实验室走向市场应用。

3.但是,三维封装芯片也同时带来了新的可靠性问题,需要对其进行科学准确的可靠性评估,才能使相关产品快速走向市场并提高用户使用信心。tsv结构是三维集成封装最为典型和关键的结构之一,在芯片中承担能量、信号通路和机械支撑功能,其可靠性直接影响芯片性能和服役寿命,因而需要对其进行科学全面且准确地可靠性试验与评估。基于tsv的三维封装芯片在其制造和使用过程中需要承受温度、湿度、电流/电压、振动等多应力耦合作用,因而对其进行可靠性试验与评估必须要考虑多应力的耦合影响。而当前已有tsv结构可靠性的研究基本以有限元热仿真为主,缺少试验研究。为数不多的试验研究设计了专用的tsv测试芯片,对其进行了热循环和电偏置测试,但是这些芯片及测试电路均不能实现多应力加载。

技术实现要素:

4.本发明的目的在于提供一种基于倒装焊的tsv多应力可靠性试验芯片结构、装置。

5.为实现上述发明目的,本发明提供一种基于倒装焊的tsv多应力可靠性试验芯片结构,包括:

6.硅衬底,所述硅衬底上阵列设置有多个贯通所述硅衬底上表面和下表面的tsv结构;

7.顶部电极,位于所述硅衬底的上表面上,并用于与所述tsv结构的顶部相连接;

8.底部电极,位于所述硅衬底的下表面上,并用于与所述tsv结构的底部相连接;

9.在所述硅衬底上,所述顶部电极和所述底部电极将选择的所述tsv结构进行首尾相连形成菊花链互连结构,且在所述底部电极远离所述tsv结构的一侧相对应的设置有焊球。

10.根据本发明的一个方面,在所述焊球上设置有底部焊球电极;

11.所述底部焊球电极与所述底部电极相对的分别位于所述焊球的上下两侧;

12.所述底部焊球电极为规则片状结构,且其表面积大于所述焊球的截面积。

13.为实现上述发明目的,本发明提供一种基于倒装焊的tsv多应力可靠性试验芯片结构,包括:

14.硅衬底,所述硅衬底上阵列设置有多个贯通所述硅衬底上表面和下表面的tsv结构;

15.顶部电极,位于所述硅衬底的上表面上,并用于与所述tsv结构的顶部相连接;

16.焊球,所述焊球与所述tsv结构一一对应的设置在所述tsv结构的底部;

17.在所述硅衬底上,所述顶部电极将选择的所述tsv结构的顶部同时连接形成开尔文链互连结构;

18.所述开尔文链互连结构中的所述tsv结构为三个。

19.根据本发明的一个方面,在所述焊球上设置有底部焊球电极;

20.所述底部焊球电极与所述tsv结构的底部相对的分别位于所述焊球的上下两侧;

21.所述底部焊球电极为规则片状结构,且其表面积大于所述焊球的截面积。

22.为实现上述发明目的,本发明提供一种前述的tsv多应力可靠性试验芯片结构的测试装置,包括:

23.温湿度试验箱,用于对所述tsv多应力可靠性试验芯片结构加载温度应力和湿度应力;

24.振动台,用于对所述tsv多应力可靠性试验芯片结构加载振动应力;

25.电源及信号发生器,用于对所述tsv多应力可靠性试验芯片结构加载电应力;

26.测试电路板,用于对所述tsv多应力可靠性试验芯片结构进行固定和电连接,以及对所述tsv多应力可靠性试验芯片结构进行承载温度监测;

27.测试夹具,用于固定所述测试电路板;

28.所述tsv多应力可靠性试验芯片结构与所述测试电路板焊接连接;

29.信号采集装置,与所述测试电路板电连接,用于采集电信号。

30.根据本发明的一个方面,所述测试电路板一侧的中间位置阵列设置有多个用于电连接的触点,以及与所述触点相连接的接线端子;

31.在所述测试电路板上与所述触点相邻的位置设置用于监测所述tsv多应力可靠性试验芯片结构承载温度的热电偶;

32.所述触点与所述tsv多应力可靠性试验芯片结构上的tsv结构相对应的设置,且相互焊接连接。

33.根据本发明的一个方面,所述测试电路板还设置有固定安装位;

34.所述固定安装位在靠近所述测试电路板边缘的位置设置有多个。

35.根据本发明的一个方面,所述测试电路板采用氧化铝陶瓷基板制成;

36.所述测试夹具为矩形金属薄板;

37.所述测试夹具上设置有用于安装所述测试电路板的安装限位孔和用于可拆卸安装配重块的配重块安装位,以及与所述配重块安装位可拆卸连接的配重块;

38.所述配重块安装位在所述安装限位孔的周围环绕设置有多个。

39.为实现上述发明目的,本发明提供一种用于前述的测试装置的测试方法,包括:

40.s1.明确测试目标,即确定多应力类型及载荷参数、tsv多应力可靠性试验芯片结构的类型、测试链路长度以及在所述测试电路板上测试的接线端子;

41.s2.确定tsv多应力可靠性试验芯片结构的尺寸参数,设计掩膜版,并进行流片、测试和划片,获得用于测试的tsv多应力可靠性试验芯片结构的裸片;

42.s3.基于模态分析,并根据振动载荷频率范围确定测试电路板的尺寸参数和所述测试夹具的尺寸参数,并设计制造所述测试电路板和所述测试夹具;

43.s4.选择链路类型,将具有相应链路类型的tsv多应力可靠性试验芯片结构焊接到所述测试电路板上;

44.s5.将步骤s1中确定的接线端子通过耐高温硅胶线连接到电源及信号发生器;

45.s6.将所述测试电路板安装在测试夹具上,对测试电路板、所述测试夹具、tsv多应力可靠性试验芯片结构组合体的固有频率进行测试,判断是否满足要求,若满足,则进行多应力可靠性试验与分析,否则,则重新调整所述测试夹具的结构。

46.根据本发明的一种方案,本方案不仅能够实现单一应力的加载测试,还能够方便且全面地实现对实际的tsv芯片结构进行多应力(温度、电流/电压、湿度、振动)加载,实现了通过试验手段科学全面且准确地评估tsv结构的可靠性。

47.根据本发明的一种方案,本方案的tsv多应力可靠性试验芯片结构通过一侧的电极即可实现任意一个tsv结构的单独或组合引出,具有灵活多变的测试样本量,具备成本低、柔性高、模块化的特点,可为tsv结构的可靠性试验与评估提供硬件基础。

48.根据本发明的一种方案,通过采用在tsv上设置电极的方式不仅能够实现多个tsv结构的多样化连接,还能够方便采用焊球基于电极实现tsv结构的引出,对本发明的灵活测试提供了有效保障。

49.根据本发明的一种方案,有效解决了bga倒装焊的芯片可靠性测试难度大的问题,实现了测试的稳定可靠,以及灵活多样,不仅成本低,而且测试效率高。

50.根据本发明的一种方案,本发明的芯片结构,可以有选择的实现对单个tsv和多个tsv链路进行多应力试验。

51.根据本发明的一种方案,本发明在进行试验的实施过程中,可以对测试装置固有频率进行调整和修正,从而满足振动测试需要,提高了本方案的测试灵活性和适用性。

52.根据本发明的一种方案,通过芯片结构、测试电路板、测试夹具、多应力加载装置(温湿度试验箱、振动台、电源及信号发生器等)、信号采集装置所组成的整体有效实现了多应力条件下的可靠性测试。其中芯片结构的链路、电极以及倒装焊球设计提供了可供选择的被测对象,测试电路板和测试夹具的特殊设计提供了多应力加载的途径,多应力加载装置以及信号采集系统提供了多应力来源与信号采集。

53.根据本发明的一种方案,测试夹具及配重块的设计,可以确保测试装置固有频率处于试验目标频率范围内,进而方便地进行振动应力加载。

附图说明

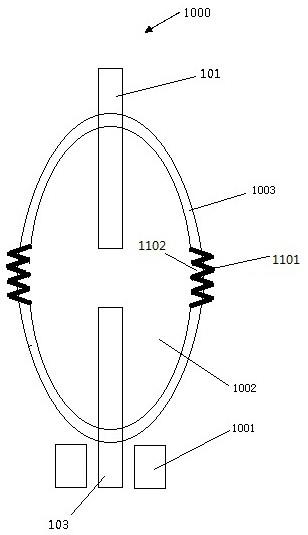

54.图1是示意性表示根据本发明的一种实施方式的tsv多应力可靠性试验芯片结构的结构图;

55.图2是示意性表示图1中x位置的结构放大图;

56.图3是示意性表示根据本发明的一种实施方式的tsv结构的结构图;

57.图4是示意性表示根据本发明的另一种实施方式的tsv多应力可靠性试验芯片结

构的结构图;

58.图5是示意性表示图4中y位置的电路连接结构放大图;

59.图6是示意性表示根据本发明的一种实施方式的tsv多应力可靠性试验芯片结构的下表面结构图;

60.图7是示意性表示根据本发明的一种实施方式的tsv多应力可靠性试验芯片结构的下表面上底部焊球电极的布置结构图;

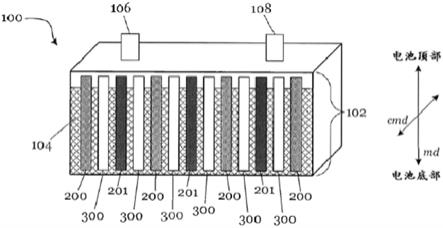

61.图8是示意性表示根据本发明的一种实施方式的测试线路板的结构图;

62.图9是示意性表示根据本发明的一种实施方式的测试线路板的背面结构图;

63.图10是示意性表示根据本发明的一种实施方式的测试线路板与tsv多应力可靠性试验芯片结构的组装结构图;

64.图11是示意性表示根据本发明的一种实施方式的测试方法的流程图。

具体实施方式

65.为了更清楚地说明本发明实施方式或现有技术中的技术方案,下面将对实施方式中所需要使用的附图作简单地介绍。显而易见地,下面描述中的附图仅仅是本发明的一些实施方式,对于本领域普通技术人员而言,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

66.在针对本发明的实施方式进行描述时,术语“纵向”、“横向”、“上”、“下”、“前”、“后”、“左”、“右”、“竖直”、“水平”、“顶”、“底”、“内”、“外”所表达的方位或位置关系是基于相关附图所示的方位或位置关系,其仅是为了便于描述本发明和简化描述,而不是指示或暗示所指的装置或元件必须具有特定的方位、以特定的方位构造和操作,因此上述术语不能理解为对本发明的限制。

67.下面结合附图和具体实施方式对本发明作详细地描述,实施方式不能在此一一赘述,但本发明的实施方式并不因此限定于以下实施方式。

68.结合图1和图2所示,根据本发明的一种实施方式,本发明的一种基于倒装焊的tsv多应力可靠性试验芯片结构,包括:硅衬底11,顶部电极12,底部电极13。在本实施方式中,硅衬底11上阵列设置有多个贯通硅衬底11上表面111和下表面112的tsv结构113;顶部电极12位于硅衬底11的上表面上,并用于与tsv结构113的顶部相连接;底部电极13位于硅衬底11的下表面上,并用于与tsv结构113的底部相连接。在本实施方式中,在硅衬底11上,顶部电极12和底部电极13将选择的tsv结构113进行首尾相连形成菊花链互连结构,且在底部电极13远离tsv结构113的底部相对应的设置有焊球14。

69.结合图1和图2所示,根据本发明的一种实施方式,在焊球14上设置有底部焊球电极141。在本实施方式中,底部焊球电极141与底部电极13相对的分别位于焊球14的上下两侧。在本实施方式中,底部焊球电极141为规则片状结构,且其表面积大于焊球14的截面积。

70.根据本发明,通过在焊球14上设置底部焊球电极141有效的提高了tsv结构113的焊接面积对保证本发明的焊接稳定有利,同时还有效降低了焊接难度。

71.在本实施方式中,顶部电极、底部电极和底部焊球电极采用铜电极,其宽度和厚度需要计算其电阻来确定进而确保链路中电极的电阻远低于tsv电阻,从而降低链路中非tsv部分对试验结果的影响。

72.在本实施方式中,焊球位于底部焊球电极的中心位置。在本实施方式中,底部焊球电极为矩形电极,底部焊球电极的尺寸远大于焊球尺寸。焊球植于电极中心处,便于芯片以倒装焊方式安装到测试基板上。以倒装焊连接到基板为三维封装芯片中最为常见的tsv连接方式,这样的安装方式接近tsv实际服役情况,可以使试验结果更真实地反映实际情况。另外,倒装焊球使得芯片与基板存在一定间隙(由焊球尺寸决定),从而使得芯片更充分地与试验环境接触,进而更充分地加载温度和湿度应力。

73.如图3所示,根据本发明的一种实施方式,tsv结构113在三维芯片中承担着信号、能量通路以及机械支撑功能。在本实施方式中,硅衬底11上设置的tsv结构113包括硅通孔11a,附着在硅通孔11a内侧面上的绝缘层11b,附着在绝缘层11b内侧面上的隔离层11c,附着在隔离层11c上的种子层11d,以及填充在种子层11d中的柱状体11e;柱状体11e采用导电材料填充而成,在其填充成型后整体呈柱状,其相对的两端分别处于硅衬底11的上表面111和下表面112上。在本实施方式中,在柱状体11e的相对两端还设置有一定厚度的重分布层11f,重分布层11f的材料也为导电材料,其可设置为与柱状体11e一致的导电材料,也可以为不同的,可根据需要进行设置。

74.在本实施方式中,硅通孔11a采用深硅刻蚀、化学气相沉积、溅射、电镀、化学机械抛光等工艺在硅晶圆上制备的孔。

75.在本实施方式中,绝缘层11b采用二氧化硅制成;隔离层11c采用金属钽制成;种子层11d采用沉积铜制成;柱状体11e采用电镀铜制成;重分布层11f采用金属铜制成。

76.结合图1和图2所示,根据本发明的一种实施方式,在硅衬底11上,顶部电极12和底部电极13将选择的tsv结构113进行首尾相连形成菊花链互连结构。在本实施方式中,顶部电极12和底部电极13均为长条状的结构,且通过顶部电极12和底部电极13的端部分别与tsv结构113的顶底两端连接。在本实施方式中,可选取硅衬底11上的部分或全部tsv结构113进行菊花链互连结构的搭建。在本实施方式中,在硅衬底11的上表面111上,将顶部电极12相对的两端分别与相邻的两个tsv结构113的顶部相连接,其中,顶部电极12由处于菊花链互连结构起始位置的tsv结构113开始,通过顶部电极12将相邻的tsv结构113两两相连;在硅衬底11的下表面112上,将底部电极13与tsv结构113的底部两两相连,其中底部电极13与顶部电极12是相对错位设置的;通过上述设置,实现了各tsv结构113的首尾连接。

77.在本实施方式中,在底部电极13远离tsv结构113的一侧上设置焊球14以实现电极的引出。其中,焊球14的设置数量与tsv结构113的数量相一致。

78.在本实施方式中,tsv结构113中硅通孔11a的直径d,tsv结构113间的节距p,设置tsv结构113的硅衬底11的厚度t,硅衬底11的长度l和硅衬底11的宽度w等关键参数均根据需要搭建的菊花链互连结构预先设置完成。此外,还可通过预先改变上述参数,以使得本方案的芯片结构能够用于探究不同参数(如孔径、节距等)对tsv结构连接构成的菊花链互连结构的可靠性的影响。

79.在本实施方式中,在同一硅衬底11可设置多个菊花链互连结构,以实现同一硅衬底11上可以完成多个样本量的试验。

80.结合图4和图5所示,根据本发明的另一种实施方式,本发明的一种基于倒装焊的tsv多应力可靠性试验芯片结构,包括:硅衬底11,顶部电极12,焊球14。在本实施方式中,硅衬底11上阵列设置有多个贯通硅衬底11上表面111和下表面112的tsv结构113;顶部电极

12,位于硅衬底11的上表面上,并用于与tsv结构113的顶部相连接;焊球14与tsv结构113一一对应的设置在tsv结构113的底部。在本实施方式中,在硅衬底11上,顶部电极12将选择的tsv结构113的顶部同时连接形成开尔文链互连结构;其中,开尔文链互连结构中的tsv结构113为三个。

81.结合图4和图5所示,根据本发明的另一种实施方式,在焊球14上设置有底部焊球电极141。在本实施方式中,底部焊球电极141与tsv结构113的底部相对的分别位于焊球14的上下两侧;底部焊球电极141为规则片状结构,且其表面积大于焊球14的截面积。

82.在本实施方式中,顶部电极和底部焊球电极采用铜电极,其宽度和厚度需要计算其电阻来确定进而确保链路中电极的电阻远低于tsv电阻,从而降低链路中非tsv部分对试验结果的影响。

83.在本实施方式中,焊球位于底部焊球电极的中心位置。在本实施方式中,底部焊球电极为矩形电极,底部焊球电极的尺寸远大于焊球尺寸。焊球植于电极中心处,便于芯片以倒装焊方式安装到测试基板上。以倒装焊连接到基板为三维封装芯片中最为常见的tsv连接方式,这样的安装方式接近tsv实际服役情况,可以使试验结果更真实地反映实际情况。另外,倒装焊球使得芯片与基板存在一定间隙(由焊球尺寸决定),从而使得芯片更充分地与试验环境接触,进而更充分地加载温度和湿度应力。

84.在本实施方式中,tsv结构113的设置方式与前述设置方式一致,在此不再赘述。

85.结合图4和图5所示,根据本发明的另一种实施方式,在硅衬底11上,顶部电极12将选择的tsv结构113的顶部同时连接,焊球14与选择的tsv结构113的底部一一对应设置形成开尔文链互连结构。在本实施方式中,顶部电极12为长条状的结构,且通过顶部电极12的端部与tsv结构113的顶端连接。在本实施方式中,在同一硅衬底11可设置至少一个开尔文链互连结构。其中,每个开尔文链互连结构中的tsv结构113选择设置有三个。通过上述设置,每三个tsv结构113构成一个开尔文链互连结构,可采用四线法测试单个tsv结构113的电阻,同时还兼顾了消除电极电阻影响的优点。

86.在本实施方式中,tsv结构113通过设置焊球14以实现电极的引出。其中,焊球14的设置数量与tsv结构113的数量相一致。

87.在本实施方式中,tsv结构113中硅通孔11a的直径d,tsv结构113间的节距p,设置tsv结构113的硅衬底11的厚度t,硅衬底11的长度l和硅衬底11的宽度w等关键参数均根据需要搭建的开尔文链互连结构预先设置完成。此外,还可通过预先改变上述参数,以使得本方案的芯片结构能够用于探究不同参数(如孔径、节距等)对tsv结构连接构成的开尔文链互连结构的可靠性的影响。

88.在本实施方式中,在同一硅衬底11可设置多个开尔文链互连结构,以实现同一硅衬底11上可以完成多个样本量的试验。

89.根据本发明的一种实施方式,本发明中前述的具有菊花链互连结构的芯片结构和具有开尔文链互连结构的芯片结构均通过设计掩膜版并采用成熟工艺流片,其中,可将两种芯片在同一片晶圆上进行流片,划片后可得到相应芯片裸片,裸片外尺寸为:l(长)

×

w(宽)

×

t(厚)。为了能够直接将温度和湿度直接加载到tsv结构113,不再对裸片进行封装。然后对芯片进行测试,淘汰不合格的裸片。

90.本发明的tsv多应力可靠性试验芯片结构通过上述设置的结构可直接焊接到相应

的测试线路板上即可连接到数字采集系统进行测试。而且本方案基于上述结构实现了在多应力环境下的可靠性测试。

91.根据本发明的一种实施方式,本方案中所述的应力是指可靠性工程领域中的“广义应力”,包括电/磁、力/力矩等工作载荷,以及温度、湿度、电、振动等环境应力,与力学上的“应力”概念存在区别。而本发明所设计的多应力可靠性试验,主要针对温度、湿度、电、振动四种应力。

92.为实现上述多应力的可靠性测试,在本方案中采用相应的测试装置实现。

93.根据本发明的一种实施方式,本发明提供一种用于前述的tsv多应力可靠性试验芯片结构的测试装置,包括:温湿度试验箱、振动台、电源及信号发生器、测试电路板2、测试夹具和信号采集装置。在本实施方式中,温湿度试验箱用于对tsv多应力可靠性试验芯片结构1加载温度应力和湿度应力;振动台用于对tsv多应力可靠性试验芯片结构1加载振动应力;电源及信号发生器用于对tsv多应力可靠性试验芯片结构1加载电应力;测试电路板2用于对tsv多应力可靠性试验芯片结构1进行固定和电连接,以及对tsv多应力可靠性试验芯片结构1进行承载温度监测。测试夹具用于固定测试电路板2并与振动台相连接。在本实施方式中,tsv多应力可靠性试验芯片结构1与测试电路板2焊接连接,其中,tsv多应力可靠性试验芯片结构1可通过焊球14与测试电路板2直接焊接连接,或通过底部焊球电极141与测试电路板2焊接连接。信号采集装置,与所述测试电路板2电连接,用于采集电信号。

94.结合图8和图9所示,根据本发明的一种实施方式,测试电路板2一侧的中间位置阵列设置有多个用于电连接的触点21,以及与触点21相连接的接线端子22。在本实施方式中,触点21与tsv多应力可靠性试验芯片结构1上的tsv结构113相对应的设置,且相互焊接连接。在本实施方式中,阵列设置的触点21在测试电路板2一侧的中间位置构成用于tsv多应力可靠性试验芯片结构1倒装焊的电极矩阵,其尺寸需要根据tsv多应力可靠性试验芯片结构1外形尺寸和底部的底部焊球电极141尺寸进行设计,具体包括:底部焊球电极141的外形尺寸l(长)

×

w(宽),底部焊球电极141的电极边长(n_pad),(参见图6和图7),底部焊球电极141的电极间隙(g_pad)(参见图6和图7),底部焊球电极141的电极矩阵边长(m)(参见图6和图7)。

95.在本实施方式中,在测试电路板2上与触点21相邻的位置设置用于监测tsv多应力可靠性试验芯片结构1承载温度的热电偶。通过上述设置,可有效实现对测试过程中的tsv多应力可靠性试验芯片结构1的承载温度进行实施监测,以保证测试过程的多应力的准确采集。

96.在本实施方式中,测试电路板2为矩形双层板,其外形尺寸为:lp(长)

×

wp(宽)。

97.如图10所示,在本实施方式中,测试电路板2为tsv多应力可靠性试验芯片结构1提供机械支撑、电气连接、安装固定作用,并且需要为多应力加载提供硬件条件。因此,试验测试中,直接对测试电路板2进行温度、湿度加载,测试电路板2上的裸片(即tsv多应力可靠性试验芯片结构)可以与温湿度环境充分接触。为了耐高温/低温、耐湿,基板采用氧化铝陶瓷材料,且设置的触点采用沉金工艺处理。

98.结合图8和图9所示,根据本发明的一种实施方式,测试电路板2还设置有固定安装位23。在本实施方式中,固定安装位23在靠近测试电路板2边缘的位置设置有多个。在本实施方式中,测试电路板2通过固定安装位23采用罗伞连接的方式安装到振动台的测试夹具

上,以实现其稳定连接。

99.根据本发明的一种实施方式,将接线端子22通过导线连接到电源及信号发生器即可实现加载电应力或者测试电参数。通过上述设置,将待测试的芯片结构安装到测试电路板2上时,可基于测试线路板上的接线端子22由测试和加载需要来决定其与触点的连接位置和连接方式,进而使得本方案的测试装置具备优良的测试柔性。

100.根据本发明的一种实施方式,本发明的测试装置的固有频率由其本身的几何参数、材料、边界条件所确定。进而,本发明的测试装置在振动测试前需要明确所要加载的振动频率范围和振动量级。在进行振动应力测试时,所采用的振动应力的频率范围和振动量级需要在测试装置可加载的振动频率和振动量级范围内。在本实施方式中,测试电路板2的设计尺寸、测试夹具等需要进行有限元模态分析计算其固有频率,反复修正改进确保测试电路板2、测试夹具、tsv多应力可靠性试验芯片结构1在组合状态下的固有频率被加载的振动应力频率范围和振动量级所覆盖。

101.根据本发明的一种实施方式,测试夹具为矩形金属薄板。在本实施方式中,测试夹具上设置有用于安装测试电路板2的安装限位孔和用于可拆卸安装配重块的配重块安装位,以及与所述配重块安装位可拆卸连接的配重块。在本实施方式中,配重块安装位在安装限位孔的周围环绕设置有多个。通过上述设置,测试夹具的尺寸,以及安装限位孔的尺寸由振动测试所需的频率范围决定,一般首先采用有限元模态分析进行初步设计,使得测试装置固有频率被振动测试频率范围所覆盖。开展实际试验前,采用扫频测试验证模态分析结果,并可以通过安装配重块来调整和修正。

102.为进一步说明本方案,结合附图1至11对本方案的测试装置的测试流程做进一步说明。

103.s1.明确测试目标,即确定多应力类型(如温度、湿度、电应力、振动中的至少一种)及载荷参数(如温度范围和加载周期、湿度范围和加载周期、电应力范围和加载周期、振动评率范围和振动量级)、tsv多应力可靠性试验芯片结构1的类型(测试对象)、测试链路长度及在测试电路板2上测试的接线端子22;

104.s2.确定tsv多应力可靠性试验芯片结构1的尺寸参数,设计掩膜版,并进行流片、测试和划片,获得用于测试的tsv多应力可靠性试验芯片结构1的裸片;

105.s3.基于模态分析,并根据振动载荷频率范围确定测试电路板2的尺寸参数和测试夹具尺寸参数,并设计制造相应的测试电路板2和测试夹具;

106.s4.选择链路类型,将具有相应链路类型的tsv多应力可靠性试验芯片结构1焊接到测试电路板2上;

107.s5.将步骤s1中确定的接线端子22通过耐高温硅胶线连接到电源及信号发生器或者信号采集装置(即数字采集系统);

108.s6.将测试电路板2安装在测试夹具上,对测试电路板2、测试夹具、tsv多应力可靠性试验芯片结构1组合体的固有频率进行测试,判断是否满足要求,若满足,则进行多应力可靠性试验与分析,否则,则重新调整测试夹具的结构(例如:调整尺寸或安装配重块)。

109.上述内容仅为本发明的具体方案的例子,对于其中未详尽描述的设备和结构,应当理解为采取本领域已有的通用设备及通用方法来予以实施。

110.以上所述仅为本发明的一个方案而已,并不用于限制本发明,对于本领域的技术

人员来说,本发明可以有各种更改和变化。凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。