铜cmp的工艺控制方法

技术领域

1.本发明涉及一种半导体集成电路的制造方法,特别是涉及一种铜化学机械研磨(cmp)的工艺控制方法。

背景技术:

2.在半导体集成电路制造中,铜线的形成工艺往往需要采用大马士革工艺,大马士革工艺是先形成沟槽,之后再填充铜层,之后在进行铜cmp将沟槽外的铜层去除并将沟槽内的铜层研磨到所需的厚度并形成铜线。所以在大马士革工艺中往往需要采用铜cmp。

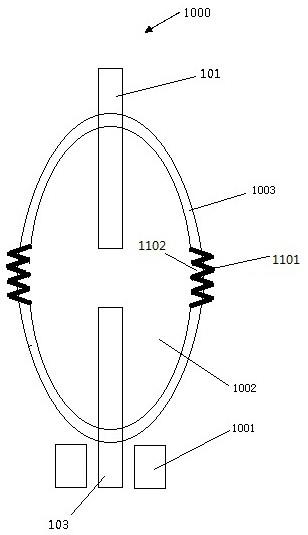

3.如图1所示,是现有化学机械研磨设备的结构示意图,现有cmp设备包括底盘装置即研磨台101,研磨台101会在旋转装置的带动下旋转,图1中用旋转线表示所述研磨台101会旋转。

4.在研磨台101上设置有研磨垫102。

5.晶圆(wafer)103会固定在研磨头104上,研磨头104也会旋转,且研磨头104还具有能施加压力的装置,使得晶圆103会和研磨垫102压在一起。

6.包括了研磨颗粒和研磨浆料(slurry)的研磨液106会从研磨液管输送到研磨液碰嘴105上并通过研磨液碰嘴105流动到研磨垫102上。

7.研磨时,研磨头104会将晶圆104和研磨垫102接触并施加压力以及转动,之后实现对晶圆104膜层的研磨。研磨过程中,研磨液106主要是用于增加各种晶圆103如硅片的表面物质和水的氢键结合能力,增加被研磨物质和研磨垫的分子亲和力,同时研磨颗粒也会带走研磨下来的物质颗粒。

8.钻石盘107上设置有钻石108,钻石盘107也能进行选择;砖石盘107能在研磨垫102上扫动,从而清除研磨垫102上的研磨残留物并时研磨垫102的表面保持粗糙。

9.在铜cmp中,由于铜cmp之前包括进行沟槽刻蚀的工艺即前层刻蚀,前层刻蚀后沟槽底部剩余介质层的厚度会影响铜cmp后铜线的厚度,最后会影响器件的电阻率(rs)电性参数,从而影响产品良率。

技术实现要素:

10.本发明所要解决的技术问题是提供一种铜cmp的工艺控制方法,能消除铜cmp之前的介质层刻蚀工艺对铜线厚度的不利影响并从而能提高产品良率。

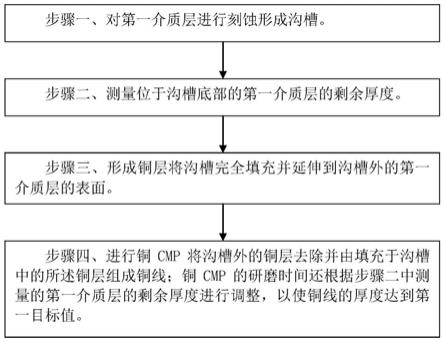

11.为解决上述技术问题,本发明提供的铜cmp的工艺控制方法包括如下步骤:

12.步骤一、提供第一介质层,对所述第一介质层进行刻蚀形成沟槽,所述沟槽位于铜线形成区域中。

13.步骤二、测量位于所述沟槽底部的所述第一介质层的剩余厚度。

14.步骤三、形成铜层,所述铜层将所述沟槽完全填充并延伸到所述沟槽外的所述第一介质层的表面。

15.步骤四、进行铜cmp,所述铜cmp将所述沟槽外的所述铜层去除以及将所述沟槽内

的所述铜层的顶部表面和所述沟槽外的所述第一介质层的顶部表面相平,由填充于所述沟槽中的所述铜层组成所述铜线;所述铜cmp的研磨时间还根据步骤二中测量的所述第一介质层的剩余厚度进行调整,以使所述铜线的厚度达到第一目标值。

16.进一步的改进是,步骤四中,所述铜cmp的研磨时间的调整值和所述第一介质层的剩余厚度的关系为:

[0017][0018]

其中,δt表示所述铜cmp的研磨时间的调整值,rox表示所述第一介质层的剩余厚度,target2所述第一介质层的剩余厚度的第二目标值,rr表示所述铜cmp的研磨速率。

[0019]

进一步的改进是,所述铜cmp的研磨时间为所述铜cmp的研磨时间的初始设定值减去调整值。

[0020]

进一步的改进是,所述铜cmp的研磨时间的初始设定值为最近多次所述铜cmp中使所述铜线的厚度达到所述第一目标值所需要的研磨时间的平均值。

[0021]

进一步的改进是,rr取上一次铜cmp的研磨速率的最大值。

[0022]

进一步的改进是,所述第一介质层为形成于半导体衬底上的层间膜。

[0023]

进一步的改进是,步骤一中还同时形成通孔开口,所述通孔开口完全穿过所述第一介质层并将底层金属线表面露出;

[0024]

步骤三中,所述铜层将所述通孔开口完成填充并形成所述通孔。

[0025]

进一步的改进是,所述底层金属线形成于底层层间膜中。

[0026]

进一步的改进是,所述半导体衬底和所述第一介质层之前包括一层以上的所述底层层间膜和所述底层金属线,各所述底层金属线之间通过底层通孔连接。

[0027]

进一步的改进是,所述底层金属线的材料包括铜,铜材料组成的所述底层金属线的铜cmp的工艺控制步骤和所述铜线的铜cmp的工艺控制步骤相同。

[0028]

进一步的改进是,所述半导体衬底包括硅衬底。

[0029]

进一步的改进是,所述第一介质层的材料包括低介电常数层。

[0030]

进一步的改进是,所述底层层间膜的材料包括低介电常数层。

[0031]

进一步的改进是,所述低介电常数层包括sicoh。

[0032]

进一步的改进是,在所述第一介质层和下一层的所述底层层间膜之间还间隔有sicn层。

[0033]

进一步的改进是,步骤二完成后将所述第一介质层的剩余厚度直接计算所述铜cmp的研磨时间的调整值,之后将所述铜cmp的研磨时间的调整值导入到跑货(r2r)系统,然后所述跑货系统将所述铜cmp的研磨时间的调整值反馈到所述铜cmp的研磨机台实现对所述铜cmp的研磨时间的自动调整。

[0034]

进一步的改进是,步骤二完成后将所述第一介质层的剩余厚度直接计算所述铜cmp的研磨时间的调整值,之后直接在所述铜cmp的研磨机台上通过手动方式对所述铜cmp的研磨时间的进行调整。

[0035]

在铜cmp中,铜cmp和之前的介质层刻蚀工艺具有关联性,也即铜cmp之前的介质层刻蚀工艺即前层刻蚀工艺会影响到铜cmp,本发明通过在第一介质层刻蚀之后测量沟槽底部的第一介质层的剩余厚度并根据第一介质层的剩余厚度来调整铜cmp的研磨时间,从而

能使铜cmp后铜线的厚度保持为目标值即第一目标值,所以,本发明能消除铜cmp之前的介质层刻蚀工艺对铜线厚度的不利影响,最后能使器件的电阻率保持稳定,并从而能提高产品良率。

附图说明

[0036]

下面结合附图和具体实施方式对本发明作进一步详细的说明:

[0037]

图1是现有化学机械研磨设备的结构示意图;

[0038]

图2是本发明实施例铜cmp的工艺控制方法的流程图;

[0039]

图3a

‑

图3d是本发明实施例铜cmp的工艺控制方法各步骤中的器件结构示意图。

具体实施方式

[0040]

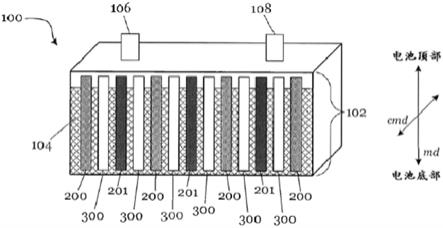

如图2所示,是本发明实施例铜cmp的工艺控制方法的流程图;如图3a至图3d所示,是本发明实施例铜cmp的工艺控制方法各步骤中的器件结构示意图;本发明实施例铜cmp的工艺控制方法包括如下步骤:

[0041]

步骤一、如图3a所示,提供第一介质层204。所述第一介质层204的顶部表面用标记2041标出。

[0042]

如图3b所示,对所述第一介质层204进行刻蚀形成沟槽205,所述沟槽205位于铜线208形成区域中。

[0043]

本发明实施例以双大马士革工艺中的铜cmp为例进行说明,下形成所述沟槽205的同时形成通孔开口206,所述通孔开口206完全穿过所述第一介质层204并将底层金属线202表面露出。

[0044]

本发明实施例中,所述第一介质层204为形成于半导体衬底上的层间膜。

[0045]

所述底层金属线202形成于底层层间膜201中。

[0046]

所述半导体衬底和所述第一介质层204之前包括一层以上的所述底层层间膜201和所述底层金属线202,各所述底层金属线202之间通过底层通孔209连接。

[0047]

所述半导体衬底包括硅衬底。

[0048]

所述第一介质层204的材料包括低介电常数层。

[0049]

所述底层层间膜201的材料包括低介电常数层。

[0050]

较佳为,所述低介电常数层包括sicoh。

[0051]

在所述第一介质层204和下一层的所述底层层间膜201之间还间隔有sicn层203。

[0052]

步骤二、如图3b所示,测量位于所述沟槽205底部的所述第一介质层204的剩余厚度d1。

[0053]

步骤三、如图3c所示,形成铜层207,所述铜层207将所述沟槽205完全填充并延伸到所述沟槽205外的所述第一介质层204的表面。

[0054]

步骤四、如图3d所示,进行铜cmp,所述铜cmp将所述沟槽205外的所述铜层207去除以及将所述沟槽205内的所述铜层207的顶部表面和所述沟槽205外的所述第一介质层204的顶部表面相平,由填充于所述沟槽205中的所述铜层207组成所述铜线208;所述铜cmp的研磨时间还根据步骤二中测量的所述第一介质层204的剩余厚度d1进行调整,以使所述铜线208的厚度d2达到第一目标值。

[0055]

本发明实施例中,所述铜cmp的研磨时间的调整值和所述第一介质层204的剩余厚度d1的关系为:

[0056][0057]

其中,δt表示所述铜cmp的研磨时间的调整值,rox表示所述第一介质层204的剩余厚度d1,target2所述第一介质层204的剩余厚度d1的第二目标值,rr表示所述铜cmp的研磨速率。

[0058]

所述铜cmp的研磨时间为所述铜cmp的研磨时间的初始设定值减去调整值。

[0059]

所述铜cmp的研磨时间的初始设定值为最近多次所述铜cmp中使所述铜线208的厚度d2达到所述第一目标值所需要的研磨时间的平均值。也即:所述铜cmp的研磨时间的初始设定值的获得方法为:

[0060]

统计出最近多次如25次所述铜cmp中使所述铜线208的厚度d2达到所述第一目标值所需要的研磨时间,通常是统计出最近多次相同产品或类似产品的所述铜cmp中使所述铜线208的厚度d2达到所述第一目标值所需要的研磨时间。

[0061]

对统计的多次研磨时间取平均值即得到所述铜cmp的研磨时间的初始设定值。

[0062]

rr取上一次铜cmp的研磨速率的最大值。

[0063]

由图3d所示可知,所述铜cmp会使所述第一介质层204的顶部表面从虚线2041的位置处下降到线2042的位置处,所述第一介质层204的损失厚度用d3表示。

[0064]

所述铜层207将所述通孔开口206完成填充并形成所述通孔209。

[0065]

所述底层金属线202的材料包括铜,铜材料组成的所述底层金属线202的铜cmp的工艺控制步骤和所述铜线208的铜cmp的工艺控制步骤相同。

[0066]

本发明实施例中,步骤二完成后将所述第一介质层204的剩余厚度d1直接计算所述铜cmp的研磨时间的调整值,之后将所述铜cmp的研磨时间的调整值导入到跑货系统,然后所述跑货系统将所述铜cmp的研磨时间的调整值反馈到所述铜cmp的研磨机台实现对所述铜cmp的研磨时间的自动调整。在其他实施例中也能为:步骤二完成后将所述第一介质层204的剩余厚度d1直接计算所述铜cmp的研磨时间的调整值,之后直接在所述铜cmp的研磨机台上通过手动方式对所述铜cmp的研磨时间的进行调整。手动调整方式能在跑货系统还没有应用时进行,例如在新产品试流片阶段能采用手动调整方式调整所述铜cmp的研磨时间。

[0067]

在铜cmp中,铜cmp和之前的介质层刻蚀工艺具有关联性,也即铜cmp之前的介质层刻蚀工艺即前层刻蚀工艺会影响到铜cmp,本发明实施例通过在第一介质层204刻蚀之后测量沟槽205底部的第一介质层204的剩余厚度d1并根据第一介质层204的剩余厚度d1来调整铜cmp的研磨时间,从而能使铜cmp后铜线208的厚度d2保持为目标值即第一目标值,所以,本发明实施例能消除铜cmp之前的介质层刻蚀工艺对铜线208厚度的不利影响,最后能使器件的电阻率保持稳定,并从而能提高产品良率。

[0068]

以上通过具体实施例对本发明进行了详细的说明,但这些并非构成对本发明的限制。在不脱离本发明原理的情况下,本领域的技术人员还可做出许多变形和改进,这些也应视为本发明的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。