1.本实用新型涉及存储器测试技术领域,尤其是一种存储器板级装置测试电路。

背景技术:

2.存储管理要实现的目的是为用户提供方便、安全和充分大的存储空间,随着科技的发展,市场需求量很大,需要对器件的读、写功能,包括全空间写入、读取,包括写全零,写全一,正棋盘格,反棋盘格,march c算法以及部分时间参数进行测试,需要比较全面的测试器件的各种工作情况;但在测试过程中,由于电压电流不稳定,会出现损坏测试芯片或者测试参数不准确的情况,因而需要实用新型一种能保证测试芯片安全性及准确性的测试电路。

技术实现要素:

3.本实用新型的目的在于克服现有技术的不足,提供一种存储器板级装置测试电路。

4.本实用新型解决其技术问题是采取以下技术方案实现的:

5.一种存储器板级装置测试电路,包括测试芯片及与所述测试芯片连接的采样电路,所述采样电路对测试芯片的电压电流数据采样保证所述测试芯片的稳定性。

6.优选的,所述测试芯片连接存储滤波电路,用于对所述测试芯片进行滤波处理。

7.优选的,所述采样电路及所述测试芯片连接稳压电路,对电压数据进行稳压处理。

8.优选的,所述稳压电路型号为tps51206dsq。

9.优选的,所述测试芯片型号为is46dr16640b。

10.优选的,所述测试芯片通过芯片座连接子测试电路。

11.优选的,所述子测试电路连接连接电路。

12.优选的,所述连接电路还与母测试电路连接,所述母测试电路连接上位机,所述上位机控制所述母测试电路进行测试。

13.优选的,所述母测试电路包括通讯电路,上位机通过所述通讯电路连接所述连接电路。

14.优选的,所述通讯电路型号为max13236。

15.本实用新型的优点和积极效果是:

16.1.本实用新型一种存储器板级装置测试电路,包括测试芯片及分别与所述测试芯片连接的采样电路、存储滤波电路及稳压电路,所述采样电路对测试芯片的电压电流数据采样保证所述测试芯片的稳定性;所述测试芯片连接存储滤波电路,用于对所述测试芯片进行滤波处理;所述采样电路及所述测试芯片连接稳压电路,对电压数据进行稳压处理,提高所述测试芯片的安全性及稳定性。

17.2.本实用新型中所述子测试电路与所述母测试电路通过所述连接电路互连,所述测试芯片通过芯片座连接子测试电路,所述母测试电路连接上位机,所述上位机控制所述

母测试电路进行测试,对于不同的测试芯片,不用更换所述母测试电路即可完成测试内容提高测试效率。

附图说明

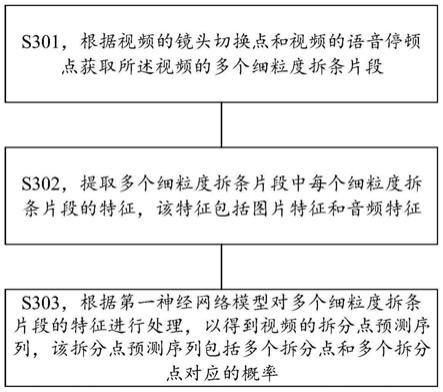

18.图1是本实用新型的电路连接框图;

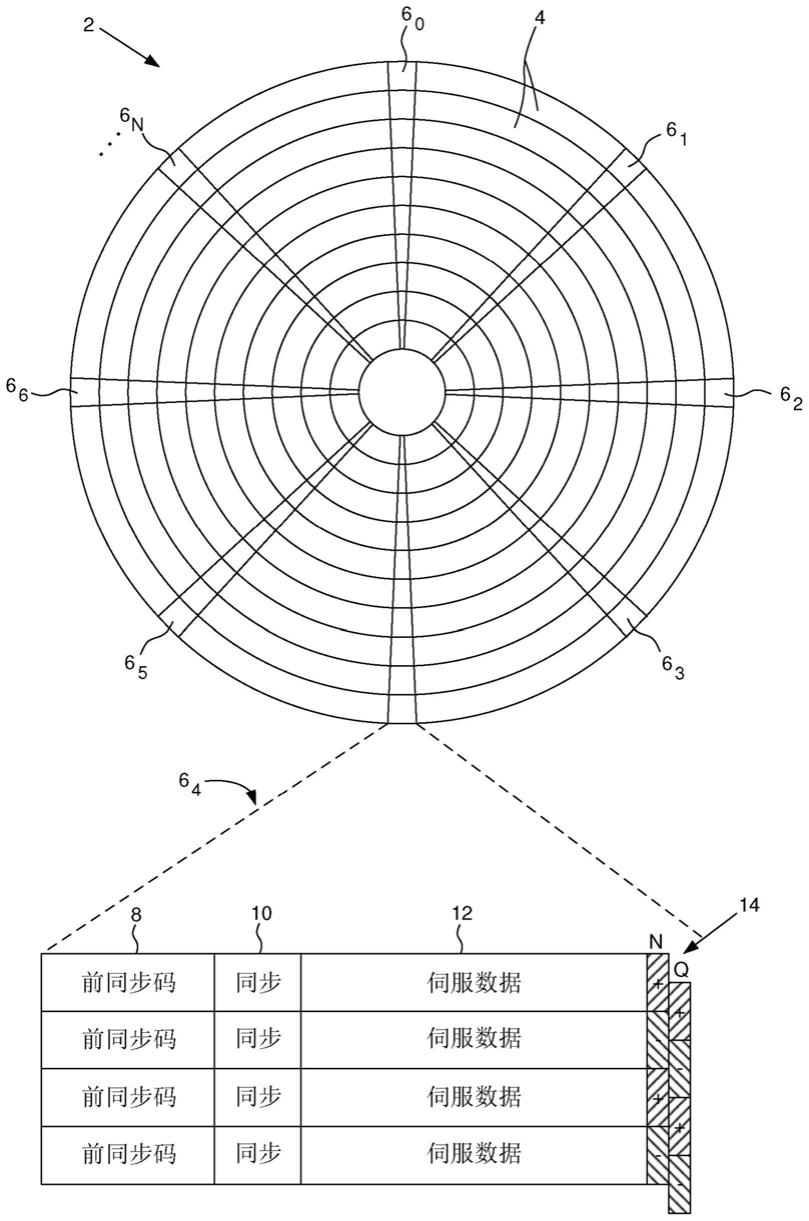

19.图2是本实用新型的测试芯片连接图;

20.图3是本实用新型的采样电路连接图;

21.图4是本实用新型的存储滤波电路连接图;

22.图5是本实用新型的稳压电路连接图;

23.图6是本实用新型的子测试电路连接图;

24.图7是本实用新型的连接电路连接图;

25.图8是本实用新型的通讯电路连接图。

具体实施方式

26.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有做出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

27.需要说明的是,当组件被称为“固定于”另一个组件,它可以直接在另一个组件上或者也可以存在居中的组件。当一个组件被认为是“连接”另一个组件,它可以是直接连接到另一个组件或者可能同时存在居中组件。当一个组件被认为是“设置于”另一个组件,它可以是直接设置在另一个组件上或者可能同时存在居中组件。本文所使用的术语“垂直的”、“水平的”、“左”、“右”以及类似的表述只是为了说明的目的。

28.除非另有定义,本文所使用的所有的技术和科学术语与属于本实用新型的技术领域的技术人员通常理解的含义相同。本文中在本实用新型的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本实用新型。本文所使用的术语“及/或”包括一个或多个相关的所列项目的任意的和所有的组合。

29.如图1

‑

3所示,本实用新型所述一种存储器板级装置测试电路,包括测试芯片及与所述测试芯片连接的采样电路,所述采样电路对测试芯片的电压电流数据采样保证所述测试芯片的稳定性;

30.具体的,所述测试芯片型号为is46dr16640b;所述测试芯片的s0_ddr_p1v8引脚及s0_ddr_vref_p0v9引脚分别连接所述采样电路的s0_ddr_p1v8引脚及s0_ddr_vref_p0v9引脚;所述采样电路包括电阻s0_sr0及电阻s0_sr采集电压电路数据。

31.进一步地,如图4所示,所述测试芯片连接存储滤波电路,用于对所述测试芯片进行滤波处理;

32.具体的,所述测试芯片的s0_ddr_vtt_p0v9引脚、s0_ddr_vddq1v8引脚及s0_ddr_p1v8引脚分别连接所述存储滤波电路的s0_ddr_vtt_p0v9引脚、s0_ddr_vddq1v8引脚及s0_ddr_p1v8引脚。

33.进一步地,如图5所示,所述采样电路及所述测试芯片连接稳压电路,对电压数据

进行稳压处理;具体的,所述稳压电路型号为tps51206dsq;所述测试芯片的s0_ddr_vtt_p0v9引脚、s0_ddr_p1v8引脚分别连接所述稳压电路的s0_ddr_vtt_p0v9引脚、s0_ddr_p1v8引脚。

34.进一步地,如图6

‑

8所示,所述测试芯片通过芯片座连接子测试电路,所述子测试电路连接连接电路;具体的,所述连接电路的fpga_hr_io引脚连接所述子测试电路的fpga_hr_io引脚。

35.进一步地,所述连接电路还与母测试电路连接,所述母测试电路连接上位机,所述上位机控制所述母测试电路进行测试;

36.进一步地,所述母测试电路包括通讯电路,上位机通过所述通讯电路连接所述连接电路;

37.具体的,母测试电路包括通讯电路,所述通讯电路型号为max13236,所述上位机连接所述通讯电路的jo接口,所述通讯电路的p3v3_crtl_main引脚连接所述连接电路的p3v3_crtl_main引脚。

38.工作原理:

39.1.所述采样电路对测试芯片的电压电流数据采样保证所述测试芯片的稳定性;

40.2.所述测试芯片连接存储滤波电路,用于对所述测试芯片进行滤波处理;

41.3.所述采样电路及所述测试芯片连接稳压电路,对电压数据进行稳压处理;

42.4.所述测试芯片通过芯片座连接子测试电路;所述子测试电路连接连接电路;

43.5.所述连接电路还与母测试电路连接,所述母测试电路连接上位机,所述上位机控制所述母测试电路进行测试。

44.本实用新型一种存储器板级装置测试电路,包括测试芯片及分别与所述测试芯片连接的采样电路、存储滤波电路及稳压电路,所述采样电路对测试芯片的电压电流数据采样保证所述测试芯片的稳定性;所述测试芯片连接存储滤波电路,用于对所述测试芯片进行滤波处理;所述采样电路及所述测试芯片连接稳压电路,对电压数据进行稳压处理,提高所述测试芯片的安全性及稳定性;所述子测试电路与所述母测试电路通过所述连接电路互连,所述测试芯片通过芯片座连接子测试电路,所述母测试电路连接上位机,所述上位机控制所述母测试电路进行测试,对于不同的测试芯片,不用更换所述母测试电路即可完成测试内容提高测试效率。

45.上述说明是针对本实用新型较佳可行实施例的详细说明,但实施例并非用以限定本实用新型的专利申请范围,凡本实用新型所提示的技术精神下所完成的同等变化或修饰变更,均应属于本实用新型所涵盖专利范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。