1.本发明通常涉及集成电路设计,以及更具体地,涉及一种利用可配置输入/输出接口电路的多封装系统及用于封装在半导体封装中的裸晶,该可配置输入/输出接口电路可被配置为用于单端(single

‑

ended)封装内(intra

‑

package)通信和差分(differential)封装间(inter

‑

package)通信。

背景技术:

2.电子产业正经历半导体封装技术的复兴。越来越多的封装组装方法已经得到发展,以使电子行业能够最大化其产品功能。通过将多个裸片(dice)/裸晶(die)集成在单个封装中,可以使印刷电路板变得更小,并且由这种集成带来的较短互连能够有助于改善电气性能和功能。由于多个裸晶可以集成在同一封装(package,或芯片,chip)中,并且系统可以在同一印刷电路板上安装多个封装(芯片),因此需要提供针对封装内通信的创新型裸晶到裸晶(die

‑

to

‑

die)输入/输出(input/output,io)接口设计,以及针对封装间通信的创新型芯片到芯片(chip

‑

to

‑

chip)io接口设计。

技术实现要素:

3.有鉴于此,本发明的目的之一是提供一种多封装系统及用于封装在半导体封装中的裸晶,其能够利用可配置的输入/输出接口电路进行单端封装内通信和差分封装间通信。

4.根据本发明的第一方面,提供了一种示例性的多封装系统。该示例性的多封装系统包括第一半导体封装和第二半导体封装。第一半导体封装包括第一裸晶和第二裸晶。第一裸晶包括第一处理电路、第一可配置输入/输出(io)接口电路(或可描述为第一可配置的io接口电路)以及第二可配置io接口电路,该第一处理电路被布置为执行指定功能。第二裸晶包括第二处理电路以及第三可配置io接口电路,该第二处理电路被布置为执行指定功能,该第三可配置io接口电路经由封装内走线耦接到第一可配置io电路。第二半导体封装包括第三裸晶。第三裸晶包括第三处理电路和第四可配置io接口电路,该第三处理电路被布置为执行指定功能,该第四可配置io接口电路经由封装间走线耦接到第二可配置io接口电路。第一处理电路通过第一可配置io接口电路和第三可配置io接口电路与第二处理电路通信,其中,第一可配置io接口电路和第三可配置io接口电路被配置为执行单端封装内通信。第一处理电路通过第二可配置io接口电路和第四可配置io接口电路与第三处理电路通信,其中,第二可配置io接口电路和第四可配置io接口电路被配置为执行差分封装间通信。第一可配置io接口电路和第二可配置io接口电路具有相同的电路设计,例如,相同的tx电路设计和/或相同的rx电路设计。

5.根据本发明的第二方面,提供了一种用于封装在半导体封装中的示例性裸晶。该示例性裸晶包括处理电路和可配置输入/输出(io)接口电路,该处理电路被布置为执行指定功能。当可配置io接口电路是通过封装内走线耦接到同一半导体封装中的另一个裸晶时,可配置io接口电路被配置为给处理电路提供单端封装内通信。当可配置io接口电路是

经由封装间走线耦接到另一半导体封装中的另一个裸晶时,可配置io接口电路被配置为给处理电路提供差分封装间通信。

6.本领域技术人员在阅读附图所示优选实施例的下述详细描述之后,可以毫无疑义地理解本发明的这些目的及其它目的。详细的描述将参考附图在下面的实施例中给出。

附图说明

7.包括的附图用以提供对本公开实施例的进一步理解,以及,附图被并入并构成本公开实施例的一部分。附图示出了本公开实施例的实施方式,并且与说明书一起用于解释本公开实施例的原理。可以理解的是,附图不一定按比例绘制,因为可以示出一些部件与实际实施中的尺寸不成比例以清楚地说明本公开实施例的概念。

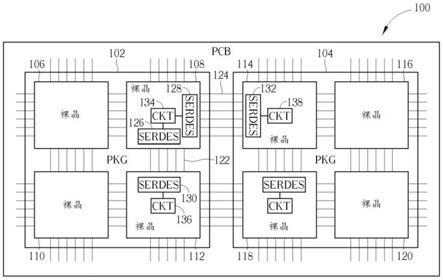

8.图1是根据本发明实施例示出的多封装系统的示意图。

9.图2是示出在封装间通信中使用的单端信令遇到的问题的示意图。

10.图3是根据本发明实施例示出的第一tx设计的示意图,该第一tx设计是由可配置io接口电路采用的电路设计的一部分。

11.图4是示出将图3所示的tx电路配置为作为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。

12.图5是示出将图3所示的tx电路配置为作为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。

13.图6是示出将图3所示的tx电路配置为作为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施例的示意图。

14.图7是示出将图3所示的tx电路配置为作为用于封装间(芯片到芯片)通信的差分io接口的一部分的另一实施例的示意图。

15.图8是根据本发明实施例示出的第二tx设计的示意图,该第二tx设计是由可配置io接口电路采用的电路设计的一部分。

16.图9是示出将图8所示的tx电路配置为作为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。

17.图10是示出将图8所示的tx电路配置为作为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。

18.图11是示出将图8所示的tx电路配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施方式的示意图。

19.图12是示出将图8所示的tx电路配置为作为用于封装间(芯片到芯片)通信的差分io接口的一部分的另一实施例的示意图。

20.图13是根据本发明实施例示出的第一rx设计的示意图,该第一rx设计是由可配置io接口电路采用的电路设计的一部分。

21.图14是示出将图13所示的rx电路配置为作为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。

22.图15是示出将图13所示的rx电路配置为作为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施例的示意图。

23.图16是示出将图13所示的rx电路配置为作为用于封装间(芯片到芯片)通信的差

分io接口的一部分的实施例的示意图。

24.图17是根据本发明实施例示出的第二rx设计的示意图,该第二rx设计是由可配置io接口电路采用的电路设计的一部分。

25.图18是说明将图17所示的rx电路配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。

26.图19是说明将图17所示的rx电路配置为用作封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施例的示意图。

27.图20是说明将图19中所示的rx电路配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。

28.图21是根据本发明实施例示出的第三rx设计的示意图,该第三rx设计是由可配置io接口电路采用的电路设计的一部分。

29.图22是说明将图21所示的rx电路配置为作为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。

30.图23是说明将图21所示的rx电路配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施例的示意图。

31.图24是说明将图21中所示的rx电路配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。

32.在下面的详细描述中,为了说明的目的,阐述了许多具体细节,以便本领域技术人员能够更透彻地理解本发明实施例。然而,显而易见的是,可以在没有这些具体细节的情况下实施一个或多个实施例,不同的实施例可根据需求相结合,而并不应当仅限于附图所列举的实施例。

具体实施方式

33.以下描述为本发明实施的较佳实施例,其仅用来例举阐释本发明的技术特征,而并非用来限制本发明的范畴。在通篇说明书及权利要求书当中使用了某些词汇来指称特定的元件,所属领域技术人员应当理解,制造商可能会使用不同的名称来称呼同样的元件。因此,本说明书及权利要求书并不以名称的差异作为区别元件的方式,而是以元件在功能上的差异作为区别的基准。本发明中使用的术语“元件”、“系统”和“装置”可以是与计算机相关的实体,其中,该计算机可以是硬件、软件、或硬件和软件的结合。在以下描述和权利要求书当中所提及的术语“包含”和“包括”为开放式用语,故应解释成“包含,但不限定于

…”

的意思。此外,术语“耦接”意指间接或直接的电气连接。因此,若文中描述一个装置耦接于另一装置,则代表该装置可直接电气连接于该另一装置,或者透过其它装置或连接手段间接地电气连接至该另一装置。

34.其中,除非另有指示,各附图的不同附图中对应的数字和符号通常涉及相应的部分。所绘制的附图清楚地说明了实施例的相关部分且并不一定是按比例绘制。

35.文中所用术语“基本”或“大致”是指在可接受的范围内,本领域技术人员能够解决所要解决的技术问题,基本达到所要达到的技术效果。举例而言,“大致等于”是指在不影响结果正确性时,技术人员能够接受的与“完全等于”有一定误差的方式。

36.图1是根据本发明实施例示出的多封装系统的示意图。多封装系统100包括多个半

导体封装(例如,102和104),该多个半导体封装安装在印刷电路板(printed circuit board,pcb)上。半导体封装也可以称为半导体芯片(semiconductor chip)。在下文中,术语“封装”和“芯片”可以互换。半导体封装102和104的每一个(由“pkg”标记)包括封装在其中的多个裸晶。在本实施例中,四个裸晶106、108、110和112被封装在同一半导体封装102中,以及,四个裸晶114、116、118和120被封装在同一半导体封装104中。应当指出的是,安装在一个pcb上的半导体封装的数量以及封装在一个半导体封装中的裸晶的数量是可以调整的,这取决于实际的设计考虑,本发明对此不做任何限制。另外,关于多封装系统100,多个半导体封装可以是同质(homogeneous)芯片(即,相同的芯片)或异质(heterogeneous)芯片(即,不同的芯片),其中,封装在同一半导体封装中的多个裸晶可以是同质裸晶(即,相同的裸晶)或异质裸晶(即,不同的裸晶)。例如,多封装系统100可以被数据中心(data center)或人工智能(artificial intelligence,ai)应用所采用,并且可以具有多个同质芯片,其中,该多个同质芯片的每一个可以具有多个裸晶,每一个裸晶可以采用本发明提出的一个或多个可配置输入/输出接口电路(configurable input/output interface circuit(s)),该可配置输入/输出接口电路能够用于单端(single

‑

ended)封装内(裸晶到裸晶)通信和/或差分(differential)封装间(芯片到芯片)通信。

37.可以理解地,封装内(裸晶到裸晶)通信是指同一封装内的不同裸晶之间的通信,封装间(芯片到芯片)通信是指不同封装之间的通信,即分别位于不同封装内的不同裸晶之间的通信。此外,单端封装内(裸晶到裸晶)通信是指:同一封装内的不同裸晶之间利用单端信号进行通信或交互。另外,差分封装间(芯片到芯片)通信是指:不同封装之间的裸晶利用差分信号进行通信或交互。如图1所示,半导体封装中的一个裸晶通过(via)封装内(intra

‑

package)通信与同一半导体封装中的另一个裸晶进行通信(封装内通信)。例如,裸晶108和裸晶112之间的封装内通信是透过被布线(routed)在半导体封装102内部的pkg走线(即,封装内走线,intra

‑

package traces)122来实现的。此外,半导体封装中的一个裸晶通过封装间(inter

‑

package)通信与不同半导体封装中的另一个裸晶进行通信(封装间通信)。例如,裸晶108和裸晶114之间的封装间通信是透过半导体封装102和半导体封装104之间的pcb走线(即,封装间走线,inter

‑

package traces)124来实现的。

38.用于封装内通信的输入/输出(io)规范可能包括一些要求。例如,要求吞吐效率为~1tbps/mm,能量效率为1pj/bit

–

0.5pj/bit,封装走线长度(package trace length)为10mm

‑

50mm,以及,误码率(bit error rate,ber)低于1e

‑

15。此外,每一个io端口的硅(silicon)面积应较小,以便进行高密集集成,且模拟/复杂电路应最小化,以提供简单/快速的移植过程。因此,在本发明实施例中,单端电路(single

‑

ended circuitry)被用来实现封装内通信(即在同一封装内的不同裸晶之间的通信,所以又可称为裸晶到裸晶通信),以满足上述要求。

39.然而,当单端电路被用来实现封装间通信(即不同封装或不同芯片之间的通信,或者说,在不同封装或芯片内的裸晶之间的通信,所以又可称为芯片到芯片通信)时,单端电路将经由走线(trace)和电源/地返回路径的耦合而遭受较大的串扰,复杂返回路径的终止(termination)较差,同步开关噪声(simultaneous switching noise,ssn)较大,以及发射机/发射端/发射(transmitter,tx)和接收机/接收端/接收(receiver,rx)之间的参考噪声较大。图2是说明在封装间通信中使用单端信令遇到的问题的示意图。由于难以使tx和rx就

参考电压vref达成一致的事实,所以参考噪声大。由于返回电流必须分流并流过电源和地的网络,因此返回路径很复杂,这会导致较差的终止和较大的串扰。由于依赖于数据的电流会在电源上产生噪声,并且该噪声通过电源耦合到其它信号,因此ssn很大。

40.与单端电路相反,差分电路具有更好的信号完整性(signal integrity,si)/功率完整性(power integrity,pi)性能,因为其固有的共模抑制比(common

‑

mode rejection ratio,cmrr)和定义明确的返回路径导致的串扰较小,明确定义的返回路径可带来较好的终止效果,差分电路操作可产生更少的ssn,以及,没有参考噪声问题等等,因此。当考虑到单端电路中的串扰/反射/ssn/参考噪声时,可以选择差分电路来实现封装间通信。

41.如果一个裸晶被设计为具有一个专用的(dedicated)单端io接口和一个专用的差分io接口,且它们都沿着一个裸晶边缘(edge)设置,则当在该裸晶边缘上不需要封装内通信时,该专用的单端io接口是冗余的,以及,当在该裸晶边缘上不需要封装间通信时,该专用的差分io接口是冗余的。此外,专用的单端io接口的实现和专用的差分io接口的实现需要不同的硅智产(silicon intellectual property,sip)块/内核,即不同的电路设计。为了解决上述问题,本发明提出利用可配置输入/输出(io)接口电路(例如,可配置的串行器/解串器(serializer/deserializer,serdes)io接口电路),其能够被配置为用于封装内通信的单端裸晶到裸晶io接口电路或者被配置为用于封装间通信的差分芯片到芯片io接口电路。也就是说,本发明提出的可配置输入/输出(io)接口电路能够被配置为针对封装内通信则利用单端信号进行通信,以及,能够被配置为针对封装间通信则利用差分信号进行通信。从而,发明实施例除能够满足封装内通信和封装间通信的性能要求外,还具有封装面积更小,以及移植性更佳等优点。

42.如图1所示,裸晶108的可配置io接口电路(由“serdes”标记)126和裸晶112的可配置io接口电路(由“serdes”标记)130均被配置为单端io接口电路,以使能(enable)裸晶108的处理电路(标记为“ckt”)134与裸晶112的处理电路(标记为“ckt”)136之间的封装内通信,其中,处理电路134用于执行裸晶108的指定功能(designated functions)或预设功能,以及,处理电路136用于执行裸晶112的指定功能或预设功能。可以理解地,不同裸晶内的处理电路所执行的指定功能可以相同或不同,本发明对此不做任何限制。可以理解地,以tx设计为例,单端io接口电路是指被配置为输出单端信号的接口电路,如图4所示,其输出单端tx比特流tx_1和tx_2,而差分io接口电路是指被配置为输出差分信号的接口电路,如图7所示,其输出由正比特流tx_ckp和负比特流tx_ckn组成的差分tx比特流,又如图8所示,其输出由tx比特流tx_out1和tx_aux1构成的差分tx比特流以及由tx比特流tx_out2和tx_aux2构成的差分tx比特流。相应地,以rx设计为例,单端io接口电路是指被配置为接收单端信号的接口电路,差分io接口电路是指被配置为接收差分信号的接口电路。此外,裸晶108的可配置io接口电路(标记为“serdes”)128和裸晶114的可配置io接口电路(标记为“serdes”)132都被配置为差分io接口电路,以使得能够在裸晶108的处理电路(由“ckt”标记)134与裸晶114的处理电路(由“ckt”标记)138之间进行封装间通信,其中,处理电路138用于执行裸晶114的指定功能。应当指出的是,同一裸晶中的所有可配置io接口电路可具有相同的电路设计(例如,相同的sip块/内核),或者,同一封装中的所有可配置io接口电路可以具有相同的电路设计(例如,相同的sip块/内核),或者,同一多封装系统中的所有可配置io接口电路可以具有相同的电路设计(例如,相同的sip块/内核),具体地,本发明实施例不做限制。可

配置io接口电路采用的该相同电路设计可以分为tx设计和rx设计,以实现serdes io功能。

43.图3是根据本发明实施例示出的第一tx设计的示意图,该第一tx设计是被可配置io接口电路采用的电路设计的一部分。tx电路300包括tx时钟产生器(tx clock generator)301和多个信道电路(例如,302_1和302_2)。为了简洁起见,在图3中仅示出了两个信道电路。实际上,可以根据实际的设计考量来调整信道电路的数量,具体地,本发明实施例不做限制。在tx电路300中实现的所有信道电路可以具有相同的电路设计。如图3所示,信道电路(由“ckt_ch1”标记)302_1包括多工器(multiplexer)(由“mux”标记)304_1和驱动电路(由“drv”标记)306_1(其可以包括,例如,前置驱动器和驱动器),以及,信道电路(由“ckt_ch2”标记)302_2包括多工器(由“mux”标记)304_2和驱动电路(由“drv”标记)306_2(其可以包括,例如,前置驱动器和驱动器)。tx时钟产生器301被设计为采用时钟产生技术(例如,锁相环),以根据参考时钟refck产生信道电路302_1和302_2的内部组件的正常操作所需的时钟。关于信道电路302_1,多工器304_1被布置为对并行(parallel)数据输入tx_in1<m:1>进行复用(multiplex)以产生串行(serial)数据输出d_out1,以及,驱动电路306_1被布置为根据串行数据输出d_out1产生并输出tx比特流tx_out1。关于信道电路302_2,多工器304_2被布置为对并行数据输入tx_in2<m:1>进行复用以产生串行数据输出d_out2,以及,驱动电路306_2被布置为根据串行数据输出d_out2产生并输出tx比特流tx_out2。

44.当任意可配置io接口电路采用上述相同的电路设计(其包括图3所示的tx设计)时,tx电路300被配置为作为(act as)用于封装内(裸晶到裸晶)通信的单端io接口的一部分,或者,被配置为作为用于封装间(芯片到芯片)通信的差分io接口的一部分。

45.图4是示出将tx电路300配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。当可配置io接口电路126和130的每一个采用上述相同的电路设计(其包括图3所示的tx设计)时,可配置io接口电路126和130的每一个具有被配置为用于单端封装内(裸晶到裸晶)通信的tx电路300。以可配置io接口电路126为例,图3所示的并行数据输入tx_in1<m:1>和tx_in2<m:1>分别被设置为从处理电路134(特别地,处理电路134的数字物理层(physical layer,phy)组件)获得的单端非时钟数据输入txdin1<m:1>和txdin2<m:1>,以及,图3所示的tx比特流tx_out1和tx_out2分别被设置为单端tx比特流tx_1和tx_2,其中,通过裸晶108和112之间的pkg走线122的一部分,单端tx比特流tx_1和tx_2被从可配置io接口电路126(其可以是模拟phy组件的一部分)发送到可配置io接口电路130。

46.由于相关领域的技术人员能够容易地理解将图4所示的相同tx结构应用至其它可配置io接口电路的细节,该其它可配置io接口电路被配置为执行单端封装内(裸晶到裸晶)通信,因此,为简洁起见,这里省略了类似的描述。

47.图5是示出将tx电路300配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。当可配置io接口电路128和132的每一个采用上述相同的电路设计(其包括图3所示的tx设计)时,可配置io接口电路128和132的每一个具有被配置为用于差分封装间(芯片到芯片)通信的tx电路300。以可配置io接口电路128为例,图3所示的并行数据输入tx_in1<m:1>和tx_in2<m:1>被设置为从处理电路134(特别是处理电路134的数字phy组件)获得的差分非时钟数据输入(包括正(positive)数据输入txdp1<m:1>和负(negative)数据输入txdn1<m:1>),以及,图3所示的tx比特流tx_out1和tx_out2被设置为

差分tx比特流(包括正比特流txp_1和负比特流txn_1),其中,正数据输入txdp1<m:1>和负数据输入txdn1<m:1>的每一个分别是并行数据输入,以及,处理电路134可以包括反相器(inverter)inv,该反相器inv被布置为生成正数据输入txdp1<m:1>的反相版本(inverse version)并作为负数据输入txdn1<m:1>,以及,经由裸晶108和裸晶114之间的pcb走线124的一部分,差分tx比特流(例如,txp_1,txn_1)被从可配置io接口电路128(其可以是模拟phy组件的一部分)传输到可配置io接口电路132。

48.由于相关领域的技术人员能够容易地理解将图5所示的相同tx结构应用至其它可配置io接口电路的细节,该其它可配置io接口电路被配置为执行差分封装间(裸晶到裸晶)通信,因此,为简洁起见,这里省略了类似的描述。

49.在一些实施例中,时钟和数据恢复(clock and data recovery,cdr)电路可以被实现在rx电路中,从而,不需要将时钟数据从tx电路传输到rx电路。关于采用图4所示的用于单端封装内(裸晶到裸晶)通信的tx结构的任何可配置io接口电路,不需要在封装内走线上传送上述单端时钟数据输入。关于采用图5所示的用于差分封装间(芯片对芯片)通信的tx结构的任何可配置io接口电路,不需要在封装间走线上传送上述差分时钟数据输入。

50.在一些实施例中,可以采用时钟转发(forwarding)方案,以从rx电路移除cdr电路,进而节省功率。因此,需要将时钟数据从tx电路发送到rx电路。换句话说,如果可配置io接口电路被配置为执行单端封装内(裸晶到裸晶)通信,则该可配置io接口电路应当发送专用的(dedicated)单端时钟数据比特流(bitstream)(其具有指示时钟信息的规则比特模式(regular bit pattern)),以及,如果可配置io接口电路被配置为执行差分封装间(芯片到芯片)通信,则该可配置io接口电路应当发送专用的差分时钟数据比特流(其具有指示时钟信息的规则比特模式)。

51.图6是示出将tx电路300配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施例的示意图。当可配置io接口电路126和130的每一个采用上述相同的电路设计(其包括图3所示的tx设计)时,可配置io接口电路126和130的每一个具有被配置为用于单端封装内(裸晶到裸晶)通信的tx电路300。以可配置io接口电路126为例,图3所示的并行数据输入tx_in1<m:1>和tx_in2<m:1>分别被从处理电路134(特别是处理电路134的数字phy组件)获得的单端时钟数据输入txdinck<m:1>和单端非时钟数据输入txdin1<m:1>设置,以及,图3所示的tx比特流tx_out1和tx_out2分别被单端tx比特流tx_ck和tx_1设置,其中,单端tx比特流tx_ck具有指示时钟信息的规则比特模式,以及,通过裸晶108和裸晶112之间的pkg走线122的一部分,单端tx比特流tx_ck和tx_1被从可配置io接口电路126(其可以是模拟phy组件的一部分)发送到可配置io接口电路130。

52.由于相关领域的技术人员能够容易地理解将图6所示的相同tx结构应用至其它可配置io接口电路的细节,该其它可配置io接口电路被配置为执行单端封装内(裸晶到裸晶)通信,因此,为简洁起见,这里省略了类似的描述。

53.图7是示出将tx电路300配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的另一实施例的示意图。当可配置io接口电路128和132的每一个采用上述相同的电路设计(其包括图3所示的tx设计)时,可配置io接口电路128和132的每一个具有被配置为用于差分封装间(芯片到芯片)通信的tx电路300。以可配置io接口电路128为例,图3所示的并行数据输入tx_in1<m:1>和tx_in2<m:1>被设置为从处理电路134(特别是处理电路134的数

字phy组件)获得的差分时钟数据输入,该差分时钟数据输入包括正时钟数据输入txdckp<m:1>和负时钟数据输入txdckn<m:1>,以及,图3所示的tx比特流tx_out1和tx_out2被设置为由正比特流tx_ckp和负比特流tx_ckn组成的差分tx比特流,其中,正时钟数据输入txdckp<m:1>和负时钟数据输入txdckn<m:1>中的每一个是并行数据输入,处理电路134可以包括反相器inv,该反相器inv被布置为生成正时钟数据输入txdckp<m:1>的反相版本并作为负时钟数据输入txdckn<m:1>,以及,通过裸晶108和裸晶114之间的pcb走线124的一部分,具有指示时钟信息的规则比特模式的差分tx比特流(tx_ckp,tx_ckn)被从可配置io接口电路128(其可以是模拟phy组件的一部分)传输到可配置io接口电路132。

54.由于相关领域的技术人员能够容易地理解将图7所示的相同tx结构应用至其它可配置io接口电路的细节,该其它可配置io接口电路被配置为执行差分封装间(芯片到芯片)通信,因此,为简洁起见,这里省略了类似的描述。

55.图8是根据本发明实施例示出的第二tx设计的示意图,该第二tx设计是由可配置io接口电路采用的电路设计的一部分。tx电路800包括多个信道电路(例如,802_1和802_2)和上述的tx时钟产生器301。为简洁起见,图8中仅示出了两个信道电路。实际上,可以根据实际设计考量来调整信道电路的数量,具体地,本发明实施例不做限制。在tx电路800中实现的所有信道电路可以具有相同的电路设计。如图8所示,信道电路(由“ckt_ch1”标记)802_1包括上述的多工器(由“mux”标记)304_1和驱动电路(由“drv”标记)806_1(例如,其可以包括前置驱动器和驱动器),以及,信道电路(用“ckt_ch2”标记)802_2包括上述的多工器(用“mux”标记)304_2和驱动电路(用“drv”标记)806_2(例如,可以包括前置驱动器和驱动器)。驱动电路306_1和806_1之间的主要区别在于,驱动电路806_1被示为具有辅助(auxiliary)电路(由“aux”标记)808_1。类似地,驱动电路306_2和806_2之间的主要区别在于,驱动电路806_2被示为具有辅助电路(由“aux”标记)808_2。

56.tx时钟产生器301被设计为采用时钟产生技术(例如,锁相环),以根据参考时钟refck产生信道电路802_1和802_2的内部组件的正常操作所需的时钟。关于信道电路802_1,多工器304_1被布置为对并行数据输入tx_in1<m:1>进行复用以产生串行数据输出d_out1,驱动电路806_1被布置为根据串行数据输出d_out1产生并输出tx比特流tx_out1,以及,被实现在驱动电路806_1中的辅助电路808_1被设置为根据相同的串行数据输出d_out1生成tx比特流tx_aux1,其中,tx比特流tx_aux1是tx比特流tx_out1的反相版本,从而,从驱动电路806_1输出的tx比特流tx_out1和tx_aux1能够构成差分tx比特流。关于信道电路802_2,多工器304_2被布置为对并行数据输入tx_in2<m:1>进行复用以产生串行数据输出d_out2,驱动电路806_2被布置为根据串行数据输出d_out2产生并输出tx比特流tx_out2,以及,被实现在驱动电路806_2中的辅助电路808_2被设置为根据相同的串行数据输出d_out2生成tx比特流tx_aux2,其中,tx比特流tx_aux2是tx比特流tx_out2的反相版本,从而,从驱动电路806_2输出的tx比特流tx_out2和tx_aux2能够构成差分tx比特流。

57.当任一可配置io接口电路采用上述电路设计(其包括图8所示的tx设计)时,tx电路800被配置为作为用于封装内(裸晶到裸晶)通信的单端io接口的一部分,或者,被配置为作为用于封装间(芯片到芯片)通信的差分io接口的一部分。

58.图9是示出将tx电路800配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。当可配置io接口电路126和130的每一个采用该相同的电路设计

(其包括图8所示的tx设计)时,可配置io接口电路126和130的每一个具有被配置为用于单端封装内(裸晶到裸晶)通信的tx电路800。以可配置io接口电路126为例,图8所示的并行数据输入tx_in1<m:1>和tx_in2<m:1>分别被设置为从处理电路134(特别是处理电路134的数字phy组件)获得的单端非时钟数据输入txdin1<m:1>和txdin2<m:1>,以及,图8所示的tx比特流tx_out1和tx_out2分别被设置为单端tx比特流tx_1和tx_2,其中,辅助电路808_1不输出tx比特流tx_aux1至裸晶108和112之间的任何pkg走线122,辅助电路808_2不输出tx比特流tx_aux2至裸晶108和112之间的任何pkg走线122,以及,经由裸晶108和112之间的pkg走线122的一部分,单端tx比特流tx_1和tx_2被从可配置io接口电路126(其可以是模拟phy组件的一部分)传输到可配置io接口电路130。在一些实施例中,在可配置io接口电路126被配置为执行单端封装内(裸晶到裸晶)通信的情况下,辅助电路808_1和808_2可以被配置为被禁用(或断电)。因此,裸晶108不具有被分配给辅助电路808_1和808_2的输出的引脚。

59.由于相关领域的技术人员能够容易地理解应用图9所示的相同tx结构至其它可配置io接口电路的细节,该其它可配置io接口电路被配置为执行单端封装内(裸晶到裸晶)通信,因此,为简洁起见,在此省略类似的描述。

60.图10是示出将tx电路800配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。当可配置io接口电路128和132的每一个采用该相同的电路设计(其包括图8所示的tx设计)时,可配置io接口电路128和132的每一个具有被配置为用于差分封装间(芯片到芯片)通信的tx电路800。以可配置io接口电路128为例,图8所示的并行数据输入tx_in1<m:1>和tx_in2<m:1>分别被设置为从处理电路134(特别是处理电路134的数字phy组件)获得的单端非时钟数据输入txdin1<m:1>和txdin2<m:1>,图8所示的tx比特流tx_out1和tx_aux1被设置为由正比特流txp_1和负比特流txn_1组成的差分tx比特流,以及,图8所示的tx比特流tx_out2和tx_aux2被设置为由正比特流txp_2和负比特流txn_2组成的差分tx比特流,其中,驱动电路806_1通过利用辅助电路808_1来启用单端到差分转换功能(single

‑

ended

‑

to

‑

differential conversion function),以产生并输出差分tx比特流(txp_1,txn_1)至pcb走线124的一部分,以及,驱动电路806_2通过利用辅助电路808_2来启用单端至差分转换功能,以产生并输出差分tx比特流(txp_2,txn_2)至pcb走线124的一部分,从而,差分比特流(txp_1,txn_1)和(txp_2,txn_2)的每一个被从可配置io接口电路128(其可以是模拟phy组件的一部分)发送到可配置io接口电路132。

61.由于相关领域的技术人员能够容易地理解应用图10所示的相同tx结构至其它可配置io接口电路的细节,其中,该其它可配置io接口电路被配置为执行差分封装间(芯片到芯片)通信,因此,为简洁起见,在此省略类似的描述。

62.如上所述,cdr电路可以被实现在rx电路中,从而,不需要将时钟数据从tx电路传输到rx电路。关于采用图9所示的用于单端封装内(裸晶到裸晶)通信的tx结构的任何可配置io接口电路,不需要在pkg走线上传输单端时钟数据输入。关于采用图10所示的用于差分封装间(芯片对芯片)通信的tx结构的任何可配置io接口电路,不需要在pcb走线上传输差分时钟数据输入。

63.如上所述,可以采用时钟转发方案,以从rx电路中移除cdr电路,进而节省功耗。因此,需要将时钟数据从tx电路发送到rx电路。换句话说,如果可配置io接口电路被配置为执行单端封装内(裸晶到裸晶)通信,则可配置io接口电路应传输专用的单端时钟数据比特流

(其具有指示时钟信息的规则比特模式),以及,如果可配置io接口电路被配置为执行差分封装间(芯片到芯片)通信,则可配置io接口电路应传输专用的差分时钟数据比特流(其具有指示时钟信息的规则比特模式)。

64.图11是示出将tx电路800配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施例的示意图。当可配置io接口电路126和130的每一个采用该相同的电路设计(其包括图8所示的tx设计)时,可配置io接口电路126和130的每一个具有被配置为用于单端封装内(裸晶到裸晶)通信的tx电路800。以可配置io接口电路126为例,图8所示的并行数据输入tx_in1<m:1>和tx_in2<m:1>分别被设置为从处理电路134(特别是处理电路的数字phy组件)获得的单端时钟数据输入txdinck<m:1>和单端非时钟数据输入txdin1<m:1>,图8所示的tx比特流tx_out1被设置为单端tx比特流tx_ck,其中,该单端tx比特流tx_ck具有指示时钟信息的规则比特模式,以及,图8中所示的tx比特流tx_out2被设置为单端tx比特流tx_1。其中,辅助电路808_1不输出tx比特流tx_aux1至裸晶108和112之间的任何pkg走线122,辅助电路808_2不输出tx比特流tx_aux2至裸晶108和112之间的任何pkg走线122,以及,经由裸晶108和112之间的pkg走线122的一部分,单端tx比特流tx_ck和tx_1被从可配置io接口电路126(其可以是模拟phy组件的一部分)传输到可配置io接口电路130。在一些实施例中,在可配置io接口电路126被配置为执行单端封装内(裸晶到裸晶)通信的情况下,辅助电路808_1和808_2可以被禁用(或断电)。因此,裸晶108可以不具有被分配给辅助电路808_1和808_2的输出的引脚。

65.由于相关领域的技术人员能够容易地理解应用图11所示的相同tx结构至其它可配置io接口电路的细节,该其它可配置io接口电路被配置为执行单端封装内(裸晶到裸晶)通信,因此,为简洁起见,这里省略了类似的描述。

66.图12是说明将tx电路800配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的另一实施例的示意图。当可配置io接口电路128和132的每一个采用该相同的电路设计(其包括图8所示的tx设计)时,可配置io接口电路128和132的每一个具有被配置为用于差分封装间(芯片到芯片)通信的tx电路800。以可配置io接口电路128为例,图8所示的并行数据输入tx_in1<m:1>和tx_in2<m:1>分别被设置为从处理电路134(特别是处理电路的数字phy组件)获得的单端时钟数据输入txdinck<m:1>和单端非时钟数据输入txdin1<m:1>,图8所示的tx比特流tx_out1和tx_aux1被设置为由正比特流tx_ckp和负比特流tx_ckn组成的差分tx比特流,以及,图8所示的tx比特流tx_out2和tx_aux2被设置为由正比特流txp_1和负比特流txn_1组成的差分tx比特流,其中,驱动电路806_1通过利用辅助电路808_1来实现单端至差分转换功能,以生成并输出差分tx比特流(tx_ckp,tx_ckn)至pcb走线124的一部分,以及,驱动电路806_2通过利用辅助电路808_2来实现单端至差分转换功能,以生成并输出差分tx比特流(txp_1,txn_1)至pcb走线124的一部分,从而,差分比特流(tx_ckp,tx_ckn)和(txp_1,txn_1)的每一个被从可配置io接口电路128(其可以是模拟phy组件的一部分)发送至可配置io接口电路132。

67.由于相关领域的技术人员能够容易地理解应用图12所示的相同tx结构至其它被配置为执行差分封装间(芯片到芯片)通信的可配置io接口电路的细节,因此,为简洁起见,这里省略了类似的描述。

68.图13是根据本发明实施例示出的第一rx设计的示意图,该第一rx设计是由可配置

io接口电路采用的电路设计的一部分。rx电路1300包括rx时钟产生器1301和多个信道电路(例如,1302_1和1302_2)。为了简洁起见,在图13中仅示出了两个信道电路。实际上,可以根据实际设计考量来调整信道电路的数量,具体地,本发明实施例不做限制。在rx电路1300中实现的所有信道电路可以具有相同的电路设计。如图13所示,信道电路(标记为“ckt_ch1”)1302_1包括rx前端(front

‑

end)电路(标记为“rxfe”)1304和后处理电路(post

‑

processing circuit)1306。rx时钟产生器1301被设计为采用时钟生成技术(例如,锁相环),以根据参考时钟refck产生信道电路1302_1和1302_2的内部组件的正常操作所需的时钟。rx前端电路1304包括比较器或比较器电路(comparator circuit,标记为“cmp”)1308,比较器电路1308具有第一输入节点n1,第二输入节点n2和输出节点n3,其中,rx前端电路1304产生的串行数据输入d_in1是在输出节点n3处从比较器输出得到的,换句话说,比较器电路1308的输出(即输出节点n3处的数据)被作为rx前端电路1304产生的串行数据输入d_in1。后处理电路1306被布置为根据串行数据输入d_in1产生并输出并行数据输入rx_in1<m:1>。后处理电路1306可以包括一个或多个后处理模块,例如,数据攫取器(slicer)1310,判决反馈均衡器(decision feedback equalizer,dfe)1312,解多工器(demultiplexer,demux)1314,和/或,时钟和数据恢复电路(标记为“cdr”)1316。由于信道电路1302_1和1302_2具有相同的电路设计,因此,类似地,信道电路1302_2产生并输出并行数据输入rx_in2<m:1>。可以理解地,数据攫取器1310用于根据时钟信号将输入的数据信号攫取下来。

69.当任何可配置io接口电路采用该电路设计(其包括图13所示的rx设计)时,rx电路1300被配置为作为用于封装内(裸晶到裸晶)通信的单端io接口的一部分,或者,被配置为作为用于封装间(芯片到芯片)通信的差分io接口的一部分。

70.图14是示出将rx电路1300配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。当可配置io接口电路126和130的每一个采用该相同的电路设计(其包括图13所示的rx设计)时,可配置io接口电路126和130的每一个具有被配置为用于单端封装内(裸晶到裸晶)通信的rx电路1300。以可配置io接口电路126为例,信道电路1302_1接收一个单端rx比特流rx_1(其是通过pkg走线122的一部分传送的),以及,信道电路1302_2接收另一单端rx比特流rx_2(其是通过pkg走线122的一部分传送的),从而,响应于单端rx比特流rx_1(其不是具有规则比特模式的专用时钟数据比特流)信道电路1302_1产生并输出并行数据输入rx_in1<m:1>,以及,响应于单端rx比特流rx_2(其不是具有规则比特模式的专用时钟数据比特流),信道电路1302_2产生并输出并行数据输入rx_in2<m:1>。

71.在该实施例中,被实现在可配置io接口电路126中的每一个信道电路的后处理电路1306包括cdr电路1316。因此,可配置io接口电路126不接收专用的单端时钟数据比特流。以信道电路1302_1为例,比较器1308的第一输入节点n1被配置为接收单端rx比特流rx_1,比较器1308的第二输入节点n2被配置为接收参考电压vref,即裸晶108的内部电压(即,内部或固有产生的电压,例如,在一些实施例中,由辅助电路/辅助处理电路产生参考电压vref)。可配置io接口电路126(其可以是模拟phy组件的一部分)获得的并行数据输入rx_in1<m:1>和rx_in2<m:1>被提供给处理电路134(特别是处理电路134的数字phy组件),以进行进一步处理。

72.由于相关领域的技术人员能够容易地理解应用图14所示的相同rx结构至被配置为执行单端封装内(裸晶到裸晶)通信的其它可配置io接口电路的细节,因此,为简洁起见,

这里省略了类似的描述。

73.图15是示出将rx电路1300配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施方式的示意图。当可配置io接口电路126和130的每一个采用该相同的电路设计(其包括图13所示的rx设计)时,可配置io接口电路126和130的每一个具有被配置为用于单端封装内(裸晶到裸晶)通信的rx电路1300。以可配置io接口电路126为例,信道电路1302_1接收一个单端rx比特流rx_1(其是通过pkg走线122的一部分传送的),而信道电路1302_2接收另一单端rx比特流rx_2(其是通过pkg走线122的一部分传送的),从而,响应于单端rx比特流rx_1(其不是具有规则比特模式的专用时钟数据比特流),信道电路1302_1产生并输出并行数据输入rx_in1<m:1>,以及,响应于单端rx比特流rx_2(其不是具有规则比特模式的专用时钟数据比特流),信道电路1302_2产生并输出并行数据输入rx_in2<m:1>。

74.在本实施例中,被实现在可配置io接口电路126中的每一个信道电路的后处理电路1306包括cdr电路1316。因此,可配置io接口电路126不接收单端时钟数据比特流。以信道电路1302_1为例,比较器1308的第一输入节点n1被配置为接收单端rx比特流rx_1,比较器1308的第二输入节点n2被配置为接收参考电压vref,其是被提供给裸晶108的外部电压(即,在外部产生的电压)。由可配置io接口电路126(其可以是模拟phy组件的一部分)获得的并行数据输入rx_in1<m:1>和rx_in2<m:1>被提供给处理电路134(特别是处理电路134的数字phy组件),以进行进一步处理。

75.由于相关领域的技术人员能够容易地理解应用图15所示的相同rx结构至被配置为用于执行单端封装内(裸晶到裸晶)通信的其它可配置io接口电路的细节,因此,为简洁起见,在此省略类似的描述。

76.图16是示出将rx电路1300配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。当可配置io接口电路128和132的每一个采用该相同的电路设计(其包括图13所示的rx设计)时,可配置io接口电路128和132的每一个具有被配置为用于差分封装间(芯片到芯片)通信的rx电路1300。以可配置io接口电路128为例,信道电路1302_1接收由正比特流rxp_1和负比特流rxn_1组成的差分rx比特流(其是经由pcb走线124的一部分传送的),以及,信道电路1302_2接收由正比特流rxp_2和负比特流rxn_2组成的另一差分rx比特流(其是通过pcb走线124的一部分传送的),从而,响应于差分rx比特流(rxp_1,rxn_1),信道电路1302_1产生并输出并行数据输入rx_in1<m:1>,以及,响应于差分rx比特流(rxp_2,rxn_2),信道电路1302_2产生并输出并行数据输入rx_in2<m:1>,其中,差分rx比特流(rxp_1,rxn_1)和(rxp_2,rxn_2)都不是具有规则比特模式的专用时钟数据比特流。

77.在该实施例中,被实现在可配置io接口电路128中的每一个信道电路的后处理电路1306包括cdr电路1316。因此,可配置io接口电路128不接收差分时钟数据比特流。以信道电路1302_1为例,比较器1308的第一输入节点n1被配置为接收正rx比特流rxp_1,以及,比较器1308的第二输入节点n2被配置为接收负rx比特流rxn_1。由可配置io接口电路128(其可以是模拟phy组件的一部分)获得的并行数据输入rx_in1<m:1>和rx_in2<m:1>被提供给处理电路134(特别是处理电路134的数字phy组件),以进行进一步处理。

78.由于相关领域的技术人员能够容易地理解图16所示的相同rx结构应用至被配置为执行差分封装间(芯片到芯片)通信的其它可配置io接口电路的细节,因此,为简洁起见,在此省略类似的描述。

79.如图14至图16所示,被配置为用于单端封装内(裸晶到裸晶)通信的rx前端电路1304和被配置为用于差分封装间(芯片到芯片)通信的rx前端电路1304可以具有相同的有源(active)电路组件。然而,这仅出于说明的目的,并不意味着对本发明的限制。可替代地,被配置为用于单端封装内(裸晶到裸晶)通信的rx前端电路1304和被配置为用于差分封装间(芯片到芯片)通信的rx前端电路1304可以不具有相同的有源电路组件。

80.图17是根据本发明实施例示出的第二rx设计的示意图,该第二rx设计是由可配置io接口电路采用的电路设计的一部分。rx电路1700包括多个信道电路(例如,1702_1和1702_2)和前面提及的rx时钟产生器1301。为简洁起见,图17中仅示出了两个信道电路。实际上,可以根据实际设计考虑来调整信道电路的数量,具体地,本发明对此不做限制。被实现在rx电路1700中的所有信道电路可以具有相同的电路设计。信道电路1302_1和1702_1之间的主要区别在于,所示的rx前端电路1704具有辅助电路(标记为“aux”)1706。辅助电路1706被配置为应用(apply)辅助处理(auxiliary processing),以协助产生串行数据输入d_in1。例如,在第一示例中,辅助电路1706可以是为了实现单端模式(即输入为单端信号)的某些目的而设置的,诸如为了产生输入端的参考电压,在该示例中,当可配置io接口电路操作在差分模式(即输入为差分信号)时,辅助电路1706是关闭的或被禁用,而当操作在单端模式时,辅助电路1706是开启的或被使能。在第二示例中,辅助电路1706可以是为了差分模式的需要而设置的,例如,用于在差分模式中补偿信道特性,诸如减少前后码之间的相互干扰等,在该示例中,辅助电路1706可以被配置为对比较器的输出做进一步处理,以及,当可配置io接口电路操作在单端模式时,辅助电路1706是关闭的或被禁用,而当操作在差分模式时,辅助电路1706是开启的或被使能。在本发明实施例中,当rx电路1700所处的可配置io接口电路被配置为执行单端封装内(裸晶到裸晶)通信和差分封装间(芯片到芯片)通信的其中一者时,辅助电路1706被禁用或被关闭,以及,当rx电路1700所处的io接口电路被配置为执行单端封装内(裸晶到裸晶)通信和差分封装间(芯片到芯片)通信的另一者时,辅助电路1706被启用。例如,当比较器1308处于单端rx操作下时,应用辅助电路1706。对于另一示例,当比较器1308处于差分rx操作下时,应用辅助电路1706。

81.图18是示出将rx电路1700配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。当可配置io接口电路126和130的每一个采用该相同的电路设计(其包括图17所示的rx设计)时,可配置io接口电路126和130的每一个都将rx电路1700配置为用于单端封装内(裸晶到裸晶)的通信。作为示例而非限制,在一实施例中,在比较器1308接收到差分rx比特流时,辅助电路1706可以被布置为将辅助处理应用于位于比较器1308的输出节点n3处的比较器输出,以协助产生通道特性更好的d_in1。由于图18中所示的rx电路1700被配置为用于单端封装内(裸晶到裸晶)通信,因此,rx前端电路1704的辅助电路1706被禁用(或断电)。作为示例而非限制,图14中示出的被配置为用于单端封装内(裸晶到裸晶)通信的rx前端电路1304以及图18中所示的被配置为用于单端封装内(裸晶到裸晶)通信的rx前端电路1704可以具有相同的有源电路组件以及相同的数据处理功能。

82.图19是示出将rx电路1700配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施方式的示意图。当可配置io接口电路126和130的每一个采用该相同的电路设计(其包括图17所示的rx设计)时,可配置io接口电路126和130的每一个都将rx电路1700配置为用于单端封装内(裸晶到裸晶)的通信。作为示例而非限制,在比较器1308接收

差分rx比特流时,辅助电路1706可以被布置为将辅助处理应用于在比较器1308的输出节点n3处的比较器输出,以补偿信道特性。由于图19中所示的rx电路1700用于单端封装内(裸晶到裸晶)通信,因此,rx前端电路1704的辅助电路1706被禁用(或断电)。作为示例而非限制,图15所示的被配置为用于单端封装内(裸晶到裸晶)通信的rx前端电路1304和图19所示的被配置为用于单端封装内(裸晶到裸晶)通信的rx前端电路1704可以具有相同的有源电路组件以及相同的数据处理功能。

83.图20是示出将rx电路1700配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。当可配置io接口电路128和132的每一个采用该相同的电路设计(其包括图17所示的rx设计)时,可配置io接口电路128和132的每一个具有被配置为用于差分封装间(芯片到芯片)通信的rx电路1700。作为示例而非限制,在比较器1308接收到差分rx比特流时,辅助电路1706可以被布置为将辅助处理应用于在比较器1308的输出节点n3处的比较器输出。由于图20中所示的rx电路1700被配置为用于差分封装间(芯片到芯片)通信,rx前端电路1704的辅助电路1706被使能。应当注意,如图18和图19所示的被配置为用于单端封装内(裸晶到裸晶)通信的rx前端电路1704以及图20所示的被配置为用于差分封装间(芯片到芯片)通信的rx前端电路1704可以具有不同的有源电路组件布置以及不同的数据处理功能。作为示例而非限制,除了由辅助电路1706提供的辅助处理功能之外,图20所示的被配置成用于差分封装间(芯片到芯片)通信的rx前端电路1704以及图16所示的被配置为用于差分封装间(芯片到芯片)通信的rx前端电路1304可以具有相同的数据处理功能。

84.关于图13中所示的rx设计1300,实现了时钟和数据恢复电路1316,从而,不需要将时钟数据从tx电路发送到rx电路。因此,利用图14至图15和图18至图19中任何一个所示的rx设计的可配置io接口电路无需接收单端时钟数据比特流,以及,利用图16和图20中任何一个所示的rx设计的可配置io接口电路无需接收差分时钟数据比特流。在一些实施例中,tx电路可以采用时钟转发方案,以及,cdr电路可以从rx电路中移除以节省功率。因此,在serdes io接口中实现无cdr的rx电路的情况下,需要通过封装内部的走线将专用的单端时钟数据比特流(其具有指示时钟信息的规则比特模式)从tx电路传输到rx电路,以及,通过封装之间的走线将专用的差分时钟数据比特流(其具有指示时钟信息的规则比特模式)从tx电路传输到rx电路。

85.图21是根据本发明实施例示出的第三rx设计的示意图,该第三rx设计是由可配置io接口电路采用的电路设计的一部分。rx电路2100包括时钟数据信道电路2102_0和多个非时钟数据信道电路(例如,2102_1和2102_2)。为了简洁起见,图21中仅示出了两个非时钟数据信道电路。实际上,可以根据实际设计考量来调整非时钟数据信道电路的数量。被实现在rx电路2100中的所有非时钟数据信道电路可以具有相同的电路设计。如图21所示,时钟数据信道电路(标记为“ckt_ch0”)2102_0包括rx前端电路(标记为“rxfe”)2108和rx时钟产生器2110,以及,非时钟数据信道电路(标记为“ckt_ch1”)2102_1包括后处理电路2106和前面提及的rx前端电路(标记为“rxfe”)1304(或1704)。需要说明的是,如果本发明的非时钟数据信道电路2102_1使用rx前端电路1304,则不存在辅助电路1706,而如果本发明的非时钟数据信道电路2102_1使用rx前端电路1704,则可以根据可配置io接口电路的配置来选择性地启用或禁用辅助电路1706。

86.关于时钟数据信道电路2102_0,rx前端电路2108包括比较器或比较器电路(由

“

cmp”标记)2112,该比较器电路具有第一输入节点n1',第二输入节点n2'和输出节点n3',其中,串行数据输入d_ck是从rx前端电路2108生成的时钟数据输入,并且是从输出节点n3'处的比较器输出中得出的。时钟数据信道电路2102_0的rx时钟产生器2110被布置为根据串行数据输入d_ck产生非时钟数据信道电路2102_1和2102_2的内部组件的正常操作所需的rx数据时钟rxck_2rxdata。

87.关于非时钟数据信道电路2102_1,rx前端电路1304/1704被布置为生成串行数据输入d_in1,以及,后处理电路2106被布置为根据串行数据输入d_in1产生并输出并行数据输入rx_in1<m:1>。后处理电路2106可以包括一个或多个后处理模块,例如,数据攫取器1310,判决反馈均衡器(dfe)1312和/或解多工器(demux)1314。应注意,时钟和数据恢复电路没有被实现在后处理电路2106中。由于非时钟数据信道电路2102_1和2102_2具有相同的电路设计,因此,类似地,从非时钟数据信道电路2102_2输出并行数据输入rx_in2<m:1>。

88.当任何可配置io接口电路采用该电路设计(其包括图21所示的rx设计)时,rx电路2100可以被配置为用作单端封装内(裸晶到裸晶)通信的单端io接口的一部分或者被配置为用作封装间(芯片到芯片)通信的差分io接口的一部分。

89.图22是示出将rx电路2100配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的实施例的示意图。当可配置io接口电路126和130的每一个采用相同的电路设计(其包括图21所示的rx设计)时,可配置io接口电路126和130的每一个的rx电路2100被配置为用于单端封装内(裸晶到裸晶)的通信。以可配置io接口电路126为例,每一个非时钟数据信道电路的后处理电路2106没有cdr电路,可配置io接口电路126(特别是时钟数据信道电路2102_0)接收通过pkg走线122的一部分传送过来的单端时钟数据比特流。更具体地,比较器2112的第一输入节点n1'被配置为接收单端rx比特流rx_ck(即单端时钟数据比特流),以及,比较器2112的第二输入节点n2'被配置为接收参考电压vref,该参考电压vref是裸晶108的内部电压(即,内部或固有产生的电压)。rx前端电路2108从输出节点n3'处的比较器输出获得串行数据输入d_ck,以及,rx时钟产生器2110根据串行数据输入d_ck产生rx数据时钟rxck_2rxdata,并将rx数据时钟rxck_2rxdata提供给非时钟数据信道电路2102_1和2102_2的每一个。在可配置io接口电路126(其可以是模拟phy组件的一部分)获得的并行数据输入rx_in1<m:1>和rx_in2<m:1>被提供给处理电路134(特别是处理电路134的数字phy组件),以进行进一步处理。

90.由于相关领域的技术人员能够容易地理解应用图22所示的相同rx结构至被配置为执行单端封装内(裸晶到裸晶)通信的其它可配置io接口电路的细节,因此,为简洁起见,在此省略类似的描述。

91.图23是示出将rx电路2100配置为用于封装内(裸晶到裸晶)通信的单端io接口的一部分的另一实施方式的示意图。当可配置io接口电路126和130的每一个采用上述相同的电路设计(其包括图21所示的rx设计)时,可配置io接口电路126和130的每一个的rx电路2100被配置为用于单端封装内(裸晶到裸晶)的通信。以可配置io接口电路126为例,每一个非时钟数据信道电路的后处理电路2106没有cdr电路,可配置io接口电路126(特别是时钟数据信道电路2102_0)接收通过pkg走线122的一部分传送过来的单端时钟数据比特流。更具体地,比较器2112的第一输入节点n1'被配置为接收单端rx比特流rx_ck(即该单端时钟数据比特流),以及,比较器2112的第二输入节点n2'被配置为接收参考电压vref,该参考电

压vref是提供给裸晶108的外部电压(即,在外部产生的电压)。rx前端电路2108从输出节点n3'处的比较器输出获得串行数据输入d_ck,以及,rx时钟产生器2110根据串行数据输入d_ck产生rx数据时钟rxck_2rxdata,并将rx数据时钟rxck_2rxdata提供给非时钟数据信道电路2102_1和2102_2的每一个。由可配置io接口电路126(其可以是模拟phy组件的一部分)获得的并行数据输入rx_in1<m:1>和rx_in2<m:1>被提供给处理电路134(特别是处理电路134的数字phy组件),以进行进一步处理。

92.由于相关领域的技术人员能够容易地理解应用图23所示的相同rx结构至被配置为执行单端封装内(裸晶到裸晶)通信的其它可配置io接口电路的细节,因此,为简洁起见,在此省略类似的描述。

93.图24是示出将rx电路2100配置为用于封装间(芯片到芯片)通信的差分io接口的一部分的实施例的示意图。当可配置io接口电路128和132的每一个采用该相同的电路设计(其包括图21所示的rx设计)时,可配置io接口电路128和132的每一个具有被配置为用于差分封装间(芯片到芯片)通信的rx电路2100。以可配置io接口电路128为例,每一个非时钟数据信道电路的后处理电路2106不具有cdr电路,以及,可配置io接口电路128(特别是时钟数据信道电路2102_0)接收通过pcb走线124的一部分传输过来的差分时钟数据比特流。时钟数据信道电路2102_0被配置为接收差分rx比特流(即差分时钟数据比特流),其中,差分rx比特流由正rx比特流rx_ckp和负rx比特流rx_ckn组成。更具体地说,比较器2112的第一输入节点n1’被配置为接收正rx比特流rx_ckp,比较器2112的第二输入节点n2’被配置为接收负rx比特流rx_ckn。rx前端电路2108从输出节点n3’处的比较器输出获得串行数据输入d_ck,以及,rx时钟产生器2110根据串行数据输入d_ck产生rx数据时钟rxck_2rxdata,并将rx数据时钟rxck_2rxdata提供给非时钟数据信道电路2102_1和2102_2的每一个。由可配置io接口电路126(其可以是模拟phy组件的一部分)获得的并行数据输入rx_in1<m:1>和rx_in2<m:1>被提供给处理电路134(特别是处理电路134的数字phy组件),以进行进一步处理。

94.由于相关领域的技术人员能够容易地理解应用图24所示的相同rx结构至被配置为执行差分封装间(芯片到芯片)通信的其它可配置io接口电路的细节,因此,为简洁起见,这里省略了类似的描述。

95.此外,对于本文所使用之任何复数和/或单数形式之词语,本领域熟练技术人员可根据语境和/或应用场景是否合适而将复数转换至单数和/或将单数转换至复数。为清晰起见,此处即对文中单数/复数之间的各种置换作出明确规定。

96.虽然本发明已经通过示例的方式以及依据优选实施例进行了描述,但是,应当理解的是,本发明并不限于公开的实施例。相反,它旨在覆盖各种变型和类似的结构(如对于本领域技术人员将是显而易见的),例如,不同实施例中的不同特征的组合或替换。因此,所附权利要求的范围应被赋予最宽的解释,以涵盖所有的这些变型和类似的结构。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。