[0001]

本发明涉及存储器领域。具体地,本发明涉及可以很容易地直接访问到ecc阵列模块从而在读操作和写操作的过程中很容易地切换多种模式的存储器及其存储方法和对应的电子设备。

背景技术:

[0002]

纠错码(error correction code,ecc)是一种对数据进行检错和纠错的方法。它利用在一定长度数据位的基础上增加额外的数据来实现检错和纠错功能,这些额外的数据称为校验位。校验位的长度根据选定的ecc算法来确定。

[0003]

在选定ecc算法之后,一定长度的数据位都存在与其对应的校验位,而这些校验位也需要阵列来存储。选定ecc算法之后的写入和读出过程如下:当n位数据从系统被写入存储器时,首先通过ecc编码模块经由选定的ecc算法产生该n位数据的m位校验位,然后n位数据和m位校验位一起被写入相应的存储阵列(如图1中所示)。当从存储器读出n位数据时,n位数据和m位校验位从各自的存储阵列中读出,被放大后送入ecc解码模块。ecc解码模块可以对错误进行检测和纠正,得到经纠正的n位数据(如图2中所示)。

[0004]

然而,在这种情况下,当对存储器进行测试时,为了实现不同的测试目标,可能会需要不同的特殊的数据拓扑。例如,可能需要为

‘

b11111111、

‘

b00000000、b10101010、

‘

b01010101、

‘

b11101111、

‘

b00010000等或者其他的任何数据拓扑。

[0005]

对于数据阵列而言,很容易实现这样的数据拓扑,因为数据阵列中存储的值就是外部系统所写入的值。但是,对于ecc阵列而言,ecc阵列中所存储的校验位是通过选定ecc算法由相应的数据位计算得到的。也就是说,校验位既与相应的数据位的值相关,又与所选定的ecc算法相关。因此,对于ecc阵列,很难或者不能得到特殊的数据拓扑。这就意味着对ecc阵列的测试结果将会是不真实或者不准确或者不精确的。

[0006]

因此,亟需解决现有技术中的上述技术问题。

技术实现要素:

[0007]

基于上述技术问题,本发明提出了一种存储器及其存储方法和对应的电子设备。本发明是基于这样的认识而提出的:如果存储器能够直接访问到ecc阵列模块,则它就可以很容易地控制在ecc阵列模块中实际所存储的数据的值,从而能够在ecc阵列模块中存储特殊拓扑数据;当然,同时,在这一过程中,不能够影响到ecc阵列模块的正常功能。针对此,本发明的存储器中引入了写选择模块和/或读选择模块,可以很容易地直接访问到ecc阵列模块,能够在写操作和读操作的过程中非常灵活地切换多种模式。

[0008]

根据本发明的第一方面,提供了一种存储器,包括:

[0009]

第一数据阵列模块,所述第一数据阵列模块用于存储第一n-m位数据;

[0010]

第二数据阵列模块,所述第二数据阵列模块用于存储第一m位数据;

[0011]

纠错码ecc阵列模块,所述第二数据阵列模块与所述ecc阵列模块的容量相同,所

述ecc阵列模块用于存储第二m位数据;

[0012]

ecc处理模块,所述ecc处理模块与所述第一数据阵列模块、所述第二数据阵列模块、所述ecc阵列模块连接,且所述ecc处理模块从所述第一数据阵列模块接收第一n-m位数据、从所述第二数据阵列模块接收第一m位数据以及从所述ecc阵列模块接收第二m位数据,以及所述ecc处理模块对所述第一n-m位数据、所述第一m位数据、所述第二m位数据进行处理,得到经处理的数据;

[0013]

选择模块,所述选择模块与所述第一数据阵列模块、所述第二数据阵列模块、所述ecc阵列模块、所述ecc处理模块连接,所述选择模块从所述第一数据阵列模块接收所述第一n-m位数据、从所述第二数据阵列接收第一m位数据、从所述ecc阵列模块接收所述第二m位数据以及从所述ecc处理模块接收所述经处理的数据,且根据一个选择控制指令而选择性地输出;

[0014]

其中,n、m均为正整数,且n大于m。

[0015]

根据本发明的存储器的一个优选实施方案,所述选择控制指令为第一读选择控制指令,所述选择模块根据所述第一读选择控制指令输出所述第一n-m位数据以及所述第一m位数据。

[0016]

根据本发明的存储器的一个优选实施方案,所述选择控制指令为第二读选择控制指令,所述选择模块根据所述第二读控制指令输出所述第一n-m位数据、所述第一m位数据以及所述第二m位数据。

[0017]

根据本发明的存储器的一个优选实施方案,所述ecc处理模块包括ecc解码模块,所述ecc解码模块对所述第一n-m位数据、所述第一m位数据和所述第二m位数据进行ecc解码,得到第一经纠正的n位数据以及第一经纠正的m位数据,且将所述第一经纠正的n位数据以及所述第一经纠正的m位数据输出至所述选择模块。

[0018]

根据本发明的存储器的一个优选实施方案,所述选择控制指令为第三读选择控制指令,所述选择模块根据所述第三读选择控制指令输出所述第一经纠正的n位数据以及所述第一经纠正的m位数据。

[0019]

根据本发明的存储器的一个优选实施方案,所述ecc处理模块包括ecc解码模块,所述ecc解码模块根据所述第二m位数据对所述第一n-m位数据和所述第一m位数据进行ecc解码,得到第二经纠正的n位数据,且将所述第二经纠正的n位数据输出至所述选择模块。

[0020]

根据本发明的存储器的一个优选实施方案,所述选择控制指令为第四读选择控制指令,所述选择模块根据所述第四读选择控制指令输出所述第二经纠正的n位数据。

[0021]

根据本发明的存储器的一个优选实施方案,所述选择控制指令为第五读选择控制指令,所述选择模块根据所述第五读选择控制指令输出所述第二经纠正的n位数据以及所述第二m位数据。

[0022]

根据本发明的存储器的一个优选实施方案,所述ecc处理模块包括ecc编码模块,所述ecc编码模块从输入端接收第二n位数据,对所述第二n位数据进行编码,得到第一m位数据,且将所述第一m位数据输出至所述选择模块。

[0023]

根据本发明的存储器的一个优选实施方案,所述选择模块从输入端接收第二m位数据。

[0024]

根据本发明的存储器的一个优选实施方案,所述第二m位数据是所述第二n位数据

的一部分。

[0025]

根据本发明的存储器的一个优选实施方案,所述选择控制指令为第一写选择控制指令,所述选择模块根据所述第一写选择控制指令将所述第一m位数据输出至所述ecc阵列模块,以及将所述第二m位数据输出至所述第二数据阵列模块。

[0026]

根据本发明的存储器的一个优选实施方案,所述选择控制指令为第二写选择控制指令,所述选择模块根据所述第二写选择控制指令将所述第一m位数据输出至所述第二数据阵列模块,以及将所述第二m位数据输出至所述ecc阵列模块。

[0027]

根据本发明的第二方面,提供了一种用于存储器的存储方法,所述存储器包括:第一数据阵列模块,所述第一数据阵列模块用于存储第一n-m位数据;第二数据阵列模块,所述第二数据阵列模块用于存储第一m位数据;纠错码ecc阵列模块,所述ecc阵列模块用于存储第二m位数据,所述第二数据阵列模块与所述ecc阵列模块的容量相同;ecc处理模块,所述ecc处理模块与所述第一数据阵列模块、所述第二数据阵列模块、所述ecc阵列模块连接;以及,选择模块,所述选择模块与所述第一数据阵列模块、所述第二数据阵列模块、所述ecc阵列模块、所述ecc处理模块连接;所述存储方法包括:

[0028]

所述ecc处理模块从所述第一数据阵列模块接收第一n-m位数据、从所述第二数据阵列模块接收第一m位数据以及从所述ecc阵列模块接收第二m位数据,以及所述ecc处理模块对所述第一n-m位数据、所述第一m位数据、所述第二m位数据进行处理,得到经处理的数据;

[0029]

所述选择模块从所述第一数据阵列模块接收所述第一n-m位数据、从所述第二数据阵列接收第一m位数据、从所述ecc阵列模块接收所述第二m位数据以及从所述ecc处理模块接收所述经处理的数据,且所述选择模块根据一个选择控制指令而选择性地输出;

[0030]

其中,n、m均为正整数,且n大于m。

[0031]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0032]

当所述选择控制指令为第一读选择控制指令时,所述选择模块根据所述第一读选择控制指令输出所述第一n-m位数据以及所述第一m位数据。

[0033]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0034]

当所述选择控制指令为第二读选择控制指令时,所述选择模块根据所述第二读控制指令输出所述第一n-m位数据、所述第一m位数据以及所述第二m位数据。

[0035]

根据本发明的存储方法的一个优选实施方案,所述ecc处理模块包括ecc解码模块;所述存储方法还包括:

[0036]

所述ecc解码模块对所述第一n-m位数据、所述第一m位数据和所述第二m位数据进行ecc解码,得到第一经纠正的n位数据以及第一经纠正的m位数据,且将所述第一经纠正的n位数据以及所述第一经纠正的m位数据输出至所述选择模块。

[0037]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0038]

当所述选择控制指令为第三读选择控制指令时,所述选择模块根据所述第三读选择控制指令输出所述第一经纠正的n位数据以及所述第一经纠正的m位数据。

[0039]

根据本发明的存储方法的一个优选实施方案,所述ecc处理模块包括ecc解码模块;所述存储方法还包括:

[0040]

所述ecc解码模块根据所述第二m位数据对所述第一n-m位数据和所述第一m位数

据进行ecc解码,得到第二经纠正的n位数据,且将所述第二经纠正的n位数据输出至所述选择模块。

[0041]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0042]

当所述选择控制指令为第四读选择控制指令时,所述选择模块根据所述第四读选择控制指令输出所述第二经纠正的n位数据。

[0043]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0044]

当所述选择控制指令为第五读选择控制指令时,所述选择模块根据所述第五读选择控制指令输出所述第二经纠正的n位数据以及所述第二m位数据。

[0045]

根据本发明的存储方法的一个优选实施方案,所述ecc处理模块包括ecc编码模块;所述存储方法还包括:

[0046]

所述ecc编码模块从输入端接收第二n位数据,对所述第二n位数据进行编码,得到第一m位数据,且将所述第一m位数据输出至所述选择模块。

[0047]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0048]

所述选择模块从输入端接收第二m位数据。

[0049]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0050]

所述第二m位数据是所述第二n位数据的一部分。

[0051]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0052]

当所述选择控制指令为第一写选择控制指令,所述选择模块根据所述第一写选择控制指令将所述第一m位数据输出至所述ecc阵列模块,以及将所述第二m位数据输出至所述第二数据阵列模块。

[0053]

根据本发明的存储方法的一个优选实施方案,所述存储方法还包括:

[0054]

当所述选择控制指令为第二写选择控制指令时,所述选择模块根据所述第二写选择控制指令将所述第一m位数据输出至所述第二数据阵列模块,以及将所述第二m位数据输出至所述ecc阵列模块。

[0055]

根据本发明的第三方面,提供了一种电子设备,所述电子设备包括:

[0056]

至少一个上述的存储器;以及

[0057]

至少一个处理器,所述处理器与所述存储器连接,且所述处理器与所述存储器通过所述总线进行通信,所述处理器对所述存储器中数据进行处理。

[0058]

根据本发明的第四方面,提供了一种电子设备,所述电子设备包括:

[0059]

至少一个存储器,在所述存储器上存储有计算机可执行指令;以及

[0060]

至少一个处理器,所述处理器与所述存储器连接,且所述处理器与所述存储器通过所述总线进行通信,当所述处理器执行所述计算机可执行指令时,所述计算机可执行指令使得所述处理器执行上述的存储方法。

附图说明

[0061]

通过下文结合对附图的说明,将更容易理解本发明,在附图中:

[0062]

图1示出了已知的包含ecc功能的存储器的写入过程。

[0063]

图2示出了已知的包含ecc功能的存储器的读出过程。

[0064]

图3是根据本发明的一个实施方案的写入过程的示意图。

[0065]

图4是根据本发明的一个实施方案的读出过程的示意图。

[0066]

图5是根据本发明的另一实施方案的读出过程的示意图。

[0067]

图6是根据本发明的一个实施方案的读出方法的流程图。

[0068]

图7是根据本发明的一个实施方案的写入方法的流程图。

具体实施方式

[0069]

下面将结合附图来对本发明的实施方案进行进一步详述。

[0070]

图3是根据本发明的一个实施方案的写入过程的示意图。

[0071]

图3中也示意性示出了写入过程中所涉及的存储器的构成,所述存储器包括:第一数据阵列模块310、第二数据阵列模块320、纠错码ecc阵列模块330、ecc编码模块340和写选择模块350。

[0072]

从图3中可以看到,ecc编码模块340与写选择模块350连接,且ecc编码模块340从一个输入端接收n位数据,对n位数据进行编码,得到m位校验数据,且将所述m位校验数据输出至写选择模块350。

[0073]

从图3中还可以看到,写选择模块350除了从ecc编码模块340接收m位校验数据之外,还可以从所述输入端接收n位数据中的m位数据,且根据写选择控制指令sel_wr_mode而将m位校验数据或者所述n位数据中的m位数据选择性地写入至第二数据阵列模块320或者ecc阵列模块340。

[0074]

图3中所涉及的写选择控制指令sel_wr_mode主要分为如下两种:

[0075]

(1)测试模式,将所述m位校验数据写入至第二数据阵列模块320,以及将所述n位数据中的m位数据写入至ecc阵列模块330(此时,假定n位数据为特殊拓扑数据,从而所述n位数据中的m位数据也为特殊拓扑数据);

[0076]

(2)正常模式,将所述n位数据中的m位数据写入至第二数据阵列模块320,以及将所述m位校验数据写入至ecc阵列模块330(此时,假定n位数据为非特殊拓扑数据且非校验数据的数据,从而所述n位数据中的m位数据也为所述非特殊拓扑数据且非校验数据的数据)。

[0077]

然而,应理解,图3不限制于如上两种写选择控制指令sel_wr_mode。

[0078]

图3中的写选择控制指令sel_wr_mode也可以包括诸如:正常模式,将m位校验数据写入至第二数据阵列模块320,以及将所述n位数据中的m位数据写入至ecc阵列模块330(此时,假定n位数据为特殊拓扑数据,从而所述n位数据中的m位数据也为特殊拓扑数据);测试模式,将所述n位数据中的m位数据写入至第二数据阵列模块320,以及将m位校验数据写入至ecc阵列模块330(此时,假定n位数据为非特殊拓扑数据且非校验数据的数据,从而所述n位数据中的m位数据也为所述非特殊拓扑数据且非校验数据的数据);等等。在本发明中,根据需要,可以在任意模式中将m位校验数据或者从输入端所接收的n位数据中的m位数据选择性地写入至第二数据阵列模块320或者ecc阵列模块340。

[0079]

对比图1,可以看到本发明的图3中将数据阵列模块分成第一数据阵列模块310和第二数据阵列模块320,其中第二数据阵列模块320与ecc阵列模块330的容量相同。另外,引入了写选择模块350,写选择模块350用于选择性地将m位校验数据或者从输入端所接收的n位数据中的m位数据写入至第二数据阵列模块320或者ecc阵列模块340。在图3中,存储器通

过写选择模块350可以直接地访问到第二数据阵列模块320和ecc阵列模块330。这样,如果需要,可以直接对ecc阵列模块330第二数据阵列模块320和ecc阵列模块330进行写操作,在这两个模块中实现特殊拓扑数据。例如,在背景技术部分所提及的测试模式中,如果需要在ecc阵列中写入特殊拓扑数据,则可以直接通过写选择模块350将特殊拓扑数据写入ecc阵列模块330中。

[0080]

图4和图5示出了在图3的写入过程之后的读出过程。此时,ecc阵列模块中可能存储的是m位校验数据,也可能存储的是从输入端所接收的n位数据中的m位数据。

[0081]

图4是根据本发明的一个实施方案的读出过程的示意图。

[0082]

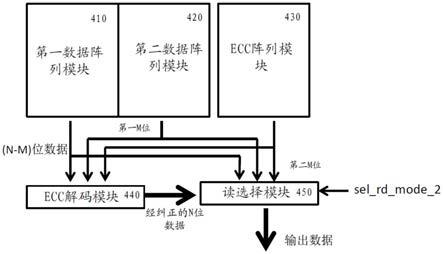

图4中也示意性示出了读出过程中所涉及的存储器的构成,所述存储器包括第一数据阵列模块410、第二数据阵列模块420、纠错码ecc阵列模块430、ecc解码模块440和读选择模块450,其中第二数据阵列模块420与ecc阵列模块430的容量相同。

[0083]

从图4中可以看到,ecc解码模块440与第一数据阵列模块410、第二数据阵列模块420、ecc阵列模块430连接,且ecc解码模块440从第一数据阵列模块410接收n-m位数据、从第二数据阵列模块420接收第一m位数据以及从ecc阵列模块430接收第二m位数据,ecc解码模块440对所述n-m位数据、所述第一m位数据、所述第二m位数据进行解码,得到经解码的数据,其中n、m均为正整数。

[0084]

读选择模块450与第一数据阵列模块410、第二数据阵列模块420、ecc阵列模块430、ecc解码模块440连接,且读选择模块450从第一数据阵列模块410接收所述n-m位数据、从第二数据阵列模块420接收第一m位数据、从ecc阵列模块430接收所述第二m位数据以及从所述ecc解码模块440接收所述经解码的数据,且根据读选择控制指令sel_rd_mode而选择性地输出。在图4中,读选择模块450从ecc解码模块440所接收的经处理的数据为经纠正的n位数据。

[0085]

图4中所涉及的读选择控制指令sel_rd_mode主要分为如下几种:

[0086]

(1)测试模式,读出n-m位数据以及第一m位数据(假定测试模式时,m位校验数据写入至第二数据阵列模块,m位特殊拓扑数据写入至ecc阵列模块,则第一m位数据为m位校验数据,第二m位数据为m位特殊拓扑数据);

[0087]

(2)测试模式,读出n-m位数据位数据、第一m位数据以及第二m位数据(也延续上述(1)中的假定);

[0088]

(3)正常模式,读出经纠正的n位数据(假定正常模式时,n位数据中的m位数据写入至第二数据阵列模块,m位校验数据写入至ecc阵列模块,则第一m位数据为n位数据中的m位数据,第二m位数据为m位校验数据);

[0089]

(4)正常模式,读出经纠正的n位数据以及第二m位数据(也延续上述(4)中的假定)。

[0090]

然而,应理解,图4不限制于如上几种读选择控制指令sel_rd_mode。

[0091]

图4中的读选择控制指令sel_rd_mode也可以包括诸如:

[0092]

正常模式,读出n-m位数据以及第一m位数据(假定正常模式时,m位校验数据写入至第二数据阵列模块,m位特殊拓扑数据写入至ecc阵列模块,则第一m位数据为m位校验数据,第二m位数据为m位特殊拓扑数据);或者

[0093]

正常模式,读出n-m位数据位数据、第一m位数据以及第二m位数据(也延续上述正

常模式的假定);或者

[0094]

测试模式,读出经纠正的n位数据(假定测试模式时,n位数据中的m位数据写入至第二数据阵列模块,m位校验数据写入至ecc阵列模块,则第一m位数据为n位数据中的m位数据,第二m位数据为m位校验数据);或者

[0095]

测试模式,读出经纠正的n位数据以及第二m位数据(也延续上述测试模式的假定);等等。

[0096]

在本发明中,根据需要,可以在任意模式中读出n-m位数据、第一m位数据、第二m位数据、经纠正的n位数据中的一个或多个。

[0097]

对比图2,可以看到本发明的图4中将数据阵列模块分成第一数据阵列模块410和第二数据阵列模块420,其中第二数据阵列模块420与ecc阵列模块430的容量相同。另外,引入了读选择模块450,读选择模块450用于选择性地读出n-m位数据、第一m位数据、第二m位数据、经纠正的n位数据中的一个或多个。在图4中,存储器通过读选择模块450可以直接地访问到第二数据阵列模块420和ecc阵列模块430。这样,如果需要,可以直接对ecc阵列模块430第二数据阵列模块420和ecc阵列模块430进行读操作,在这两个模块中实现特殊拓扑数据。例如,在背景技术部分所提及的测试模式中,如果需要在ecc阵列中测试特殊拓扑数据,则可以直接通过读选择模块450将特殊拓扑数据从ecc阵列模块430读出。

[0098]

图5是根据本发明的另一实施方案的读出过程的示意图。

[0099]

与图4中类似,图5中也示意性示出了读出过程中所涉及的存储器的构成,所述存储器包括第一数据阵列模块510、第二数据阵列模块520、纠错码ecc阵列模块530、ecc解码模块540和读选择模块550,其中第二数据阵列模块520与ecc阵列模块530的容量相同。

[0100]

从图5中可以看到,ecc解码模块540与第一数据阵列模块510、第二数据阵列模块520、ecc阵列模块530连接,且ecc解码模块540从第一数据阵列模块510接收n-m位数据、从第二数据阵列模块520接收第一m位数据以及从ecc阵列模块530接收第二m位数据,ecc解码模块540对所述n-m位数据、所述第一m位数据、所述第二m位数据进行解码,得到经解码的数据,其中n、m均为正整数。

[0101]

读选择模块550与第一数据阵列模块510、第二数据阵列模块520、ecc阵列模块530、ecc解码模块540连接,且读选择模块550从第一数据阵列模块510接收所述n-m位数据、从第二数据阵列模块520接收第一m位数据、从ecc阵列模块530接收所述第二m位数据以及从所述ecc解码模块540接收所述经解码的数据,且根据读选择控制指令sel_rd_mode而选择性地输出。在图5中,读选择模块550从ecc解码模块540所接收的经处理的数据为经纠正的n位数据以及经纠正的第二m位数据。

[0102]

图5中的上述布置的考虑因素为:如果ecc阵列模块所存储的m位校验数据也出错,也可以根据ecc算法进行检测纠正,一般经纠正的m位校验数据是不需要输出的。然而,在一些情况下,如果测试需要,也可以将经纠正的m位校验数据输出,以供分析或者其他需求。

[0103]

图5中所涉及的读选择控制指令sel_rd_mode主要分为如下几种:

[0104]

(1)测试模式,读出n-m位数据以及第一m位数据(假定测试模式时,m位校验数据写入至第二数据阵列模块,m位特殊拓扑数据写入至ecc阵列模块,则第一m位数据为m位校验数据,第二m位数据为m位特殊拓扑数据);

[0105]

(2)测试模式,读出n-m位数据位数据、第一m位数据以及第二m位数据(也延续上述

(1)中的假定);

[0106]

(3)测试模式,读出经纠正的n位数据以及经纠正的第二m位数据(假定测试模式时,n位数据中的m位数据写入至第二数据阵列模块,m位校验数据写入至ecc阵列模块,则第一m位数据为n位数据中的m位数据,第二m位数据为m位校验数据;则ecc解码模块540针对n位数据解码,得到经纠正的n位数据,且针对m位校验数据解码,得到经纠正的第二m位数据);

[0107]

(4)正常模式,读出经纠正的n位数据(假定正常模式时,n位数据中的m位数据写入至第二数据阵列模块,m位校验数据写入至ecc阵列模块,则第一m位数据为n位数据中的m位数据,第二m位数据为m位校验数据);

[0108]

(5)正常模式,读出经纠正的n位数据以及第二m位数据(也延上述(4)中的假定)。

[0109]

然而,应理解,图5不限制于如上几种读选择控制指令sel_rd_mode。

[0110]

图5中的读选择控制指令sel_rd_mode也可以包括诸如:

[0111]

正常模式,读出n-m位数据以及第一m位数据(假定正常模式时,m位校验数据写入至第二数据阵列模块,m位特殊拓扑数据写入至ecc阵列模块,则第一m位数据为m位校验数据,第二m位数据为m位特殊拓扑数据);或者

[0112]

正常模式,读出n-m位数据位数据、第一m位数据以及第二m位数据(延续上述正常模式的假定);或者

[0113]

正常模式,读出经纠正的n位数据以及经纠正的第二m位数据(假定正常模式时,n位数据中的m位数据写入至第二数据阵列模块,m位校验数据写入至ecc阵列模块,则第一m位数据为n位数据中的m位数据,第二m位数据为m位校验数据;则ecc解码模块540针对n位数据解码,得到经纠正的n位数据,且针对m位校验数据解码,得到经纠正的第二m位数据);或者

[0114]

测试模式,读出经纠正的n位数据(假定测试模式时,n位数据中的m位数据写入至第二数据阵列模块,m位校验数据写入至ecc阵列模块,则第一m位数据为n位数据中的m位数据,第二m位数据为m位校验数据);或者

[0115]

测试模式,读出经纠正的n位数据以及第二m位数据(延续上述测试模式的假定);等等。

[0116]

在本发明中,根据需要,可以在任意模式中读出n-m位数据、第一m位数据、第二m位数据、经纠正的n位数据、经纠正的第二m位数据(当第二m位数据为m位校验数据时)中的一个或多个。

[0117]

类似于图4,本发明的图5中将数据阵列模块分成第一数据阵列模块510和第二数据阵列模块520,其中第二数据阵列模块520与ecc阵列模块530的容量相同。另外,引入了读选择模块550,读选择模块550用于选择性地读出n-m位数据、第一m位数据、第二m位数据、经纠正的n位数据、经纠正的第二m位数据(当第二m位数据为m位校验数据时)中的一个或多个。在图5中,存储器通过读选择模块550可以直接地访问到第二数据阵列模块520和ecc阵列模块530。这样,如果需要,可以直接对ecc阵列模块530第二数据阵列模块520和ecc阵列模块530进行读操作,在这两个模块中实现特殊拓扑数据。

[0118]

图6是根据本发明的一个实施方案的读出方法的流程图。图6中的读出方法如上针对图3所描述的存储器。所述读出方法包括:

[0119]

步骤s610:ecc解码模块从第一数据阵列模块接收n-m位数据、从第二数据阵列模块接收第一m位数据以及从ecc阵列模块接收第二m位数据,且所述ecc解码模块对所述n-m位数据、所述第一m位数据、所述第二m位数据进行解码,得到经解码的数据;

[0120]

步骤s620:读选择模块从第一数据阵列模块接收所述n-m位数据、从第二数据阵列接收所述第一m位数据、从ecc阵列模块接收所述第二m位数据以及从ecc解码模块接收所述经解码的数据,且读选择模块根据一个选择控制指令而选择性地输出。

[0121]

图7是根据本发明的一个实施方案的写入方法的流程图。图7中的写入方法如上针对图4至图5中的任一个所描述的存储器。所述写入方法包括:

[0122]

步骤s710:ecc编码模块从输入端接收n位数据,对所述n位数据进行编码,得到m位校验数据;

[0123]

步骤s720:写选择模块从ecc编码模块接收所述m位校验数据以及从所述输入端接收n位数据中的m位数据,且根据一个写选择控制指令而选择性地将所述m位校验数据或者从所述输入端所接收的所述n位数据中的m位数据写入至所述ecc阵列模块或者所述第二数据阵列模块。

[0124]

本发明提出的存储器及其存储方法可以很容易地直接访问到所述ecc阵列模块或者所述第二数据阵列模块,能够在写操作和读操作的过程中非常灵活地切换多种模式。

[0125]

本发明中所提出的存储器是存储芯片(例如,rom、sdram、ram、dram、sram、flash、eprom、eeprom、cd-rom或其他光盘存储装置、磁盘存储装置或其他磁性存储装置),以用于存储数据和/或计算机代码。存储器可以是或包括非瞬态易失性存储器或非易失性存储器等。

[0126]

应注意,上文所提及的实施方案例示而非限制本发明,且在不脱离所附权利要求的范围的前提下,本领域技术人员将能够设计许多替代实施方案。应理解,本发明的范围由权利要求限定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。