技术特征:

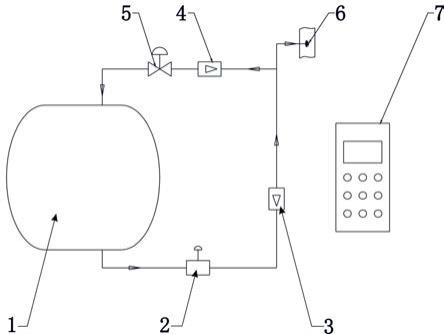

1.两维声光衍射器件的控制电路,其特征在于:包含mpu(2)、fpga(6)以及存储器(5),通信接口(1)与mpu(2)的通信端相连,mpu(2)的端口总线数据连接存储器(5)的总线数据端口,且连接到fpga(6)的输入端,进而连接至fpga(6)的数据读取发送模块(601)的总线数据端口;mpu(2)的输出端连接fpga(6)输入引脚,进而连接至fpga(6)的数据读取发送模块(601)启动读取信号端,mpu(2)的输入引脚连接到fpga(6)的输出引脚,进而连接至数据读取发送模块(601)的数据装载完成信号输出端,mpu(2)的总线数据线连接到fpga(6)的输入引脚,进而连接至fpga(6)的出光控制模块(602)的数据输入端口;mpu(2)的输入引脚连接触发接口(3);触发接口(3)分别连接mpu(2)输入端和fpga(6)的输入引脚,进而连接至出光控制模块(602)的输入端;晶振(4)连接fpga(6)的全局时钟端;数据读取发送模块(601)的输出端分别连接mpu(2)的输入端和出光控制模块(602)的输入端;数据发送模块(601)的输出端连接射频驱动器(7)的输入端;出光控制模块(602)的输出端连接激光器(8);射频驱动器(7)的输出端分别连接声光衍射器件一(9)和声光衍射器件二(10)。2.根据权利要求1所述的两维声光衍射器件的控制电路,其特征在于:mpu(2)为型号stm32f407的微处理单元,最高工作频率168m。3.根据权利要求1所述的两维声光衍射器件的控制电路,其特征在于:存储器(5)为型号is65lv256al的8位32k静态存储器。4.根据权利要求1所述的两维声光衍射器件的控制电路,其特征在于:fpga(6)为xilinx公司型号为xc6slx4的fpga。5.根据权利要求1所述的两维声光衍射器件的控制电路,其特征在于:晶振(4)为100mhz的晶振。6.利用权利要求1所述的电路实现两维声光衍射器件的控制方法,其特征在于:上位机通过通信接口(1)发送指令及数据到mpu(2),两维声光衍射器件即aod,通过光束在平面上扫出相应的图形,图形由若干个打点形成,加工前将图形的坐标转成aod工作频率调节字即ftw,工作频率对应衍射角度;aod可控制到每个点的能量大小,aod的幅度控制字即acw;通信接口(1)通过发送加工速度参数来改变扫描速度,加工速度即mpu(5)启动对fpga(6)的数据读取发送模块(601)的读取频率,读取频率越高扫描速度越快;通信接口(1)发送延时参数和控制模式参数给mpu(2)同时传输至fpga(6)的出光控制模块(602),分别设定激光出光的延时时间以及选择gate控制还是trigger控制;开始加工时,加工启动信号通过触发接口(3)输入至mpu(2)的中断输入口和出光控制模块(602)的输入端,mpu(2)接收到加工信号后输出read信号给数据读取发送模块(601),数据读取发送模块(601)从存储器(5)中读取加工图形各个点对应的aod的ftw和acw,并发送给射频驱动器(7),由于是两维正交的声光衍射器件,需两组工作频率和功率值对应于平面上的两维坐标;射频驱动器(7)接收到数据后分别驱动声光衍射器件一(9)和声光衍射器件二(10)进行扫描和功率变化;数据读取发送模块(601)利用寄存器端口将声光衍射器件一(9)和声光衍射器件二(10)的工作数据,在锁存信号latch1/latch2和数据选择信号mux1/mux2的配合下传输给射频驱动器(7),当mux为(1,1)时传输ftw,当mux为(0,1)时传输acw,当latch信号为高时,锁存数据;出光控制模块(602)切换gate控制和trigger控制,同时根据延时参数进行延时出光。

7.根据权利要求6所述的两维声光衍射器件的控制方法,其特征在于:所述gate控制是根据外部加工启动信号,延时设定的时间后再输出高电平到激光器(8)进行出光。8.根据权利要求7所述的两维声光衍射器件的控制方法,其特征在于:延时是通过fpga的计数器对时钟的计数实现。9.根据权利要求6所述的两维声光衍射器件的控制方法,其特征在于:所述trigger控制是根据数据读取发送模块(601)输出的数据装载完成信号对激光器(8)进行脉冲控制。10.根据权利要求9所述的两维声光衍射器件的控制方法,其特征在于:装载完成即对扫描图形个点的ftw和acw数据从存储器(5)读取并装载到射频驱动器(7),每完成一个点信息装载,即输出一个光脉冲。

技术总结

本发明涉及两维声光衍射器件的控制电路及控制方法,通信接口与MPU的通信端相连,MPU的端口总线数据连接存储器的总线数据端口,连接FPGA的输入端;MPU的输出端连接FPGA输入引脚,MPU的输入引脚连接FPGA的输出引脚,MPU的总线数据线连接FPGA的输入引脚;MPU的输入引脚连接触发接口;触发接口连接MPU输入端和FPGA的输入引脚;晶振连接FPGA的全局时钟端;数据读取发送模块的输出端连接MPU的输入端和FPGA的出光控制模块的输入端;FPGA的数据发送模块的输出端连接射频驱动器的输入端;出光控制模块的输出端连接激光器;射频驱动器的输出端连接两声光衍射器件,对其衍射角度和功率改变。变。变。

技术研发人员:赵裕兴 许卫星

受保护的技术使用者:苏州德龙激光股份有限公司

技术研发日:2021.06.23

技术公布日:2021/10/23

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。