技术特征:

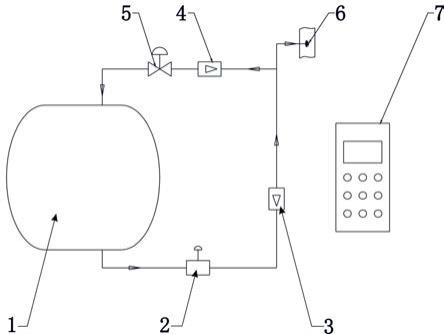

1.一种宽范围信号发生器装置,其特征在于:接口电路(1)、dds低频模块(2)、pll高频模块(3)、时钟模块(5)、液晶显示模块(8)、fpga(4)和微处理器(6);所述接口电路(1)与dds低频模块(2)连接,且所述接口电路(1)模块与所述pll高频模块(3)连接,所述dds低频模块(2)和所述pll高频模块(3)均分频连到fpga(4)的i/o端口,所述时钟模块(5)连接到fpga(4)的时钟信号输入端,fpga(4)连接有用于处理信息的微处理器(6),微处理器(6)还与液晶显示模块(8)相连。2.根据权利要求1所述的一种宽范围信号发生器装置,其特征在于:所述fpga(4)与所述微处理器(6)的连接采用spi总线;所述液晶显示模块(8)与所述微处理器(6)的连接采用spi总线。3.根据权利要求1所述的一种宽范围信号发生器装置,其特征在于:所述微处理器(6)采用arm处理器。4.根据权利要求3所述的一种宽范围信号发生器装置,其特征在于:所述arm处理器选取的型号为stm32f407vet6。5.根据权利要求1所述的一种宽范围信号发生器装置,其特征在于:所述时钟模块(5)采用3627封装的高精度恒温晶振。6.根据权利要求2所述的一种宽范围信号发生器装置,其特征在于:所述液晶显示模块(8)包括7寸液晶显示屏和按键。7.根据权利要求1所述的一种宽范围信号发生器装置,其特征在于:所述fpga(4)的型号选取为ep4ce6e22c8。

技术总结

本申请公开了一种宽范围信号发生器装置,涉及时间频率测量领域,目的在于能够产生满足时间频率测量设备,比如通用计数器检定的频率信号,该装置包括接口电路、DDS低频模块、PLL高频模块、时钟模块、液晶显示模块、FPGA和微处理器,时钟模块连接到FPGA的I/O端口,DDS低频模块、PLL高频模块分别于FPGA相连,FPGA连与微处理器相连,微处理器还与液晶显示模块相连,通过接口电路的优化,可输出极低幅值的频率信号,使用DDS和PLL方法,输出频率低可到10uHz,高可达30GHz,通过网络或者串口能够程控输出信号的频率和幅度,提高测量通用计数器的效率,降低了测试成本。降低了测试成本。降低了测试成本。

技术研发人员:马战国 安媛 刘欢

受保护的技术使用者:西安同步电子科技有限公司

技术研发日:2021.03.02

技术公布日:2021/10/8

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。