基于fpga实现的多通道信号预处理系统及方法

技术领域

1.本发明涉及数字信号处理领域,具体涉及一种基于fpga实现的多通道信号预处理系统及方法,适用于接收多通道雷达回波且实时性高、数据量大的设计。

背景技术:

2.随着现代电子技术的应用和发展,越来越多的电子应用由模拟系统向数字系统转变,模数转换(a/d转换)的多路扩展、高精度、低成本、实时性显著等特点在模数转换中越来越重要,在实际工程应用中,要求数据采集系统具备实时处理、高速率、多通道和系统稳定等特点。多通道同步高速数据采集系统在很多场合都有着广泛的应用,是数字信号处理中必不可少的前期环节,而通道间的同步性往往是数据采集系统中的关键部分。在硬件方面,因为印刷电路板设计(pcb设计)、加工、处理过程和测试环境等的差异,无法使多个通道之间的信号完全同步,而硬件设计过程一般是不可逆的,加工完成之后不能再进行调整。

3.目前的雷达接收单元中,ad的采样速率最高可达几个gsps,多通道、高速率的数据的并行处理,对后边的信号处理器提出了很高要求。fpga运行速度在几百兆左右,无法实时处理如此高速的数据流,且存储数据后再进行分析处理无法满足实时处理的要求。

技术实现要素:

4.针对现有技术中存在的问题,本发明的目的在于提供一种基于fpga实现的多通道信号预处理系统及方法,该系统结构简单,其预处理方法能够解决现有数据采集系统存在的多通道采样数据不同步的问题,实现大规模多通道信号的数据采集,并通过数字下变频模块降低数据率。

5.本发明的技术思路为:首先ad配置模块产生控制信号完成对8片ad芯片的配置,配置后ad芯片开始工作,将差分时钟和差分数据信号分别发送给fpga中的ad时钟模块和ad数据模块。ad时钟模块将差分时钟转换单端时钟并送给ad数据模块,在ad数据模块中完成差分数据信号到单通道数据信号的转换,输出32通道数据给数字下变频模块做ddc处理,然后将处理结果送给光纤发送模块,通过光纤发送给下一级信号处理单元。本设计中雷达有4种工作模式,不同模式下数字下变频处理的参数会有差异。上位机通过串口下发工作模式信息,经串口接收与发送模块解析后送给参数选择模块,由该模块选择对应的参数给数字下变频模块。同时串口接收与发送模块会将一些状态信息通过串口上报给上位机。

6.为了达到上述目的,本发明采用以下技术方案予以实现。

7.(一)基于fpga实现的多通道信号预处理系统,包括:ad芯片、fpga和上位机;其中,所述fpga包含ad配置模块、ad时钟模块、ad数据模块、数字下变频模块、串口接收与发送模块、参数选择模块和光纤发送模块;

8.所述ad配置模块的信号输出端与所述ad芯片的控制端电连接;

9.所述ad芯片的时钟信号输出端与所述ad时钟模块的信号输入端电连接;所述ad芯片的数据信号输出端与所述ad数据模块的第一信号输入端电连接;所述ad时钟模块的信号

输出端与所述ad数据模块的第二信号输入端电连接;

10.所述ad数据模块的信号输出端与所述数字下变频模块的第一信号输入端电连接;

11.所述上位机与所述串口接收与发送模块双向电连接,所述串口接收与发送模块的信号输出端与所述参数选择模块的信号输入端电连接,所述参数选择模块的信号输出端与所述数字下变频模块的第二信号输入端电连接;

12.所述数字下变频模块的信号输出端与所述光纤发送模块的信号输入端电连接。

13.本发明技术方案(一)的特点和进一步的改进为:

14.(1)所述ad芯片为ads4449模数转换器。

15.(2)所述ad配置模块用于产生控制信号,实现对所述ad芯片中寄存器的配置;

16.所述ad芯片用于将外部输入的模拟信号转换为差分数据信号,并将所述差分数据信号发送给所述ad数据模块;所述ad芯片还用于将差分时钟信号发送给所述ad时钟模块;

17.所述ad时钟模块用于将所述差分时钟信号转换为单端时钟信号,并将所述单端时钟信号发送给所述ad数据模块;

18.所述ad数据模块用于将所述差分数据信号转换为单通道数据信号,并将所述单通道数据信号发送给所述数字下变频模块;

19.所述上位机用于通过所述串口接收与发送模块发送工作模式信息给所述参数选择模块,所述参数选择模块根据接收的所述工作模式信息确定所述数字下变频模块的工作参数信息;

20.所述数字下变频模块用于根据所述参数选择模块确定的工作参数信息来对每个所述单通道数据信号进行数字下变频处理;

21.所述光纤发送模块用于将所述数字下变频模块的处理结果发送给下一级信号处理单元。

22.(3)所述ad时钟模块包含依次连接的ibufgds、idelaye2和bufg;所述ibufgds用于将差分时钟信号转换为单端时钟信号;所述idelaye2用于调整时钟延时来保证单端时钟信号与单通道数据相位对齐;所述bufg用于将局部时钟转换为全局时钟。

23.(4)所述ad数据模块包含依次连接的ibufds、iddr和fifo,其中,所述ad时钟模块的信号输出端与所述iddr的信号输入端电连接;所述ibufds用于将所述差分数据信号转换为单端数据信号,并将单端数据信号发送给所述iddr;

24.所述iddr用于接收所述ibufds发送的单端数据信号和所述时钟模块发送的单端时钟信号,并用于在时钟的上升沿读取数据给通道1,在时钟的下降沿读取数据给通道2,从而将单端数据信号转为两个单通道数据信号;

25.所述fifo用于缓存所述单通道数据信号。

26.(二)基于fpga实现的多通道信号预处理方法,包括以下步骤:

27.步骤1,由fpga中的ad配置模块产生控制信号,实现对所述ad芯片中寄存器的配置;配置完成后,ad芯片将外部输入的模拟信号转换为差分数据信号,并将所述差分数据信号发送给ad数据模块;同时,ad芯片将差分时钟信号发送给ad时钟模块;

28.步骤2,ad时钟模块将差分时钟信号转换为单端时钟信号,并将所述单端时钟信号发送给ad数据模块;

29.步骤3,ad数据模块将所述差分数据信号转换为单通道数据信号,并将所述单通道

数据信号发送给数据下变频模块;

30.步骤4,上位机通过串口接收与发送模块发送工作模式信息给参数选择模块,所述参数选择模块根据接收的工作模式信息确定所述数字下变频模块的工作参数信息;

31.步骤5,所述数字下变频模块根据所述参数选择模块确定的工作参数信息对每个单通道数据信号进行数字下变频处理,并将数字下变频处理结果发送给光纤发送模块;

32.步骤6,所述光纤发送模块通过光纤将所述数字下变频处理结果发送给下一级信号处理单元。

33.本发明技术方案(二)的特点和进一步的改进为:

34.(1)步骤2中,所述ad时钟模块包含依次连接的ibufgds、idelaye2和bufg;所述ibufgds将差分时钟信号转换为单端时钟信号;所述idelaye2通过调整时钟延时来保证单端时钟信号与单通道数据相位对齐;所述bufg用于将局部时钟转换为全局时钟。

35.(2)步骤3中,所述ad数据模块包含依次连接的ibufds、iddr和fifo,其中,所述ad时钟模块的信号输出端与所述iddr的信号输入端电连接;所述ibufds将所述差分数据信号转换为单端数据信号,并将单端数据信号发送给所述iddr;

36.所述iddr接收所述ibufds发送的单端数据信号和所述时钟模块发送的单端时钟信号,并在时钟的上升沿读取数据给通道1,在时钟的下降沿读取数据给通道2,将单端数据信号转为两个单通道数据信号。

37.(3)步骤5中,所述数字下变频处理具体包含以下子步骤:

38.子步骤5.1,将每个单通道数据信号分别与nco产生的正弦余弦序列相乘,得到正交混频结果;

39.子步骤5.2,对所述正交混频的结果同时做抽取和低通滤波,得到低通滤波结果;

40.子步骤5.3,对所述低通滤波结果再次进行抽取,得到数字下变频处理结果。

41.(4)子步骤5.1中,所述nco产生的正弦余弦序列如下:

42.正弦序列

43.余弦序列

44.其中,f

s

为采样频率,f

c

为信号的中心频率。

45.与现有技术相比,本发明的有益效果为:

46.(1)本发明采用xilinx公司的virtex7系列的fpga作为核心处理器件,可以实现数据处理、数据缓存、高速数据传输和时钟校准等功能,适用于高采样率、高数据率、实时性要求高的场合。

47.(2)本发明采用ti公司的ads4449模数转换器作为数据采集器件,该芯片是一款高线性、四通道、14位、250msps的模数转换器(adc)。此器件针对低功耗和高无杂散动态范围(sfdr)而设计,具有低噪声性能以及在宽输入频率范围内出色的sfdr。

48.(3)本发明提供了一种基于fpga的多通道数据同步采集以及信号预处理的方法,以fpga作为主要处理器,控制多通道数据的同步采集和数据的处理及传输,从而满足系统多通道、同步和实时性高的要求。

附图说明

49.下面结合附图和具体实施例对本发明做进一步详细说明。

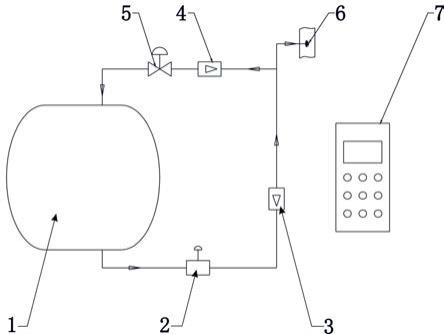

50.图1为本发明的基于fpga实现的多通道信号预处理系统结构图;

51.图2为ad配置模块的框图;

52.图3为ad配置模块中四个控制信号的时序图;

53.图4为ad时钟模块的处理流程图:

54.图5为ad数据模块的处理流程图:

55.图6为数字下变频的处理流程图;

56.图7为uart的数据格式。

具体实施方式

57.下面将结合实施例对本发明的实施方案进行详细描述,但是本领域的技术人员将会理解,下列实施例仅用于说明本发明,而不应视为限制本发明的范围。

58.(一)参考图1,基于fpga(现场可编程门阵列)实现的多通道信号预处理系统,包括:ad芯片、fpga和上位机;其中,所述fpga包含ad配置模块、ad时钟模块、ad数据模块、数字下变频模块、串口接收与发送模块、参数选择模块和光纤发送模块;

59.所述ad配置模块的信号输出端与所述ad芯片的控制端电连接;

60.所述ad芯片的时钟信号输出端与所述ad时钟模块的信号输入端电连接;所述ad芯片的数据信号输出端与所述ad数据模块的第一信号输入端电连接;所述ad时钟模块的信号输出端与所述ad数据模块的第二信号输入端电连接;

61.所述ad数据模块的信号输出端与所述数字下变频模块的第一信号输入端电连接;

62.所述上位机与所述串口接收与发送模块双向电连接,所述串口接收与发送模块的信号输出端与所述参数选择模块的信号输入端电连接,所述参数选择模块的信号输出端与所述数字下变频模块的第二信号输入端电连接;

63.所述数字下变频模块的信号输出端与所述光纤发送模块的信号输入端电连接。

64.具体的,参考图2,fpga中的ad配置模块用于产生sen、sclk、sdata和sdout四个控制信号,实现对8片ad芯片(ads4449芯片)中寄存器的配置,使其正常工作。这四个控制信号的时序图如图3所示,当sen为低时,sdata的16bit数据被锁存在每个sclk的下降沿,sdata的前8bit代表寄存器地址,后8bit代表寄存器数据;按照图3方式产生控制信号,即可实现对ad芯片的配置,使其按照设计要求工作。

65.ad芯片配置完成后,ad芯片将外部输入的模拟信号转换为差分数据信号,并将差分数据信号发送给ad数据模块;同时,ad芯片将差分时钟信号发送给所述ad时钟模块。差分信号就是两个反相的信号,可以起到校正的作用。

66.ad时钟模块用于将差分时钟信号转换为单端时钟信号,并将单端时钟信号发送给ad数据模块。具体的,因硬件设计的工艺问题,每个通道的数据信号并不一定是完全同步的,所以需要对单端时钟信号进行延时,以此保证32个通道数据信号对齐同步。ad时钟模块包含依次连接的ibufgds、idelaye2和bufg;可以通过ibufgds将差分时钟信号转为单端时钟信号,并将单端时钟信号通过全局时钟缓冲bufg,使时钟的延迟和抖动最小。但是在实际情况下,由于板卡的pcb设计和加工等的差异,板卡上8片ad到达fpga的路径长短不同,且

fpga内布局布线时路径也会有所不同,所以可能导致时钟与数据信号的相位没有对齐,采样时会有偏差存在,出现毛刺,空采噪声信号时效果也不理想。针对此情况,利用idelaye2调整时钟延时来保证单端时钟与单通道数据相位对齐。idelaye2的时钟延迟有0~31阶,每一阶的延迟精度约为78ps,可以在0~31区间调节阶数达到相位对齐效果。在测试时,可以通过fpga中的vio(虚拟输入输出)调节阶数,得到数据稳定的阶数区间,在该区间内时钟与数据信号的相位是对齐的,各通道信号同步。最后再取该区间的中间值固定。所以本设计中对时钟的处理如图4,将差分时钟信号通过ibufgds、idelaye2和bufg,转为单端时钟信号。

67.参考图5,ad数据模块用于将两两通道的差分数据信号转换为单通道数据信号,并将单通道数据信号发送给数字下变频模块。具体的,ad数据模块包含依次连接的ibufds、iddr和fifo,ad时钟模块的信号输出端与iddr的信号输入端电连接。先将ad芯片输出的14bit差分数据信号按bit通过ibufds转为单端数据信号;再将单端数据信号通过iddr,其中iddr的输入时钟为ad时钟模块输出的单端时钟信号,然后在该时钟的上升沿读取数据给通道1,在时钟的下降沿读取数据给通道2,由此将单端数据信号转为两个通道各自的数据信号;最后将各通道数据通过fifo(先入先出)缓存,并用200mhz的工作时钟将每个通道的数据信号读出。另外,ad芯片寄存器配置期间fifo一直是复位的,配置完2ms后fifo才开始工作,保证了数据传输的实时性和正确性。采集32个通道的数据进行分析,空采噪声时,噪声频域图中无其他频谱,没有其他干扰信号,噪声效果比较理想。给32个通道输入单频信号分析,无杂散动态范围在80dbc左右,信噪比在67dbfs~71dbfs之间,所有通道的隔离度都在65db以上,ad芯片各性能指标均达到了设计要求。

68.上位机用于通过串口接收与发送模块发送工作模式信息给参数选择模块,参数选择模块根据接收的工作模式信息确定数字下变频模块的工作参数信息。具体的,串口接收与发送模块,是通过uart(universal asynchronous receiver/transmitter)通信实现数据的串行接收与发送。参考图7,为uart的数据格式,当线路上没有数据传送时处于空闲状态,为高电平。起始信号一般由一个逻辑0的数据位表示,紧接着的是传输数据的主体内容,即8bit有效数据,之后进入停止位,完成一包数据的传输。本次串口的波特率为1mbps,时钟20mhz,采样1bit数据需要20个时钟周期,所以当周期计数超过180时进入空闲状态。当检测到有一段时间没接收到数据时,串口报错。串口接收的信息为上位机发送的工作模式信息,发送的信息有各通道采样状态、串口收发状态和板卡温度信息。

69.参数选择模块,就是根据串口接收与发送模块接收到的工作模式信息选择对应的混频参数、滤波器系数组别以及二次抽取的倍数送给数字下变频模块。本设计总共有4种工作模式。对于混频来说,4种工作模式下信号的中心频率f

c

分别为125m、130m、150m、160m,相应的dds ip核的频率控制字k也不同,本模块已经将4种模式下的k值都罗列出来,再根据工作模式信息选择对应的k值。对于多相滤波来说,滤波器系数已经按组存放好了,只需要选择对应的组别即可,4种工作模式下的组别分别为1、2、3、4。对于二次抽取,也是根据工作模式信息选择对应的抽取倍数,4种工作模式下的二次抽取倍数分别为4、2、2、2。最后将这三种参数(k值、组别、二次抽取倍数)发送给数字下变频模块。

70.数字下变频模块(ddc)用于根据参数选择模块确定的工作参数信息来对每个单通道数据信号进行数字下变频处理。具体的,数字下变频模块是将32通道数据进行混频、多相滤波和二次抽取处理,滤除不感兴趣的信号,并降低采样率。参考图6,是对一片ad的4个通

道进行ddc的流程图,将该模块复用8次即可完成对32通道的ddc处理。

71.混频就是将ad数据模块输出的32通道数据分别与nco产生的正弦余弦序列相乘得到正交混频结果。nco产生的正弦余弦序列如下:

72.正弦序列

73.余弦序列

74.其中采样频率f

s

=200mhz。本设计中有多个工作模式,每个模式下信号的中心频率f

c

不同,分别有125m、130m、150m、160m、165m几种。当f

c

=150mhz,f

s

=200mhz时,本振序列的值比较特殊,正弦序列s(n)={0,

‑

1,0,1,0,

‑1…

},余弦序列c(n)={1,0,

‑

1,0,1,0

…

},所以可以将正余弦序列存在rom(只读存储器)里调用,而不需要用复杂的算法去产生。而当f

c

与f

s

的比值不是上述这种特殊值时,就需要用dds(直接数字频率合成器)ip核产生频率为f

c

的正余弦序列进行混频。dds输出频率为f

clk

为系统工作频率、n为相位累加器位宽(这里取48)、k为频率控制字,输入k即可得到相应的正余弦序列。

75.多相滤波是在高采样率的情况下,对正交混频的结果同时做抽取和低通滤波。这里的抽取倍数统一为5。按照不同工作模式下的滤波要求,先在matlab中设计好滤波器,导出滤波器系数文件。使用vivado软件的fir ip核,将设计好的滤波系数文件导入fir ip核中即可。因为不同工作模式要求不同的滤波效果,滤波器系数有差异,如果每种滤波器都使用fir ip核,会占用大量dsp48乘法器资源,开销太大。这里选择在一个fir ip核中动态切换滤波系数的方法,即将多组系数按顺序叠放在同一个系数文件中,每组系数要求长度相同,若不一致则在末尾补零。在fir核中设置好系数的组数,之后通过参数选择模块发送的系数组别选择即可。vivado中的fir核可以同时完成抽取和滤波,容易实现多相滤波结构,方便了滤波设计。

76.二次抽取:同样的,不同工作模式下抽取倍数不同,若在多相滤波时要求实现完全抽取,会增加fir ip核的数量,消耗乘法器资源,所以本次抽取不在fir ip核中实现。在多相滤波阶段已经做过一次抽取,本模块是对滤波结果再次进行抽取,即二次抽取。二次抽取用计数器实现,抽取倍数是由参数选择模块发送过来的。

77.光纤发送模块用于将数字下变频模块的处理结果发送给下一级信号处理单元。具体的,光纤发送模块是在fpga中通过高速串行收发器(gth ip核)发送32通道的数字下变频结果。ddc结果和gth工作在不同时钟域下,首先将要发送的ddc结果通过fifo缓冲,转换到gth的时钟域下。然后对gth ip核进行参数配置,配置参数包括线速率、参考时钟、数据位宽、编码方式、k码和对齐码。根据实际要求,数据传输以帧为单元,不同帧之间设置一定的传输间隔。每帧数据的前40个数据为模式信息,包含帧头、工作模式和数据长度等信息。总共有8路光纤,负责发送32个通道的数据,每路光纤负责发送4个通道的数据。

78.(二)基于fpga实现的多通道信号预处理方法,包括以下步骤:

79.步骤1,由fpga中的ad配置模块产生控制信号,通过spi(串行外设接口)实现对ad芯片(ads4449芯片)中寄存器的配置,配置完成后,ad芯片将外部输入的模拟信号转换为差分数据信号,并将差分数据信号发送给ad数据模块;同时,ad芯片将差分时钟信号发送给ad

时钟模块。

80.步骤2,ad时钟模块将差分时钟信号转换为单端时钟信号,并将单端时钟信号发送给ad数据模块。因硬件设计的工艺问题,每个通道的数据信号并不一定是完全同步的,所以需要对单端时钟信号进行延时,以此保证32个通道数据信号对齐同步。

81.步骤3,ad数据模块将差分数据信号转换为单通道数据信号,并将单通道数据信号发送给数据下变频模块,总共完成32个通道数据信号的转换。

82.步骤4,上位机通过串口接收与发送模块发送工作模式信息给参数选择模块,参数选择模块根据接收的工作模式信息确定数字下变频模块的工作参数信息。

83.具体的,串口接收与发送模块接收上位机通过串口发送的工作模式信息并发送给参数选择模块,同时将各通道的采样状态、串口收发状态以及温度信息通过串口上报给上位机。

84.参数选择模块:本设计中雷达有4种工作模式,不同模式对应不同的参数,这些参数会影响数字下变频模块的处理。所以需要根据串口收发模块发送的工作模式信息选择对应的参数送给数字下变频模块。

85.步骤5,数字下变频(ddc)模块根据参数选择模块确定的工作参数信息来对每个单通道数据信号进行数字下变频处理,并将数字下变频处理结果发送给光纤发送模块。

86.具体的,对32个通道的数据信号进行数字下变频。总共有32个通道,这里的ddc模块主要负责对4个通道进行处理,复用8次完成32通道的ddc。ddc主要由混频、多相滤波和二次抽取三个部分实现。

87.步骤6,光纤发送模块通过光纤将数字下变频处理结果发送给下一级信号处理单元。设计光纤发送模块,1路光纤发送1片ad即4个通道的数据,总共需要8路光纤。工作模式选用裸传的方式,由数据码和空闲码组成。

88.虽然,本说明书中已经用一般性说明及具体实施方案对本发明作了详尽的描述,但在本发明基础上,可以对之作一些修改或改进,这对本领域技术人员而言是显而易见的。因此,在不偏离本发明精神的基础上所做的这些修改或改进,均属于本发明要求保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。