本发明涉及通信技术领域,尤其涉及一种数字多波束信号处理系统及时间同步方法。

背景技术:

大型相控阵多波束系统中数字信号处理时,经常会需要多片fpga资源协同工作完成大容量的信号和数据处理,但进行数字信号处理时各个fpga板卡之间的信号及帧号时序同步等直接影响系统的性能,以前的多波束信号处理系统常是以高精度的钟作为时间参考,同时给各个板卡提供时间基准,这对10m时钟精度提出了较高的要求,而且对于各fpga帧同步也无法进行进一步的指导和借鉴意义。

技术实现要素:

本发明的目的在于提供一种数字多波束信号处理系统及时间同步方法,通过在主控fpga0上配置同步帧号,并通过主控fpga0向子fpga配置相应的同步帧号,实现了系统的时间同步方法。

本发明通过下述技术方案实现:

一种数字多波束信号处理系统时间同步方法,包括

s1:获取同源1pps信号,并将1pps信号作用于主控fpga0;

s2:主控fpga0根据1pps信号产生第一中断信号与第二中断信号;

s3:根据第一中断信号,配置主控fpga0的第一帧号,根据第二中断信号,回读主控fpga0的第二帧号,判断第一帧号与第二帧号是否一致,若一致,则将第一帧号与第二帧号作为同步帧号,进入步骤s4,否则,重复步骤s1~s3;

s4:通过主控fpga0向子fpga配置同步帧号,获得第一子同步帧号,检测第一子同步帧号与同步帧号的无线帧终端是否一致,若一致,则系统时间同步成功,否则,进入步骤s5;

s5:在主控fpga0无线帧的第二个时隙时,通过spi总广播向子fpga配置同步帧号,获得子fpga的第二子同步帧号;

s6:通过背板轮询方式回读子fpga的第二子同步帧号,并将第二子同步帧号与同步帧号进行比对,若比对一致,则系统时间同步成功,否则,重复步骤s1~s6。

传统在对多波束系统中,数字信号处理的时候,都是通过采用高精度时钟作为时间参考,给各个板卡提供一个时间基准,但是在这种方法使用的过程中,通常对高精度时钟要求特别高,且造价高,对fpga各板之间的帧同步也没有什么作用,采用本发明提供的一种数字多波束信号处理系统及时间同步方法,通过对主控fpga0板配置同步帧号,并通过主控fpga0向各个子fpga配置同步帧号,实现了在系统中,各个板卡上的fpga板间信息帧号同步,并减少了fpga板间信息帧不会出现丢帧和错误的情况。

优选地,所述步骤s3中,配置主控fpga0的第一帧号的具体方法步骤包括:

根据主控fpga0的帧信号进行初始化;

以第一中断信号状态为基准,对初始化后的帧信号和帧头进行信息分配。

优选地,所述通过背板轮询方式回读子fpga的第二子同步帧号的具体方法为:

在主控fpga0无线帧第四个时隙时,采用背板轮询方式,以时隙为颗粒度通过spi总线回读子fpga的第二子同步帧号。

优选地,所述第一中断信号包括第一帧中断信号与第一时隙中断信号。

优选地,所述第二中断信号包括第二帧中断信号与第二时隙中断信号。

本发明还公开了一种数字多波束信号处理系统,所述时间同步系统包括;

综合处理机,用于获取同源1pps信号,并将1pps信号作用于主控fpga0,且根据主控fpga0反馈的信号,向主控fpga0配置帧号;

主控fpga0,用于产生第一中断信号与第二中断信号,将第一中断信号与第二中断信号反馈到所述综合处理机内,同时接收综合处理机配置的帧号,匹配出同步帧号,并将同步帧号配置给子fpga,同时检测子fpga的子同步帧号与主控fpga0的同步帧号是否一致;

子fpga,用于接收主控fpga0配置的帧号,实现与主控fpga0帧号同步;

背板,用于通过导线将主控fpga与子fpga连接。

优选地,所述时间同步系统包括若干子fpga。

通过采用本发明提供的系统,能够通过主控fpga0同时将同步帧号配置给若干个子fpga,能够实现实时配置传输。

本发明与现有技术相比,具有如下的优点和有益效果:

采用本发明提供的一种数字多波束信号处理系统及时间同步方法,通过对主控fpga0配置同步帧号,并通过主控fpga0对子fpga的信号帧进行同步匹配,使得数字多波束信号处理系统的时间以及各个fpga板上的信号帧同步,且能够减少子fpga之间信息帧不会出现丢帧和错误的情况发生。

本发明提供的时间同步方法,选择某一主控板的fpga作为参考的方式,可以减少系统与外部的互联和交互,减少了同步过程数据的吞吐量和同步时间,提高系统同步精度。

附图说明

此处所说明的附图用来提供对本发明实施例的进一步理解,构成本申请的一部分,并不构成对本发明实施例的限定。在附图中:

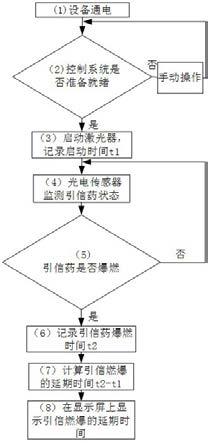

图1为时间同步方法示意图

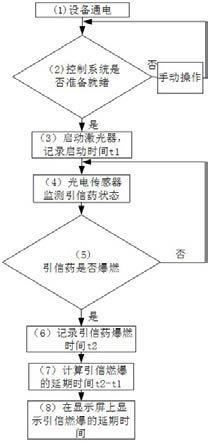

图2为系统示意图

具体实施方式

为使本发明的目的、技术方案和优点更加清楚明白,下面结合实施例和附图,对本发明作进一步的详细说明,本发明的示意性实施方式及其说明仅用于解释本发明,并不作为对本发明的限定。

实施例一

本实施例公开了一种数字多波束信号处理系统时间同步方法,如图1所示,包括

s1:获取同源1pps信号,并将1pps信号作用于主控fpga0;

采用同源1pps秒脉冲信号,做为同步脉冲信息,且采用122.88m时钟作为脉冲采集时钟。

s2:主控fpga0根据1pps信号产生第一中断信号与第二中断信号;

所述第一中断信号包括第一帧中断信号与第一时隙中断信号;所述第二中断信号包括第二帧中断信号与第二时隙中断信号。

当1pps秒脉冲信号作用于主控fpga0上的时候,主控fpga0会在1pps秒脉冲信号的作用下,产生帧中断信号与时隙中断信号,且所产生的帧中断信号与时隙中断信号用于给主控fpga0配置同步信号,当有多个1pps秒脉冲信号作用与主控fpga0上的时候,主控fpga0就会产生不同的帧中断信号与时隙中断信号,二次产生的帧中断信号与时隙中断信号,是用于对主控fpga0产生的同步帧号回读,且进行比较。

帧中断信号为微处理机与外围设备进行输入/输出控制的一种方法,帧中断即是以数据帧长为间隔当交换机收到一个数据帧的首部时,只要查出帧的目的地址,就开始转发该帧,时隙中断即是以时隙长度为间隔进行分组交换。

s3:根据第一中断信号,配置主控fpga0的第一帧号,根据第二中断信号,回读主控fpga0的第二帧号,判断第一帧号与第二帧号是否一致,若一致,则将第一帧号与第二帧号作为同步帧号,进入步骤s4,否则,重复步骤s1~s3;

回读主控fpga0的第二帧号,为根据主控fpga0的反馈读取。

这一步主要是为主控fpga0的同步帧号进行匹配,能够将匹配的同步帧号通过主控fpga0去控制子fpga,使得每个子fpga上的同步帧号与主控fpga0上的帧号进行同步。

所述步骤s3中,配置主控fpga0的第一帧号的具体方法步骤包括:

根据主控fpga0的帧信号进行初始化;以第一中断信号状态为基准,对初始化后的帧信号和帧头进行信息分配。

s4:通过主控fpga0向子fpga配置同步帧号,获得第一子同步帧号,检测第一子同步帧号与同步帧号的无线帧终端是否一致,若一致,则系统时间同步成功,否则,进入步骤s5;

当主控fpga0向子fpga的同步帧号配置完成之后,还需要对子fpga上的第一子同步帧号与主控fpga0上同步帧号进行比对,在比对一致的情况下,才能算作系统时间同步成功,若比对不一致,则需要进行下一步操作。

s5:在主控fpga0无线帧的第二个时隙时,通过spi总线广播向子fpga配置同步帧号,获得子fpga的第二子同步帧号;

在通过spi总线广播向子fpga配置同步帧号的时候,先进行初始化过程,在按照spi总线船舶的第二个时隙时间状态进行参数设置。

s6:通过背板轮询方式回读子fpga的第二子同步帧号,并将第二子同步帧号与同步帧号进行比对,若比对一致,则系统时间同步成功,否则,重复步骤s1~s6。

所述通过背板轮询方式回读子fpga的第二子同步帧号的具体方法为:

在主控fpga0无线帧第四个时隙时,采用背板轮询方式,以时隙为颗粒度通过spi总线回读子fpga的第二子同步帧号。

背板轮询,每一个fpga所在的处理板上是通过背板进行互联和通信的,即是通过以时分的方式对各个板卡进行同步和配置,时分方式指的是各个板卡之间按照时间顺序进行周期性的配置。

实施例二

本实施例基于实施例一的基础上,公开了一种能够实现实施例一种时间同步方法的数字多波束信号处理系统,如图2所示,所述系统包括;

综合处理机,用于获取同源1pps信号,并将1pps信号作用于主控fpga0,且根据主控fpga0反馈的信号,向主控fpga0配置帧号;

在多波束信号处理系统中,里面所有的硬件板有一个同源1pps,且作为同步脉冲信息,122.88m时钟作为脉冲采集时钟,当1pps脉冲信号发送到各个fpga板上的时候,处理板上的fpga会产生帧中断信号以及时隙中断信号,并将产生的帧中断信号与时隙中断信号反馈给综合处理机,让综合处理机进行处理;

当综合处理机接收到处理板的帧中断信号与时隙中断信号后,会根据接收到的反馈信号向主控fpga0配置第一帧号,在根据传输过来的第二个帧中断信号与时隙中断信号,回读此刻在主控fpga0上的第二帧号,同时检测第一帧号与第二帧号是否一致,若一致,则代表匹配成功,并将第一帧号与第二帧号同时作为同步帧号,若不一致,则代表匹配没有成功,则需要重复的对主控fpga0进行同步帧号匹配。

主控fpga0,用于产生第一中断信号与第二中断信号,将第一中断信号与第二中断信号反馈到所述综合处理机内,同时接收综合处理机配置的帧号,匹配出同步帧号,并将同步帧号配置给子fpga,同时检测子fpga的子同步帧号与主控fpga0的同步帧号是否一致;

主控fpga0在同步帧号匹配完成之后,将匹配的同步帧号,通过信号传输的方式,匹配给子fpga板上,并且主控fpga在时间内读取子fpga上的子同步帧号,并将子同步帧号与同步帧号做比对,若一致,则表示系统的帧信号同步成功,若不一致,则表示系统的帧号信息同步未成功。

子fpga,用于接收主控fpga0配置的帧号,实现与主控fpga0帧号同步;

背板,用于通过导线将主控fpga与子fpga连接。所述时间同步系统包括若干子fpga。

主控fpga0与子fpga之间的连接,是通过导线连接的,但是他们是借助于通过背板将各个fpga板之间进行连接。

以上所述的具体实施方式,对本发明的目的、技术方案和有益效果进行了进一步详细说明,所应理解的是,以上所述仅为本发明的具体实施方式而已,并不用于限定本发明的保护范围,凡在本发明的精神和原则之内,所做的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

本文用于企业家、创业者技术爱好者查询,结果仅供参考。