1.本发明涉及一种半导体封装及其制造方法,尤其涉及一种具有传感区的半导体芯片的半导体封装及其制造方法。

背景技术:

2.近年来,例如智能手机、平板电脑、穿戴式电子设备等越来越多电子设备,逐渐采用传感器来控制由设备所提供的各种操纵功能。由于对传感器封装的高可制造性(manufacturability)以及质量的要求越来越高,因此需要具有灵活且可靠的方法以将传感器封装在芯片上。因此,为了使传感器封装达到具有更好的操作性和更高可制造性,如何提升传统芯片封装方法实成为亟欲解决的课题。

技术实现要素:

3.本发明是针对一种半导体封装及其制造方法,其可以将具有传感器的半导体芯片整合且内连线(interconnect)于芯片级封装,并将其最佳化。

4.根据本发明的实施例,一种半导体封装,包括多个第一芯片、多个硅穿孔、至少一绝缘体、第一电路结构与第一密封体。每一第一芯片包括第一有源面、第一有源面上的传感区、相对于第一有源面的第一背面与从第一背面朝向第一有源面延伸的多个通孔。多个硅穿孔配置于多个第一芯片的多个通孔中且与多个第一芯片电性连接。绝缘体配置于多个第一芯片的第一有源面上。第一电路结构配置于多个第一芯片的第一背面上且与多个硅穿孔电性连接。

5.第一密封体侧向包封多个第一芯片。

6.在本发明的一实施例中,上述的第一密封体配置于绝缘体上。

7.在本发明的一实施例中,上述的第一密封体更侧向包封绝缘体。

8.在本发明的一实施例中,上述的第一密封体更侧向包封第一电路结构。

9.根据本发明的实施例,一种半导体封装的制造方法。方法至少包括以下步骤。提供第一芯片,其中第一芯片包括第一有源面、第一有源面上的传感区、相对于第一有源面的第一背面与从第一背面朝向第一有源面延伸的多个通孔;形成多个硅穿孔于第一芯片的多个通孔中。形成第一电路结构于第一芯片的第一背面上以与多个硅穿孔电性连接;配置第二芯片于第二电路结构上,其中第二芯片包括面朝向第一芯片的第一有源面的第二有源面,且第二芯片与第一芯片电性连接;以及形成第二密封体于第一电路结构上以侧向包封第二芯片。

10.在本发明的一实施例中,上述的在形成多个硅穿孔之前,形成第一密封体,以侧向包封第一芯片。

11.根据本发明的实施例,一种半导体封装的制造方法。方法至少包括以下步骤。提供多个第一芯片,每一第一芯片包括第一有源面、第一有源面上的传感区、相对于第一有源面的第一背面以及从第一背面朝向第一有源面延伸的多个通孔;形成多个硅穿孔于多个第一

芯片的多个通孔中;形成第一电路结构于第一芯片的第一背面上以与多个硅穿孔电性连接;提供载板;提供至少一绝缘体;接合载板、绝缘体与多个第一芯片于多个硅穿孔与第一电路结构,其中绝缘体配置于载板与第一芯片之间,第一芯片的第一有源面面向绝缘体,且第一芯片配置于在板上且彼此被物理分隔;形成第一密封体于载板上,其中第一密封体侧向包封第一芯片;以及形成第二电路结构于第一密封体上。

12.在本发明的一实施例中,上述的形成多个导电端子于第二电路结构,其中多个导电端子与第一芯片以及第二芯片电性连接。

13.在本发明的一实施例中,上述的提供第一芯片包括提供载板。形成绝缘体于载板。配置第一芯片于绝缘体上,其中第一芯片的第一有源面面向绝缘体。

14.在本发明的一实施例中,上述的在形成第二电路结构之后,多个第一芯片通过第二电路结构彼此电性连接。

15.为让本发明的上述特征和优点能更明显易懂,下文特举实施例,并配合所附附图作详细说明如下。

附图说明

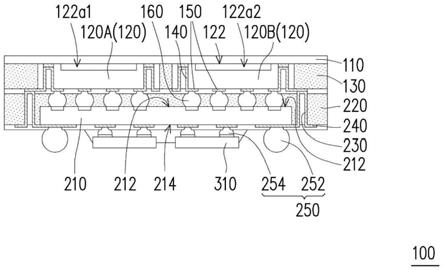

16.图1a至图1j是根据本发明一实施例的半导体封装的制造方法的剖面示意图;

17.图2a以及图2b是图1c中的半导体封装的制造方法的区域tv的放大剖面示意图;

18.图3a至图3d是根据本发明一实施例的半导体封装的制造方法的剖面示意图;

19.图4a至图4d是根据本发明一实施例的半导体封装的制造方法的剖面示意图;

20.图4e是根据本发明一实施例的半导体封装的制造方法的俯视示意图;

21.图5是根据本发明一实施例的半导体封装的制造方法的剖面示意图;

22.图6a至图6d是根据本发明一实施例的半导体封装的制造方法的剖面示意图;

23.图6e是根据本发明一实施例的半导体封装的制造方法的俯视示意图。

24.附图标记说明

25.50:临时载板

26.51:去黏合层

27.53:永久载板

28.100、200、400、600:半导体封装

29.110、411、611:绝缘体

30.120、120a、120b、420:第一芯片

31.122:第一有源面

32.122a、122a1、122a2、422a:传感区

33.124:第一背面

34.126:第一导电接垫

35.128、222:通孔

36.128a:内侧壁

37.130:第一密封体

38.130a、220a、252a、254a:顶面

39.140、440:硅穿孔

40.142:第一绝缘部分

41.144:第一阻障部分

42.146:第一晶种部分

43.148:第一导电部分

44.150、427:第一电路结构

45.152:第二绝缘部分

46.154:第二阻障部分

47.156:第二晶种部分

48.158:第二导电部分

49.160、250、460:导电端子

50.210、510:第二芯片

51.212、512:第二有源面

52.214、514:第二背面

53.216、516:第二导电接垫

54.220:第二密封体

55.230、530:模塑通孔

56.240、440、540:第二电路结构

57.252:第一元件

58.254:第二元件

59.310:第三芯片

60.312:前表面

61.314:导电连接器

62.316:底胶

63.412、612、p1a、p2a、p2a’:开口

64.413、613:空穴

65.422:有源面

66.424:背面

67.426:导电接垫

68.428:导电柱

69.430:密封体

70.cr:中央区

71.l1:绝缘层

72.l2:阻障层

73.l3:晶种层

74.l4:导电层

75.p1:第一保护层

76.p2、p2’:第二保护层

77.pr:周边区

78.tv:区域

具体实施方式

79.现将详细地参考本发明的示范性实施例,示范性实施例的实例说明于附图中。只要有可能,相同元件符号在附图和描述中用来表示相同或相似部分。

80.下文将会附加标号以对本发明较佳实施例进行详细描述,并以附图说明。在可能的情况下,相同或相似的构件在附图中将以相同的标号显示。

81.图1a至图1j是根据本发明一实施例的半导体封装的制造方法的剖面示意图。图2a以及图2b是图1c中的半导体封装的制造方法的区域tv的放大剖面示意图。

82.请参照图1a,可以提供临时载板50。临时载板50可以是玻璃衬底、芯片衬底或其他适宜的衬底材料,只要前述的材料能够于后续的工艺中,承载形成于其上的封装件。

83.在一些实施例中,去黏合层51可以形成于临时载板50上,以于之后的工艺中提升结构(如在工艺中的中间结构)与临时载板50的离型性(releasability)。举例而言,去黏合层51可以是光热转换(light-to-heat-conversion,lthc)离型层或其他适宜的离型层。

84.绝缘体110可以形成于临时载板50上。举例而言,绝缘体110可以是通过沉积工艺、旋转涂布(spin coating)工艺、狭缝式涂布(slit coating)工艺或其他适宜的工艺,以如聚合物、可固化树脂的绝缘材料或其他适宜的保护材料所形成。在一实施例中,绝缘体110可以被称为覆盖层或硬涂层(hard coating layer)。

85.在一些实施例中,绝缘体110可以形成于去黏合层51上,但本发明不限于此。

86.在一未示出的实施例中,绝缘体110可以直接形成于临时载板50上。

87.在形成绝缘体110之后,多个第一芯片120可以配置于绝缘体110上。在图1a中第一芯片120的数量仅用于示例性的示出,而本发明不限于此。举例而言,在图1a中示例性的示出四个第一芯片120。

88.在一实施例中,在配置第一芯片120之后,可以依据设计上的需求对绝缘体110进行固化工艺,以提升对第一芯片120的保护。

89.第一芯片120具有第一有源面122、位在第一有源面122上的传感区122a以及相对于第一有源面122的第一背面124。第一芯片120可以以第一有源面122面向绝缘体110的方式配置于绝缘体110上。

90.在一些实施例中,第一芯片120可以包括位在第一有源面122上,且围绕传感区122a的多个第一导电接垫126。

91.在一些实施例中,第一芯片120的第一有源面122上的第一导电接垫126可以被绝缘体110所覆盖。在一实施例中,第一芯片120的第一有源面122上的传感区122a以及第一导电接垫126可以被绝缘体110所覆盖。

92.在一些实施例中,第一芯片120可以是传感芯片。根据设计上的需求任何适宜的传感器可以用于第一芯片120上,本发明不限于此。

93.在一些实施例中,第一芯片120可以包括光学传感器,其可以采用如光电二极管(photodiode)、光电晶体(phototransistor)或其类似者的光检测器,以传感光并将接收的光能转换成电信号,以由第一芯片120上的电子电路进行处理。在这种情况下,绝缘体110可以是半透明或透明,以使光传递到第一芯片120的传感区122a。

94.在一实施例中,第一芯片(如图4b、图5或图6b中的第一芯片)可以包括其可以采用化学传感器、生物传感器或其类似者的分子传感器。在一未示出的实施例中,第一芯片可以

是微机电系统(mems)芯片。

95.在一实施例中,多个第一芯片120可以包括第一芯片120a(可以被称为第一传感芯片)以及第一芯片120b(可以被称为第二传感芯片)。第一芯片120a的传感区122a1内包括的光电传感材料与第一芯片120b的传感区122a2内包括的光电传感材料可以是不同形式。因此,第一芯片120a的传感波长范围可以与第一芯片120b的传感波长范围不同。换句话说,具有光学传感器的多个第一芯片120可以分别收集不同波长的光,并提供互补的光谱响应度(spectral responsivity)。举例而言,第一芯片120a为红外线(infrared,ir)检测芯片以及第一芯片120b为可见光检测芯片,但本发明不限于此。

96.请参照图1b,第一密封体130可以形成于临时载板50上,以侧向包封第一芯片120。

97.在一实施例中,第一密封体130可以通过模塑工艺(molding process)(如覆模工艺(over-molding process))或其他适宜的工艺,以如树脂(如环氧树脂(epoxy))的绝缘材料或其他适宜的绝缘材料所形成。在一实施例中,形成于临时载板50上的前述绝缘材料的厚度可以大于第一芯片120的厚度。在这种情况下,举例而言,可以通过研磨工艺(grinding process)、抛光工艺(polishing process)或其他适宜的工艺减薄绝缘材料的厚度,以暴露出第一芯片120的第一背面124。

98.在一实施例中,可以在进行厚度减薄工艺的期间,移除第一芯片120的背侧(如相对于第一有源面122的一侧)上的部分块状半导体材料(如块状硅),但本发明不限于此。

99.第一芯片120的第一背面124可以与第一密封体130的顶面130a(如第一密封体130远离临时载板50的表面)共面(coplanar)。

100.在形成第一密封体130之后,从第一背面124朝向第一有源面122的多个通孔128可以用蚀刻、钻孔或其他适宜的工艺形成于每一第一芯片120上,以暴露出第一导电接垫126。

101.请参照图1c、图2a与图2b,多个硅穿孔(tsvs)140可以形成于各个第一芯片120的通孔128中,以电性连接至第一导电接垫126。电性连接至硅穿孔140的第一电路结构150可以形成于第一芯片120的第一背面124上。

102.在一些实施例中,部分第一电路结构150可以形成于第一密封体130的顶面130a上,本发明不限于此。

103.在一些实施例中,第一电路结构150的导电部分以及硅穿孔140的导电部分可以于相同工艺或类似工艺(如沉积工艺)的期间一起形成,但本发明不限于此。

104.在一实施例中,第一芯片120用于信号传输的导线可以用第一电路结构150重新分布出去。在一实施例中,第一电路结构150可以被称为重布线路层(redistribution layer;rdl)。

105.形成硅穿孔140与第一电路结构150的示例如下。

106.请参照图2a,举例而言,绝缘材料可以用沉积工艺、旋转涂布工艺或其他适宜的工艺形成于第一芯片120的第一背面124上与通孔128中。绝缘材料可以由如聚酰亚胺(polyimide),聚苯并恶唑(polybenzoxazole,pbo),苯环丁烯(benzocyclobutene,bcb)所制成的聚合物,或是以四乙氧基硅烷(tetraethoxysilane,teos)进行化学气相沉积(chemical vapor deposition,cvd)或原子沉积法(atomic layer deposition,ald)所形成的氧化硅或其类似者所制成。

107.在形成绝缘材料之后,举例而言,可以用蚀刻工艺移除通孔128中绝缘材料的底

部,以暴露出第一导电接垫126,而形成绝缘层l1。举例而言,绝缘层l1可以包括第一绝缘部分142与第二绝缘部分152,第一绝缘部分142形成于通孔128的内侧壁128a,第二绝缘部分152形成于第一背面124上且藕合至第一绝缘部分142。

108.在一实施例中,第二绝缘部分152可以完全覆盖第一芯片120的第一背面124,但本发明不限于此。在一实施例中,第二绝缘部分152可以完全覆盖第一芯片120的第一背面124以及第一密封体130的顶面130a,但本发明不限于此。

109.请参照图2b,在形成绝缘层l1之后,阻障层l2、晶种层l3以及导电层l4可以形成于第一芯片120的通孔128中以及第一背面124上,以覆盖绝缘层l1以及第一导电接垫126。

110.在一些实施例中,在形成阻障层l2之后,可以通过阻障层l2暴露出至少一部份的第一芯片120的第一背面124上的绝缘层l1。

111.在一实施例中,晶种层l3可以共形(conformally)形成于阻障层l2上且导电层l4可以共形形成于晶种层l3上。换句话说,阻障层l2、晶种层l3以及导电层l4其可以彼此共形被称为一个单一层。

112.在一实施例中,阻障层l2可以作为扩散阻障(diffusion barrier),以防止形成于其上的导电层向介电质中迁移。晶种层l3可以改善通孔128中的导电层l4的结合力。在一实施例中,导电层l4可以被电镀且填充于通孔128中,以形成导电柱。阻障层l2的材料可以包括钛、钽或其他适宜的材料。晶种层l3的材料可以包括铜、金、镍或其合金。导电层l4的材料可以包括铜、金、银或其组合。

113.举例而言,阻障层l2可以包括第一阻障部分144以及第二阻障部分154,第一阻障部分144形成于通孔128中且耦合至第一导电接垫126,第二阻障部分154形成于第一背面124上且耦合至第一阻障部分144。覆盖阻障层l2的晶种层l3可以包括第一晶种部分146以及第二晶种部分156,第一晶种部分146形成于通孔128中,第二晶种部分156形成于第一背面124上且耦合至第一晶种部分146。覆盖晶种层l3的导电层l4可以包括第一导电部分148以及第二导电部分158,第一导电部分148形成于通孔128中,第二导电部分158形成于第一背面124上且耦合至第一导电部分148。

114.在一些实施例中,形成于通孔128中的部分(如绝缘层l1的第一绝缘部分142、阻障层l2的第一阻障部分144、晶种层l3的第一晶种部分146以及导电层l4的第一导电部分148)可以被称为是硅穿孔140。

115.至少形成于第一背面124上的导电部分(如阻障层l2的第二阻障部分154、晶种层l3的第二晶种部分156及/或导电层l4的第二导电部分158)可以被称为是第一电路结构150。在一实施例中,第一电路结构150可以包括导电部分(如阻障层l2的第二阻障部分154、晶种层l3的第二晶种部分156及/或导电层l4的第二导电部分158)以及绝缘部分(如绝缘层l1的第二绝缘部分152)。

116.硅穿孔140延伸穿过第一芯片120且电性连接至第一电路结构150,可以在第一芯片120的第一背面124处提供与第一导电接垫126输入/输出(i/o)接触。

117.请参照图1d,举例而言,多个导电端子160可以用电镀工艺、植球工艺(ball placement process)或其他适宜的工艺形成于第一电路结构150上。

118.在一实施例中,具有多个开口p1a的第一保护层p1可以形成于第一电路结构150及/或第一密封体130上。举例而言,保护材料(如环氧树脂、聚酰亚胺、聚苯并恶唑(pbo),苯

环丁烯(bcb))可以形成于第一电路结构150及第一密封体130上。接着,可以移除保护材料的一部分,以形成具有开口p1a的第一保护层p1,以暴露出第一电路结构150的至少一部分。在一实施例中,第一保护层p1可以包括光致抗蚀剂材料且通过曝光显影工艺形成开口p1a。然后,导电端子160可以形成于第一保护层p1的开口p1a中,以直接接触暴露出的第一电路结构150并与第一芯片120电性连接。在一实施例中,导电端子160可以包括导电球、导电柱、导电凸块或其组合。然而,本发明不限于此。可以根据设计上的需求采用其他可能的形式或形状的导电端子160。为了增加导电端子160与第一电路结构150的结合力,可以选择性地执行焊接工艺(soldering process)及回焊工艺(reflowing process)。

119.请参照图1e,可以经由导电端子160于第一电路结构150上配置第二芯片210。

120.第二芯片210可以包括面向第一芯片120的第一背面124的第二有源面212、相对于第二有源面212的第二背面214以及分布于第二有源面212上的多个第二导电接垫216。换句话说,第二芯片210的第二有源面212与第一芯片120的第一背面124可以面向彼此。第二芯片210可以经由第一电路结构150电性连接至第一芯片120。换句话说,穿过第一芯片120的电信号可以通过第一导电接垫126至硅穿孔140、第一电路结构150、导电端子160并至第二芯片210的第二导电接垫216。

121.请参照图1f,第二密封体220形成于第一电路结构150上,以侧向包封第二芯片210与导电端子160。换句话说,通过第二密封体220包封的第二芯片210可以配置于第一芯片120与第一密封体130上。

122.在一实施例中,第二密封体220可以类似于第一密封体130。举例而言,第二密封体220可以通过模塑工艺(如覆模工艺)或其他适宜的工艺,以如树脂(如环氧树脂)的绝缘材料或其他适宜的绝缘材料所形成。在一实施例中,第一电路结构150上形成的前述绝缘材料的厚度可以大于第二芯片210的厚度。在这样的情况下,举例而言,可以用研磨工艺或其他适宜的工艺减薄绝缘材料的厚度,以暴露出第二芯片210的第二背面214。

123.在一实施例中,在厚度减薄工艺的期间,可以移除第二芯片210的背侧(如相对于第二有源面212的一侧)上的部分块状半导体材料(如块状硅),但本发明不限于此。

124.第二芯片210的第二背面214可以与第二密封体220的顶面220a共面。第二密封体220的顶面220a为远离第一密封体130的表面。

125.在一实施例中,在形成第二密封体220之后,举例而言,围绕第二芯片210的多个通孔222可以用雷射钻孔、机械钻孔或其他适宜的工艺形成于第二密封体220上。通孔222可以暴露出第一电路结构150的至少一部分。

126.请参照图1g,多个模塑通孔(tmvs)230可以形成于通孔222中,以电性连接至第一电路结构150以及第一芯片120。电性连接至模塑通孔230的第二电路结构240可以形成于第二芯片210的第二背面214上。

127.在一实施例中,第二芯片210用于信号传输的导线可以用第二电路结构240重新分布出去。在一实施例中,第二电路结构240可以被称为重布线路层。

128.在一实施例中,模塑通孔230以及第二电路结构240可以于相同工艺或类似工艺(如沉积工艺)期间一起形成,但本发明不限于此。

129.举例而言,如铜、铝、镍或其类似者的导电材料(未示出)可以通过溅镀工艺、沉积工艺、电镀工艺或其他适宜的工艺形成于第二芯片210的第二背面214上与第二密封体220

的通孔222中。接着,可以通过微影(photolithography)与蚀刻工艺(etching process)对导电材料图案化,以形成图案化导电层。形成于通孔222中的图案化导电层的一部分可以被称为模塑通孔230以及形成于第二芯片210的第二背面214上的图案化导电层的另一部分可以称为第二电路结构240。在一实施例中,在导电材料之前,晶种(seed)材料可以形成于第二芯片210的第二背面214上与第二密封体220的通孔222中。

130.请参照图1h,多个导电端子250可以形成于第二电路结构240上,以与第一芯片120以及第二芯片210电性连接。

131.在一实施例中,具有多个开口p2a的第二保护层p2可以形成于第二密封体220上,以覆盖第二电路结构240且可以通过第二保护层p2的开口p2a暴露出第二电路结构240的至少一部分。第二保护层p2的形成工艺可以类似于第一保护层p1,而省略详细描述。

132.在形成第二保护层p2之后,导电端子250可以形成于第二保护层p2的开口p2a中,以与暴露出的第二电路结构240直接接触且电性连接至第二芯片210。举例而言,导电端子250可以包括通过植球工艺、电镀工艺或其他适宜工艺形成的导电球、导电柱、导电凸块或其组合。然而,本发明不限于此。此外,为了增加导电端子250与第二电路结构240的结合力,可以选择性地执行焊接工艺及回焊工艺。

133.在一实施例中,导电端子250可以包括多个第一元件252以及多个第二元件254,第一元件252形成于第二芯片210的中央区cr,多个形成于第二芯片210围绕中央区cr的周边区pr。第二元件254的尺寸可以大于第一元件252的尺寸。换句话说,从第一元件252的顶面252a至第二电路结构240的最短距离可以小于第二元件254的顶面254a至第二电路结构240的最短距离。在一些替代实施例中,第一元件252的顶面252a可以与第二元件254的顶面254a对齐。

134.请参照图1i,第三芯片310可以配置于第二电路结构240上。举例而言,第三芯片310可以包括面向第二芯片210的第二背面214的前表面312与分布于前表面312上的多个导电连接器314。第三芯片310的导电连接器314可以电性连接至第二电路结构240。

135.在一实施例中,在形成导电端子250之前,可以于第二电路结构240上配置第三芯片310。在这样的情况下,在使用覆晶(flip-chip)技术于第二电路结构240上配置第三芯片310之后,可以省略形成导电端子250的第一元件252。换句话说,第三芯片310可以直接通过导电连接器314电性连接至第二电路结构240,其可以作为第一元件252,因此形成导电端子250的第一元件252可以是不必要的。

136.在一实施例中,底胶316可以形成于第三芯片310与第二保护层p2的间隙之间,以提升贴附工艺的可靠度(reliability)。在一示例性的实施例中,作为记忆体的第三芯片310电性连接至具有传感区122a的第一芯片120以及作为处理器的第二芯片210。在这样的情况下,第三芯片310可以在第二芯片210的处理下进行各种应用。

137.在一实施例中,可以提供配置具有不同功能多于一个的第三芯片310于第二电路结构240上。图1i中所示的第三芯片310的数量仅作为示例性的示出而本发明不限于此。

138.可以执行切单工艺(singulation process)且可以移除临时载板50,因此实质上完成了如图1j所示的半导体封装100的工艺。

139.在一实施例中,在配置第三芯片310之后,可以执行切单工艺。在切单工艺之后,可以从绝缘体110上移除临时载板50。举例而言,可以将紫外光雷射、可见光或热等外部能量

施加到至去黏合层51,以使绝缘体110可以从临时载板50上剥离。

140.在一实施例中,可以在配置第三芯片310前执行切单工艺。本发明不限制切单工艺与配置第三芯片310的工艺顺序。

141.在通过上述半导体封装100的制造方法可以整合第一芯片120、第二芯片210以及第三芯片310,而可以提升半导体封装100的作业效能(operating performance)以及可制造性(manufacturability)。

142.图3a至图3d是根据本发明一实施例的半导体封装的制造方法的剖面示意图。本实施例的制造方法类似于图1a至图1j的实施例的说明而工艺描述可以省略。

143.请参照图3a,硅穿孔440可以为导电柱,且硅穿孔440填充于第一芯片120的通孔128内,以电性连接至第一电路结构150。举例而言,在图2b中最上层的导电层l4可以形成绝缘层l1、阻障层l2以及晶种层l3之后填充于通孔128中。接着,在形成第一电路结构150与硅穿孔440之后,第一保护层p1可以形成于第一电路结构150与第一密封体130上。第一保护层p1具有暴露出第一电路结构150的至少一部份的开口p1a。然后,多个模塑通孔530可以形成于暴露出的第一电路结构150上。

144.举例而言,可以通过旋转涂布光致抗蚀剂材料,并将光致抗蚀剂材料烘烤且微影(即,曝光及显影工艺),以在第一保护层p1上形成具有预定图案的图案化光致抗蚀剂层(未示出)。部分已被暴露出的第一电路结构150可以进一步暴露于图案化光致抗蚀剂层。接下来,可以通过电镀工艺或其他适宜的工艺,以在被图案化光致抗蚀剂层进一步暴露出的第一电路结构150上形成模塑通孔530。在形成模塑通孔530之后,例如可以通过蚀刻、灰化或其他适宜的移除工艺来移除图案化光致抗蚀剂层。

145.请参照图3b,在形成模塑通孔530之后,可以通过于第一电路结构150上覆晶接合配置第二芯片510。换句话说,在本实施例中,采用覆晶技术的第一芯片120与第二芯片510可以经由分布于第二有源面512上的第二导电接垫516电性连接。与图1e所示出的实施例相比,在本实施例中,可以省略于第一芯片120与第二芯片510之间形成导电端子。在一实施例中,所形成的模塑通孔530可以围绕第一芯片120,且第二芯片510可以配置于第一电路结构150上,而第二芯片510覆盖于第一芯片120上。然后,可以形成第二密封体220,以侧向包封第二芯片510与模塑通孔530。第二密封体220的形成工艺可以类似于图1f所示出的实施例而省略详细描述。为了进一步电性连接,可以减薄第二密封体220的厚度,以暴露出模塑通孔530的至少一部分。

146.请参照图3c与图3d,在形成第二密封体220之后,第二电路结构540可以形成于模塑通孔530与第二芯片510的第二背面514上。举例而言,具有多个开口p2a’的第二保护层p2’可以形成于第二密封体220与第二芯片510上,且开口p2a’暴露出模塑通孔530的至少一部分。接着,第二电路结构540可以形成于第二保护层p2’的开口p2a’中。在一实施例中,依电路设计上的需求,第二保护层p2’与第二电路结构540的形成工艺可以执行多次,以获得多层电路。为了进一步电性连接,最上层的第二保护层p2’可以具有暴露出至少一部分顶部第二电路结构540的开口p2a’。在形成第二电路结构540之后,后续的制造过程可以类似于如图1h至图1j的实施例中的描述,而省略详细描述。在执行切单工艺且移除临时载板50之后,实质上完成了如图3d所示的半导体封装200的工艺。

147.基于上述,绝缘体覆盖第一芯片的第一有源面可以保护第一有源面上的传感区,

以避免在后续的工艺中被损坏。此外,绝缘体与传感区之间的距离最小化,以达到改善半导体封装的传感能力。第二芯片的第二有源面面朝向第一芯片的第一背面。此外,第一电路结构与硅穿孔于第一芯片与第二芯片之间电性连接。如此一来,半导体封装可以使第一芯片与第二芯片之间维持较短的电子传递路径,以降低信号的传递、较低的电容并达到较佳地电路效能。此外,具有导电连接器的第三芯片面朝向第二芯片的第二背面且经由第一电路结构与第二电路结构与第一芯片以及第二芯片电性连接。如此一来,半导体封装的制造方法可以整合第一芯片、第二芯片以及第三芯片,而可以达到较佳地作业效能以及较好地制造性。

148.图4a至图4d是根据本发明一实施例的半导体封装的制造方法的剖面示意图。图4e是根据本发明一实施例的半导体封装的制造方法的俯视示意图。举例而言,图4e可以是图4a的结构的俯视图。

149.请参照图4a与图4e,可以提供永久载板53。永久载板53可以包括玻璃衬底、芯片衬底、金属衬底、层压衬底或其他适宜的衬底材料,只要前述的材料能够于后续的工艺中,承载形成于其上的封装件。

150.在一实施例中,多个绝缘体411可以形成于永久载板53上。绝缘体411具有至少一开口412。图4a或图4e中绝缘体411的数量仅作为示例性示出而本发明不限于此。在一实施例中,绝缘体411可以被称为阻挡结构(dam structure)。

151.在一些实施例中,绝缘体411与永久载板53可以直接接触,但本发明不限于此。在一未示出的实施例中,黏着层可以配置于绝缘体411与永久载板53之间。

152.在一实施例中,形成绝缘体411的材料可以是环氧树脂、硅基树脂、橡胶或其他适宜的绝缘材料,但本发明不限于此。

153.请参照图4b,多个第一芯片420可以配置于绝缘体411上。多个硅穿孔140、第一电路结构427与多个导电柱428可以配置于每一第一芯片420上。

154.在一实施例中,第一芯片420中的一个可以对应配置于绝缘体411中的一个,但本发明不限于此。

155.在一实施例中,第一芯片420可以类似于第一芯片120。举例而言,第一芯片420可以包括有源面422、有源面422上的传感区422a、相对于有源面422的背面424与从背面424朝向有源面422延伸的多个通孔128。

156.在一实施例中,第一芯片420可以包括位在有源面422上,且环绕传感区422a的多个导电接垫426。举例而言,第一芯片420可以以有源面422面向绝缘体411配置于绝缘体411上。换句话说,第一芯片420的有源面422上的传感区422a与导电接垫426可以被绝缘体411所覆盖。第一芯片420的传感区422a对应至绝缘体411的开口412。换句话说,第一芯片420的传感区422a、绝缘体411的开口412与永久载板53可以构成空穴413(如图4c所标示)。

157.请参照图1c、图2b与图4b,多个硅穿孔(tsvs)140可以形成于每一第一芯片420的通孔128中,以电性连接至导电接垫426。硅穿孔140的形成工艺可以相同或类似于硅穿孔140的形成工艺,因此硅穿孔的形成工艺将于此不再赘述。

158.在一些实施例中,第一电路结构427可以配置于每一第一芯片420的背面424上。在一实施例中,第一电路结构427可以包括多个导电层、多个绝缘层以及多个导电通孔。导电层的对应部分及/或导电通孔的对应部分可以形成对应电路。第一电路结构427的对应电路

可以与对应硅穿孔140电性连接。第一电路结构427可以通过一般半导体工艺形成,而于此不再赘述。

159.在一实施例中,第一电路结构427可以被称为重布线路层。

160.在一实施例中,第一电路结构427投影于永久载板53上的正投影面积与第一芯片420投影于永久载板53上的正投影面积实质上相等。

161.在一实施例中,多个导电柱428可以配置于第一电路结构427上。导电柱428可以电性连接至第一电路结构427的对应电路。

162.请参照图4c,密封体430可以形成于永久载板53上,以侧向包封第一芯片420、第一电路结构427与导电柱428。密封体430可以通过模塑工艺(如覆模工艺)所形成。在一实施例中,密封体430可以通过如树脂(如环氧树脂)的绝缘材料或其他适宜的绝缘材料所形成。

163.在一实施例中,于永久载板53上形成的绝缘材料的厚度可以覆盖导电柱428的顶面428a。这样的情况下,举例而言,可以用研磨工艺或其他适宜的工艺减薄形成于永久载板53上的绝缘材料的厚度,以暴露出导电柱428的顶面428a,以形成密封体430。

164.在一些实施例中,导电柱428的顶面428a可以与密封体430远离永久载板53的顶面430a共面。

165.在一些实施例中,密封体430可以侧向包封绝缘体411。

166.请参照图4d,第二电路结构440可以形成于密封体430上。第二电路结构440的对应电路可以电性连接至对应的导电柱428。第一芯片420可以通过第二电路结构440的对应电路相互电性连接。第二电路结构440可以通过一般半导体工艺形成,因此于此不再赘述。

167.在一实施例中,第二电路结构440投影于永久载板53上的正投影面积可以大于第一芯片420投影于永久载板53上的正投影面积。在一实施例中,第二电路结构440可以被称为扇出重布线路层(fo rdl)。

168.在形成第二电路结构440之后,可以于第二电路结构440上形成多个导电端子460。导电端子460的形成工艺可以相同或类似于导电端子160的形成工艺,因此导电端子的形成工艺于此不再赘述。

169.在执行前述工艺之后,实质上形成了在本实施例中所提供的半导体封装400。

170.图5是依据本发明一实施例的半导体封装的制造方法的剖面示意图。本实施例的制造方法类似于图4a至图4e所示出的实施例,因此可以省略工艺描述。

171.请参照图5,在第一芯片420配置于永久载板53上之前,绝缘体411可以配置于第一芯片420的有源面422上。换句话说,具有绝缘体411在上的第一芯片420可以配置于永久载板53上。

172.在绝缘体411与第一芯片420配置于永久载板53上之后,可以通过类似于图4c至图4d的步骤提供本实施例中的半导体封装。

173.图6a至图6d是依据本发明一实施例的半导体封装的制造方法的剖面示意图。图6e是依据本发明一实施例的半导体封装的制造方法的俯视示意图。举例而言,图6e是图6a的结构的俯视示意图。本实施例的制造方法类似于图4a至图4e所示出的实施例而可以省略工艺描述。

174.请参照图6a至图6e,绝缘体611可以形成于永久载板53上。绝缘体611具有多个开口612。在一实施例中,绝缘体611可以被称为阻挡结构。

175.请参照图6b,多个第一芯片420可以配置于绝缘体611上。在一实施例中,可以于对应的绝缘体611中的一个上配置多于一个第一芯片420,但本发明不限于此。

176.第一芯片420的传感区422a对应于绝缘体611的开口612。换句话说,第一芯片420的传感区422、绝缘体611的开口612以及永久载板53可以构成对应空穴613。

177.在一实施例中,绝缘体611可以还具有多个微通道(microchannel)。微通道可以通过绝缘体611的表面(如面向永久载板53的表面)上的槽(groove)形成,但本发明不限于此。微通道可以连接对应空穴613。

178.请参照图6c至图6d,第一芯片420配置于永久载板53上之后,可以通过类似于图4c至图4d的步骤提供本实施例的半导体封装600(如图6d所标示)。

179.最后应说明的是:以上各实施例仅用以说明本发明的技术方案,而非对其限制;尽管参照前述各实施例对本发明进行了详细的说明,本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分或者全部技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本发明各实施例技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。