1.本实用新型涉及半导体光刻领域,尤其涉及一种测量套刻误差的测试结构。

背景技术:

2.套刻误差(overlay,ovl)是指在光刻制造工艺中,当前层的图案与前层图案之间的对准精度。由于集成电路芯片的制造是通过多层结构层叠而成,因此各层结构之间的套刻精度直接影响集成电路芯片的有效性及良品率。在半导体芯片的制备工艺中,可根据套刻误差值来调整制备集成电路芯片的工艺参数,以提高集成电路芯片的有效性及良品率,因此,测得精确的套刻误差值是提高良品率的关键步骤。

3.对于finfet制备工艺,制备的过程更为复杂,需应用很多张光罩光刻来完成,而目前对于因光罩光刻导致的晶圆(wafer)的套刻误差所采用的测量方法主要是光学测量方法,但光学测量的缺点是测量结构是专门的ovl pad,不能代表其他常用的或基本的金属线/栅极结构的套刻误差情况;且光学测量方法只能看到晶圆表面的套刻误差情况,对于真实的3d芯片,光学测量法并不能表征晶圆在表面以下的工艺偏移量情况。如图1所示,第一光罩1与第二光罩2在曝光之后完成图形的叠加,在理想情况下第一光罩1和第二光罩2完全对准,此时无套刻误差。但在实际的工艺制程中,第一光罩1和第二光罩2在光刻工艺过程中会产生套刻偏移量,如图2所示,第一光罩1和第二光罩2的图形叠加后,在晶圆下表面发生了偏移量,光学测量法仅能表征晶圆上表面的套刻误差,而监测不到晶圆表面下方发生的工艺偏移量,因而也无法表征两次光刻工艺之间真正的套刻误差。

4.因此,有必要提出一种不仅能测量晶圆平面套刻误差,且能在立体层面测量整体套刻误差的测量方法和测试结构。

技术实现要素:

5.本实用新型的主要目的在于克服现有技术中的全部或部分不足,提供一种测量套刻误差的测试结构,能在立体层面表征晶圆整体套刻误差,且能测量晶圆整体的套刻误差。为解决上述技术问题,本实用新型的解决方案是:

6.首先,本实用新型提供了一种用于测量套刻误差的测试子结构,其中,所述测试子结构包括第一光罩和第二光罩,所述第一光罩包括若干个第一图形,所述第二光罩包括若干个第二图形,所述第一光罩和第二光罩按预置套刻偏移量交叉叠加组合;所述第一图形既可以一个独立的图形,也可以是若干个独立或相互关联的子图形组成;第二图形也同样。工艺中根据实际需要来设置不同的组合,例如第一图形为一个独立的图形,第二图形为一些子图形组合而成。优选地,所述第一图形为栅结构图形或其组合,所述第二图形为金属线图形或其组合;所述第一图形连接形成正极板、所述第二图形连接形成负极板;或所述第一图形连接形成负极板、所述第二图形连接形成正极板;将所述正极板和负极板分别连线形成正测试端和负测试端。

7.所述预置套刻偏移量为零偏移量、左偏移量或右偏移量;所述零偏移量表示所述

子结构中的第二光罩相对于第一光罩位置对准,偏移量为0;所述左偏移量表示所述子结构中第二光罩相对于第一光罩的位置向左偏移的偏移量,所述右偏移量表示所述子结构中第二光罩相对于第一光罩的位置向右偏移的偏移量。本测试结构于晶圆平面来说可以测量平面任意方向例如x、y或者其他任何一个方向上的偏移量;为了方便说明,本实施例中采用以观察者为坐标用“左”或“右”的方式来说明,例如:从左向右、左偏移量、从右向左、右侧等。

8.此外,本实用新型还提供了一种测量套刻误差的测试结构,应用于晶圆套刻误差的测量,所述测试结构包括n个上述子结构,n个所述测试子结构分别具有不同的预置套刻偏移量,其中,n为不小于3的整数。优选地,所述n为3

‑

1000范围内的整数。

9.将预置套刻偏移量为零偏移量的子结构作为中心子结构;将预置套刻偏移量为左偏移量的子结构组成第一子结构群,所述第一子结构群的各子结构中的左偏移量以步长值递增;将预置套刻偏移量为右偏移量的子结构组成第二子结构群,所述第二子结构群的各子结构中的右偏移量以步长值递增。

10.作为本实用新型的另一方面,提供了一种测量套刻误差的方法,所述方法采用上述测试结构,所述方法包括测量各子结构的电容值,并将测量的电容值在坐标系中拟合形成曲线图,所述曲线图的纵坐标轴对应于各子结构测量的电容值,横坐标轴对应于各子结构中所述预置套刻偏移量,确定所述曲线图的谷值点,根据所述谷值点确定晶圆的真实套刻误差。

11.其中,横坐标的原点对应于中心子结构的零偏移量,横坐标的左半轴数值的绝对值对应于第一子结构群中子结构的预置的左偏移量,横坐标的右半轴的数值对应于第二子结构群中子结构的预置的右偏移量;确定所述曲线图的谷值点,其中,所述谷值点对应的横坐标值为m,若m为负数,则表示因第一光罩和第二光罩形成的晶圆的真实套刻误差为向右偏移|m|;若m为正数,则表示因第一光罩和第二光罩形成的晶圆的真实套刻误差为向左偏移m。

12.进一步地,为了降低电学测量方法在实际测量过程中因测量偏差带来的影响,以获得更加精确的套刻误差值,所述方法还包括形成多组测试结构,所述多组测试结构采用的所述步长值不同,测量所述多组测试结构的套刻误差,以所述多组测试结构的套刻误差的均值作为最终的套刻误差值。

13.所述步长值在0.1nm

‑

20nm范围内。步长值越小,电容测试得到的套刻误差的精度越准确。因此可根据工艺需求来调整步长,对于旧的工艺,例如对于0.18um逻辑芯片工艺,可选择5nm作为步长值,预置的套刻偏移量在

‑

40nm到 40nm范围内,其中

‑

40nm表示预置的左偏移量为40nm, 40nm表示预置的右偏移量为40nm;对于越先进的工艺技术节点,步长要求设置的数值越小越好,例如对于14nm的finfet制备工艺,可以选择以1nm为步长值, 预置的套刻偏移量在

‑

15nm到 15nm范围内。

14.所述正极板和负极板间的距离在1nm

‑

10nm范围内。

15.所述测量测试结构中各子结构的电容值时所采用的方法为lcr测量法、基于电荷的电容测量方法(cbcm ,charge based capacitance measurement)或基于正交时钟的电压电容测量法(qvcm ,quadrature

‑

clocked voltagedepen dent capacitance measurement)三种中的任意一种。

16.此外,基于本实用新型测量套刻误差的方法设置的一组测试结构,能测量的是因

两个光罩光刻导致的晶圆的套刻误差,当需要测量全部光罩光刻导致的晶圆的套刻误差时,则需要分别针对每两个光罩设置一组测试结构来完成测量过程。

17.与现有技术相比,本实用新型的有益效果是:

18.1、本实用新型通过设计特定的测试结构来实现晶圆套刻误差的测量,不仅能表征晶圆在光刻工艺过程中表面产生的套刻误差,同时能从立体角度表征整体的套刻误差。

19.2、本实用新型通过设计的测试结构结合电学测量法来准确测量晶圆的套刻误差,相对于传统的光学测量法,本实用新型中的电学测量法更易于实现,且测量值接近于真实的套刻误差。

20.3、本实用新型所提供的测量套刻误差的方法可根据芯片的制备工艺和精度要求,灵活调整测试结构的组成,例如根据制备工艺和精度要求设置更为精确的步长值和测试子结构数量,以达到根据工艺或精度需求准确测量晶圆套刻误差的目的。

附图说明

21.为了更清楚地说明本实用新型的技术方案,下面将对实施方式中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施方式,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以如这些附图获得其他的附图。

22.图1所示为光刻后光罩组合叠加的理想状况;

23.图2所示为光罩组合叠加后上表面下方产生套刻误差的情形;

24.图3所示为本实用新型实施例中的测试结构对应的光罩组合;

25.图4所示为本实用新型实施例中的一组测试结构的示意图;

26.图5所示为本实用新型实施例中的测试结构光刻后的电学测试方法连接图;

27.图6所示为本实用新型实施例中的测试结构实际测量电容值后拟合的曲线图。

28.附图标记:1

‑

第一光罩,2

‑

第二光罩,21、22、23、24、25

‑

子结构,3

‑

栅结构图形,4

‑

金属线图形。

具体实施方式

29.下面结合具体实施方式对本实用新型作进一步详细描述:

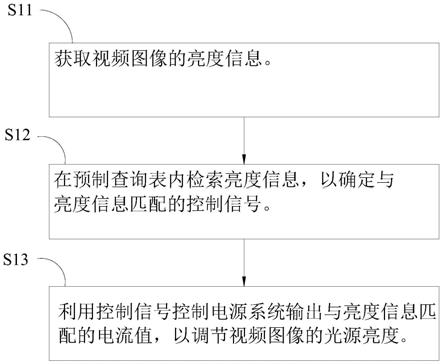

30.一种测量套刻误差的方法,通过设置一组测试结构并采用电学测量方法来测量晶圆整体的套刻误差,该测量套刻误差的方法包括:

31.步骤s1:获取待测套刻误差针对的光罩组合,如图3所示,所述光罩组合包括待叠加组合的第一光罩1和第二光罩2,所述第一光罩1包括2个栅结构图形3,所述第二光罩2包括2个金属线图形4。

32.步骤s2:形成一组测试结构,如图4所示,其中所述测试结构包括由所述第一光罩1和所述第二光罩2按预置套刻偏移量交叉叠加组合的5个子结构,所述5个子结构在空间上从左向右依次排布,位于中心位置的子结构23为中心子结构,所述中心子结构23左侧的子结构21和子结构22为第一子结构群,所述中心子结构23右侧的子结构24和子结构25为第二子结构群。本测试结构于晶圆平面来说可以测量平面任意方向例如x、y或者其他任何一个方向上的偏移量;为了方便说明,本实施例中采用以观察者为坐标用“左”或“右”的方式来

说明,例如:从左向右、左偏移量、从右向左、右侧等。

33.所述预置套刻偏移量分为零偏移量、左偏移量及右偏移量,其中所述零偏移量表示所述中心子结构23中的第二光罩2相对于第一光罩1位置对准;所述左偏移量表示所述第一子结构群的各子结构中的第二光罩2相对于第一光罩1的位置预置左偏移量,所述左偏移量以步长值按第一子结构群的空间位置从右向左递增,在本实施例中,子结构22中的第二光罩2相对于第一光罩1预置的左偏移量为1个步长值,子结构21中的第二光罩2相对于第一光罩1预置的左偏移量为2个步长值;所述右偏移量表示所述第二子结构群的各子结构中的第二光罩2相对于第一光罩1的位置预置右偏移量,所述右偏移量以步长值按第二子结构群的空间位置从左向右递增,在本实施例中,子结构24中的第二光罩2相对于第一光罩1预置的右偏移量为1个步长值,子结构25中的第二光罩2相对于第一光罩1预置的右偏移量为2个步长值。在本实施例中,所述步长值设置为5nm。

34.步骤s3:如图5所示,将按照步骤s2中得到的所述测试结构完成光刻并完成beol工艺步骤后,将测试结构中各子结构的所述栅结构图形3连接形成正极板,所述金属线图形4连接形成负极板,并将正极板和负极板分别连线形成正测试端和负测试端。

35.本实用新型采用测量子结构的电容值的电学测量方法来表征光刻工艺导致的晶圆的套刻误差,基于以下原理:

36.c=εs/d;(1)

37.在上述公式(1)中,c表示电容值,ε表示介电常数,s表示两个电极板的相对面积,d表示正负电极板的距离。

38.其中,ε和s在本实用新型的设计结构中是定值,因此电容c与d为关联因素,且呈负相关关系。本实用新型采用将测试结构中的子结构构成电极板并测量其电容的方法来表征极板间的距离,其中d对应于本技术中测量的套刻误差来说,等于第一光罩1和第二光罩2叠加组合得到的图形之间的距离。由于金属线或栅结构分别在整体上形成电容板,因此电容测量法表征的是光刻工艺导致的晶圆整体的套刻误差,而不仅是表征光刻工艺导致的晶圆上平面套刻误差。

39.步骤s4:采用lcr测量法来测量测试结构中各子结构的电容值,子结构21、22、23、24、25中测得的电容值分别为50pf、25pf、50pf、100pf、150pf,并将测量的电容值在坐标系中拟合形成曲线图,如图6所示,所述曲线图的纵坐标轴对应于各子结构测量的电容值,横坐标轴对应于各子结构中所述预置的套刻偏移量,其中横坐标的原点对应于中心子结构23的零偏移量,横坐标的左半轴数值的绝对值对应于第一子结构群中子结构21、22的预置的左偏移量,横坐标的右半轴的数值对应于第二子结构群中子结构24、25的预置的右偏移量。所述曲线图以曲线谷值点为中心,曲线在谷值点的左右两侧基本呈中心对称走向。

40.步骤s5:观察步骤s4中拟合的曲线谷值点,读取谷值点对应的横坐标值为

‑

5nm,表示因第一光罩1和第二光罩2形成的晶圆的真实套刻误差为向右偏移5nm。

41.最后,需要注意的是,以上列举的仅是本实用新型的具体实施例。显然,本实用新型不限于以上实施例,还可以有很多变形。本领域的普通技术人员能从本实用新型公开的内容中直接导出或联想到的所有变形,均应认为是本实用新型的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。