技术特征:

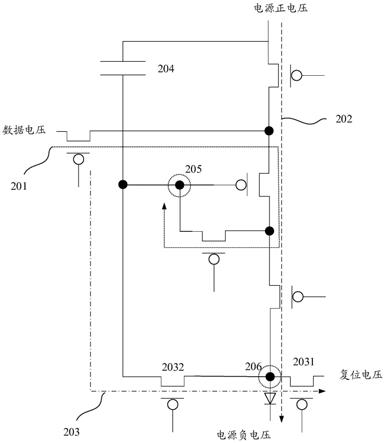

1.一种像素驱动电路,其特征在于,所述像素驱动电路包括:数据写入通路、发光通路、复位通路和电容器;所述数据写入通路的一端与数据电压连接,所述数据写入通路的另一端与第一节点连接;所述发光通路的一端与电源正电压连接,所述发光通路的另一端与电源负电压连接;所述复位通路包括第一晶体管和第二晶体管,所述第一晶体管的第一端与第二节点连接,所述第一晶体管的第二端与复位电压连接,所述第二晶体管的第一端与所述第一节点连接,所述第二晶体管的第二端与所述第二节点连接;所述电容器的一端与所述电源正电压连接,所述电容器的另一端与所述第一节点连接;其中,所述数据写入通路由第一门控信号控制,所述发光通路由第二门控信号控制,所述复位通路由第三门控信号控制。2.根据权利要求1所述的像素驱动电路,其特征在于,所述数据写入通路包括第三晶体管、第四晶体管和第五晶体管;所述第三晶体管的栅极与所述第一门控信号连接,所述第三晶体管的第一端与所述数据电压连接,所述第三晶体管的第二端与第三节点连接;所述第四晶体管的栅极与所述第一门控信号连接,所述第四晶体管的第一端与第四节点连接,所述第四晶体管的第二端与所述第一节点连接;所述第五晶体管的栅极与所述第一节点连接,所述第五晶体管的第一端与所述第三节点连接,所述第五晶体管的第二端与所述第四节点连接。3.根据权利要求1所述的像素驱动电路,其特征在于,所述发光通路包括第六晶体管、第七晶体管、第五晶体管和发光二极管;所述第六晶体管的栅极与所述第二门控信号连接,所述第六晶体管的第一端与所述电源正电压连接,所述第六晶体管的第二端与第三节点连接;所述第七晶体管的栅极与所述第二门控信号连接,所述第七晶体管的第一端与第四节点连接,所述第七晶体管的第二端与第二节点连接;所述发光二极管的正极与所述第二节点连接,所述发光二极管的负极与电源低电压连接;所述第五晶体管的栅极与所述第一节点连接,所述第五晶体管的第一端与所述第三节点连接,所述第五晶体管的第二端与所述第四节点连接。4.根据权利要求1所述的像素驱动电路,其特征在于,所述第一晶体管和所述第二晶体管的栅极均与所述第三门控信号连接。5.根据权利要求1所述的像素驱动电路,其特征在于,响应于所述像素驱动电路处于复位阶段,所述数据写入通路和所述发光通路断开,所述复位通路导通;响应于所述像素驱动电路处于数据写入阶段,所述复位通路和所述发光通路断开,所述数据写入通路导通;响应于所述像素驱动电路处于发光阶段,所述复位通路和所述数据写入通路断开,所述发光通路导通。6.根据权利要求5所述的像素驱动电路,其特征在于,在所述复位阶段,第一门控信号处于高电平,第二门控信号处于高电平,第三门控信号处于低电平;复位电压通过所述复位通路对第一节点和第二节点进行电压复位。

7.根据权利要求5所述的像素驱动电路,其特征在于,在所述数据写入阶段,第一门控信号处于低电平,第二门控信号处于高电平,第三门控信号处于高电平;数据电压通过所述数据写入通路对第一节点进行数据写入。8.根据权利要求5所述的像素驱动电路,其特征在于,在所述发光阶段,第一门控信号处于高电平,第二门控信号处于低电平,第三门控信号处于高电平;电源正电压和所述第五晶体管写入的数据电压控制所述发光二极管发光。9.根据权利要求1所述的像素驱动电路,其特征在于,所述第二晶体管为双门控晶体管。10.一种显示屏,其特征在于,所述显示屏包括权利要求1-9任一项所述的像素驱动电路。11.一种终端,其特征在于,所述终端包括权利要求10所述的显示屏。

技术总结

本申请涉及一种像素驱动电路、显示屏和终端,属于终端技术领域。该像素驱动电路包括:数据写入通路、发光通路、复位通路和电容器;通过像素驱动电路的数据写入、发光和复位,从而完成像素驱动电路的发光过程,将第一晶体管的第一端与第二节点连接,第一晶体管的第二端与复位电压连接,通过第三门控信号控制第一晶体管和第二晶体管的断开或导通状态,使得像素驱动电路在主要漏电路径中包括第一晶体管和第二晶体管,从而将漏电过程中漏电电流为电压经过第一晶体管和第二晶体管行程的电流,从而减小该主要漏电路径的漏电电流,使得不同频率下漏电电流的差异减小,从而减小矫正参数精细化调试难度。试难度。试难度。

技术研发人员:聂诚磊 崔志佳

受保护的技术使用者:OPPO广东移动通信有限公司

技术研发日:2020.04.20

技术公布日:2021/10/21

再多了解一些

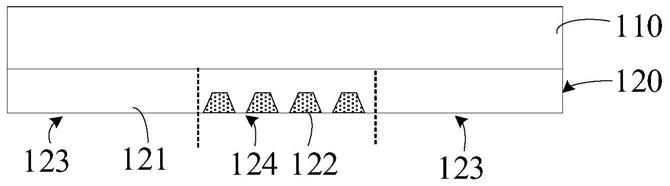

本文用于企业家、创业者技术爱好者查询,结果仅供参考。