1.本揭示中所述实施例内容是有关于显示技术,特别关于一种显示装置以及一种驱动晶片。

背景技术:

2.随着显示技术的发展,显示面板已被广泛地应用至各式电子设备上。举例而言,显示面板可被应用于电视、计算机、手机、穿戴式装置上。在运作上,显示面板可依据影像数据显示出对应的影像,以供使用者观看。

技术实现要素:

3.本揭示的一些实施方式是关于一种显示装置。显示装置包含一处理电路、一驱动电路以及一显示面板。驱动电路耦接处理电路且用以侦测处理电路与驱动电路之间的一数据传输是否为异常。显示面板耦接驱动电路且包含一显示阵列以及一移位暂存电路。显示阵列用以显示一影像。移位暂存电路耦接显示阵列。当数据传输于一第一帧的一第一显示周期内为异常时,由驱动电路输出给移位暂存电路的一控制信号于第一显示周期内包含一禁能位准,以控制移位暂存电路停止运作且影像停止更新。

4.在一些实施例中,驱动电路包含一栅极控制器以及一时序控制器。栅极控制器耦接移位暂存电路且用以输出控制信号给移位暂存电路。时序控制器耦接栅极控制器且用以控制栅极控制器。

5.在一些实施例中,栅极控制器还用以输出一栅极时脉信号给移位暂存电路,且栅极时脉信号于一异常时间点后包含一致能位准以及一禁能位准。

6.在一些实施例中,栅极控制器还用以输出一栅极时脉信号给移位暂存电路,且栅极时脉信号于一异常时间点后为一禁能位准。

7.在一些实施例中,驱动电路还包含一传输接口以及一源极控制器。传输接口耦接处理电路且用以接收来自处理电路的一影像数据。源极控制器耦接显示阵列且用以依据影像数据输出一数据信号至显示阵列。

8.在一些实施例中,控制信号于第一显示周期与一第二帧的一第二显示周期之间包含一禁能位准,以控制移位暂存电路停止运作。

9.在一些实施例中,驱动电路还用以控制移位暂存电路于第二显示周期重新正常运作。

10.本揭示的一些实施方式是关于一种驱动晶片。驱动晶片包含一驱动电路以及一第一脚位。驱动电路用以侦测驱动电路与一显示面板中的一处理电路之间的一数据传输是否为异常。驱动电路用以透过第一脚位输出一控制信号给显示面板中的一移位暂存电路。当数据传输于一第一帧的一第一显示周期内为异常时,控制信号于第一显示周期内包含一禁能位准以控制移位暂存电路停止运作。

11.在一些实施例中,驱动电路包含一栅极控制器以及一时序控制器。栅极控制器耦

接移位暂存电路且用以透过第一脚位输出控制信号给移位暂存电路。时序控制器耦接栅极控制器且用以控制栅极控制器。

12.在一些实施例中,驱动晶片还包含一第二脚位。栅极控制器还用以透过第二脚位输出一栅极时脉信号给移位暂存电路,且栅极时脉信号于一异常时间点后包含一致能位准以及一禁能位准。

13.在一些实施例中,驱动晶片还包含一第二脚位。栅极控制器还用以透过第二脚位输出一栅极时脉信号给移位暂存电路,且栅极时脉信号于一异常时间点后为一禁能位准。

14.在一些实施例中,驱动电路还包含一传输接口以及一源极控制器。传输接口用以接收来自处理电路的一影像数据。源极控制器用以依据影像数据输出一数据信号至显示面板。

15.在一些实施例中,控制信号于第一显示周期与一第二帧的一第二显示周期之间包含一禁能位准,以控制移位暂存电路停止运作。

16.在一些实施例中,驱动电路还用以控制移位暂存电路于第二显示周期重新正常运作。

附图说明

17.为让本揭示的上述和其他目的、特征、优点与实施例能够更明显易懂,所附附图的说明如下:

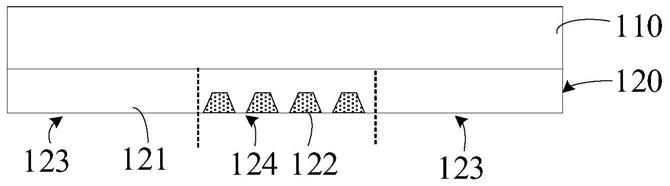

18.图1a是依照本揭示一些实施例所绘示的一显示装置的示意图;

19.图1b是依照本揭示一些实施例所绘示的一驱动晶片的示意图;

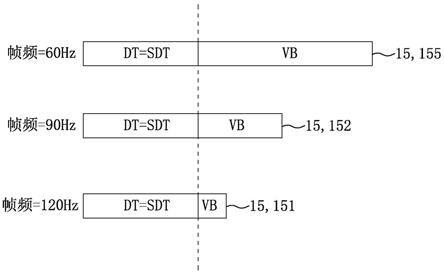

20.图2是依照本揭示一些实施例所绘示的一显示装置的多个信号的时序图;

21.图3是依照本揭示一些实施例所绘示的一显示装置的多个信号的时序图;

22.图4是依照本揭示一些实施例所绘示的一显示装置的多个信号的时序图;以及

23.图5是依照本揭示一些实施例所绘示的一显示方法的流程图。

24.【符号说明】

25.100:显示装置

26.120:处理电路

27.140:驱动电路

28.141:传输接口

29.142:数据路径

30.143:源极控制器

31.144:栅极控制器

32.145:时序控制器

33.160:显示面板

34.161:显示阵列

35.162:移位暂存电路

36.500:显示方法

37.c:驱动晶片

38.p1,p2,p3:脚位

39.sdata,sdataa,sdatab,sdatac:影像数据

40.vd,vd1

‑

vd13,vd1a,vd1b,vd1c:数据信号

41.vg,vg1

‑

vg16:栅极信号

42.stv,stva,stvb,stvc:起始信号

43.gck,gck1a,gck2a,gck3a,gck4a,gck1b,gck2b,gck3b,gck4b,gck1c,gck2c,gck3c,gck4c:栅极时脉信号

44.clr,clra,clrb,clrc:控制信号

45.img:影像

46.t1a,t2a,t3a,t4a,t5a,t6a,t7b,t6c,t7c:时间点

47.d1a

‑

d16a,d1b

‑

d16b,d1c

‑

d16c:数据

48.f1a,f1b,f1c:帧

49.s510,s520:操作

具体实施方式

50.在本文中所使用的用词“耦接”亦可指“电性耦接”,且用词“连接”亦可指“电性连接”。“耦接”及“连接”亦可指二个或多个元件相互配合或相互互动。

51.参考图1a。图1a是依照本揭示一些实施例所绘示的显示装置100的示意图。在一些实施例中,显示装置100可被应用于电视、计算机、手机、穿戴式装置上,但本揭示不以此些电子设备为限。

52.以图1a示例而言,显示装置100包含处理电路120、驱动电路140以及显示面板160。处理电路120耦接驱动电路140。驱动电路140耦接显示面板160。

53.处理电路120可透过驱动电路140控制显示面板160显示出对应的影像img。在一些实施例中,处理电路120是以应用处理器(application processor)实现,但本揭示不以此为限。

54.驱动电路140包含传输接口141、数据路径142、源极控制器143、栅极控制器144以及时序控制器(timing controller,tcon)145。传输接口141耦接处理电路120、数据路径142以及时序控制器145。数据路径142耦接源极控制器143。时序控制器145耦接源极控制器143以及栅极控制器144。

55.显示面板160包含显示阵列161以及移位暂存电路162。显示阵列161包含多个子像素。源极控制器143透过多条数据线耦接显示阵列161,其中各数据线耦接显示阵列161中的其中一列子像素。移位暂存电路162透过多条扫描线耦接显示阵列161,其中各扫描线耦接显示阵列161中的其中一行子像素。栅极控制器144耦接移位暂存电路162。

56.在运作上,处理电路120可依据一传输规范将影像数据sdata传输给传输接口141。在一些实施例中,传输接口141为移动产业处理器接口(mobile industry processor interface,mipi)。在这些实施例中,处理电路120可透过移动产业处理器接口的传输规范将影像数据sdata传输给传输接口141。

57.需特别说明的是,本揭示并不以上述的移动产业处理器接口以及传输规范为限,其他各种适用的接口以及传输规范皆在本揭示的范围中。

58.当传输接口141接收到来自处理电路120的影像数据sdata后,传输接口141可透过

数据路径142将影像数据sdata输出给源极控制器143,且将影像数据sdata输出给时序控制器145。时序控制器145则可依据接收到的影像数据sdata控制源极控制器143以及栅极控制器144。

59.举例而言,时序控制器145可控制栅极控制器144输出起始信号stv、一个或多个栅极时脉信号gck(图1a中是以多个栅极时脉信号gck为例)以及控制信号clr给移位暂存电路162。起始信号stv可用以启动移位暂存电路162。一般而言,移位暂存电路162中包含多级移位暂存器。这些移位暂存器会依据栅极时脉信号gck逐级运作以分别产生多个栅极信号vg。这些栅极信号vg可透过移位暂存电路162与显示阵列161之间的这些扫描线输出给显示阵列161。以图1a示例而言,若移位暂存电路162与显示阵列161之间具有16条扫描线,移位暂存电路162所产生的这些栅极信号vg包含栅极信号vg1

‑

vg16,其中栅极信号vg1可透过第一条扫描线输出给第一行子像素,栅极信号vg2可透过第二条扫描线输出给第二行子像素,以此类推。

60.另一方面,时序控制器145可控制源极控制器143依据影像数据sdata输出一个或多个数据信号vd(图1a中是以多个数据信号vd为例)。这些数据信号vd可透过源极控制器143与显示阵列161之间的这些数据线输出给显示阵列161。以图1a示例而言,若源极控制器143与显示阵列161之间具有13条数据线,源极控制器143所产生的这些数据信号vd包含数据信号vd1

‑

vd13,其中数据信号vd1可透过第一条数据线输出给第一列子像素,数据信号vd2可透过第二条数据线输出给第二列子像素,以此类推。

61.接着,显示阵列161可依据这些栅极信号vg以及这些数据信号vd显示出对应的影像img。举例而言,显示阵列161中的各子像素分别对应于一驱动晶体管。各子像素的驱动晶体管可依据一对应的栅极信号vg导通。接着,此子像素(例如但不限于液晶电容)可依据一对应的数据信号vd被充电至对应的电压位准,进而使此子像素显示出对应的灰阶。基于相似的运作原理,显示面板161中的所有子像素可协同运作以显示出影像img。

62.然而,当显示面板160上发生干扰或静电放电(electrostatic discharge,esd)事件时,处理电路120与驱动电路140之间的数据传输将会为异常。驱动电路140可用以侦测处理电路120与驱动电路140之间的数据传输是否异常。当驱动电路140侦测到处理电路120与驱动电路140之间的数据传输为异常时,驱动电路140可输出包含禁能位准的控制信号clr给移位暂存电路162,以控制移位暂存电路162停止运作。当移位暂存电路162停止运作,显示阵列161上的影像img将不再更新。

63.参考图1a以及图1b。图1b是依照本揭示一些实施例所绘示的驱动晶片c的示意图。驱动晶片c包含图1a中的驱动电路140且包含脚位p1

‑

p3。驱动电路140的栅极控制器144可透过脚位p1输出起始信号stv,透过脚位p2输出栅极时脉信号gck,且透过脚位p3输出控制信号clr。

64.于次特别说明的是,驱动晶片c可包含更多脚位,以输出其他信号(例如:图1a中的这些数据信号vd)。

65.参考图1a以及图2。图2是依照本揭示一些实施例所绘示的显示装置100的多个信号的时序图。

66.为了易于了解,图2中仅绘示出第一条数据线上的数据信号vd1a(对应影像数据sdataa),而省略了其他条数据线上的数据信号。据此,下面段落仅针对耦接第一条数据线

的第一列子像素描述。

67.以图2示例而言,数据信号vd1a于帧f1a的显示周期内包含数据d1a至d16a。

68.于时间点t1a,起始信号stva从禁能位准转为具有致能位准。起始信号stva的禁能位准例如为逻辑值0,起始信号stva的致能位准例如为逻辑值1,但本揭示不以此为限。如前所述,具有致能位准的起始信号stva可用以启动移位暂存电路162。

69.于时间点t2a,栅极时脉信号gck1a从禁能位准转为具有致能位准。栅极时脉信号gck1a的禁能位准例如为逻辑值0,栅极时脉信号gck1a的致能位准例如为逻辑值1,但本揭示不以此为限。当栅极时脉信号gck1a具有致能位准,移位暂存电路162中的第一级移位暂存器可依据栅极时脉信号gck1a输出具有致能位准的栅极信号vg1给第一条扫描线,以控制第一行子像素的这些驱动晶体管导通。而源极控制器143可于时间点t3a依据数据d1a对第一列子像素的驱动晶体管充电。据此,位于第一列上且位于第一行的该子像素将可显示出对应于数据d1a的灰阶。

70.相似地,于时间点t3a,栅极时脉信号gck2a从禁能位准转为具有致能位准。栅极时脉信号gck2a的禁能位准例如为逻辑值0,栅极时脉信号gck2a的致能位准例如为逻辑值1,但本揭示亦不以此为限。当栅极时脉信号gck2a具有致能位准,移位暂存电路162中的第二级移位暂存器可依据栅极时脉信号gck2a输出具有致能位准的栅极信号vg2给第二条扫描线,以控制第二行子像素的驱动晶体管导通。而源极控制器143可于时间点t4a依据数据d2a对第一列子像素的驱动晶体管充电。据此,位于第一列上且位于第二行的该子像素将可显示出对应于数据d2a的灰阶。

71.接着,栅极时脉信号gck3a以及栅极时脉信号gck4a依序具有致能位准。基于相似的运作原理,位于第一列上且位于第三行的该子像素将可显示出对应于数据d3a的灰阶,而位于第一列上且位于第四行的该子像素将可显示出对应于数据d4a的灰阶。

72.于时间点t5a,栅极时脉信号gck1a再次具有致能位准。在这个情况下,移位暂存电路162中的第五级移位暂存器可依据栅极时脉信号gck1a输出具有致能位准的栅极信号给第五条扫描线,以控制第五行子像素的驱动晶体管导通。基于相似的运作原理,位于第一列上且位于第五行的该子像素将可显示出对应于数据d5a的灰阶。

73.接着,栅极时脉信号gck2a以及栅极时脉信号gck3a依序再次具有致能位准。基于相似的运作原理,位于第一列上且位于第六行的该子像素将可显示出对应于数据d6a的灰阶,而位于第一列上且位于第七行的该子像素将可显示出对应于数据d7a的灰阶。

74.然而,若显示面板160于异常时间点t6a点发生干扰或静电放电事件,处理电路120与驱动电路140之间的数据传输将会为异常。以图2示例而言,由于显示面板160于帧f1a的显示周期内为异常,因此驱动电路140会于帧f1a的显示周期内输出包含禁能位准的控制信号clra给移位暂存电路162,以控制移位暂存电路162停止运作。控制信号clra的禁能位准例如为逻辑值1,但本揭示不以此为限。当移位暂存电路162停止运作,这些栅极信号vg将无法导通这些子像素的驱动晶体管。据此,显示阵列161上的影像img将会停止更新。由于影像img停止更新,因此可避免显示阵列161显示出错误的影像。

75.在图2中,栅极时脉信号gck1a

‑

gck4a于异常时间点t6a后皆正常运作。换句话说,各栅极时脉信号gck1a

‑

gck4a于异常时间点t6a后仍包含致能位准以及禁能位准。然而,由于移位暂存电路162已停止运作,故显示阵列161上的影像img于异常时间点t6a后仍停止更

新。

76.参考图1a以及图3。图3是依照本揭示一些实施例所绘示的显示装置100的多个信号的时序图。

77.图3中的影像数据sdatab相似于图2中的影像数据sdataa。图3中的栅极时脉信号gck1b

‑

gck4b相似于图2中的栅极时脉信号gck1a

‑

gck4a。图3中的数据信号vd1b相似于图2中的数据信号vd1a。图3中的数据d1b

‑

d16b(包含于帧f1b的显示周期内)相似于图2中的数据d1a

‑

d16a(包含于帧f1a的显示周期内)。

78.图3与图2之间的主要差异在于,图3中的控制信号clrb于帧f1b的显示周期与下一帧的显示周期之间包含禁能位准。相似于图2中的控制信号clra,图3中的控制信号clrb的禁能位准例如为逻辑值1,控制信号clrb的致能位准例如为逻辑值0,但本揭示不以此为限。以图3示例而言,控制信号clrb于时间点t7b从致能位准转为具有禁能位准。据此,可在两相邻帧的显示周期之间控制移位暂存电路162停止运作。接着,当进入下一帧的显示周期,起始信号stvb可再次具有致能位准,以控制移位暂存电路162重新正常运作。

79.参考图1a以及图4。图4是依照本揭示一些实施例所绘示的显示装置100的多个信号的时序图。

80.图4中的影像数据sdatac相似于图3中的影像数据sdatab。图4中的控制信号clrc相似于图3中的控制信号clrb。图4中的数据信号vd1c相似于图2中的数据信号vd1b。图4中的数据d1c

‑

d16c(包含于帧f1c的显示周期内)相似于图3中的数据d1b

‑

d16b(包含于帧f1b的显示周期内)。

81.图4与图3之间的主要差异在于,图4中的栅极时脉信号gck1c

‑

gck3c于异常时间点t6c后具有禁能位准(例如为逻辑值0),而栅极时脉信号gck1_4在恢复为禁能位准后则保持为禁能位准。

82.而相似于图3,图4中的控制信号clrc于帧f1c的显示周期与下一帧的显示周期之间包含禁能位准(例如为逻辑值1)。以图4示例而言,控制信号clrc于时间点t7c从致能位准转为具有禁能位准。据此,可在两相邻帧的显示周期之间控制移位暂存电路162停止运作。接着,当进入下一帧的显示周期,起始信号stvc可再次具有致能位准,以控制移位暂存电路162重新正常运作。

83.再次参考图1a。在一些其他的实施例中,移位暂存电路162可由两组多级移位暂存器实现。其中一组设置于显示阵列161的一侧(例如:图面上的右侧),而另一组设置于显示阵列161的另一侧(例如:图面上的左侧),以实现双驱动的架构。

84.参考图5。图5是依照本揭示一些实施例所绘示的显示方法500的流程图。在一些实施例中,显示方法500被应用于图1a的显示装置100。以图5示例而言,显示方法500包含操作s510以及s520。显示方法500将于以下段落搭配图1a进行描述。

85.在操作s510中,通过驱动电路140侦测处理电路120与驱动电路140之间的数据传输是否为异常。

86.在操作s520中,当驱动电路140侦测到处理电路120与驱动电路140之间的数据传输为异常时,通过驱动电路140输出包含禁能位准的控制信号clr给移位暂存电路162。据此,移位暂存电路162将会停止运作且使得显示阵列161上的影像img不再更新。

87.综上所述,本揭示中,驱动电路可于数据传输为异常时控制移位暂存电路停止运

作且使得显示面板上的影像停止更新。

88.虽然本揭示已以实施方式揭示如上,然其并非用以限定本揭示,任何本领域具通常知识者,在不脱离本揭示的精神和范围内,当可作各种的更动与润饰,因此本揭示的保护范围当视所附的权利要求书所界定的范围为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。