pcie扩展电路及扩展卡

技术领域

1.本实用新型涉及板卡设计技术领域,尤其涉及一种pcie(peripheral component interconnect express,高速串行计算机扩展总线标准)扩展电路及扩展卡。

背景技术:

2.基于网络安全行业对数据信息安全的重视,对于网闸的整机方案,在实际应用中存在的问题为:整机网口数量少,或者整机没有可扩展的高速率传输接口。

技术实现要素:

3.基于此,有必要针对上述问题,提出了一种pcie扩展电路及扩展卡,本实用新型目的是通过在pcie扩展电路中设置驱动芯片模块和时钟缓冲器芯片模块,并通过驱动芯片模块和时钟缓冲器芯片模块将主板的pcie接口发送的一路pcie控制信号和一路时钟信号分别分为两路pcie控制信号和两路时钟信号并分别发送给第一连接器和第二连接器,进而实现了对输入pcie扩展电路中的pcie控制信号和时钟信号进行扩展的目的,最终达到了对主板的pcie接口进行扩展的效果。

4.在第一方面,本技术提供了一种pcie扩展电路,所述pcie扩展电路包括:驱动芯片模块、时钟缓冲器芯片模块、第一连接器和第二连接器;

5.所述第一连接器和所述第二连接器均与所述驱动芯片模块电连接;

6.所述第一连接器和所述第二连接器均与所述时钟缓冲器芯片模块电连接;

7.其中,所述驱动芯片模块还与主板的pcie接口电连接,用于接收所述pcie接口传输的pcie控制信号,将所述pcie控制信号分成第一pcie控制信号和第二pcie控制信号,将所述第一pcie控制信号发送给所述第一连接器并将所述第二pcie控制信号发送给所述第二连接器;

8.其中,所述时钟缓冲器芯片模块还与所述pcie接口电连接,用于接收所述pcie接口传输的时钟信号,将所述时钟信号分成第一时钟信号和第二时钟信号,将所述第一时钟信号发送给所述第一连接器并将所述第二时钟信号发送给所述第二连接器。

9.在其中一种实施例中,所述驱动芯片模块包括:驱动芯片,所述驱动芯片用于增强所述pcie控制信号的驱动能力;所述驱动芯片包括第一输入接口、第一输出接口、第二输出接口、第二输入接口、第三输入接口和第三输出接口;

10.所述第一输入接口和所述第三输出接口均与所述pcie接口电连接;

11.所述第一输出接口和所述第二输入接口均与所述第一连接器电连接;

12.所述第二输出接口和所述第三输入接口均与所述第二连接器电连接。

13.在其中一种实施例中,所述驱动芯片模块还包括:第一滤波电路;

14.所述第一滤波电路的第一端与所述驱动芯片电连接,所述第一滤波电路的第二端为第一预设电压输入端。

15.在其中一种实施例中,所述驱动芯片模块还包括:第二滤波电路、第三滤波电路、

第四滤波电路和第五滤波电路;

16.所述第二滤波电路的一端与所述第一输出接口电连接,所述第二滤波电路的另一端与所述第一连接器电连接;

17.所述第三滤波电路的一端与所述第二输出接口电连接,所述第三滤波电路的另一端与所述第二连接器电连接;

18.所述第四滤波电路的一端与所述第二输入接口电连接,所述第四滤波电路的另一端与所述第一连接器电连接;

19.所述第五滤波电路的一端与所述第三输入接口电连接,所述第五滤波电路的另一端与所述第二连接器电连接。

20.在其中一种实施例中,所述时钟缓冲器芯片模块包括:时钟缓冲器芯片,所述时钟缓冲器芯片用于增强所述时钟信号的驱动能力;所述时钟缓冲器芯片包括:第四输入接口、第四输出接口和第五输出接口;

21.所述第四输入接口与所述pcie接口电连接;

22.所述第四输出接口与所述第一连接器电连接;

23.所述第五输出接口与所述第二连接器电连接。

24.在其中一种实施例中,所述时钟缓冲器芯片模块还包括:第六滤波电路;

25.所述第六滤波电路的第一端与所述时钟缓冲器芯片电连接,所述第六滤波电路的第二端为第二预设电压输入端。

26.在其中一种实施例中,所述时钟缓冲器芯片模块还包括:第一匹配电阻电路、第二匹配电阻电路和第三匹配电阻电路;

27.所述第一匹配电阻电路的一端与所述第四输入接口电连接,所述第一匹配电阻电路的另一端与所述pcie接口电连接;

28.所述第二匹配电阻电路的一端与所述第四输出接口电连接,所述第二匹配电阻电路的另一端与所述第一连接器电连接;

29.所述第三匹配电阻电路的一端与所述第五输出接口电连接,所述第三匹配电阻电路的另一端与所述第二连接器电连接。

30.在其中一种实施例中,所述pcie扩展电路还包括:第一金手指接口和第二金手指接口;

31.所述驱动芯片模块、所述第一金手指接口和所述pcie接口依次电连接;

32.所述时钟缓冲器芯片模块、所述第二金手指接口和所述pcie接口依次电连接。

33.在其中一种实施例中,所述第一连接器与第一外部设备卡电连接,所述第二连接器与第二外部设备卡电连接。

34.在第二方面,本技术提供了一种pcie扩展卡,所述pcie扩展卡包括如上所述实施例中任意一种所述pcie扩展电路,并且所述pcie扩展卡为l形。

35.采用本实用新型实施例,具有如下有益效果:

36.采用本实用新型的一种pcie扩展电路及扩展卡,通过在pcie扩展电路中设置驱动芯片模块,实现了将输入到pcie扩展电路中的pcie控制信号分成两路pcie控制信号并分别输出到第一连接器和第二连接器的目的,进而达到了对主板的pcie接口发送到pcie扩展电路中的pcie控制信号进行扩展的效果;通过在pcie扩展电路中设置时钟缓冲器芯片模块,

实现了将输入到pcie扩展电路中的时钟信号分成两路时钟信号并分别输出到第一连接器和第二连接器的目的,进而达到了对主板的pcie接口发送到pcie扩展电路中的时钟信号进行扩展的效果。最终达到了对主板的pcie接口进行扩展的效果。

附图说明

37.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

38.其中:

39.图1为本技术实施例中pcie扩展电路的结构框图;

40.图2为本技术实施例中pcie扩展电路的另一结构框图;

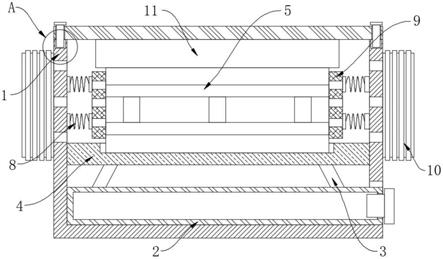

41.图3为本技术实施例中驱动芯片模块的电路图;

42.图4为本技术实施例中时钟缓冲器芯片模块的电路图。

具体实施方式

43.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

44.请参阅图1,为本技术实施例中pcie扩展电路的结构框图,该pcie扩展电路包括:驱动芯片模块101、时钟缓冲器芯片模块102、第一连接器103和第二连接器104;第一连接器103和第二连接器104均与驱动芯片模块101电连接;第一连接器103和第二连接器104均与时钟缓冲器芯片模块102电连接;其中,驱动芯片模块101还与主板105的pcie接口106电连接,用于接收pcie接口106传输的pcie控制信号,将pcie控制信号分成第一pcie控制信号和第二pcie控制信号,将第一pcie控制信号发送给第一连接器103并将第二pcie控制信号发送给第二连接器104;其中,时钟缓冲器芯片模块102还与pcie接口106电连接,用于接收pcie接口106传输的时钟信号,将时钟信号分成第一时钟信号和第二时钟信号,将第一时钟信号发送给第一连接器103并将第二时钟信号发送给第二连接器104。

45.在本技术实施例中,pcie是一种高速串行计算机扩展总线标准,它原来的名称为“3gio”,是由英特尔在2001年提出的,旨在替代旧的pci,pci

‑

x和agp总线标准。pcie属于高速串行点对点双通道高带宽传输,所连接的设备分配独享通道带宽,不共享总线带宽,主要支持主动电源管理,错误报告,端对端的可靠性传输,热插拔以及服务质量(qos)等功能。pcie接口有很多规格,具体包括:x1带宽模式、x4带宽模式、x8带宽模式以及x16带宽模式等,不同规格的pcie接口的1到11对引脚都是一样的,剩下的引脚分别为pcie控制信号线和时钟信号线,并且该pcie控制信号和时钟信号均为高速差分信号。

46.在一种可行的实现方式中,本技术中的主板105的pcie接口106为x8带宽模式,驱动芯片模块101与pcie接口106中的pcie控制信号线电连接,用于接收pcie接口106传输的x8带宽模式的pcie控制信号,驱动芯片模块101在接收到x8带宽模式的pcie控制信号之后,

通过驱动芯片模块101对pcie控制信号输出接口的重新分配,会将接收到的x8带宽模式的pcie控制信号分成两路pcie控制信号,一路为第一pcie控制信号,另一路为第二pcie控制信号,而第一pcie控制信号和第二pcie控制信号均为x4带宽模式的pcie控制信号,驱动芯片模块101会将第一pcie控制信号对应的x4带宽模式的pcie控制信号发送给第一连接器103,将第二pcie控制信号对应的x4带宽模式的pcie控制信号发送给第二连接器104。

47.同时,时钟缓冲器芯片模块102与pcie接口106中的时钟信号线电连接,用于接收pcie接口106传输的时钟信号,时钟缓冲器芯片模块102接收到时钟信号之后,会对时钟信号进行扩展,将接收到的时钟信号扩展成两路时钟信号,一路为第一时钟信号,另一路为第二时钟信号,时钟缓冲器芯片模块102会将第一时钟信号发送给第一连接器103,将第二时钟信号发送给第二连接器104。

48.可以理解的是,第一连接器103能够接收到x4带宽模式的pcie控制信号和时钟信号,第二连接器104也能够接收到x4带宽模式的pcie控制信号和时钟信号,因此第一连接器103和第二连接器104均相当于x4带宽模式的pcie接口的功能。

49.具体的,在本技术实施例中,第一连接器103为pcie连接器或者欧式连接器,第二连接器104为minipcie连接器。

50.需要说明的是,上述仅为本技术实施例中的一种可行的实现方式,对于主板105的pcie接口106的带宽模式以及第一连接器103和第二连接器104的具体类型,此处不做限定。

51.在本技术实施例中,通过在pcie扩展电路中设置驱动芯片模块101,实现了将输入到pcie扩展电路中的pcie控制信号分成两路pcie控制信号并分别输出到第一连接器103和第二连接器104的目的,进而达到了对主板105的pcie接口106发送到pcie扩展电路中的pcie控制信号进行扩展的效果;通过在pcie扩展电路中设置时钟缓冲器芯片模块102,实现了将输入到pcie扩展电路中的时钟信号分成两路时钟信号并分别输出到第一连接器103和第二连接器104的目的,进而达到了对主板105的pcie接口106发送到pcie扩展电路中的时钟信号进行扩展的效果。最终达到了对主板105的pcie接口106进行扩展的效果。

52.请参阅图2,为本技术实施例中pcie扩展电路的另一结构框图,该驱动芯片模块101包括:驱动芯片201,驱动芯片201用于增强pcie控制信号的驱动能力;驱动芯片201包括第一输入接口202、第一输出接口203、第二输出接口204、第二输入接口205、第三输入接口206和第三输出接口207;第一输入接口202和第三输出接口207均与pcie接口106电连接;第一输出接口203和第二输入接口205均与第一连接器103电连接;第二输出接口204和第三输入接口206均与第二连接器104电连接。

53.具体的,请参阅图3,为本技术实施例中驱动芯片模块的电路图,驱动芯片201为驱动芯片u2,该驱动芯片u2采用的是型号为ds80pci800sqf的ti(texas instruments)驱动芯片,该驱动芯片能够增强pcie控制信号的驱动能力。其中,第一输入接口202具体包括驱动芯片u2中的ib_0 接口、ib_0

‑

接口、ib_1 接口、ib_1

‑

接口、ib_2 接口、ib_2

‑

接口、ib_3 接口和ib_3

‑

接口,上述驱动芯片u2中的信号输入接口作为第一输入接口202与pcie接口106中的pcie控制信号线电连接,用于接收pcie接口106发送的pcie控制信号,驱动芯片u2对接收到的pcie控制信号执行增强驱动能力的操作;第一输出接口203具体包括驱动芯片u2中的ob_0 接口、ob_0

‑

接口、ob_1 接口和ob_1

‑

接口,驱动芯片u2将增强后的pcie接口106发送的pcie控制信号分成两路pcie控制信号,并将其中一路pcie控制信号对应的第一pcie控

制信号发送到上述驱动芯片u2中的信号输出接口,并将第一pcie控制信号发送到与上述驱动芯片u2中的信号输出接口电连接的第一连接器103;第二输出接口204具体包括驱动芯片u2中的ob_2 接口、ob_2

‑

接口、ob_3 接口和ob_3

‑

接口,驱动芯片u2将另一路pcie控制信号对应的第二pcie控制信号发送到上述驱动芯片u2中的信号输出接口,并将第二pcie控制信号发送到与上述驱动芯片u2中的信号输出接口电连接的第二连接器104。

54.其中,具体的,第二输入接口205具体包括驱动芯片u2中的oa_0 接口、oa_0

‑

接口、oa_1 接口和oa_1

‑

接口,驱动芯片u2通过上述信号输入接口接收第一连接器103反馈的pcie控制信号;第三输入接口206具体包括驱动芯片u2中的oa_2 接口、oa_2

‑

接口、oa_3 接口和oa_3

‑

接口,驱动芯片u2通过上述信号输入接口接收第二连接器104反馈的pcie控制信号;第三输出接口207具体包括驱动芯片u2中的ia_0 接口、ia_0

‑

接口、ia_1 接口、ia_1

‑

接口、ia_2 接口、ia_2

‑

接口、ia_3 接口和ia_3

‑

接口,驱动芯片u2将通过第二输入接口205和第三输入接口206接收到的第一连接器103和第二连接器104反馈的pcie控制信号执行增强驱动能力的操作后发送给第三输出接口207,进而第三输出接口207能够将第一连接器103和第二连接器104反馈的增强后的pcie控制信号发送给与其电连接的pcie接口106,达到了将第一连接器103和第二连接器104反馈的pcie控制信号进行驱动能力增强并发送给主板105的效果。

55.在本技术实施例中,通过在pcie扩展电路中设置包括驱动芯片201的驱动芯片模块101,驱动芯片201实现了增强主板105的pcie接口106发送的pcie控制信号的驱动能力的目的,同时驱动芯片201还能够对接收到的主板105的pcie接口106发送的pcie控制信号进行扩展,实现了对主板105的pcie接口106进行扩展的目的。并且驱动芯片201还实现了增强反馈给主板105的pcie控制信号的驱动能力的目的,进而增强了主板105通过pcie接口106进行通讯时pcie控制信号的驱动能力。

56.需要说明的是,上述实施例仅为一种驱动芯片201可行的实现方式,此处不做限定。

57.请参阅图3,为本技术实施例中驱动芯片模块的电路图,驱动芯片模块101还包括:第一滤波电路301;第一滤波电路301的第一端与驱动芯片201电连接,第一滤波电路301的第二端为第一预设电压输入端p3v3。

58.具体的,驱动芯片201为驱动芯片u2,第一滤波电路301包括:电容c34和电容c35,电容c34的一端同时与电容c35的一端和驱动芯片u2电连接,电容c34的一端还为第一预设电压输入端p3v3;电容c34的另一端与电容c35的另一端电连接并接地。

59.在本技术实施例中,通过在驱动芯片201与第一预设电压输入端p3v3之间设置第一滤波电路301,实现了为驱动芯片201提供稳定的电源电压的目的。

60.需要说明的是,上述实施例仅为第一滤波电路301中的电容的数量和连接方式的一种情况,此处不做限定,在实际应用中,包括其他数量的电容以及这些电容的连接方式的具有滤波功能的滤波电路也属于本技术的保护范围。

61.请参阅图2,为本技术实施例中pcie扩展电路的另一结构框图,该驱动芯片模块101还包括:第二滤波电路208、第三滤波电路209、第四滤波电路210和第五滤波电路211;第二滤波电路208的一端与第一输出接口203电连接,第二滤波电路208的另一端与第一连接器103电连接;第三滤波电路209的一端与第二输出接口204电连接,第三滤波电路209的另

一端与第二连接器104电连接;第四滤波电路210的一端与第二输入接口205电连接,第四滤波电路210的另一端与第一连接器103电连接;第五滤波电路211的一端与第三输入接口206电连接,第五滤波电路211的另一端与第二连接器104电连接。

62.具体的,请参阅图3,为本技术实施例中驱动芯片模块的电路图,第二滤波电路208包括:电容c31、电容c30、电容c29和电容c28;电容c31的一端与ob_0 接口电连接,电容c31的另一端与第一连接器103电连接;电容c30的一端与ob_0

‑

接口电连接,电容c30的另一端与第一连接器103电连接;电容c29的一端与ob_1 接口电连接,电容c29的另一端与第一连接器103电连接;电容c28的一端与ob_1

‑

接口电连接,电容c28的另一端与第一连接器103电连接。

63.具体的,请参阅图3,为本技术实施例中驱动芯片模块的电路图,第三滤波电路209包括:电容c27、电容c26、电容c25和电容c24;电容c27的一端与ob_2 接口电连接,电容c27的另一端与第二连接器104电连接;电容c26的一端与ob_2

‑

接口电连接,电容c26的另一端与第二连接器104电连接;电容c25的一端与ob_3 接口电连接,电容c25的另一端与第二连接器104电连接;电容c24的一端与ob_3

‑

接口电连接,电容c24的另一端与第二连接器104电连接。

64.具体的,请参阅图3,为本技术实施例中驱动芯片模块的电路图,第四滤波电路210包括:电容c23、电容c22、电容c21和电容c20;电容c23的一端与oa_0 接口电连接,电容c23的另一端与第一连接器103电连接;电容c22的一端与oa_0

‑

接口电连接,电容c22的另一端与第一连接器103电连接;电容c21的一端与oa_1 接口电连接,电容c21的另一端与第一连接器103电连接;电容c20的一端与oa_1

‑

接口电连接,电容c20的另一端与第一连接器103电连接。

65.具体的,请参阅图3,为本技术实施例中驱动芯片模块的电路图,第五滤波电路211包括:电容c19、电容c18、电容c17和电容c16;电容c19的一端与oa_2 接口电连接,电容c19的另一端与第二连接器104电连接;电容c18的一端与oa_2

‑

接口电连接,电容c18的另一端与第二连接器104电连接;电容c17的一端与oa_3 接口电连接,电容c17的另一端与第二连接器104电连接;电容c16的一端与oa_3

‑

接口电连接,电容c16的另一端与第二连接器104电连接。

66.在本技术实施例中,通过在驱动芯片201的信号输入输出接口处设置第二滤波电路208、第三滤波电路209、第四滤波电路210和第五滤波电路211,达到了提高驱动芯片201输出到第一连接器103和第二连接器104的相应的pcie控制信号的品质的效果,同时也达到了提高驱动芯片201接收到的第一连接器103和第二连接器104反馈的相应的pcie控制信号的品质的效果。

67.需要说明的是,上述实施例仅为第二滤波电路208、第三滤波电路209、第四滤波电路210和第五滤波电路211中的电容的数量和连接方式的一种情况,此处不做限定,在实际应用中,包括其他数量的电容以及这些电容的连接方式的具有滤波功能的滤波电路也属于本技术的保护范围。

68.请参阅图2,为本技术实施例中pcie扩展电路的另一结构框图,时钟缓冲器芯片模块102包括:时钟缓冲器芯片212,时钟缓冲器芯片212用于增强时钟信号的驱动能力;时钟缓冲器芯片212包括:第四输入接口213、第四输出接口214和第五输出接口215;第四输入接

口213与pcie接口106电连接;第四输出接口214与第一连接器103电连接;第五输出接口215与第二连接器104电连接。

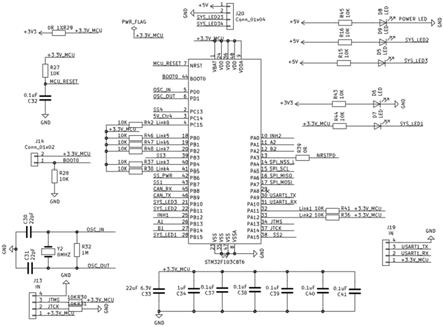

69.具体的,请参阅图4,为本技术实施例中时钟缓冲器芯片模块的电路图,时钟缓冲器芯片212为时钟缓冲器芯片u1,该时钟缓冲器芯片u1采用的是型号为cy28400

‑

2的时钟缓冲器芯片,该时钟缓冲器芯片能够增强时钟信号的驱动能力。其中,第四输入接口213具体包括时钟缓冲器芯片u1中的src_in接口和src_in#接口,上述时钟缓冲器芯片u1中的信号输入接口作为第四输入接口213与pcie接口106中的时钟信号线电连接,用于接收pcie接口106发送的时钟信号,时钟缓冲器芯片u1对接收到的时钟信号执行增强驱动能力的操作;第四输出接口214具体包括时钟缓冲器芯片u1中的dift1接口和difc1接口,时钟缓冲器芯片u1将增强后的pcie接口106发送的时钟信号分成两路时钟信号,并将其中一路时钟信号对应的第一时钟信号发送到上述时钟缓冲器芯片u1中的信号输出接口,并将第一时钟信号发送到与上述时钟缓冲器芯片u1中的信号输出接口电连接的第一连接器103;第五输出接口215具体包括时钟缓冲器芯片u1中的dift2接口和difc2接口,时钟缓冲器芯片u1将另一路时钟信号对应的第二时钟信号发送到上述时钟缓冲器芯片u1中的信号输出接口,并将第二时钟信号发送到与上述时钟缓冲器芯片u1中的信号输出接口电连接的第二连接器104。

70.在本技术实施例中,通过在pcie扩展电路中设置包括时钟缓冲器芯片212的时钟缓冲器芯片模块102,时钟缓冲器芯片212实现了增强主板105的pcie接口106发送的时钟信号的驱动能力的目的,同时时钟缓冲器芯片212还能够对接收到的主板105的pcie接口106发送的时钟信号进行扩展,实现了对主板105的pcie接口106进行扩展的目的。

71.需要说明的是,上述实施例仅为一种时钟缓冲器芯片212可行的实现方式,此处不做限定。

72.请参阅图4,为本技术实施例中时钟缓冲器芯片模块的电路图,时钟缓冲器芯片模块102还包括:第六滤波电路401;第六滤波电路401的第一端与时钟缓冲器芯片212电连接,第六滤波电路401的第二端为第二预设电压输入端vcc3_3。

73.具体的,时钟缓冲器芯片212为时钟缓冲器芯片u1,第六滤波电路401包括:电容c22、电容c23、电容c24、电容c25、电容c26、电容c27和电阻r31;电容c22的一端同时与电容c23的一端、电容c24的一端、电容c25的一端、电阻r31的一端和时钟缓冲器芯片u1电连接;电容c22的一端还为第二预设电压输入端vcc3_3;电容c22的另一端同时与电容c23的另一端、电容c24的另一端和电容c25的另一端电连接并接地;电阻r31的另一端同时与电容c26的一端、电容c27的一端和时钟缓冲器芯片u1电连接;电容c26的另一端与电容c27的另一端电连接并接地。

74.在本技术实施例中,通过在时钟缓冲器芯片212与第二预设电压输入端vcc3_3之间设置第六滤波电路401,实现了为时钟缓冲器芯片212提供稳定的电源电压的目的。

75.需要说明的是,上述实施例仅为第六滤波电路401中的电阻和电容的数量以及连接方式的一种情况,此处不做限定,在实际应用中,包括其他数量的电阻和电容以及这些电阻和电容的连接方式的具有滤波功能的滤波电路也属于本技术的保护范围。

76.请参阅图2,为本技术实施例中pcie扩展电路的另一结构框图,时钟缓冲器芯片模块102还包括:第一匹配电阻电路216、第二匹配电阻电路217和第三匹配电阻电路218;第一匹配电阻电路216的一端与第四输入接口213电连接,第一匹配电阻电路216的另一端与

pcie接口106电连接;第二匹配电阻电路217的一端与第四输出接口214电连接,第二匹配电阻电路217的另一端与第一连接器103电连接;第三匹配电阻电路218的一端与第五输出接口215电连接,第三匹配电阻电路218的另一端与第二连接器104电连接。

77.具体的,请参阅图4,为本技术实施例中时钟缓冲器芯片模块的电路图,第一匹配电阻电路216包括:电阻r42和电阻r43;电阻r42的一端与src_in接口电连接,电阻r42的另一端与pcie接口106的时钟信号线电连接;电阻r43的一端与src_in#接口电连接,电阻r43的另一端与pcie接口106的时钟信号线电连接。

78.具体的,请参阅图4,为本技术实施例中时钟缓冲器芯片模块的电路图,第二匹配电阻电路217包括:电阻r32、电阻r33、电阻r34、电阻r35、电阻r36和电阻r37;电阻r32的一端与dift1接口电连接,电阻r32的另一端同时与电阻r36的一端和电阻r33的一端电连接;电阻r33的另一端与第一连接器103电连接;电阻r36的另一端与电阻r37的一端电连接并接地;电阻r37的另一端同时与电阻r34的一端和电阻r35的一端电连接;电阻r34的另一端与difc1接口电连接;电阻r35的另一端与第一连接器103电连接。

79.具体的,请参阅图4,为本技术实施例中时钟缓冲器芯片模块的电路图,第三匹配电阻电路218包括:电阻r38、电阻r39、电阻r40、电阻r41、电阻r45和电阻r46;电阻r38的一端与dift2接口电连接,电阻r38的另一端同时与电阻r40的一端和电阻r39的一端电连接;电阻r39的另一端与第二连接器104电连接;电阻r40的另一端与电阻r41的一端电连接并接地;电阻r41的另一端同时与电阻r45的一端和电阻r46的一端电连接;电阻r45的另一端与difc2接口电连接;电阻r46的另一端与第二连接器104电连接。

80.在本技术实施例中,通过在时钟缓冲器芯片模块102的信号输入输出接口处设置第一匹配电阻电路216、第二匹配电阻电路217和第三匹配电阻电路218,达到了提高时钟缓冲器芯片模块102输出到第一连接器103和第二连接器104的相应的时钟信号的品质的效果。

81.需要说明的是,上述实施例仅为第一匹配电阻电路216、第二匹配电阻电路217和第三匹配电阻电路218中的电阻的数量和连接方式的一种情况,此处不做限定,在实际应用中,包括其他数量的电阻以及这些电阻的连接方式的匹配电阻电路也属于本技术的保护范围。

82.请参阅图2,为本技术实施例中pcie扩展电路的另一结构框图,pcie扩展电路还包括:第一金手指接口219和第二金手指接口220;驱动芯片模块101、第一金手指接口219和pcie接口106依次电连接;时钟缓冲器芯片模块102、第二金手指接口220和pcie接口106依次电连接。

83.在一种可行的实现方式中,第一连接器103与第一外部设备卡221电连接,第二连接器104与第二外部设备卡222电连接。

84.上述实施例仅为一种可行的实现方式,不对pcie扩展电路能够连接的外部设备卡的数量做限定。

85.在一种可行的实现方式中,本技术还提供了一种pcie扩展卡,该pcie扩展卡包括如图1至4中任意一种pcie扩展电路,并且该pcie扩展卡为l形。

86.在本技术实施例中,通过将具有pcie扩展电路的pcie扩展卡做成l形,使得pcie扩展卡在实现对主板105的pcie接口106进行扩展以及增强pcie控制信号和时钟信号的驱动

能力的同时,还通过特有的l形使得该pcie扩展卡在整机方案中进行使用时安装和拆除更加方便。

87.上述实施例仅为一种可行的实现方式,在实际应用中,还可以根据整机方案的具体情况将pcie扩展卡制作成其他形状,此处不做限定。

88.以上实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

89.以上所述实施例仅表达了本技术的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对本技术专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本技术构思的前提下,还可以做出若干变形和改进,这些都属于本技术的保护范围。因此,本技术专利的保护范围应以所附权利要求为准。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。