mbus主机发送电路和mbus总线系统

技术领域

1.本实用新型涉及数据通信领域,尤其涉及一种mbus主机发送电路和mbus总线系统。

背景技术:

2.mbus是一种主从式半双工传输总线,具有抗干扰能力强、传输距离远、施工简单、供电灵活等特点,被广泛的应用于各种计量仪表(如电表、水表、气表、热表)的抄读中。

3.mbus总线系统由一个主设备、若干从设备和一对连接线缆组成,所有从设备并行连接在总线上,由主设备控制总线上的所有串行通信进程。通常,主设备是一个智能控制器,从设备是各种计量仪表,主设备与从设备进行通信,获取从设备的测量数据。

4.目前,现有的mbus主机通信电路中,发送电路是通过dc

‑

dc升压电路将总线电压升至35v,而后通过控制ldo浮地电平方式实现的。这种电路由于光耦响应速度慢以及ldo本身的时延,容易产生通信速率无法提高和通信过程中存在一定的误码率等问题。

技术实现要素:

5.本实用新型的主要目的在于提供一种mbus主机发送电路和mbus总线系统,旨在解决通信速率缓慢的问题。

6.为了实现上述目的,本实用新型提供一种mbus主机发送电路,包括:光耦隔离模块、转换开关、升压芯片电路以及依次连接的第一电阻、第二电阻和第三电阻;所述光耦隔离模块的输入端与主机连接,所述光耦隔离模块的输出端与所述转换开关的控制端连接;所述转换开关的第一输出端和第二输出端对应连接所述第二电阻的两端,所述第二电阻和所述第三电阻的公共端与所述升压芯片电路的输出电压控制端连接,所述升压芯片电路的输入端与第一供电电源连接,所述升压芯片电路的输出端为mbus主机发送电路的信号输出端;

7.所述光耦隔离模块,用于接收所述主机发出的第一信号或第二信号,并向所述转换开关对应发送开启信号或关断信号;

8.所述转换开关,用于在接收到所述开启信号时,触发所述升压芯片电路输出所述第一电阻和第三电阻的总阻值对应的第一电平信号;

9.所述转换开关,还用于在接收到所述关断信号时,触发所述升压芯片电路输出所述第一电阻、第二电阻和第三电阻的总阻值对应的第二电平信号。

10.可选地,所述光耦隔离模块包括第四电阻及光耦,所述光耦的阳极经所述第四电阻与第二供电电源连接;所述光耦的阴极作为所述光耦隔离模块的输入端与所述主机连接;所述光耦的集电极与第三供电电源连接,所述光耦的发射极为所述光耦隔离模块的输出端。

11.可选地,所述转换开关包括mos管,所述mos管的栅极为所述转换开关的控制端,所述mos管的漏极和源极与所述转换开关的第一输出端和第二输出端。

12.可选地,所述转换开关还包括第五电阻,所述第五电阻连接在所述mos管的栅极和漏极之间。

13.可选地,所述mos管为pmos管。

14.可选地,所述升压芯片电路包括dc

‑

dc芯片、第六电阻、第七电阻、电感和第一二极管;所述dc

‑

dc芯片的输入引脚为所述升压芯片电路的输入端,所述dc

‑

dc芯片的反馈引脚为所述升压芯片电路的输出电压控制端;所述第六电阻的一端与所述第一供电电源连接,所述第六电阻的另一端与所述第七电阻的一端连接,所述第七电阻的另一端接地,所述dc

‑

dc芯片的使能引脚与所述第六电阻和第七电阻的公共端连接;所述电感的一端与所述dc

‑

dc芯片的输入引脚连接,所述电感的另一端与所述dc

‑

dc芯片的调整开关引脚和所述第一二极管的正极连接,所述第一二极管的负极为所述升压芯片电路的输出端

15.可选地,所述升压芯片电路还包括第一电容和第二电容,所述第一电容的一端与所述dc

‑

dc芯片的输入引脚连接,所述第二电容的一端与所述dc

‑

dc芯片的使能引脚连接,所述第一电容和所述第二电容的另一端都接地。

16.可选地,所述升压芯片电路还包括第三电容,所述第三电容的一端与所述第一二极管的负极连接,所述第三电容的另一端接地。

17.可选地,所述dc

‑

dc芯片频率高于1mhz,第三电容的电容值低于10μf。

18.此外,为实现上述目的,本实用新型还提供一种mbus总线系统,包括mbus主机、mbus从机和mbus总线,所述mbus主机包括mbus主机发送电路,所述mbus主机发送电路被配置为如上所述的mbus主机发送电路。

19.本实用新型提供的mbus主机发送电路和mbus总线系统,通过在mbus主机发送电路中设置转换开关和升压芯片电路,加快了所述光耦隔离模块对所述主机发出的信号的处理和传输,结合所述第一电阻、第二电阻和第三电阻组成的反馈电路加速了对升压芯片电路的反馈,提高了所述升压芯片电路发出电平信号的速度和通信波形上升、下降沿的变化速率,从而提高了通信速率,同时有效降低了通信误码率。进一步地,通过mbus主机发送电路的内部结构调整,再结合已有mbus主机发送电路,可以从整体上提高了mbus电路的收发速率。

附图说明

20.为了更清楚地说明本实用新型实施例或现有技术中的技术方案,下面将对实施例或现有技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本实用新型的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图示出的结构获得其他的附图。

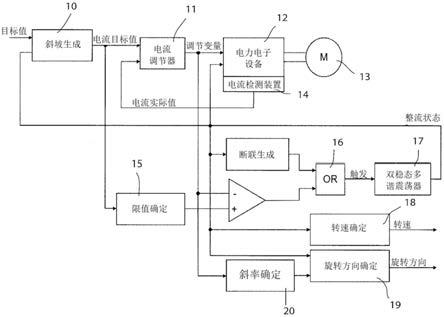

21.图1为本实用新型mbus主机发送电路一实施例的模块示意图;

22.图2为图1实施例的电路结构示意图。

23.本实用新型目的的实现、功能特点及优点将结合实施例,参照附图做进一步说明。

24.附图标号说明:

25.26.具体实施方式

27.应当理解,此处所描述的具体实施例仅仅用以解释本实用新型,并不用于限定本实用新型。

28.下面将结合本实用新型实施例中的附图,对本实用新型实施例中的技术方案进行清楚、完整地描述,显然,所描述的实施例仅仅是本实用新型的一部分实施例,而不是全部的实施例。基于本实用新型中的实施例,本领域普通技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本实用新型保护的范围。

29.需要说明,本实用新型实施例中所有方向性指示(诸如上、下、左、右、前、后

……

)仅用于解释在某一特定姿态(如附图所示)下各部件之间的相对位置关系、运动情况等,如果该特定姿态发生改变时,则该方向性指示也相应地随之改变。

30.另外,在本实用新型中涉及“第一”、“第二”等的描述仅用于描述目的,而不能理解为指示或暗示其相对重要性或者隐含指明所指示的技术特征的数量。由此,限定有“第一”、“第二”的特征可以明示或者隐含地包括至少一个该特征。另外,各个实施例之间的技术方案可以相互结合,但是必须是以本领域普通技术人员能够实现为基础,当技术方案的结合出现相互矛盾或无法实现时应当认为这种技术方案的结合不存在,也不在本实用新型要求的保护范围之内。

31.本实用新型提供一种mbus主机发送电路,通过对发送电路的内部结构调整,提高主机的信号发送速率,再结合mbus主机接收电路,整体上提高了mbus电路的收发速率。

32.需要说明的是,mbus物理层bit流传输具有独特的电平特征,如下表所示:

33.bitbit流的表示bit流传输方向逻辑“1”(mark)22v≤vmark≤42v主机到从机逻辑“0”(space)12v≤vspace≤vmark

‑

10v主机到从机

34.具体主机到从机的bit流传输通过总线电平切换方式实现,定义逻辑“1”(mark),逻辑“0”(space),主机向从机发送逻辑“1”时,总线电压为vmark(≤42v),发送逻辑“0”时,总线电压降到vspace(≥12v)。

35.可以理解的是,本实用新型所述mbus主机发送电路的输出即为vmark或vspace。

36.参见图1和图2,在一实施例中,所述mbus主机发送电路,包括:光耦隔离模块10、转换开关20、升压芯片电路30以及依次连接的第一电阻r1、第二电阻r2和第三电阻r3;所述光耦隔离模块10的输入端与主机连接,所述光耦隔离模块10的输出端与所述转换开关20的控制端连接;所述转换开关20的第一输出端和第二输出端对应连接所述第二电阻r2的两端,所述第二电阻r2和所述第三电阻r3的公共端与所述升压芯片电路30的输出电压控制端连接,所述升压芯片电路30的输入端与第一供电电源vcc1连接,所述升压芯片电路30的输出端为mbus主机发送电路的信号输出端;

37.所述光耦隔离模块10,用于接收所述主机发出的第一信号或第二信号,并向所述转换开关20对应发送开启信号或关断信号;

38.所述转换开关20,用于在接收到所述开启信号时,触发所述升压芯片电路30输出所述第一电阻r1和第三电阻r3的总阻值对应的第一电平信号;

39.所述转换开关20,还用于在接收到所述关断信号时,触发所述升压芯片电路30输出所述第一电阻r1、第二电阻r2和第三电阻r3的总阻值对应的第二电平信号。

40.其中,所述主机用于与作为mbus从机的水表、气表、热表等表进行通信,可以为智能电表等类似设备。

41.本实施例中,所述主机发出第一信号时,所述光耦隔离模块10接收并向所述转换开关20发送开启信号,所述转换开关20触发所述升压芯片电路30输出所述第一电阻r1和第三电阻r3的总阻值对应的第一电平信号;所述主机发出第二信号时,所述光耦隔离模块10接收并向所述转换开关20发送关断信号,所述转换开关20触发所述升压芯片电路30输出所述第一电阻r1、第二电阻r2和第三电阻r3的总阻值对应的第二电平信号。从而实现了mbus物理层bit流的传输。

42.可以理解的是,所述第一信号和第二信号分别是数字信号“0”和“1”。

43.优选的,第一电平信号和第二电平信号分别为22v和36v。

44.基于上述实施例,在进一步地实施例中,所述光耦隔离模块10包括第四电阻r4及光耦u1,所述光耦u1的阳极经所述第四电阻r4与第二供电电源vcc2连接;

45.所述光耦u1的阴极作为所述光耦隔离模块10的输入端与所述主机连接;所述光耦u1的集电极与第三供电电源vcc3连接,所述光耦u1的发射极为所述光耦隔离模块10的输出端。

46.光耦隔离模块10为本领域成熟的技术,作用在此不再赘述.

47.基于上述实施例,在进一步地实施例中,所述转换开关20包括mos管q1,所述mos管q1的栅极为所述转换开关20的控制端,所述mos管q1的漏极和源极与所述转换开关20的第一输出端和第二输出端。

48.上述转换开关20还包括第五电阻r5,所述第五电阻r5连接在所述mos管的栅极和漏极之间。

49.其中,所述转换开关20可以与所述光耦隔离模块构成光耦加速方案,原理如下:一

方面,所述mos管可以与光耦输出形成类达林顿电路,提高q1的打开速度;另一方面,光耦关断时r5迅速放电,提高了q1的关断速度。需要说明的是,此光耦加速方案的应用不限于mbus发送电路。

50.可选地,所述mos管为pmos管。

51.基于上述实施例,在进一步地实施例中,所述升压芯片电路包括dc

‑

dc芯片u2、第六电阻r6、第七电阻r7、电感l1和第一二极管d1;

52.所述dc

‑

dc芯片的输入引脚in为所述升压芯片电路30的输入端,所述dc

‑

dc芯片的反馈引脚fb为所述升压芯片电路30的输出电压控制端;所述第六电阻r6的一端与所述第一供电电源vcc1连接,所述第六电阻r6的另一端与所述第七电阻r7的一端连接,所述第七电阻r7的另一端接地,所述dc

‑

dc芯片的使能引脚en与所述第六电阻r6和第七电阻r7的公共端连接;所述电感l1的一端与所述dc

‑

dc芯片的输入引脚in连接,所述电感l1的另一端与所述dc

‑

dc芯片的调整开关引脚sw和所述第一二极管d1的正极连接,所述第一二极管d1的负极为所述升压芯片电路30的输出端

53.可以理解的是,所述dc

‑

dc芯片u2的反馈引脚fb有一个参考电压vref(比如0.6v),输出端电压vout的大小通过第三电阻r3的阻值与第一电阻r1和第二电阻r2的阻值之和的比值大小确定,本实施例的升压芯片电路40需要输出的电压为22v时,所述转换开关20开启,将第一电阻r1旁路,此时第二电阻r2和第三电阻r3构成反馈电阻网络,输出电压则将第三电阻r3和第二电阻r2的比值设为相应的值;升压芯片电路40需要输出的电压为36v时,所述转换开关20断开,此时第一电阻r1、第二电阻r2和第三电阻r3构成反馈电阻网络,输出电压将第三电阻r3的阻值与第一电阻r1和第二电阻r2的比值设为相应的值。

54.上述所述升压芯片电路还包括第一电容c1和第二电容c2,所述第一电容c1的一端与所述dc

‑

dc芯片的输入引脚in连接,所述第二电容c2的一端与所述dc

‑

dc芯片的使能引脚en连接,所述第一电容c1和所述第二电容c2的另一端都接地。

55.上述所述升压芯片电路还包括第三电容c3,所述第三电容c3的一端与所述第一二极管d1的负极连接,所述第三电容c3的另一端接地。

56.为了更好的实现电路效果,上述dc

‑

dc芯片u2最好选用频率高于1mhz,

57.第三电容c3最好选用电容值低于10μf的,以使36v到22v跌落尽量快。

58.参见图2,可以理解的是,所述mbus主机发送电路还包括信号输出电路40,所述输出电路40包括第八电阻r8、第二二极管d2、瞬态抑制二极管tvs、热敏电阻rt和mbus接口tb 10;

59.所述第八电阻r8的一端为所述输出电路40的输入端与所述升压芯片电路30的输出端连接,所述第八电阻r8的另一端与所述第二二极管d2的阳极连接,所述第二二极管d2的阴极通过所述热敏电阻rt1与所述mbus接口tb 10的一端连接,所述mbus接口tb 10的另一端接地,所述瞬态抑制二极管tvs的一端与所述第二二极管d2的阴极连接,所述瞬态抑制二极管tvs的另一端接地。

60.输出电路40为现有技术,在此不再赘述。

61.结合图1和图2,本实用新型的具体电路原理如下:

62.主机发出信号“0”时,光耦u1的输入端接收并导通,光耦的输出端导通,此时,pmos管q1的vgs大于开启电压,pmos管q1导通,并将第一电阻r1旁路,则第二电阻r2和第三电阻r3组成反馈电阻网络,通过预设第二电阻r2阻值和第三电阻r3阻值的比值,使得dc

‑

dc芯片的输出电压为22v,即逻辑“0”信号;

63.主机发出信号“1”时,光耦u1的输入端接收并截止,光耦的输出端截止,此时,pmos管q1的vgs小于开启电压,pmos管q1截止,则第一电阻r1、第二电阻r2和第三电阻r3组成反馈电阻网络,通过预设第一电阻r1阻值、第二电阻r2阻值和第三电阻r3阻值的比值,使得dc

‑

dc芯片的输出电压为36v,即逻辑“1”信号,再通过信号输出电路的mbus接口发送至从机。

64.综上,本实用新型电路中设置mos电路和dc

‑

dc电路,加快了光耦对所述主机发出的信号的处理和传输,提高了反馈电阻网络的转换速度,加快了所述dc

‑

dc芯片发出电平信号,提高了通信波形上升、下降沿的变化速率,从而提高了通信速率,同时有效降低了通信误码率。

65.本实用新型还提供一种mbus总线系统,该系统包括mbus主机和mbus主机发送电路,该mbus主机发送电路的结构可参照上述实施例,在此不再赘述。理所应当地,由于本实施例的mbus总线系统采用了上述mbus主机发送电路的技术方案,因此该mbus总线系统具有上述mbus主机发送电路所有的有益效果。

66.以上仅为本实用新型的优选实施例,并非因此限制本实用新型的专利范围,凡是利用本实用新型说明书及附图内容所作的等效结构或等效流程变换,或直接或间接运用在其他相关的技术领域,均同理包括在本实用新型的专利保护范围内。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。