1.本发明涉及成像装置。

背景技术:

2.通常,通过引入微工艺和提高封装密度,已经实现了具有二维构造的成像装置的每个像素面积的减小。近年来,已经开发出具有三维构造的成像装置以实现成像装置的尺寸的减小和成像装置的像素密度的增大(例如,参见专利文献1)。这种具有三维构造的成像装置均包括具有多个传感器像素的第一半导体基板和具有用于信号的读出处理的读出电路的第二半导体基板,每个信号是通过像素之中的相应的一个像素获得的。第二半导体基板层叠在第一半导体基板的一个表面侧上。

3.引用文献列表

4.专利文献

5.专利文献1:jp 2010

‑

245506a

技术实现要素:

6.本发明要解决的技术问题

7.读出电路均包括用于在传感器像素之中进行选择的选择晶体管、用于放大由传感器像素获得的信号的放大晶体管以及用于复位由传感器像素获得的信号的复位晶体管。读出电路中所包括的晶体管的布置和尺寸(在下文中称为布局)影响成像装置的性能。因此,期望提高布局的自由度。

8.本发明是鉴于上述情况而做出的,并且本发明的目的是提供一种能够提高其布局的自由度的成像装置。

9.技术问题的解决方案

10.根据本发明的一方面的成像装置包括:第一半导体基板,其包括构造为执行光电转换的传感器像素;和第二半导体基板,其包括读出电路,所述读出电路构造为输出基于从所述传感器像素输出的电荷的像素信号。所述第二半导体基板层叠在所述第一半导体基板的一个表面侧上以构成层叠体。所述第二半导体基板包括面对所述第一半导体基板的第一表面和位于所述第一表面的相反侧的第二表面。所述读出电路中所包括的第一晶体管设置在所述第一表面中,并且所述读出电路中所包括的第二晶体管设置在所述第二表面中。

11.与读出电路中所包括的晶体管仅设置在第二半导体基板的一侧的情况相比,能够使分配给晶体管的布置区域的面积更大,因此提高了读出电路的布局的自由度。例如,可以将放大晶体管设置在第二半导体基板的第一表面中,并且可以将选择晶体管和复位晶体管设置在第二半导体基板的第二表面中。该构造可以使放大晶体管的面积最大化,从而使得发生在成像装置中的随机噪声减少。

附图说明

12.图1是示出了根据本发明第一实施方案的成像装置的构造示例的示意图。

13.图2是示出了根据本发明第一实施方案的像素单元的构造示例的电路图。

14.图3是示出了根据本发明第一实施方案的像素单元的构造示例的在深度方向上的截面图。

15.图4a是示出了根据本发明第一实施方案的像素单元的构造示例的在水平方向上的截面图。

16.图4b是示出了根据本发明第一实施方案的像素单元的构造示例的在水平方向上的截面图。

17.图4c是示出了根据本发明第一实施方案的像素单元的构造示例的在水平方向上的截面图。

18.图5是示出了多个像素单元的布局示例的在水平方向上的截面图。

19.图6是示出了多个像素单元的布局示例的在水平方向上的截面图。

20.图7是示出了多个像素单元的布局示例的在水平方向上的截面图。

21.图8是示出了根据本发明第一实施方案的成像装置的制造方法的截面图。

22.图9是示出了根据本发明第一实施方案的成像装置的制造方法的截面图。

23.图10是示出了根据本发明第一实施方案的成像装置的制造方法的截面图。

24.图11是示出了根据本发明第一实施方案的成像装置的制造方法的截面图。

25.图12是示出了根据本发明第二实施方案的成像装置的构造示例的在厚度方向上的截面图。

26.图13a是示出了根据本发明第二实施方案的像素单元的构造示例的在水平方向上的截面图。

27.图13b是示出了根据本发明第二实施方案的像素单元的构造示例的在水平方向上的截面图。

28.图13c是示出了根据本发明第二实施方案的像素单元的构造示例的在水平方向上的截面图。

29.图13d是示出了根据本发明第二实施方案的像素单元的构造示例的在水平方向上的截面图。

30.图14是示出了根据本发明第二实施方案的成像装置的制造方法的截面图。

31.图15是示出了根据本发明第二实施方案的成像装置的制造方法的截面图。

32.图16是示出了根据本发明第二实施方案的成像装置的制造方法的截面图。

33.图17是示出了根据本发明第二实施方案的成像装置的制造方法的截面图。

具体实施方式

34.在下文中,将参照附图说明本发明的实施方案。在以下说明中所参照的附图中,相同或相似的部分用相同或相似的附图标记和符号表示。然而,应当注意的是,附图仅仅是示意性的,并且厚度与平面尺寸的关系和各层之间的厚度比例等可能与实际的不同。因此,应当考虑以下说明来确定具体的厚度和尺寸等。此外,理所当然的,在附图中可以包括在附图之间尺寸关系或尺寸比例不同的部分。

35.在以下说明中,诸如上和下等方向的定义仅仅是为了便于说明的定义,并且不限制本发明的技术思想。例如,不用说,当将物体旋转90度并且进行观察时,上下转换为左右并且被读取,并且当将物体旋转180度并且进行观察时,上下颠倒并且被读取。

36.此外,存在着使用术语“x轴方向”、“y轴方向”和“z轴方向”进行说明的情况。例如,z轴方向与稍后说明的层叠体的厚度方向平行。x轴方向和y轴方向是与z轴方向正交的方向。x轴方向、y轴方向和z轴方向彼此正交。在以下说明中,与x轴方向和y轴方向平行的方向也称为水平方向。此外,在以下说明中,术语“平面图”意味着从z轴方向观看。

37.(第一实施方案)

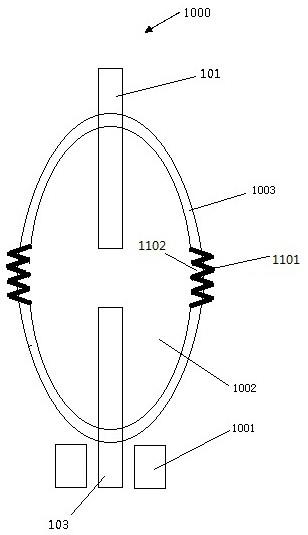

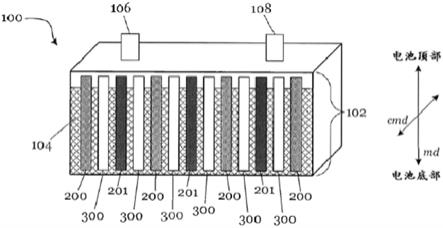

38.图1是示出了根据本发明第一实施方案的成像装置1的构造示例的示意图。成像装置1包括三个基板(第一基板10、第二基板20和第三基板30)。成像装置1是具有通过层叠三个基板(第一基板10、第二基板20和第三基板30)构成的三维构造的成像装置。第一基板10、第二基板20和第三基板3按此顺序层叠。

39.第一基板10使得第一半导体基板11包括多个用于执行光电转换的传感器像素12。多个传感器像素12以矩阵形式设置在第一基板10的像素区域13中。第二基板20使得第二半导体基板21包括用于输出基于从传感器像素12输出的电荷的像素信号的读出电路22,一个电路针对每四个传感器像素12。第二基板20包括在行方向上延伸的多个像素驱动线23和在列方向上延伸的多个垂直信号线24。

40.第三基板30使得第三半导体基板31包括用于处理像素信号的逻辑电路32。逻辑电路32包括例如垂直驱动电路33、列信号处理电路34、水平驱动电路35和系统控制电路36。逻辑电路32(具体地,水平驱动电路35)将每个传感器像素12的输出电压vout输出到外部。在逻辑电路32中,例如,可以在与源极电极和漏极电极接触的杂质扩散区域的表面上形成包含诸如cosi2或nisi等硅化物的低电阻区域,并且该硅化物是通过使用自对准硅化物(self aligned silicide)工艺形成的。

41.例如,垂直驱动电路33以行为单位依次选择多个传感器像素12。例如,列信号处理电路34对从由垂直驱动电路33选择的行中的每个传感器像素12输出的像素信号执行相关双采样(cds:correlated double sampling)处理。例如,列信号处理电路34执行cds处理,从而提取像素信号的信号电平并且保持与由传感器像素12之中的相应的一个传感器像素接收到的光量相对应的像素数据。例如,水平驱动电路35将保持在列信号处理电路34中的像素数据依次输出到外部。例如,系统控制电路36控制逻辑电路32中的所有区块(垂直驱动电路33、列信号处理电路34和水平驱动电路35)的驱动。

42.图2是示出了根据本发明第一实施方案的像素单元pu的构造示例的电路图。如图2所示,在成像装置1中,四个传感器像素12电连接至一个读出电路22以构成一个像素单元pu。四个传感器像素12共用一个读出电路22,并且来自四个传感器像素12中的各者的输出被输出到共用的读出电路22。

43.传感器像素12包括彼此共有的组件。在图2中,为了彼此区分各个传感器像素12的组件,在各个传感器像素12的组件的附图标记(例如,稍后说明的pd、tg和fd)的末端赋予相应的标识号(1、2、3或4)。在下文中,在需要彼此区分各个传感器像素12的组件的情况下,在各个传感器像素12的组件的附图标记的末端赋予这种相应的标识号。然而,在不需要彼此区分各个传感器像素12的组件的情况下,在传感器像素12的组件的附图标记的末端不赋予

标识号。

44.传感器像素12均包括例如光电二极管pd(光电转换元件的一个示例)、电连接至光电二极管pd的传输晶体管tr以及暂时保持从光电二极管pd经由传输晶体管tr输出的电荷的浮动扩散部fd。光电二极管pd执行光电转换以产生与接收到的光量相对应的电荷。光电二极管pd的阴极电连接至传输晶体管tr的源极,并且光电二极管pd的阳极电连接至基准电位线(例如,接地)。传输晶体管tr的漏极电连接至浮动扩散部fd,并且传输晶体管tr的栅极电极电连接至像素驱动线23。传输晶体管tr例如是互补金属氧化物半导体(cmos:complementary metal oxide semiconductor)晶体管。

45.共用一个读出电路22的各个传感器像素12的浮动扩散部fd彼此电连接并且电连接至共有的读出电路22的输入端子。读出电路22包括例如放大晶体管amp(第一晶体管的一个示例)、复位晶体管rst和选择晶体管sel(第二晶体管的一个示例)。需要注意的是,可以根据需要省略选择晶体管sel。

46.复位晶体管rst的源极(读出电路22的输入端子)电连接至浮动扩散部fd,并且复位晶体管rst的漏极电连接至电源线vdd和放大晶体管amp的漏极两者。复位晶体管rst的栅极电极电连接至像素驱动线23(参见图1)。放大晶体管amp的源极电连接至选择晶体管sel的漏极,并且放大晶体管amp的栅极电极电连接至复位晶体管rst的源极。选择晶体管sel的源极(读出电路22的输出端子)电连接至垂直信号线24,并且选择晶体管sel的栅极电极电连接至像素驱动线23(参见图1)。

47.当传输晶体管tr导通时,传输晶体管tr将光电二极管pd的电荷传输到浮动扩散部fd。如稍后说明的图3所示,传输晶体管tr的栅极电极tg例如从第一半导体基板11的表面穿过阱层we延伸到到达光电二极管pd的深度。复位晶体管rst将浮动扩散部fd的电位复位为预定电位。当复位晶体管rst导通时,浮动扩散部fd的电位复位为电源线vdd的电位。选择晶体管sel控制来自读出电路22的像素信号的输出时序。

48.放大晶体管amp生成与保持在浮动扩散部fd中的电荷的电平相对于的电压信号作为像素信号。放大晶体管amp构造为源极跟随器放大器,以输出与由各个光电二极管pd产生的电荷的电平相对应的电压的像素信号。当选择晶体管sel导通时,放大晶体管amp将浮动扩散部fd的电位放大并且将与如此放大的电位相对应的电压经由垂直信号线24输出到列信号处理电路34。复位晶体管rst、放大晶体管amp和选择晶体管sel例如是cmos晶体管。

49.图3是示出了根据本发明第一实施方案的像素单元pu的构造示例的在厚度方向上的截面图。需要注意的是,图3所示的截面图仅仅是示意图,并且不是旨在严格地且正确地示出实际结构的图。图3所示的截面图包括为了通过查看附图容易理解成像装置1中所包括的像素单元pu的构造的说明而有意改动晶体管和杂质扩散层的在水平方向上的位置的一些部分。

50.例如,在图3中,浮动扩散部fd、传输晶体管tr的栅极电极tg和阱接触层wec在水平方向上并排设置。然而,在实际结构中,存在着浮动扩散部fd、栅极电极tg和阱接触层wec在垂直于附图平面的方向上并排设置的情况。在这种情况下,浮动扩散部fd和阱接触层wec中的一者设置在附图平面的前方,浮动扩散部fd和阱接触层wec中的另一者设置在附图平面的后方,并且栅极电极tg介于这两者之间。将在稍后说明的图4a至图4c中更准确地示出成像装置1的实际结构。

51.如图3所示,成像装置1使得第二基板20层叠在第一基板10的前表面10a(一个表面的一个示例)侧上以构成层叠体。在第一基板10的前表面10a侧,设置有光电二极管pd、传输晶体管tr和浮动扩散部fd。光电二极管pd、传输晶体管tr和浮动扩散部fd是针对每个传感器像素12设置的。

52.第一基板10的另一个表面(例如,后表面)为光入射表面。成像装置1是在其后表面上设置有彩色滤光片和光接收透镜的背面照射式成像装置。彩色滤光片和光接收透镜是针对每个传感器像素12设置的。

53.第一基板10中所包括的第一半导体基板11包括例如硅基板。在第一半导体基板11的前表面的一部分中和在该部分附近,设置有第一导电类型(例如,p型)的阱层we。在比阱层we更深的区域中,设置有第二导电类型(例如,n型)的光电二极管pd。此外,在每个阱层we的内部,设置有p型浓度比阱层we更高的阱接触层wec和n型的浮动扩散部fd。设置阱接触层wec是为了减小阱层we和配线之间的接触电阻。

54.在第一半导体基板11中,设置有旨在将相邻的传感器像素12彼此电隔离的元件隔离层16。每个元件隔离层16具有例如浅沟槽隔离(sti:shallow trench isolation)结构,并且在第一半导体基板11的深度方向上延伸。元件隔离层16包含例如氧化硅。此外,在第一半导体基板11中,在元件隔离层16和光电二极管pd之间设置有p型层17和n型层18。p型层17位于元件隔离层16侧,并且n型层18位于光电二极管pd侧。

55.在第一半导体基板11的表面侧,设置有绝缘膜15。例如,绝缘膜15是通过层叠氧化硅膜(sio)、氮化硅膜(sin)、氧氮化硅膜(sion)和碳氮化硅膜(sicn)中的任一种或两种以上而形成的膜。

56.第二基板20中所包括的第二半导体基板21包括例如硅基板。第二半导体基板21具有面对第一基板10的前表面21a(第一表面的一个示例)和位于前表面21a的相反侧的后表面21b(第二表面的一个示例)。在图3中,前表面21a是上表面,并且后表面21b是下表面。在前表面21a中,设置有放大晶体管amp。在后表面21b中,设置有选择晶体管sel和复位晶体管rst。

57.第二半导体基板21设置有元件隔离层26和p型阱层27。元件隔离层26设置在第二半导体基板21的后表面21b侧,从而在选择晶体管sel和复位晶体管rst之间电隔离。阱层27设置在从后表面21b到前表面21a和后表面21b之间的中间位置的范围内。阱层27将设置在第二半导体基板21的前表面21a侧的放大晶体管amp与都设置在第二半导体基板21的后表面21b侧的选择晶体管sel和复位晶体管rst电隔离。

58.第二基板20包括覆盖第二半导体基板21的前表面21a、后表面21b和侧表面的绝缘膜25。例如,绝缘膜25是通过层叠sio、sin、sion和sicn中的一种或两种以上而形成的膜。第一基板10的绝缘膜15和第二基板20的绝缘膜彼此接合以构成层间绝缘膜51。

59.成像装置1包括多个配线l1至l10,该多个配线l1至l10设置在层间绝缘膜51内并且均电连接至第一基板10和第二基板20中的至少一者。如图2和图3所示,配线l1将放大晶体管amp的漏极ad电连接至电源线vdd。配线l2(第二配线的一个示例)将一个像素单元pu中所包括的四个浮动扩散部fd电连接至放大晶体管amp的栅极电极ag。配线l3将放大晶体管amp的源极as电连接至选择晶体管sel的漏极sd。配线l4将选择晶体管sel的栅极电极sg电连接至像素驱动线23(参见图1)。

60.配线l5将选择晶体管sel的源极ss电连接至垂直信号线24。配线l6将复位晶体管rst的漏极rd电连接至电源线vdd。配线l7将复位晶体管rst的栅极电极rg电连接至像素驱动线23。配线l8将复位晶体管rst的源极rs电连接至配线l2。配线l9(第一配线的一个示例)将传输晶体管tr的栅极电极tg电连接至像素驱动线23(参见图1)。配线l10将阱接触层wec电连接至供应基准电位(例如,接地电位:0v)的基准电位线。在成像装置1中,配线l2连接至放大晶体管amp的栅极电极ag的后表面agb(在图3中,上表面)侧。

61.在配线l1至l10中,在层叠体的厚度方向上延伸的配线部分包含钨(w),并且在与层叠体的厚度方向正交的方向(例如,水平方向)上延伸的配线部分包含铜(cu)或以cu为主要成分的cu合金。然而,在本发明的实施方案中,配线l1至l10的材料不限于这些材料,并且可以包括其他材料。

62.图4a至图4c是示出了根据本发明第一实施方案的像素单元pu的构造示例的在水平方向上的截面图。更具体地,图4a示出了在图3所示的位置sec1处水平切割的像素单元pu的截面图。位置sec1与选择晶体管sel的栅极电极sg的上表面和复位晶体管rst的栅极电极rg的上表面处于相同的高度。图4b示出了在图3所示的位置sec2处水平切割的像素单元pu的截面图。位置sec2与放大晶体管amp的栅极电极ag的下表面处于相同的高度。图4c示出了在图3所示的位置sec3处水平切割的像素单元pu的截面图。位置sec1与传输晶体管tr的栅极电极tg的上表面处于相同的高度。

63.图4a至图4c分别示出了一个像素单元的图,并且处于其中这些图在层叠体的厚度方向(例如,z轴方向)上彼此重叠的位置关系。图4a所示的选择晶体管和复位晶体管rst、图4b所示的放大晶体管amp以及图4c所示的四个传感器像素12在z轴方向上彼此重叠。如图4a所示,包括选择晶体管sel和复位晶体管rst的晶体管组在平面图中位于像素单元pu的中心部分处。包括配线l2、l9和l10的配线组位于晶体管组的外部。配线组设置为在平面图中夹着晶体管组左右对称。

64.如图4b所示,放大晶体管amp在平面图中位于像素单元pu的中心部分处。在层叠体的厚度方向上,放大晶体管amp、选择晶体管sel和复位晶体管rst处于彼此重叠的位置关系。此外,在平面图中,包括配线l2、l9和l10的配线组位于放大晶体管amp的外部。配线组设置为在平面图中夹着放大晶体管amp左右对称。

65.如图4c所示,一个像素单元pu中所包括的四个传感器像素12设置为经由元件隔离层16彼此靠近。此外,在四个传感器像素12之中的各者中,传输晶体管tr的栅极电极tg在平面图中介于浮动扩散部fd和阱层we之间。栅极电极tg将浮动扩散部fd和阱层we隔开。如图3所示,光电二极管pd位于浮动扩散部fd、阱层we和栅极电极tg的下方。

66.图5至图7是示出了多个像素单元pu的布局示例的在水平方向上的截面图。更具体地,图5示出了在图3所示的位置sec3处水平切割的成像装置1的截面图。图6示出了在图3所示的位置sec2处水平切割的成像装置1的截面图。图7示出了在图3所示的位置sec1处水平切割的第一基板10的截面图。如图5至图7所示,在成像装置1中,多个像素单元pu在x轴方向和y轴方向上以固定间隔排列。像素单元pu在x轴方向和y轴方向上重复设置。

67.接下来,将说明成像装置1的制造方法。需要注意的是,成像装置1是使用诸如成膜设备(包括化学气相沉积(cvd:chemical vapor deposition)设备和溅射设备)、离子注入设备、热处理设备、蚀刻设备和粘合设备等各种设备制造的。在下文中,将这些设备统称为

制造设备。

68.图8至图11是示出了根据本发明第一实施方案的成像装置1的制造方法的截面图。如图8所示,使用制造设备通过cmos工艺在第一半导体基板11的前表面11a侧形成阱层we、元件隔离层16、p型层17、n型层18、光电二极管pd、传输晶体管tr的栅极电极tg、浮动扩散部fd和阱接触层wec。然后,制造设备在第一半导体基板11的前表面11a侧形成绝缘膜15,随后使其表面平坦化。这样就完成了第一基板10。

69.在第一基板10的制造过程之前、之后或与之并行,制造设备在第二半导体基板21的前表面21a(图8中的上表面)中形成放大晶体管amp。例如,制造设备在第二半导体基板21的前表面21a上形成放大晶体管amp的源极as和漏极ad。然后,制造设备在第二半导体基板21的前表面21a上形成放大晶体管amp的栅极电极ag。以覆盖漏极ad并且露出源极as的方式形成栅极电极ag。可替代地,制造设备可以形成漏极ad和栅极电极ag,随后通过使用栅极电极ag作为掩模来形成源极as。接下来,制造设备在第二半导体基板21的前表面21a侧形成绝缘膜25,随后使其表面平坦化。

70.接下来,制造设备使形成在第二半导体基板21上的绝缘膜25和形成在第一基板10上的绝缘膜15彼此面对,然后将绝缘膜15和25接合在一起。接合方法例如是等离子体接合。通过该过程,如图9所示,第一半导体基板11和第二半导体基板21被一体化为层叠体。

71.接下来,如图10所示,制造设备通过cmos工艺在第二半导体基板21的后表面21b(图10中的上表面)中形成元件隔离层26、阱层27、选择晶体管sel和复位晶体管rst。

72.接下来,如图11所示,制造设备部分地去除第二半导体基板21,从而露出放大晶体管amp的源极as、漏极ad和栅极电极ag。例如,制造设备在第二半导体基板21的后表面21b侧形成第一掩模,使得第一掩模具有覆盖选择晶体管sel和复位晶体管rst两者并且使其余区域开口的形状。第一掩模包括例如抗蚀剂掩模和硬掩模。然后,针对第二半导体基板21,制造设备对从第一掩模露出的部分执行干蚀刻,从而使放大晶体管amp的源极as和漏极ad露出。此后,制造设备从第二半导体基板21的后表面21b侧去除第一掩模。

73.接下来,制造设备在第二半导体基板21的后表面21b侧形成第二掩模,使得第二掩模具有覆盖选择晶体管sel、复位晶体管rst、以及放大晶体管amp的源极as和漏极ad并且使其余区域开口的形状。第二掩模包括例如抗蚀剂掩模和硬掩模。然后,针对第二半导体基板21,制造设备对从第二掩模露出的部分执行干刻蚀。在该干蚀刻中,将绝缘膜25用作蚀刻阻挡层。通过该过程,放大晶体管amp的栅极电极ag从第二半导体基板21的下方露出。此后,制造设备从第二半导体基板21的后表面21b侧去除第二掩模。

74.接下来,制造设备形成图3所示的配线l1至l10。例如,制造设备多次执行绝缘膜的形成过程、绝缘膜的平坦化过程、接触孔的形成过程以及绝缘膜上和接触孔中的配线的形成过程。如上所述,在垂直方向上延伸的配线包含钨(w),并且在水平方向上延伸的配线包含cu或cu合金。这样就完成了成像装置1。

75.如上所述,根据本发明第一实施方案的成像装置1包括具有用于执行光电转换的传感器像素的第一半导体基板11和具有用于输出基于从传感器像素12输出的电荷的像素信号的读出电路22的第二半导体基板21。第二半导体基板21层叠在第一半导体基板11的前表面11a侧上以构成层叠体。第二半导体基板21具有面对第一半导体基板11的前表面21a和位于前表面21a的相反侧的后表面21b。读出电路22中所包括的放大晶体管amp设置在前表

面21a中,并且读出电路22中所包括的选择晶体管sel和复位晶体管rst设置在后表面21b中。

76.通过该构造,与读出电路22中所包括的晶体管仅设置在第二半导体基板21的一侧的情况相比,能够使分配给晶体管的布置区域的面积更大,因此提高了读出电路22的布局的自由度。例如,将放大晶体管amp设置在第二半导体基板21的前表面21a中,并且将选择晶体管sel和复位晶体管rst设置在第二半导体基板21的后表面21b中。通过该构造,在每个像素单元pu中,可以使放大晶体管amp的面积最大化。放大晶体管amp的这种最大化面积使得发生在成像装置中的随机噪声减少。

77.(第二实施方案)

78.在上述的第二实施方案中,已经说明了浮动扩散部fd经由配线l2连接至放大晶体管amp的栅极电极ag的后表面agb侧。然而,在本发明的实施方案中,浮动扩散部fd与栅极电极ag的连接方式不限于此。例如,浮动扩散部fd可以经由配线l2连接至栅极电极ag的前表面aga侧。

79.图12是示出了根据本发明第二实施方案的成像装置1a的构造示例的在厚度方向上的截面图。需要注意的是,如在第一实施方案中所述的图12的情况,图12所示的截面图也仅仅是示意图,并且不是旨在严格地且正确地示出实际结构的图。图12所示的截面图包括为了通过查看附图容易理解成像装置1a的构造的说明而有意改动晶体管和杂质扩散层的在水平方向上的位置的一些部分。将在稍后说明的图13a至图13d中更准确地示出成像装置1a的实际结构。

80.如图12所示,成像装置1a包括将浮动扩散部fd电连接至放大晶体管amp的栅极电极ag的配线l2。配线l2包括设置在第一基板10中的第一配线部l21和设置在第二基板20中的第二配线部l22。第一配线部l21电连接至一个像素单元pu中所包括的四个浮动扩散部fd1至fd4。第二配线部l22连接至与四个浮动扩散部fd1至fd4相同的像素单元pu中所包括的放大晶体管amp的栅极电极ag。第二配线部l22连接至栅极电极ag的前表面aga。

81.在第一配线部l21和第二配线部l22中,在z轴方向上延伸的配线部分包含钨(w)。在与层叠体的厚度方向正交的方向(例如,水平方向)上延伸的配线部分包含铜(cu)或cu合金。第一配线部l21和第二配线部l22在第一基板10和第二基板20之间的接合平面处分别形成为在水平方向上扩展的板形状。然后,在接合平面处,第一配线部l21和第二配线部l22通过cu

‑

cu接合而一体化。

82.图13a至图13d是示出了根据本发明第二实施方案的像素单元pu的构造示例的在水平方向上的截面图。更具体地,图13a示出了在图12所示的位置sec1处水平切割的像素单元pu的截面图。图13b示出了在图12所示的位置sec21处水平切割的像素单元的截面图。位置sec21与放大晶体管amp的栅极电极ag的下表面处于相同的高度。图13c示出了在图12所示的位置sec22处水平切割的像素单元pu的截面图。位置sec22是第一基板10和第二基板20之间的接合平面。图13d示出了在图12所示的位置sec1处水平切割的像素单元pu的截面图。

83.图13a至图13d分别示出了一个像素单元的图,并且处于其中这些图在z轴方向上彼此重叠的位置关系。图13a所示的选择晶体管和复位晶体管rst、图13b所示的放大晶体管amp、图13c所示的板状配线l2以及图13d所示的四个传感器像素12在z轴方向上彼此重叠。如图13a所示,同样,在成像装置1a中,包括选择晶体管sel和复位晶体管rst的晶体管组在

平面图中位于像素单元pu的中心部分处。包括配线l2、l9和l10的配线组位于晶体管组的外部。配线组设置为在平面图中夹着晶体管组左右对称。

84.如上所述,在成像装置1a中,配线l2没有连接至放大晶体管amp的栅极电极ag的后表面agb,而是连接至前表面aga。因此,如图13a所示,关于成像装置1a中的多个配线l2,在位置sec1处没有出现连接至栅极电极ag的配线部分。

85.如图13b所示,即使在成像装置1a中,放大晶体管amp在平面图中也位于像素单元pu的中心部分处。在平面图中,连接至传感器像素12(参见图2)的配线组位于放大晶体管amp的外部。配线组包括配线l2、l9和l10。在从z轴方向看到的平面图中,配线组的至少一部分设置为夹着放大晶体管amp左右对称。需要注意的是,成像装置1a的栅极电极ag在后表面agb侧没有被分配用于连接至配线l2的任何区域(例如,如图4b所示,在x轴方向上与漏极ad相邻的区域),因此漏极ad的区域因为该区域而更宽。

86.如图13c所示,在位置sec22处,配线l2的第二配线部l22形成为在水平方向上扩展的板形状。尽管未示出,但是在位置sec22处,配线l2的第一配线部l21同样形成为在水平方向上扩展的板形状。例如,在位置sec22处,第一配线部l21和第二配线部l22具有彼此相同的形状和尺寸。如图13d所示,成像装置1a在位置sec3处的构造与图4c所示的成像装置1在位置sec3处的构造相同。

87.图14至图17是示出了根据本发明第二实施方案的成像装置1a的制造方法的截面图。如图14所示,使用制造设备通过cmos工艺在第一半导体基板11的前表面11a侧形成阱层we、元件隔离层16、p型层17、n型层18、光电二极管pd、传输晶体管tr的栅极电极tg、浮动扩散部fd和阱接触层wec中的各者。然后,制造设备在第一半导体基板11的前表面11a侧形成绝缘膜15。然后,制造设备部分地蚀刻绝缘膜15以在浮动扩散部fd上形成接触孔。

88.接下来,制造设备形成从浮动扩散部fd穿过接触孔直到绝缘膜15的顶部的第一配线部l21。形成第一配线部l21的方法没有特别限制,然而,例如,可以包括单镶嵌法或双镶嵌法。在形成绝缘膜15之后,制造设备使绝缘膜15的上表面和第一配线部l21的上表面平坦化。通过平坦化,绝缘膜15的上表面和第一配线部l21的上表面变得彼此齐平(例如,绝缘膜15的上表面和第一配线部l21的上表面之间不存在台阶的状态)。这样就完成了第一基板10。

89.在第一基板10的制造过程之前、之后或与之并行,制造设备在第二半导体基板21的前表面21a(图3中的上表面)中形成放大晶体管amp。形成放大晶体管amp的方法与在第一实施方案中参照图8所述的方法相同。然后,制造设备在第二半导体基板21的前表面21a侧形成绝缘膜25。然后,制造设备部分地蚀刻绝缘膜25以在放大晶体管amp的栅极电极ag的前表面aga上形成接触孔。

90.然后,制造设备形成从栅极电极ag的前表面aga穿过接触孔直到绝缘膜25的顶部的配线(第二配线部l22的一部分)。形成配线的方法没有特别限制,然而,例如,可以包括单镶嵌法或双镶嵌法。在形成绝缘膜25之后,制造设备使绝缘膜25的上表面和第二配线部l22的上表面两者平坦化。通过平坦化,绝缘膜25的上表面和第二配线部l22的上表面变得彼此齐平(例如,绝缘膜25的上表面和第二配线部l22的上表面之间不存在台阶的状态)。

91.接下来,制造设备使形成在第二半导体基板21上的绝缘膜25和形成在第一基板10上的绝缘膜15彼此面对,然后将绝缘膜15和25接合在一起,并且还将第一配线部l21和第二

配线部l22接合在一起。接合方法例如是等离子体接合。通过该过程,如图15所示,第一半导体基板11和第二半导体基板21被一体化为层叠体。另外,第一配线部l21和第二配线部l22被一体化为配线l2。

92.后续处理与第一实施方案中的处理相同。接下来,如图16所示,制造设备通过cmos工艺在第二半导体基板21的后表面21b(图16中的上表面)中形成元件隔离层26、阱层27、选择晶体管sel和复位晶体管rst。接下来,如图17所示,制造设备部分地去除第二半导体基板21,从而露出放大晶体管amp的源极as、漏极ad和栅极电极ag。然后,制造设备形成图12所示的配线l1、l3至l10和第二配线部l22的其余部分(例如,高于位置sec21的部分)。这样就完成了成像装置1a。

93.根据本发明第二实施方案的成像装置1a,如根据第一实施方案的成像装置1的情况,可以增大分配给读出电路22中所包括的晶体管的布置区域的面积。这导致读出电路22的布局的自由度提高。例如,构造可以使得放大晶体管amp设置在第二半导体基板21的前表面21a中并且使得选择晶体管sel和复位晶体管rst设置在后表面21b中。这使得放大晶体管amp的面积最大化,从而导致随机噪声的进一步减少。

94.此外,在成像装置1a中,配线l2连接至放大晶体管amp的栅极电极ag的前表面aga。通过该构造,与配线l2连接至栅极电极ag的后表面agb的情况相比,可以减少穿过第二半导体基板21侧的配线l2的数量。例如,穿过第二半导体基板21侧的配线l2的数量的这种减少使得像素单元pu的尺寸成比例地缩小,或者可替代地,使得像素单元pu中所包括的第二半导体基板21在水平方向上扩展。另外,在配线l2中,可以减小浮动扩散部fd和栅极电极ag之间的配线长度,这使得寄生电容减小。以这种方式,成像装置1a可以有助于实现像素单元pu的进一步微型化和更高性能。

95.(其他实施方案)

96.如上所述,尽管已经以具体实施方案和变形例的形式说明了本发明,但是不应当将构成本发明的一部分的说明和附图理解为限制本发明。应当理解的是,根据本发明,各种替代实施方案、示例和可操作技术对于本领域技术人员是显而易见的。

97.例如,在上述的第一实施方案和第二实施方案中,关于其中放大晶体管amp设置在第二半导体基板21的前表面21a中并且选择晶体管sel和复位晶体管rst设置在后表面21b中的构造,已经进行了说明。然而,本发明的实施方案不限于此。选择晶体管sel和复位晶体管rst可以设置在第二半导体基板21的前表面21a中,并且放大晶体管amp可以设置在后表面21b中。可替代地,选择晶体管sel和复位晶体管rst中的一者和放大晶体管amp可以设置在前表面21a中,并且选择晶体管sel和复位晶体管rst中的另一者可以设置在后表面21b中。

98.以这种方式,显然,本技术包括本文中未记载的各种实施方案。在不脱离上述实施方案和变形例的主旨的情况下,可以对组件进行各种省略、替换和变更中的至少一种。此外,本说明书中记载的有益效果仅仅是示例,并非旨在限制,并且可以获得其他有益效果。

99.需要注意的是,本发明还可以包括以下构造。

100.(1)一种成像装置,其包括:

101.第一半导体基板,其包括构造为执行光电转换的传感器像素;和

102.第二半导体基板,其包括读出电路,所述读出电路构造为输出基于从所述传感器

像素输出的电荷的像素信号,其中,

103.所述第二半导体基板层叠在所述第一半导体基板的一个表面侧上以构成层叠体,

104.所述第二半导体基板包括面对所述第一半导体基板的第一表面和位于所述第一表面的相反侧的第二表面,

105.所述读出电路中所包括的第一晶体管设置在所述第一表面中,并且

106.所述读出电路中所包括的第二晶体管设置在所述第二表面中。

107.(2)根据(1)所述的成像装置,其中,

108.在所述层叠体的厚度方向上,所述第一晶体管和所述第二晶体管彼此重叠。

109.(3)根据(1)或(2)所述的成像装置,其中,

110.所述传感器像素包括:

111.光电转换元件,

112.传输晶体管,其电连接至所述光电转换元件,和

113.浮动扩散部,其构造为暂时保持从所述光电转换元件经由所述传输晶体管输出的电荷,

114.所述读出电路包括:

115.复位晶体管,其构造为将所述浮动扩散部的电位复位为预定电位,

116.放大晶体管,其构造为产生与保持在所述浮动扩散部中的电荷的电平相对应的电压信号作为所述像素信号,和

117.选择晶体管,其构造为控制从所述放大晶体管输出的所述像素信号的输出时序,

118.所述第一晶体管是从所述复位晶体管、所述放大晶体管和所述选择晶体管之中选择的一种晶体管,并且

119.所述第二晶体管是所述复位晶体管、所述放大晶体管和所述选择晶体管之中的除所述一种晶体管以外的其他晶体管。

120.(4)根据(3)所述的成像装置,其中,

121.所述一种晶体管包括所述放大晶体管,并且

122.所述其他晶体管包括所述复位晶体管和所述选择晶体管。

123.(5)根据(4)所述的成像装置,其中,

124.多个所述传感器像素电连接至一个所述读出电路,以构成一个像素单元,并且

125.在从所述层叠体的厚度方向看到的平面图中,所述放大晶体管位于所述像素单元的中心部分处。

126.(6)根据(4)或(5)所述的成像装置,其中,

127.所述层叠体包括:

128.配线组,其电连接至所述传感器像素,并且

129.在从所述层叠体的厚度方向看到的平面图中,所述配线组的至少一部分设置为夹着所述放大晶体管左右对称。

130.(7)根据(6)所述的成像装置,其中,

131.所述配线组包括与所述传输晶体管的栅极电极连接的第一配线,并且所述第一配线设置为夹着所述放大晶体管左右对称。

132.(8)根据(4)至(7)中任一项所述的成像装置,其中,

133.所述层叠体包括:

134.第二配线,其连接至所述放大晶体管的栅极电极的面对所述第一半导体基板的表面。

135.附图标记列表

136.1、1a:成像装置

137.3:列信号处理电路

138.10:第一基板

139.10a、11a、21a:前表面

140.11:第一半导体基板

141.12:传感器像素

142.13:像素区域

143.15、25:绝缘膜

144.16、26:元件隔离层

145.17:p型层

146.18:n型层

147.20:第二基板

148.21:第二半导体基板

149.21b:后表面

150.22:读出电路

151.23:像素驱动线

152.24:垂直信号线

153.27:阱层

154.30:第三基板

155.31:第三半导体基板

156.32:逻辑电路

157.33:垂直驱动电路

158.34:列信号处理电路

159.35:水平驱动电路

160.36:系统控制电路

161.51:层间绝缘膜

162.ad、rd、sd:漏极

163.ag、rg、sg、tg:栅极电极

164.aga:前表面

165.agb:后表面

166.amp:放大晶体管

167.as、rs、ss:源极

168.fd:浮动扩散部

169.l1、l2、l3、l4、l5、l6、l7、l8、l9、l10:配线

170.l21:第一配线部

171.l22:第二配线部

172.pd:光电二极管

173.pu:像素单元

174.rst:复位晶体管

175.sec1、sec2、sec3、sec21、sec22:位置

176.sel:选择晶体管

177.tr:传输晶体管

178.vdd:电源线

179.we:阱层

180.wec:阱接触层

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。