1.本发明属于硅基光子集成技术领域,尤其涉及一种兼容锗硅探测器和薄膜铌酸锂调制器的硅光集成芯片。

背景技术:

2.近年来,硅基光子集成被视为大带宽、低功耗光互连的理想解决方案之一。利用硅光技术的硅光集成芯片可集成多路高速调制器,探测器以及波分复用/解复用等器件,可满足大容量通信的需求。电光调制器作为硅光集成芯片中的一项核心器件,其性能对硅光集成芯片的总体性能起到至关重要的作用。目前主流的硅基电光调制器利用等离子色散效应,采用硅波导掺杂的方式形成pn结,不仅调制区域光传输损耗较大,而且调制器的电光带宽受限,较难大于50ghz,无法满足未来更高波特率信号传输的使用场景。

3.为解决上述技术问题,铌酸锂linbo3因其在整个电信通信波段透明,具有很强的电光效应等优点,近几十年来被作为电光调制器的理想材料。由于传统的铌酸锂电光调制器的尺寸较大,往往达到几厘米或十几厘米,且难以集成其他器件,因此较难往小型化集成化方向发展。近年来,薄膜铌酸锂电光调制器采用刻蚀铌酸锂薄膜形成光波导的方式大大提高了调制效率,因此将调制器的尺寸减小了一个数量级,如几毫米调制区长度,带宽也得到显著提升,可高达100ghz。虽然小型化得到显著改善,但是集成度方面依然受限,这种集成有一定的难度,现有的硅光平台采用cmos兼容工艺,可制作锗硅探测器,热调相移器以及各类无源器件,但难以直接将铌酸锂材料添加进硅光工艺。

技术实现要素:

4.为解决上述技术问题,本发明提供一种兼容锗硅探测器和薄膜铌酸锂调制器的硅光集成芯片。为了对披露的实施例的一些方面有一个基本的理解,下面给出了简单的概括。该概括部分不是泛泛评述,也不是要确定关键/重要组成元素或描绘这些实施例的保护范围。其唯一目的是用简单的形式呈现一些概念,以此作为后面的详细说明的序言。

5.本发明采用如下技术方案:

6.在一些可选的实施例中,提供一种兼容锗硅探测器和薄膜铌酸锂调制器的硅光集成芯片,包括:薄膜铌酸锂调制器以及单片集成在硅光集成芯片中的锗硅结构探测器;所述薄膜铌酸锂调制器包括:位于第一衬底上的硅光波导以及位于第二衬底上且倒贴在所述硅光波导一侧的薄膜铌酸锂波导。

7.进一步的,所述薄膜铌酸锂调制器还包括:垂直绝热耦合器,所述垂直绝热耦合器将所述硅光波导中的光导入到所述薄膜铌酸锂波导中,以及将所述薄膜铌酸锂波导中的光导回至所述硅光波导中。

8.进一步的,所述硅光波导对应的第一衬底为绝缘衬底上的硅衬底,所述硅光波导由soi晶圆的顶层硅刻蚀而成;所述薄膜铌酸锂波导对应的第二衬底为绝缘衬底上的硅衬底或铌酸锂衬底,所述薄膜铌酸锂波导在其他工艺平台制作完成后贴合在所述硅光集成芯

片上对应于所述硅光波导的位置处。

9.进一步的,所述硅光波导的宽度范围为300

‑

1000nm,高度范围为100

‑

500nm;所述薄膜铌酸锂波导的宽度范围为600

‑

3000nm,高度范围为300

‑

1000nm。

10.进一步的,所述硅光集成芯片上设置用于容纳所述薄膜铌酸锂波导的刻蚀槽,所述刻蚀槽开设在所述硅光波导与所述薄膜铌酸锂波导之间。

11.进一步的,所述的兼容锗硅探测器和薄膜铌酸锂调制器的硅光集成芯片,还包括:第一金属层及第二金属层;所述第一金属层作为所述薄膜铌酸锂调制器的行波调制电极,所述第二金属层作为所述薄膜铌酸锂调制器的电输入信号的电接触接口。

12.进一步的,所述薄膜铌酸锂波导的中心位于所述第一金属层电极间距的中心。

13.进一步的,所述第一金属层的厚度范围为300

‑

1000nm;所述第二金属层的厚度范围为1000

‑

3000nm;所述锗硅结构探测器的锗层厚度范围为300

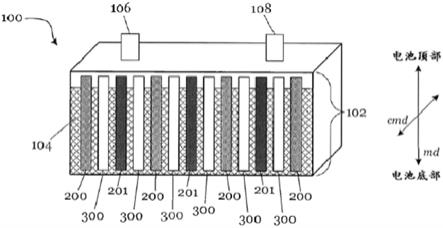

‑

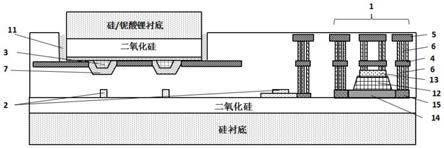

1000nm,宽度范围为1

‑

20μm。

14.进一步的,所述薄膜铌酸锂调制器还包括:硅基3db光分束器及硅基3db光合束器;所述硅基3db光分束器将输入的光等分成两束,两束光分别通过所述垂直绝热耦合器进入所述薄膜铌酸锂波导中,再通过所述垂直绝热耦合器进入所述硅光波导中,最后通过所述硅基3db光合束器进行干涉后输出。

15.进一步的,所述第一金属层形成cpw形式的行波电极传输线,射频信号的馈入通过所述第二金属层完成,行波电极的终端负载采用掺杂硅形成。

16.本发明所带来的有益效果:本发明采用混合集成方式将薄膜铌酸锂调制器集成到硅光集成芯片,完成集成后的集成芯片既拥有高速调制器,也具备高速探测器,可更好的满足未来通信对信号传输速率的要求;保证小型化的前提下大幅提升集成度;大大提高了调制效率和带宽。

附图说明

17.图1是本发明兼容锗硅探测器和薄膜铌酸锂调制器的硅光集成芯片的界面示意图;

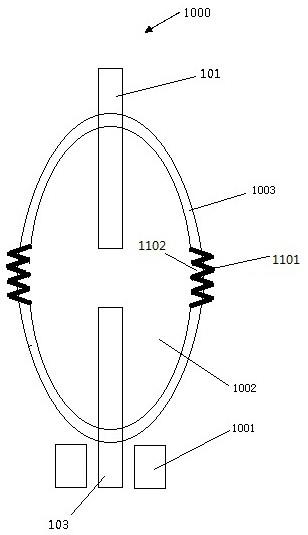

18.图2是本发明薄膜铌酸锂波导与硅光集成芯片贴合前的状态示意图;

19.图3是本发明硅基混合集成的薄膜铌酸锂调制器示意图;

20.图4是图3中a位置对应的器件截面示意图;

21.图5是图3中b位置对应的器件截面示意图;

22.图6是图3中c位置对应的器件截面示意图;

23.图7是图3中d位置对应的器件截面示意图;

24.图8是图3中e位置对应的器件截面示意图

25.图9是图3中f位置对应的器件截面示意图。

具体实施方式

26.以下描述和附图充分地展示出本发明的具体实施方案,以使本领域的技术人员能够实践它们。其他实施方案可以包括结构的、逻辑的、电气的、过程的以及其他的改变。实施例仅代表可能的变化。除非明确要求,否则单独的部件和功能是可选的,并且操作的顺序可

以变化。一些实施方案的部分和特征可以被包括在或替换其他实施方案的部分和特征。

27.如图1

‑

9所示,在一些说明性的实施例中,提供一种兼容锗硅探测器和薄膜铌酸锂调制器的硅光集成芯片,包括:薄膜铌酸锂调制器及锗硅结构探测器1,锗硅结构探测器1单片集成在硅光集成芯片中。

28.薄膜铌酸锂调制器包括:硅光波导2、薄膜铌酸锂波导3、垂直绝热耦合器、硅基3db光分束器8、硅基3db光合束器9、共面波导电极16、电阻17。

29.硅光波导2由soi晶圆的顶层硅刻蚀而成;薄膜铌酸锂波导3在其他工艺平台制作完成后贴合在硅光集成芯片上对应于硅光波导2的位置处,图1中,薄膜铌酸锂波导3倒贴在硅光波导2的上方。具体的,在其他工艺平台制作完成后薄膜铌酸锂波导3通过折射率匹配胶11固定在具有硅光波导2的硅光集成芯片上。

30.硅光波导2位于第一衬底上,硅光波导2对应的第一衬底为绝缘衬底上的硅衬底。薄膜铌酸锂波导3位于第二衬底上,薄膜铌酸锂波导3对应的第二衬底为绝缘衬底上的硅衬底或铌酸锂衬底。绝缘衬底可以为二氧化硅。

31.一般的硅光集成芯片光波导只有一层,不需要使用垂直绝热耦合器,直接使用同一高度的波导进行传输或耦合即可。本发明的垂直绝热耦合器用于将硅光波导2中的光导入到薄膜铌酸锂波导3中,以及将薄膜铌酸锂波导3中的光导回至硅光波导2中。其中,垂直绝热耦合器,是指能将光从一个高度的光波导转换到另一个高度的光波导的结构,常见于不同材料光波导间的光耦合。垂直绝热耦合器结构可以是锥形耦合结构或者定向耦合器结构或者其他类型结构。

32.锗硅结构探测器1,利用cmos兼容工艺制作,单片集成的方式集成在硅光集成芯片中。与其他材料体系的光子集成技术相比,硅光技术有一些特有的优势,如硅材料在光通讯常用的波段o波段,即1260nm

‑

1360nm以及c波段,即1530

‑

1565nm是透明的,硅光平台有很高的折射率差可以实现结构紧凑的光波导器件,可以实现很高的集成度。由于硅光器件的加工工艺与cmos工艺兼容,因此可量产,成本低。

33.不过,硅材料对o波段和c波段的光是透明的,因此无法使用硅材料做光探测器。锗材料对o波段和c波段的光有吸收作用,而且与硅同是四族材料,锗材料制备工艺与cmos工艺兼容,因此使用锗硅结构做探测器有很大优势。在光集成芯片中还有一类很重要的器件,那就是调制器,起到将电信号转换成光信号的作用。目前硅光芯片中常用的调制器基于等离子色散效应,基于此效应的调制器电光带宽受限,线性度不好,不适用以后更高波特率的工作场景。本发明的薄膜铌酸锂调制器则可实现超大电光带宽并且光损耗较低,是较为理想的调制器类型。但是铌酸锂波导结构只适合做调制器,无法做探测器,无源光波导器件也因尺寸过大不适合集成,本发明将薄膜铌酸锂调制器与锗硅结构探测器统一集成到硅光芯片中,因此硅光集成芯片可利用各材料和结构的优势,使得芯片集成度高,性能优良,成本低有竞争力。

34.本发明还包括:第一金属层4及第二金属层5。对集成的薄膜铌酸锂调制器而言,第一金属层4作为薄膜铌酸锂调制器的行波调制电极,第二金属层5作为薄膜铌酸锂调制器的电输入信号的电接触接口。第一金属层4两侧设置通孔6。

35.硅光集成芯片上设置用于容纳薄膜铌酸锂波导3的刻蚀槽7,刻蚀槽7开设在硅光波导2与薄膜铌酸锂波导3之间,在图1中,刻蚀槽7开设在硅光波导2的上方。硅光芯片上的

刻蚀槽7,可使得薄膜铌酸锂波导3与硅光波导2的高度差降低以便减小两者之间的耦合损耗,性能更好。

36.将薄膜铌酸锂波导3的位置设定在第一金属层4构成的行波电极的合适位置实现高效率调制,即薄膜铌酸锂波导3的中心位于第一金属层4电极间距的中心。

37.硅光波导2的宽度范围为300

‑

1000nm,高度范围为100

‑

500nm。目前市面上常用的硅光波导高度在100

‑

500nm范围内,考虑到波导模式与损耗,对应的波导宽度在300

‑

1000nm范围内波导设计较为合理,即损耗最低。

38.薄膜铌酸锂波导3的宽度范围为600

‑

3000nm,高度范围为300

‑

1000nm。目前市面上常规的薄膜铌酸锂厚度在300

‑

1000nm范围内,考虑到波导模式与损耗,对应的波导宽度在600

‑

3000nm范围内波导设计较为合理,即损耗最低。

39.第一金属层4的厚度范围为300

‑

1000nm,第二金属层5的厚度范围为1000

‑

3000nm,金属层处于上述厚度范围使得本发明可以利用现有的常规的原料和加工工艺,做到尽量少添加特殊工艺,少改动原来的工艺制程,降低集成的难度。

40.锗硅结构探测器1包括:n型掺杂硅层13、锗层12、p型掺杂硅层14。锗硅结构探测器的锗层12厚度范围为300

‑

1000nm,宽度范围为1

‑

20μm。

41.硅光波导2通过cmos兼容工艺刻蚀soi晶圆的顶层硅形成,薄膜铌酸锂波导3则在其他工艺平台制作而成。调制区域通过将薄膜铌酸锂波导3倒贴在硅光芯片中的对应区域而成,薄膜铌酸锂波导3倒贴前的状态示意图如图2所示。

42.如图3所示,光学方面,硅基3db光分束器8、硅基3db光合束器9、硅光波导2、薄膜铌酸锂波导3以及垂直绝热耦合器构成了马赫增德尔干涉仪结构。在调制器区的前部,垂直绝热耦合器负责将硅光波导2中的光导入到薄膜铌酸锂波导3中;在调制器区的后部,垂直绝热耦合器负责将薄膜铌酸锂波导3中的光导回到硅光波导2中。调制器与外部光纤或激光器等耦合的耦合器采用硅光边缘耦合器或光栅耦合器。电学方面,采用第一金属层4形成共面波导传输线形式的行波电极传输线,行波电极的终端负载通过掺杂硅制作而成。

43.硅基3db光分束器8用于将输入的光等分成两束,两束光分别进入马赫增德尔干涉仪结构的两臂,然后两束光分别通过对应的垂直绝热耦合器进入到薄膜铌酸锂波导3中,光在薄膜铌酸锂波导3传输时受到电调制信号的影响因而光的相位受到调制,之后这两束光再由垂直绝热耦合器进入到硅光波导2中,然后再通过硅基3db光合束器9进行干涉,最后输出的光便是受到调制的光信号。

44.为方便对准,可设计对应的自对准标记10,自对准结构的设计可有效降低对准难度,具体的,本发明可形成一定的对位孔以便实现自适应对准,如图6所示,自对准标记10可通过对准柱101和对准槽102实现。

45.如图5所示,第一金属层4形成cpw形式的行波电极传输线,如图4所示,射频信号的馈入通过第二金属层5完成。

46.如图6所示,薄膜铌酸锂波导3处于硅光波导2的正上方,并且由于硅光集成芯片有刻蚀槽7的原因,薄膜铌酸锂波导3可更加接近硅光波导2,从而提高垂直绝热耦合器的耦合效率,减少光损耗。

47.如图9所示,行波电极的终端负载15采用掺杂硅形成,比如采用p 掺杂,即p型重掺杂。

48.现有技术对于薄膜铌酸锂调制器集成到硅光集成芯片上有一定的难度,难以直接将铌酸锂材料添加进硅光工艺,本发明通过上述结构实现集成,提供了一种适用于硅光集成芯片的硅基薄膜铌酸锂调制器,既可利用硅光集成芯片上的高速探测器和各类有源、无源器件,又兼具铌酸锂调制器的高带宽底损耗特性。本发明采用混合集成的方法将薄膜铌酸锂调制器集成到硅光集成芯片,硅光集成芯片采用cmos兼容工艺制作,可制作锗硅结构探测器,热调相移器以及各类无源功能器件。完成集成后的集成芯片既拥有高速调制器,也具备高速探测器,可更好的满足未来通信对信号传输速率的要求。

49.本领域技术人员还应当理解,结合本文的实施例描述的各种说明性的逻辑框、模块、电路和算法步骤均可以实现成电子硬件、计算机软件或其组合。为了清楚地说明硬件和软件之间的可交换性,上面对各种说明性的部件、框、模块、电路和步骤均围绕其功能进行了一般地描述。至于这种功能是实现成硬件还是实现成软件,取决于特定的应用和对整个系统所施加的设计约束条件。熟练的技术人员可以针对每个特定应用,以变通的方式实现所描述的功能,但是,这种实现决策不应解释为背离本公开的保护范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。