使用内置自测控制器测试只读存储器

背景技术:

1.许多电子系统包含执行来自存储器的代码的微处理器。此类系统通常包含只读存储器(rom)及随机存取存储器(ram)。“启动”rom可包含于系统中以存储在系统的启动过程期间执行的代码。许多系统在启动过程期间及/或在已完成启动过程之后的闲置时间期间测试ram及rom以确认此类存储器是否结构上完整无缺及所存储的数据是否可靠。

技术实现要素:

2.在一个实例中,一种系统包含易失性存储装置、只读存储器(rom)、存储器内置自测(bist)控制器及中央处理单元(cpu)。所述cpu在发生复位事件后即刻执行来自所述rom的第一指令以致使所述cpu将多个指令从所述rom中的一系列地址拷贝到所述易失性存储装置。所述cpu还执行来自所述rom的第二指令以改变程序计数器。所述cpu进一步使用所述程序计数器执行来自所述易失性存储装置的所述多个指令。所述cpu在执行来自所述易失性存储装置的所述多个指令时致使所述rom进入测试模式且致使所述存储器bist控制器经配置以测试所述rom。

3.在另一实例中,一种方法包含:将多个指令从只读存储器(rom)内的一系列地址拷贝到易失性存储装置;及将程序计数器的值改变为对应于所述易失性存储装置内的在所述多个指令的开始处的地址。所述方法进一步包含执行来自所述易失性存储装置的所述多个指令。所述指令包含用以将所述程序计数器的所述值改变为对应于继所述rom内的所述多个指令的末尾之后的在所述rom内的地址的指令。所述方法还包含执行在所述rom内的指令以确定所述rom是否通过了测试。

附图说明

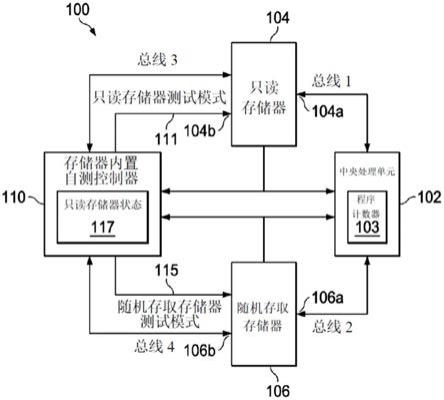

4.图1图解说明用于测试rom的实例性系统。

5.图2图解说明将代码从rom拷贝到ram以从ram执行代码从而由存储器内置自测(mbist)控制器起始rom的测试。

6.图3图解说明用于使用mbist控制器测试rom的时间线。

7.图4展示用于测试rom的系统的另一实例。

8.图5是用于测试rom的方法的流程图。

具体实施方式

9.如上文所描述,在启动过程期间验证rom的内容。循环冗余检验(crc)技术通常用于验证rom的内容。crc技术是耗时的,且一些应用可具有严格定时要求。在(举例来说)其中可包含含有rom的电路的汽车应用的情形中,需要在相对最小时间窗内验证rom的内容,特别是在rom是安全关键电路的一部分时。举例来说,每当司机打开汽车时,在所述汽车内的一或多个rom可需要验证其内容。然而,司机期望在启动汽车之后能够很快驾驶汽车并使汽车安全地操作。

10.本文中所描述的实例提供用于迅速地验证rom的内容的电路架构。所述架构包含测试系统的ram及rom两者的存储器内置自测(mbist)控制器。在启动过程期间早些时候,中央处理单元(cpu)执行来自rom的指令,所述指令致使cpu将某些指令从rom拷贝到ram(或其它类型的易失性存储装置)。cpu接着继续执行来自ram的那些特定指令。从ram执行的所拷贝指令致使cpu将rom转变到测试模式且致使cpu指示mbist控制器测试rom。通过将rom测试责任转移给mbist控制器,cpu可用于执行其它有用启动与初始化功能,借此加快启动过程。此外,在一些系统中,由rom的cpu进行紧接读取存取是不可能的,此使测试rom比紧接读取可能的情况要慢。更进一步地,如果crc过程用于测试rom,那么使用cpu的算术逻辑单元(alu)及寄存器的计算循环可包含每一经测试的rom位置10到15个循环。本文中所描述的架构以更高效且更快方式测试rom。本文中所描述的实例涉及使用ram来辅助测试rom,但可替代ram(例如,寄存器)而使用其它类型的易失性存储装置。

11.图1展示含有cpu 102、rom 104、ram 106及mbist控制器110的系统100的实例。在一个实施方案中,系统100包括系统单芯片(soc),其中图1中所展示的组件制作于共同半导体裸片上。rom 104是非暂时性存储装置。虽然在此实例中展示一个cpu 102,但可在其它实例中包含多个cpu。在此实例中,cpu 102可经由地址与数据总线(bus1)存取rom 104,且cpu 102可经由不同地址与数据总线(bus2)存取ram 106。cpu 102执行位于与程序计数器(pc)103对应的存储器位置处的代码。pc 103的值是从中提取指令的ram 106或rom 104中的地址,或所述值用于导出存储器地址(例如,添加到偏移以产生存储器地址的值)。类似地,mbist控制器110经由地址与数据总线bus3及bus4分别以通信方式耦合到rom 104及ram 106。

12.可执行指令(还称为“代码”)存储于rom 104中且可从其检索以由cpu 102执行。所述代码可包括在使系统100复位(例如,硬或软复位)后即刻执行的启动代码。所述启动代码可致使cpu 102执行各种初始化功能,例如配置各种寄存器、存在于系统中的测试接口等。ram 106可用作用于暂时存储在运行时期间使用的数据或代码的便笺存储装置。来自rom 104的代码可传送到ram 106以从ram 106执行。

13.ram 106可包括一或多个存储器装置且是双端口存储器装置。经由一个端口106a,cpu 102可存取ram 106。经由另一端口106b,mbist控制器110可存取ram 106。ram test mode信号115可经断言到第一逻辑状态以致使ram 106处于其中cpu 102能够使用ram 106的第一执行模式(称为“运行时执行模式”)中,或经断言在第二逻辑状态中以致使ram 106处于其中mbist控制器110能够存取ram的第二模式(称为“测试模式”)中。在运行时执行模式中,端口106a是活动的(且端口106b是不活动的)以允许cpu 102经由bus2存取ram 106。在测试模式中,端口106b是活动的(且端口106a是不活动的)以允许mbist控制器110经由bus4存取ram。当处于其测试模式中时,mbist控制器110可测试ram 106。举例来说,经由bus4,mbist控制器110可将预定义位型样写入到ram106,且接着读取ram以确认读取数据匹配写入到ram的内容。在一个实例中,cpu 102对mbist控制器110中的一或多个控制寄存器进行写入以触发mbist控制器110开始测试ram 106。

14.rom 104也是双端口存储器装置且包含端口104a及104b。端口104a耦合到cpu 102且端口104b耦合到存储器bist控制器110。类似于ram 106,rom test mode 111可由存储器bist控制器110断言到第一逻辑状态以致使rom 104处于其中cpu 102能够存取rom 104(例

如,以提取代码)的“运行时”执行模式中,或经断言在第二逻辑状态中以致使rom 104处于其中mbist控制器110能够存取rom的“测试模式”中。在运行时执行模式中,端口104a是活动的(且端口104b是不活动的)以允许cpu 102经由bus1存取rom 104。在测试模式中,端口104b是活动的(且端口104a是不活动的)以允许mbist控制器110经由bus3存取rom 104。

15.为了测试rom 104,可执行图2中所描述的实例性程序。转向图2,展示rom 104及ram 106的至少若干部分的内容。rom 104包含可执行代码202、204、206、208、210及212。代码202及212包括功能性rom代码以辅助启动系统而且辅助在运行时期间操作系统(例如,代表较高阶应用提供对低阶硬件组件的存取)。在启动过程期间,cpu 102开始执行(举例来说)以rom_addr_0开始的功能性rom代码202。也就是说,程序计数器103加载有对应于rom_addr_0的值且cpu 102开始在rom内的所述地址处执行指令。针对从rom 104提取的每一代码指令(或指令群组)使pc 103递增。

16.pc 103最终将是与rom 104内的代码204的位置对应的值。代码204包括致使cpu102将rom代码208从范围介于rom_addr_b与rom_addr_c之间的地址拷贝到范围介于ram_addr_x与ram_addr_y之间的ram地址的指令,如由虚线展示。用于接收rom代码208的ram 106的部分是ram的其它未使用部分220。接收到ram 106中的rom代码208在图2中经展示为ram代码222。

17.一旦将rom代码208拷贝到ram 106,便再次使pc递增到rom_addr_a。所述位置处的代码致使cpu 102将pc 103改变到与ram地址ram_addr_x(含有来自rom104的代码208的ram代码222的开始地址)对应的值。cpu 102接着执行rom代码208的指令,但执行来自ram的那些指令的副本(代码222)。所述指令包括指令208a到208d。指令208a致使cpu 102针对测试模式配置rom 104。在一个实例中,针对测试模式配置rom104包括存储器bist控制器110将rom test mode信号111(图1)断言到致使rom 104进入其中启用其端口104b(并停用端口104a)的其测试模式的逻辑状态。接着执行指令208b以致使cpu 102配置mbist控制器110以测试rom 104。在一个实例中,cpu 102对mbist控制器110中的一或多个控制寄存器进行写入以触发mbist控制器110开始测试rom 104。任何适合非易失性存储器测试过程可用于测试rom 104。

18.cpu 102接着执行指令208c以致使cpu 102进入暂停状态以等待mbist控制器110完成其对rom 104的测试。一旦mbist控制器110完成其rom测试过程,mbist控制器110便可断言对cpu 102的中断以将已完成rom测试发信号通知给cpu。cpu 102退出暂停状态且接着执行指令208d,指令208d致使cpu 102将rom 104带出其测试模式并放到运行时执行模式中以借此准许cpu 102再次经由端口104a检索来自rom的指令。mbist控制器可实施此动作,所述mbist控制器将rom test mode信号111的逻辑状态改变到与其中启用端口104a并停用端口104b的运行时执行模式对应的逻辑状态。接着执行来自ram 106的指令208e,指令208e致使cpu将pc 103改变到对应于rom_addr_d的值,rom_addr_d是继先前拷贝到ram 106的代码208之后的rom地址。

19.mbist控制器110包含rom状态寄存器117,rom状态寄存器117含有指示rom测试的结果的值。在一个实例中,rom状态寄存器包含通过/未通过指示。在新改变的pc 103返回到对应于rom_addr_d的值的情况下,cpu 102接着从rom 104而非ram 106提取指令。指令210因此经提取并致使cpu 102检查mbist状态寄存器117的rom测试的结果。如果rom 104通过

了其测试,那么指令210进一步可致使代码执行在功能性rom代码212中继续。如果rom 104确实未通过其测试,那么指令210可起始错误响应。错误响应的实例包含产生对cpu 102的中断、由错误状态机断言输出信号等。

20.图3提供图解说明如何测试rom 104的时间线的实例。在ram 106由mbist控制器110测试(且因此在图3的实例中,ram test mode信号115处于例如逻辑“0”的逻辑状态中)之前或之后,rom test mode信号111处于与rom的运行时执行模式对应的逻辑状态(图3中的“0”,如在302处所展示)中以准许cpu 102从rom 104提取代码以用于执行。在306处,cpu 102将代码208从rom 104拷贝到ram 106。rom test mode信号111的逻辑状态接着改变到用以将rom 104置于测试模式中的状态(在此实例中为逻辑“1”)以准许mbist控制器110存取端口104b以用于测试目的。从ram执行所拷贝rom代码208(现在在ram 106中)。所拷贝rom代码208致使cpu 102执行上文所阐释的操作,例如配置mbist控制器110以测试rom 104。在313处,rom test mode信号111接着经断言返回到其前一状态,其中使rom 104回到其运行时执行模式中,使得代码提取可从rom 104继续且在312处由cpu 102执行。

21.图4是实施上文所阐释的rom测试范式的系统400的实例性架构。实例性系统400包含cpu 402(其可包括arm核心)、启动rom 404、ram 406及mbist控制器410。在图4的实例中,系统400还包含额外组件,例如直接存储器存取(dma)控制器412、额外rom428及硬件crc 420。cpu 402、dma 412、mbist控制器410、硬件crc 420、rom 428及ram 406经由总线405耦合在一起。在一个实例中,总线405包括高级可扩展接口(axi),但在其它实施方案中可与其它标准一致。启动rom 404(其含有图2中所展示的rom代码)经由紧密耦合存储器(tcm)接口(itcm及dtcm)耦合到cpu 402。mbist控制器410分别经由接口413、425及427耦合到启动rom 404、rom 428及ram 406,如所展示。由cpu 102及mbist控制器110相对于图1的rom 104及ram 106执行的操作是由cpu 402及mbist控制器410相对于图4的rom 404及ram 406执行的。

22.图5展示根据实例的方法的流程图。可以所展示的次序执行或以不同次序执行操作。此外,可循序地执行操作,或者可同时执行操作中的两者或多于两者。

23.在502处,发生复位事件。可启用系统100、400的电源或者可发生软或硬复位事件。在504处,cpu开始从rom(例如,rom 104、rom 404)执行代码。rom指令中的一者在506处致使cpu将rom的代码的一部分拷贝到ram。在508处将pc改变为对应于ram中的与所拷贝rom代码的开始对应的地址。cpu接着开始从ram执行所拷贝代码,且在这样做时在510处将rom配置成测试模式。在512处,mbist控制器(例如,mbist控制器110、410)由cpu配置以测试rom,且mbist控制器接着开始测试rom(514)。

24.cpu在516处等待mbist控制器完成rom测试。一旦完成rom测试,在518处,便将rom往回配置成其运行时执行模式以准许cpu继续从rom提取指令。pc被改变到rom中的继先前所拷贝rom代码之后的地址(520)。在522处,方法包含确定rom是否通过了测试。此操作可包括cpu读取寄存器中的值(例如,通过/未通过标志)。如果rom通过了其测试,那么方法在526处继续,其中完成启动过程且系统进入其运行时环境(例如,执行一或多个运行时应用程序)。然而,如果确定rom未通过其测试,那么在524处,以适合方式(例如上文所描述的方式)处理rom错误。

25.在此说明中,术语“耦合(couple或couples)”意味间接或直接有线或无线连接。因

此,如果第一装置耦合到第二装置,那么所述连接可通过直接连接或通过经由其它装置及连接的间接连接。叙述“基于”意指“至少部分地基于”。因此,如果x基于y,那么x可随y及任何数目个额外因素而变。

26.修改在所描述实施例中是可能的,且其它实施例在权利要求书的范围内是可能的。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。