[0001]

本公开涉及半导体装置,特别涉及用于减少半导体装置中存取装置亚阈值泄漏的设备和方法

背景技术:

[0002]

半导体存储器装置(例如,dram(动态随机存取存储器))包含具有在字线和位线之间的交叉处设置的存储器单元的存储器单元阵列。半导体存储器装置可以包含分层结构的主字线和子字线。主字线是位于上层的字线,并且由行地址的第一部分选择。子字线是位于下层的字线,并且基于相对应的主字线(mwl)和字驱动器线(fx)来选择,所述字驱动器线由行地址的第二部分选择。

[0003]

由于半导体制造中的阵列存取装置的缩减(例如,晶体管电路的间距尺寸变小以及需要重新平衡注入物的掺杂),固有的存取装置关断状态泄漏增加。这种存取装置ioff泄漏的增加可能导致存储器装置的可靠性降低。例如,当感测放大器将位线驱动到“0”时,可能会影响存储数据“1”的单元。这种存取装置ioff泄漏的增加已限制了存储器单元的进一步缩放。因此,减少存取装置ioff泄漏是所期望的。

技术实现要素:

[0004]

本申请的一方面涉及一种设备,其包括:多个子字线;多个子字驱动器,其被配置成响应于激活命令而以作用电压来驱动所述多个子字线中的一个选择子字线并以非作用电压来驱动所述多个子字线中的未选择子字线;和非作用字线电压控制电路,其耦合到所述多个子字线驱动器中的每一个,所述非作用字线电压控制电路被配置成响应于所述激活命令而将所述非作用电压从第一关断状态字线电压(vnwl)移位到低于所述第一vnwl的第二vnwl。

[0005]

本申请的另一方面涉及一种设备,其包括:多个字驱动器,其被配置成驱动耦合到存储器单元阵列的多个字驱动器线;非作用字线电压控制电路,其被配置成向所述多个字驱动器提供关断状态字线电压(vnwl),并且进一步被配置成:响应于激活信号而将所述vnwl从第一电压切换到第二电压,其中所述第二电压是从所述第一电压减小的电压。

[0006]

本申请的另一方面涉及一种设备,其包括:多个存储体;和多个子字驱动器,每个子字驱动器分别耦合到多个存储体中的一个存储体,并且被配置成向所述存储体提供子字线信号,其中每个子字驱动器包括:电路,其被配置成接收主字信号和字线驱动信号,并且被配置成响应于作用主字信号而向所述子字线信号提供所述字线驱动信号的电压并响应于非作用主字信号而向所述子字线信号提供非作用电势;其中所述非作用电势响应于第一存储体的激活而被提供第一关断状态字线电压(vnwl),并且在所述第一存储体的所述激活之后的某一持续时间之后提供第二vnwl,其中所述第二vnwl是低于所述第一vnwl的电压。

[0007]

本申请的又一方面涉及一种方法,其包括:激活多个存储体中的一个存储体;响应于激活所述多个存储体中的所述存储体而向与所述存储体相关联的字驱动器提供作用激

活信号;响应于激活所述存储体而提供第一关断状态字线电压(vnwl)作为与所述存储体相关联的所述字驱动器的非作用电势;响应于对所述存储体进行预充电而向与所述存储体相关联的所述字驱动器的所述非作用电势提供第二vnwl;其中所述第一vnwl是低于所述第二vnwl的负电压。

附图说明

[0008]

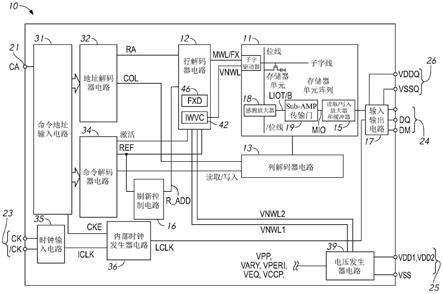

图1是根据本公开中描述的一些实例的半导体装置的框图。

[0009]

图2是根据本公开中描述的一些实例的半导体装置的示范性布局的图。

[0010]

图3是根据本公开中描述的一些实例的非作用字线电压控制电路的图。

[0011]

图4是根据本公开中描述的一些实例的在非作用字线电压控制电路的操作期间的各种信号的时序图。

[0012]

图5是根据本公开中描述的一些实例的半导体装置的存储器单元阵列的存储体的示范性配置的图。

[0013]

图6是根据本公开中描述的一些实例的存储器单元阵列的存储体的一部分的示意图。

[0014]

图7是根据本公开中描述的一些实例的字驱动器的电路图。

[0015]

图8是根据本公开中描述的一些实例的在驱动器电路的操作期间的各种信号的时序图。

具体实施方式

[0016]

下面阐述某些细节以提供对本公开的各个实施例的实例的充分理解。然而,应当理解,可以在没有这些特定细节的情况下实践本文描述的实例。此外,本文描述的本公开的特定实例不应被解释为将本公开的范围限制为这些特定实例。在其它实例中,并未详细示出公知的电路、控制信号、时序方案和软件操作,以便避免不必要地使本公开的实施例晦涩难懂。另外,诸如“耦合(couples/coupled)”之类的术语是指两个组件可以直接或间接电耦合。间接耦合可以暗示两个组件通过一或多个中间组件耦合。

[0017]

半导体存储器装置可以包含分层结构的主字线和子字线。主字线是位于上层的字线,并且由行地址的第一部分选择。子字线是位于下层的字线,并且基于相对应的主字线(mwl)和字驱动器线(fx)来选择,所述字驱动器线由行地址的第二部分选择。mwl可以由主字驱动器(mwd)驱动,并且字驱动器线fx可以由字驱动器(fxd)驱动。必须将mwl和fx都驱动到作用状态,才能在存储器装置中选择期望的子字线。当子字线被驱动到作用电势时,存储器单元连接到相对应的位线。另一方面,在子字线被驱动到非作用电势期间,存储器单元和位线保持为截止状态。在将子字线驱动到作用电势时,相对高的电压被提供给存储器垫的子字驱动器。相反,在将子字线驱动到非作用电势时,相对低的电压被提供给存储器垫的子字驱动器。当存储体已被激活时,存取装置ioff泄漏趋于增加。因此,在破坏非作用子字线方面,在较长持续时间内处于作用状态的子字线可能比在较短持续时间内处于作用状态的子字线具有更高的风险。在一些实例中,在激活字线(以激活存储体)之后的某一持续时间之后,当可能发生激活存储体中的存取装置ioff泄漏时,默认(例如,相对低的或负电压)非作用电势被设置为减小电压非作用电势。本减小电压非作用电势可以减少与存储体的激活

相关联的存取装置ioff泄漏。在页面存取操作中已涉及的行的去激活之后,非作用电势恢复到默认电压。

[0018]

与例如在激活存储体时立即提供减小电压相比,在激活存储体之后的某一持续时间之后提供减小电压可以消耗更少的功率。也就是说,与在存储体处于作用状态的整个时间内提供减小电压相比,在存储体处于作用状态的一部分时间内提供减小电压可以消耗更少的功率。

[0019]

图1是根据本公开中描述的一些实例的半导体装置10的框图。在本公开的一些实施例中,半导体装置10可以是动态随机存取存储器(dram)。半导体装置10包含存储器单元阵列11。存储器单元阵列11包含彼此交叉的多个子字线swl和多个位线bl,其中存储器单元(mc)设置在交叉点处。swl可以由子字驱动器swd驱动。为了清楚起见,在图1中仅示出了一个swl、swd、bl和mc。多个主字线mwl和字驱动器线fx可以耦合在行解码器电路12和swd之间。主字线mwl和字驱动器线fx的选择由行解码器电路12执行,并且位线bl的选择由列解码器电路13执行。例如,行解码器电路12可以包含字线驱动器46,所述字线驱动器46被配置成在字线驱动器线fx上为存储器单元阵列11生成信号。

[0020]

在一些实例中,行解码器电路12还可以包含非作用字线电压控制(iwvc)电路42,以向存储器单元阵列提供关断状态字线电压(vnwl)作为子字驱动器的非作用电势。vnwl可以取决于存储器单元阵列11的激活状态而不同。例如,当字线在某一持续时间之后保持为作用状态时,vnwl可以从第一vnwl(例如,vnwl1)切换/移位到第二vnwl(例如,vnwl2)。vnwl1可以是默认非作用电势。在本公开的一些实施例中,默认非作用电势是负电压电平。vnwl2可以是小于默认电压vnwl1的减小电压。当存储器单元阵列被预充电时,vnwl可以切换/移位到默认负电压vnwl1。减小vnwl2可以减少存取装置ioff泄漏,尤其是对于被存取的存储器单元。

[0021]

进一步参考图1,感测放大器18耦合到相对应的位线bl,并且耦合到本地i/o线对liot/b。本地io线对liot/b经由传输门tg 19耦合到主io线对miot/b,所述传输门tg 19用作到读取/写入放大器和缓冲器15的开关。转向对半导体装置10中包含的多个外部端子的说明,多个外部端子包含命令和地址端子21、时钟端子23、数据端子24以及电源端子25和26。

[0022]

命令和地址端子21被提供有命令和地址信号ca。提供给命令和地址终端21的ca信号包含命令和地址。ca信号中包含的地址经由命令/地址输入电路31传输到地址解码器电路32。地址解码器电路32接收地址,并且将解码行地址信号ra提供给行解码器电路12并将解码列地址信号col提供给列解码器电路13。

[0023]

提供给命令和地址端子21的ca信号中包含的命令经由命令/地址输入电路31输入到命令解码器电路34。命令解码器电路34对命令进行解码以提供各种内部命令信号。例如,内部命令可以包含用于选择字线的行命令信号和用于选择位线的列命令信号(例如,读取命令或写入命令)。

[0024]

当发出行激活命令并且向行地址及时提供激活命令且向列地址及时提供读取命令时,从由这些行地址和列地址指定的存储器单元阵列11中的存储器单元mc读取读取数据。更具体地,行解码器电路12选择由行地址ra指示的主字线mwl、字驱动器线fx和子字线swl,使得相关联的存储器单元mc随后连接到位线bl。此外,当通过行地址选择存储器单元

mc并且通过行激活命令激活相关联的行时,主字线mwl可以处于作用状态,并且字驱动器线fx可以处于作用状态。这导致子字线swl可以处于作用状态。相反,当未选择存储器单元mc时,字驱动器线fx可以处于非作用状态,从而将子字线swl驱动到处于非作用电势(例如,关断状态字线电压vnwl)。

[0025]

进一步参考图1,读取数据dq经由读取/写入放大器15和输入/输出电路17从数据端子24向外部输出。类似地,当发出行激活命令并且向行地址及时提供激活命令且向列地址及时提供写入命令时,输入/输出电路17可以在数据端子24处接收写入数据dq。写入数据dq经由输入/输出电路17和读取/写入放大器15提供给存储器单元阵列11并写入由行地址和列地址指定的存储器单元mc中。

[0026]

装置10可以包含用于执行刷新操作的刷新控制电路16。在刷新操作期间,可以刷新与一或多个字线相关联的存储器单元。字线的刷新可以被称为刷新,并且刷新操作可以包含多次刷新。刷新操作可以是自动刷新操作和/或其它刷新操作。在一些实施例中,刷新命令可以从外部发出到装置10并且提供给命令解码器电路34,所述命令解码器电路34将命令提供给刷新控制电路16和行解码器电路12。在一些实施例中,可以定期地由装置10的组件(例如,在内部由刷新控制电路16或命令解码器电路34)提供刷新命令。刷新控制电路16可以将刷新地址r_add提供给行解码器电路12,所述刷新地址可以指示用于进行刷新操作的行地址。如将更详细地描述,在刷新操作期间,由刷新地址r_add指示的字线(例如,子字线)可以跨多个存储器垫和/或存储体刷新。

[0027]

时钟端子23分别被提供有外部时钟信号ck和/ck。这些外部时钟信号ck和/ck彼此互补并且被提供给时钟输入电路35。时钟输入电路35接收外部时钟信号ck和/ck并提供内部时钟信号iclk。内部时钟信号iclk被提供给内部时钟发生器36,并且因此,基于从命令/地址输入电路31接收的内部时钟信号iclk和时钟启用信号cke来提供相位控制的内部时钟信号lclk。在一个非限制性实例中,dll电路可以用作内部时钟发生器36。相位控制的内部时钟信号lclk被提供给输入/输出电路17,并且用作用于确定读取数据dq的输出时序的时序信号。

[0028]

电源端子25被提供有电源电压vdd1、vdd2和vss。这些电源电压vdd1、vdd2和vss被提供给内部电压发生器电路39。内部电压发生器电路39提供各种内部电压vpp、vary、vperi、veq、vccp、vnwl1和vnwl2。

[0029]

内部电势vccp、vnwl1和vnwl2是待主要在行解码器电路12中使用的电势。行解码器电路12将主字线mwl和子字线swl(基于地址信号add选择)驱动到与高电势(例如,3.1v)相对应的vccp电平,使得存储器单元mc的单元晶体管导通。内部电压vnwl1和vnwl2可以被提供给非作用电势,以在相关联的行被激活或处于预充电状态时在行解码器电路12中使用以下拉子字线swl。

[0030]

内部电势vary和veq是待由感测放大器18、传输门19和/或读取/写入放大器15使用的电势。当感测放大器18被激活时,通过将成对位线中的一个驱动到vary电平而将另一个驱动到vss电平来放大所读出的读取数据。内部电势vperi用作大多数外围电路(例如,命令/地址输入电路31)的电源电势。通过使用相较于外部电势vdd电势更低的内部电势vperi作为这些外围电路的电源电势,可以减少半导体装置10的功耗。

[0031]

电源端子26被提供有电源电压vddq和vssq。这些电源电压vddq和vssq被提供给输

入/输出电路17。电源电压vddq和vssq可以是分别与提供给电源端子25的电源电压vdd2和vss相同的电压。然而,专用电源电压vddq和vssq可以用于输入/输出电路17,使得由输入/输出电路17生成的电源噪声不会传播到装置10的其它电路块。

[0032]

图2是根据本公开的一个实施例的半导体装置的存储器单元阵列的示范性布局的图。在本公开的一些实施例中,存储器单元阵列可以包含在半导体装置10的存储器单元阵列11中(图1)。

[0033]

图2中示出的实例的存储器单元阵列200被划分为十六个存储体,即存储体0到存储体15。可以将行解码器电路(例如,图1的行解码器电路12;图2中未示出)设置在相邻的存储体之间和/或在外围电路区域中。在其它外围电路区域上,可以设置各种外围电路和外部端子(图2中未示出)。

[0034]

图3是根据本公开中描述的一些实例的非作用字线电压控制(iwvc)电路的图。在本公开的一些实施例中,可以在行解码器电路12(在图1中)中实施iwvc电路300。在本公开的一些实施例中,iwvc电路300可以在行解码器电路12的外部实现,或者可以具有包含在行解码器电路12的内部和外部的部分。在一些实例中,iwvc电路300可以包含多个iwvc子电路(例如,304(0)、304(1)、

……

304(n-1)),每个iwvc子电路分别与相应存储体(例如,mc 302(0)、302(1)、

……

、302(n-1))相关联。

[0035]

iwvc子电路(例如,304(0))可以被配置成响应于vnwl控制信号而将关断状态字线电压vnwl1或vnwl2提供给相关联的存储体。在一个非限制性实例中,iwvc子电路(例如,303(0))可以包含复用器(例如,306(0)),其中复用器306(0)耦合到相应存储体(例如,302(0)处的存储体0)。每个复用器306可以具有分别提供vnwl1和vnwl2的第一和第二输入端子并且具有提供vnwl控制信号的控制端子。复用器可以被配置成响应于vnwl控制信号而将vnwl1或vnwl2提供给相关联的存储体。

[0036]

在一些实例中,iwvc子电路(例如,304(0))可以包含时间控制电路308(0),所述时间控制电路308(0)被配置成响应于存储体作用命令(例如,来自命令解码器电路(图1中的34)的存储器act命令)而提供vnwl控制信号。例如,时间控制电路308(0)可以具有使能端子,所述使能端子被提供有来自命令解码器电路的存储器act命令信号。在一些实例中,时间控制电路308(0)可以包含向其提供时钟信号的时钟端子。时钟信号可以由时钟电路提供。示范性时钟电路可以包含振荡器312和分频器310。振荡器312和/或分频器310可以是半导体装置的现有电路。例如,在本公开的一些实施例中,振荡器312可以是已存在于半导体装置中的刷新振荡器。存储器装置中的其它振荡器也是可能的。

[0037]

在一些实例中,时间控制电路308(0)可以是n位计数器,其可以在提供给时间控制电路的act命令信号变为作用状态时被激活。计数器可以被配置成提供持续时间。例如,计数器可以基于在时间控制电路308(0)的时钟端子处提供的时钟信号来进行计数,直至计数达到某一阈值。如上所述,可以将时钟信号提供给振荡器312和分频器310。阈值可以由计数器的时间控制端子处的时间控制信号提供。例如,时间控制信号可以由测试模式熔丝存储体提供,所述测试模式熔丝存储体可以具有多个线以代表阈值的多个位。提供给时间控制电路的时间控制信号和时钟信号限定了持续时间。换句话说,当计数器停止时,从时间控制电路(例如,308(0))接收激活act命令线起已过去了所述持续时间。当所述持续时间过去时,时间控制电路可以提供vnwl控制信号以将vnwl电压提供给存储体。

[0038]

iwvc子电路304(1)至304(n-1)可以类似于先前描述的iwvc子电路304(0)。因此,本文将不详细描述iwvc子电路304(1)至304(n-1)。

[0039]

图4是根据本公开中描述的一些实例的在非作用字线电压控制电路的操作期间的各种信号的时序图400。在本公开的一些实施例中,非作用字线电压控制电路可以被配置为图1中的iwvc 42。在本公开的一些实施例中,非作用字线电压控制电路可被配置为图3的iwvc 300。

[0040]

在图4中示出的实例中,默认vnwl可以处于第一负电压,例如vnwl1。当存储体act命令在上升沿(例如,在时间t1)针对存储体(例如,存储体a)处于作用状态时,与所述存储体耦合的时间控制电路在由时间控制电路(例如,图3中的308)控制的持续时间内被激活。所述持续时间可以由时间控制信号限定。在一个非限制性实例中,时间控制信号可以被设置为使时间控制电路(例如,图3中的308)的持续时间为大约7~10μs。当持续时间到期时,在时间t3,时间控制电路可以提供vnwl控制信号,这使与存储体(例如,存储体a)相关联的复用器选择待提供的减小电压vnwl(例如,vnwl2)。减小电压vnwl2可以是小于默认电压vnwl1的第二负电压。

[0041]

当在时间t6响应于预充电命令而对存储体(例如,存储体a)进行预充电时,vnwl控制信号变为去激活,这使与存储体相关联的复用器选择默认关断状态字线电压vnwl1。在一个非限制性实例中,对于dram存储器装置,vnwl1可以为大约负100mv,vnwl2可以比vnwl1低50-100mv。

[0042]

进一步参考图4,存储体b的iwvc以与存储体a的iwvc相似的方式操作。例如,存储体b的vnwl处于默认电压vnwl1。当存储体act命令在上升沿(例如,在时间t2)针对存储体a处于作用状态时,耦合到存储体的时间控制电路在某一持续时间内被激活。例如,所述持续时间可以由时间控制信号和分频器设置为大约7~10μs。当持续时间到期时,在时间t4,时间控制电路可以生成vnwl控制信号,以使与存储体(例如,存储体b)相关联的复用器选择待提供的减小电压vnwl2。当在时间t5响应于预充电命令而对存储体(例如,存储体b)进行预充电时,vnwl控制可以使与存储体相关联的复用器选择默认vnwl(例如,vnwl1)。在图4中示出的实例中,在将存储体a的vnwl从vnwl2切换/移位到vnwl1之前,将存储体b的vnwl从vnwl2切换/移位到vnwl1。

[0043]

图3和4针对存储体级别的操作示出,但是,关于图3和4描述的实施例也可以应用于子存储体级别。尽管vnwl1和vnwl2被示出为由图1中的电压发生器电路39提供,但是也可以使用其它电压发生器。例如,负半电压(0.5v)发生器可能已包含在存储器装置中,并且可以用于为非作用电势提供减小负电压vnwl2。类似地,默认电压vnwl1可以是减小负电压的1/5,并且也可以从负半电压发生器提供。

[0044]

尽管先前描述了大约7~10μs的示范性持续时间,但是所述持续时间可以更长或更短,而不脱离本公开的范围。在本公开的一些实施例中,所述持续时间长于刷新操作的平均刷新间隔,并且因此,在刷新操作(例如,自动刷新或自刷新操作)期间,vnwl在进行刷新操作的同时不会在默认电压和减小电压之间变化。然而,在本公开的一些实施例中,所述持续时间可以短于平均刷新间隔。

[0045]

图5是根据本公开中描述的一些实例的存储器单元阵列的存储体500的示范性配置的图。在本公开的一些实施例中,图2的存储体(存储体0到存储体15)可以各自包含图5的

存储体500的配置。

[0046]

在一些实例中,存储体500可以包含多个存储器垫区域,例如mat0-3。在图5中示出的实例中,存储体500具有四个存储器垫区域,但是在其它实例中,存储体500可以包含更多或更少的存储器垫区域。如存储器垫区域mat1中的虚线所指示,每个存储器垫区域可以被划分为多个子区域submat1-0-3。尽管图5中示出的实例包含四个子区域,但是在其它实例中,存储器垫区域mat0-3可以包含更多或更少的子区域。每个子区域submat1-0-3可以包含在y方向上对准的多个存储器垫(例如,64个)。为了清楚起见,在图5中未示出各个存储器垫。子字驱动器行swda(图5中未示出)可以在每个存储器垫的x方向上的两侧上,而感测放大器行saa可以在每个存储器垫的y方向上的两侧上。在一些实施例中,每个子区域submat1-0-3的存储器垫可以被提供给相对应的io(例如,dq焊盘)。

[0047]

子字驱动器操作可由行解码器电路(例如,图1的行解码器电路12)控制。当接收行地址ra时,行解码器通过激活由行地址ra指示的适当的主字驱动器(mwd)和适当的字驱动器(fxd)来选择子字线。在图5中示出的实例中,针对主字驱动器mwd示出了一个块,但是,主字驱动器mwd块可以包含多个主字驱动器mwd。类似地,针对字驱动器fxd示出了两个块,但是每个字驱动器fxd块可以包含多个字驱动器fxd。例如,如果每个存储器垫区域mat包含四个子区域,并且每个子区域包含64个存储器垫,则主字驱动器mwd块可以包含128个mwd,每个mwd被配置成激活相对应的主字线(mwl)。继续本实例,每个字驱动器fxd块可以包含八个字驱动器fxd,每个字驱动器fxd被配置成激活相对应的字驱动器线(fx)。在图5中示出的实例中,行地址ra的位3-15编码主字线mwl,而行地址ra的位0-2编码字驱动器线fx。然而,可以使用其它编码方案。

[0048]

图6是根据本公开中描述的一些实例的存储体600的一部分的示意图。在本公开的一些实施例中,图6中示出的存储体600的部分可以包含在图5的存储体500、图2的存储器单元阵列200和/或图1的存储器单元阵列11中。

[0049]

子字线彼此相邻,并且由不同子字驱动器行上的子字驱动器swd0-7驱动。相对应的主字信号mws和驱动信号fx以及非作用电势(例如,关断状态字线电压vnwl)被提供给子字驱动器swd0-7。主字信号和驱动信号fx是可以由行解码器电路12包含的主字驱动器mwd0-n和字驱动器fxd 604基于参考图5描述的行地址ra而提供的信号。主字信号通过主字线(图6中未示出)被提供给子字驱动器swd0-7,而驱动信号fx通过字驱动器线602被提供给子字驱动器swd0-7。

[0050]

主字线mwl可以在相应的存储器垫(例如,图3中的submat1-0中的存储器垫)的阵列区域上延伸,以将主字信号提供给存储器垫的子字驱动器行swd0-7,以激活存储器垫的子字驱动器swd0-7。也就是说,当主字驱动器mwd被激活时,它可以将作用主字信号提供给所述垫的所有子字驱动器swd0-7。如下所述,驱动信号fx包含互补信号fxt和fxf。字驱动器fxd 604的每个字驱动器线602向每个垫中的至少一个子字驱动器swd提供驱动信号fx。在图6中示出的实例中,字驱动器fxd 604包含偶数字驱动器606和奇数字驱动器608。偶数字驱动器606向每个存储器垫的偶数子字驱动器swd0、swd2、swd4和swd6提供相应的驱动信号,而奇数字驱动器608向每个存储器垫的奇数子字驱动器swd1、swd3、swd5和swd7提供相应的驱动信号。然而,在其它实例中,可以使用其它布置。在图6中示出的实例中,字驱动器fxd的每个线可以耦合到每个存储器垫中的相对应的子字驱动器swd0-7。例如,fx线5可以

耦合到每个存储器垫的子字驱动器swd5。

[0051]

在图6中示出的示范性操作中,行地址ra已指示,mwd1应当被激活,并且与字驱动器线fx 5相关联的奇数字驱动器608应当被激活。如阴影区域612所示,与非作用主字驱动器mwd0、mwdn相关联的子字线610保持非作用状态,甚至与字驱动器线fx 5相关联的子字线处于作用状态。然而,由与激活mwd1和fx 5相关联的子字驱动器swd5 616驱动的子字线614被激活。因此,与mwd1相关联的选择存储器垫的选择子字线swl被相对应的激活子字驱动器swd5驱动到作用电势。

[0052]

在一些实例中,选择存储器垫的其它子字驱动器swd将相应的未选择子字线swl驱动到非作用电势(例如,vnwl1、vnwl2)以保持非作用状态。在一些实例中,未选择存储器垫mat(例如,与mwd0和mwdn相关联的存储器垫)的子字驱动器swd保持去激活,并且未选择存储器垫mat的子字线swl未被提供电压,或被提供有非作用电势(例如,vnwl)。尽管子字驱动器swd耦合到字驱动器fxd和主字驱动器mwd,但是为了激活与子字驱动器swd相关联的子字线swl,字驱动器fxd和主字驱动器mwd必须都被激活。

[0053]

图7是根据本公开中描述的一些实例的字驱动器fxd 700的电路图。在一些实施例中,fxd 700可以包含在图5中示出的字驱动器fxd和/或图6中示出的字驱动器604中。在一些实施例中,fxd 700还可以包含在行解码器(例如,图1中的行解码器12)中。在一些实施例中,fxd 700还可以包含在存储器单元阵列(例如,图5中示出的存储器单元阵列500)的外围区域中。针对上下文,还示出了与fxd 700相关联的子字驱动器swd702。在一些实施例中,可以使用swd 702实施图6中示出的子字驱动器swd0-7。

[0054]

在解释fxd 700的细节之前,将描述swd 702。在一些实例中,swd 702可以包含p沟道型晶体管p1和n沟道型晶体管n1和n2。在一些实例中,晶体管p1是p沟道场效应晶体管(pfet),并且晶体管n1和n2是n沟道场效应晶体管(nfet)。晶体管p1和n1可以分别在节点705和707处彼此串联耦合,并且主字信号mws分别被提供给它们的栅电极(例如,栅节点)703和709。驱动信号fxt被提供给晶体管p1的节点701(例如,漏极或源极),而非作用电势vnwl被提供给晶体管n1的节点741(例如,漏极或源极)。晶体管p1和n1的节点705和707(例如,漏极或源极)可以耦合到子字线swl。驱动信号fxf被提供给晶体管n2的栅电极713,其节点711(例如,漏极或源极)连接到子字线swl,并且非作用电势vnwl被提供给其节点715(例如,漏极或源极)。

[0055]

如所述,主字信号mws由主字驱动器mwd提供,而驱动信号fxt和fxf由字驱动器fxd 700提供。图7示出了一个存储体的字驱动器,但是在一些实施例中,字驱动器700还可以在存储器单元阵列中的其它存储体(例如,图1中的11、图3中的302、图5中的500)中实施。此外,在一些实施例中,子字驱动器702可以在存储器单元阵列中的一或多个存储器垫和/或一或多个存储体(例如,图1中的11、图3中的302、图5中的500)中被实施为一或多个子字驱动器。

[0056]

进一步参考图7,当字驱动器fxd被激活时,互补驱动信号fxt和fxf可以变为作用状态(例如,fxt处于高电平(例如,vccp),并且fxf处于低电平(例如,vss))。在一些实例中,主字信号mws可以是作用低值信号。当mws变为作用状态(例如,处于低逻辑电平)时,选择swl。当主字信号mws以及驱动信号fxt和fxf被激活时(例如,mws和fxf为低值,并且fxt为高值),晶体管n1和n2未被激活,但是晶体管p1被激活以为swd提供上拉电压。例如,将相对应

的子字线swl驱动到作为fxt信号的作用电势的vccp电平。

[0057]

相反,当主mws处于作用状态并且驱动信号fxt和fxf处于非作用状态(例如,mws为低值,fxf为高值,并且fxt为低值)时,则p沟道晶体管p1被激活,并且n沟道晶体管n1被激活。fxf的高逻辑电平激活n沟道晶体管n3,因此fxt处于非作用电势(例如,vnwl)。此外,n沟道晶体管n2被激活。p沟道晶体管p1和n沟道晶体管n2二者将使子字线swl被下拉到非作用电势(例如,vnwl)。尽管fxd 700被示出为向一个子字线驱动器swd 702提供驱动信号fxt和fxf,但是fxd 700可以向多个子字驱动器提供驱动信号,例如如参考图5和6所描述。

[0058]

在一些实例中,当mws变为非作用状态(例如,处于逻辑高电平)时,未选择swl。fxf也可以处于非作用状态(例如,处于逻辑高电平)。在这种情况下,晶体管p1和n1都处于非作用状态,并且swl可以被下拉到非作用电势。

[0059]

返回到fx驱动器(例如,fxd 700),可以提供各种控制信号来控制fxd 700的操作。在图7中示出的实例中,fxd 700接收地址信号add、激活信号act。地址信号add可以由地址解码器电路(例如,图1中示出的地址解码器电路32)或刷新控制电路(例如,图1中示出的刷新控制电路16)提供。如图5和6中所示,可以使用行地址位ra0-2来指示八个fx驱动器(例如,fx0-7)中的一个。在一些实例中,fxd 700可以是八个fx驱动器中的一个。在一些实施例中,ra0-2可以是行地址的最高有效位(msb)。因此,在计数器按顺序行地址转变的某些操作(例如,刷新操作)期间,随着对地址位ra3-9、10-12进行计数,由ra0-2指示的fx驱动器保持被选择(例如,地址信号add保持为作用状态)。在已对地址位ra3-9、10-12进行计数之后,可以递增地址位ra0-2,并且地址信号add可以转变到非作用状态以取消选择当前fx驱动器,并且可以选择不同的fx驱动器。

[0060]

激活信号act可以是由命令解码器电路(例如,图1中示出的命令解码器电路34)提供的act命令信号。当与字驱动器fxd相关联的存储体变为作用状态时,激活信号act被提供为作用信号(例如,处于高逻辑电平)。可以将激活信号act提供给电平移位器706以将信号的电压升高到vccp以提供sact信号。act信号和sact信号都具有作用高逻辑电平,但是作用高电平的电压可以不同。在一些实例中,add和sact可以在电平移位器之前为1.2v,并且从电平移位器以3.1v输出。可以将add和sact作为输入提供给输出驱动信号fxf的nand门708。除非add和sact都为高值,否则fxf保持为非作用状态(例如,处于高逻辑电平)。

[0061]

fxd 700可以包含分别在节点721和723处串联耦合的两个p沟道晶体管p2和p3,其中晶体管p3在节点727处与节点729处的n沟道晶体管n3进一步串联耦合。晶体管p2的节点717可以耦合到vccp。fxf被提供给p3的栅极725和n3的栅极731。晶体管p2和n3可以在公共节点727、729处耦合,并且还可以耦合到提供驱动信号fxt的字驱动器线。字驱动器fxd 700可以进一步包含n沟道晶体管n4和n沟道晶体管n3,它们可以并联耦合到非作用电势vnwl。例如,晶体管的源极/漏极可以耦合到公共节点729、735。晶体管n3和n4的另一源极/漏极可以耦合到公共非作用电势。晶体管n3和n4的节点733和739可以分别耦合到非作用电势vnwl。晶体管p2的栅极719和n4的栅极737可以从反相器710接收反相sact信号。

[0062]

除非add和sact都为高值,否则fxd 700可以操作成使得驱动信号fxt以非作用状态被驱动到非作用电势vnwl。例如,如果add为低值(例如,fxd 700不再由地址ra0-2指示),则不管sact的状态如何,fxf和fxt将处于非作用状态(例如,fxf为高值,fxt为低值)。类似地,如果sact为低值,则无论是否选择fxd,fxf和fxt将处于非作用状态。当驱动信号fxt和

fxf处于非作用状态时,并且当mws为作用低值时,p沟道晶体管p1可以被激活,n沟道晶体管n1可以被去激活,并且n沟道晶体管n2可以被激活。p1和n2二者可以将子字线swl下拉到非作用电势vnwl。相反,当add和sact信号都处于作用状态(例如,处于高逻辑电平)时,fxf可以处于低电压。这激活了晶体管p3并且去激活了晶体管n3,并且反相sact信号激活了晶体管p2并且去激活了晶体管n4,使得fxt被驱动到作用电势(例如,vccp)。

[0063]

在预充电操作期间,可以例如由命令解码器电路34(在图1中)提供预充电命令pre。在预充电期间,激活信号act将处于非作用状态,以去激活fxd,使得驱动信号fxt和fxf变为非作用状态。主字信号mws可以处于非作用状态。p沟道晶体管p1将被去激活,n沟道晶体管n1将被激活。n沟道晶体管n2可以被激活。因此,子字线swl经由n沟道晶体管n1和n2被下拉到非作用电势(例如,vnwl)。

[0064]

图8是根据本公开中描述的一些实例的在驱动器电路的操作期间的各种信号的时序图。在本公开的一些实施例中,可以根据时序图800的示范性操作来操作图7的驱动器电路。将参考图7的驱动器电路来描述时序图800。

[0065]

在时间t0左右,选择存储体,由半导体装置接收存储体激活命令。在一些实例中,半导体装置可以是图1的半导体装置10,并且可以包含图7的驱动器电路。在时间t1或其左右,响应于存储体激活命令,激活信号act可以变为作用状态(例如,高逻辑电平),从而指示存储器的作用操作。响应于作用act信号,sact信号转变到高逻辑电平以激活晶体管p2并去激活晶体管n4。假设已选择存储体并且将地址信号add以高逻辑电平提供给存储体,则nand门708提供作用驱动信号fxf(例如,作用低逻辑电平)。作用fxf信号激活晶体管p3并去激活晶体管n3。激活晶体管p2和p3将驱动信号fxt驱动到vccp。fxt和fxf均处于作用状态。

[0066]

如本公开中所描述,当存储器被激活时,根据如图4中示出的示范性时序图,vnwl控制(在图3中)可以在某一持续时间之后针对作用存储体变化为较低的电压。在时间t2或其左右,vnwl控制可以变为作用状态(例如,处于高逻辑电平)。如图8中所示,在某一持续时间之后的vnwl控制的激活可以使非作用电势vnwl从默认vnwl(例如,vnwl1)转变到减小电压vnwl(例如,vnwl2)。如参考图3和4所描述,针对非作用存储体,非作用电势vnwl保持为默认电压(例如,vnwl1)。

[0067]

进一步参考图8,针对激活存储体,如果未选择相关联的swd(例如,mws为非作用低值),则swl可以处于非作用状态并且以其非作用电势vnwl被提供。从默认vnwl变化为减小电压vnwl的vnwl将使非作用swl从默认vnwl变化为减小电压vnwl。例如,在时间t2或其左右,响应于vnwl控制信号的激活,非作用swl也可以从默认非作用电势(例如,vnwl1)转变到减小电压非作用电势(例如,vnwl2)。如果选择了swd(例如,mws为作用低值),则选择swl信号可以随fxt而变化。例如,如果fxt为作用高值(fxf为作用低值),则swl经由晶体管p1(在图7中)被驱动到fxt的作用电势(例如,vccp)。

[0068]

进一步参考图8,可以响应于在时间t3接收的预充电命令而对存储体进行预充电。在时间t4或其左右,响应于存储体预充电命令,激活信号act可以转变到非作用状态(例如,低逻辑电平)。响应于激活信号act变为非作用状态,驱动信号fxf可以变为非作用高值,并且互补驱动信号fxt可以变为非作用低值。随着驱动信号fxf和fxt变为非作用状态,选择swl变为非作用状态。进一步响应于激活信号act变为非作用状态,vnwl控制信号可以变为非作用状态(例如,处于低逻辑电平),如先前在图3和4中所描述。响应于非作用vnwl控制信

号,激活存储体的vnwl可以从减小电压非作用电势(例如,vnwl2)转变到默认非作用电势(例如,vnwl1)。因此,非作用swl(mws为作用低值)的非作用电势vnwl可以响应于vnwl控制信号的去激活而从减小电压vnwl2转变到默认非作用电势vnwl1。类似地,非作用存储体的vnwl可以保持为默认非作用电势(例如,vnwl1)。

[0069]

图1-8中描述的各个实施例提供了以下优点:在act命令变为作用状态之后某一持续时间之后,通过将非作用电势(例如,关断状态字线电压vnwl)切换到减小电压来减少存取装置ioff泄漏。一旦存储器装置处于预充电状态,则可以将关断状态字线电压vnwl恢复到默认负电压。本公开中描述的实施例可以在不损害存储器装置的性能的情况下减少存取装置ioff泄漏。

[0070]

从前述内容可以理解,尽管本文出于说明的目的已描述了本公开的具体实施例,但是可以在不脱离本公开的精神和范围的情况下进行各种改进。因此,本公开的范围不应限于本文描述的任何具体实施例。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。