一种高精度自校irig

‑

b(ac)码调制装置及方法

技术领域

1.本发明属于irig码调制技术领域,涉及irig

‑

b(ac)码调制方法及其装置,尤其是一种高精度自校irig

‑

b(ac)码调制装置及方法。

背景技术:

2.irig码是由美国国防部下属的靶场仪器组指定的一种国际通用的对时标准,irig

‑

b(dc)码是每秒一帧的串行时间码,irig

‑

b(ac)码是将irig

‑

b(dc)码调制到1khz载波上并转换为平衡信号传输的交流时间码。b(ac)码适用于长距、低成本、同步精度要求不高的授时场景,由于线缆传输延时不固定,1pps信号提取不准确导致b(ac)码时间同步精度较低。

3.经检索,未发现与本发明相同或相近似的现有技术的公开文献。

技术实现要素:

4.本发明的目的在于克服现有技术的不足,提出一种高精度自校irig

‑

b(ac)码调制装置及方法,能够提高时统设备b(ac)码授时精度并优化接口的使用性、测试性以及维修性。

5.本发明解决其现实问题是采取了如下技术方案:

6.一种高精度自校irig

‑

b(ac)码调制装置,用于同步卫星导航信号并对外输出相位偏差优于100ns的b(ac)码,包括:卫导信息处理单元、时钟单元、编码单元、解码单元、调制单元、过零检测单元、信号处理单元、信号转换单元、数据采集单元和自校单元;

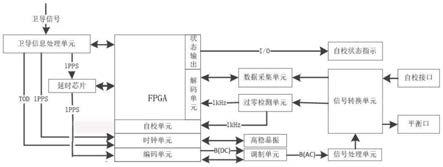

7.所述卫导信息处理单元用于识别多种卫星导航信号并将其转换为1pps tod信号,其输出端与时钟单元相连接,该时钟单元根据卫导信息处理单元输出结果维护本地时间信息;

8.该卫导信息处理单元的1pps输出端通过延时芯片与编码单元相连接,编码单元用于对系统时间进行编码,延时芯片调整输入1pps信号相位,然后由编码单元输出相位调整后的b(dc)码信号;

9.该编码单元的输出端依次与调制单元、信号处理单元与信号转换单元相连接,将b(dc)码调制为b(ac)码并完成信号处理;

10.该信号转换单元对内输出端分别与过零检测单元和数据采集单元相连接,该过零检测单元和数据采集单元的输出端与解码单元相连接,该解码单元用于恢复自校输入b(ac)码中包含的1pps、tod、b(dc)码信号;

11.所述自校单元用于计算补偿链路延时,反馈控制输出b(ac)码相位,保证输出b(ac)码相位精度。

12.而且,所述过零检测单元由高速比较器、非门输出驱动电路组成,输入为信号转换单元输出的参考电压及单端b(ac)码,高速比较器输出b(ac)码过零点对应的1khz脉冲信号,经非门驱动电路后输出至解码单元;

13.而且,所述数据采集单元采集单端b(ac)码信号电压,输出对应于1khz脉冲信号的高、低电平状态至解码单元;

14.而且,所述自校单元用于控制时间间隔测量芯片及延时芯片,测量卫导1pps信号与解码单元恢复1pps信号时间间隔,反馈控制延时芯片延时量,修正编码单元输出的b(dc)码相位。

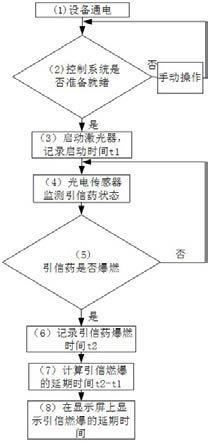

15.一种自校单元b(dc)码输出相位反馈控制方法,如图2所示,包括以下步骤:

16.步骤1、首先差分b(ac)码接入自校接口;

17.步骤2、差分b(ac)码转换为单端信号,经过高速比较器恢复为单端b(ac)码零相位点对应的1khz脉冲;

18.步骤3、控制器检测输入信号格式、脉宽和频率;

19.步骤4、控制器对外输出自校接口信号检测状态;

20.步骤5、解码单元根据1khz脉冲信号控制采样,,根据采样结果恢复1pps、tod、b(dc)码信号;

21.步骤6、时间间隔测量芯片测量恢复1pps信号与卫导1pps信号时间间隔,控制器根据测量结果进行阈值判定;

22.步骤7、完成阈值判定,修正延时芯片参数,若校正过程完成则输出校正完成提示,未完成则调整延时量,返回步骤6;

23.步骤8、流程结束。

24.本发明的优点和有益效果:

25.本发明设计的一种高精度自校irig

‑

b(ac)码调制装置及方法,使用b(ac)码授时前,将输出b(ac)码接入装置自校接口,自校接口监测输入信号并完成解码,装置测量解算1pps信号与卫导1pps信号相位差,通过反馈控制修正b(ac)码输出相位,保证接入用户端的b(ac)码信号相位精度优于100ns。在长距b码授时应用环境下,更换授时线缆后或接口后通过自校接口校正链路延时,提高授时设备使用性和测试性以及维修性,具有较高的实际应用价值。

附图说明

26.图1是本发明的一种高精度自校irig

‑

b(ac)码调制装置的组成原理图;

27.图2是本发明的一种高精度自校irig

‑

b(ac)码调制方法的相位反馈控制流程图。

具体实施方式

28.以下结合附图对本发明实施例作进一步详述:

29.一种高精度自校irig

‑

b(ac)码调制装置,如图1所示,用于同步卫星导航信号并对外输出相位偏差优于100ns的b(ac)码,装置包括:卫导信息处理单元、时钟单元、编码单元、解码单元、调制单元、过零检测单元、信号处理单元、信号转换单元、数据采集单元、自校单元;

30.所述卫导信息处理单元用于识别多种卫星导航信号并将其转换为1pps tod信号,其输出端与时钟单元相连接,该时钟单元根据卫导信息处理单元输出结果维护本地时间信息;

31.该卫导信息处理单元的1pps输出端通过延时芯片与编码单元相连接,编码单元用于对系统时间进行编码,延时芯片调整输入1pps信号相位,然后由编码单元输出相位调整后的b(dc)码信号;该编码单元的输出端依次与调制单元、信号处理单元与信号转换单元相连接,将b(dc)码调制为b(ac)码并完成信号处理;该信号转换单元对内输出端分别与过零检测单元和数据采集单元相连接,该过零检测单元和数据采集单元的输出端与解码单元相连接,该解码单元用于恢复自校输入b(ac)码中包含的1pps、tod、b(dc)码信号;所述自校单元用于计算补偿链路延时,反馈控制输出b(ac)码相位,保证输出b(ac)码相位精度。

32.在本实施例中,所述过零检测单元由高速比较器、非门输出驱动电路组成,输入为信号转换单元输出的参考电压及单端b(ac)码,高速比较器输出b(ac)码过零点对应的1khz脉冲信号,经非门驱动电路后输出至解码单元;

33.在本实施例中,所述数据采集单元采集单端b(ac)码信号电压,输出对应于1khz脉冲信号的高、低电平状态至解码单元;

34.在本实施例中,所述自校单元用于控制时间间隔测量芯片及延时芯片,测量卫导1pps信号与解码单元恢复1pps信号时间间隔,反馈控制延时芯片延时量,修正编码单元输出的b(dc)码相位。

35.下面对装置中各模块的功能和作用作进一步说明:

36.所述卫导信息处理单元,由fpga作为控制器,输入导航卫星接收机信号,卫导信息处理单元将卫导信号进行格式转换,输出1pps和tod信号至时钟单元;

37.所述时钟单元,由fpga作为控制器,输入卫导信息处理单元的1pps、tod信号及高稳晶振频率信号,时钟单元根据输入信号维护本地系统时间,输出同步后的系统时间1pps、tod信号;

38.时钟单元使用卫导1pps信号驯服高稳晶振,根据高稳晶振输出的频率信号维护本地时钟系统,将本地时钟同步至接收机时钟,本地时钟的存储形式为“年”、“月”、“日”、“时”、“分”、“秒”及“纳秒”。

39.所述编码单元,由fpga作为控制器,驱动延时芯片,输入系统时间1pps、tod信号,编码单元按照标准b码格式对系统时间进行编码,由延时芯片调整输入1pps信号相位,然后由编码单元输出延时后的b(dc)码信号;

40.编码单元根据本地时间数据,根据输入1pps信号,将b(dc)码三种码元类型在fpga内部通过“线或”的形式输出至fpga i/o引脚,生成ttl电平标准的b(dc)码;

41.所述调制单元,由fpga作为控制器,输入b(dc)码,驱动双极性da芯片,采用dds直接频率合成技术,将b(dc)码调制到频率为1khz的载波上,输出未校正的单端b(ac)码;

42.调制单元由fpga片上rom、双极性da芯片ltc1821及外围电路组成,将零相位1khz载波数据存入fpga片上rom,在高稳晶振频率信号驱动下,使用地址查询表的形式,结合b(dc)码输入值调整输入da芯片的数字量,由da芯片输出未处理的b(dc)码,未处理的b(dc)码调制比由fpga内部寄存器值确定,可调范围为1:2至1:6;

43.所述信号处理单元,由带通滤波器和放大电路组成,未处理的b(ac)码信号中包含高频、低频噪声,使用中心频率为1khz的带通滤波器,提取载波信号,抑制噪声,然后将处理后信号输入至放大电路,控制器通过放大电路数字电位器调幅,输出调理后的b(ac)码信号;

44.b(ac)码输出端对应的信号转换单元由音频信号差分放大器和隔离变压器组成,音频信号差分放大器将调理后的单端b(ac)码信号转换为平衡信号后输入至隔离变压器,隔离变压器线圈匝数比为1:1,实现输出接口的电磁隔离,变压器从端信号通过平衡口输出;

45.自校接口输入端对应的信号转换单元由隔离变压器和音频线路接收器组成,音频线路接收器将变压器输入的平衡信号转换为单端信号,并将参考电压与单端信号输出至过零检测单元与数据采集单元;

46.所述过零检测单元由高速比较器、外围滞回电路、非门输出驱动电路组成,比较器参考电压为信号转换单元对内输出的参考零位电压,输入为单端b(ac)码,非门驱动电路输出经变阻器反馈至参考电压端形成滞回电路,由非门驱动链路输出b(ac)码零相位点对应的1khz脉冲信号输出至解码单元;

47.所述数据采集单元,由fpga作为控制器,驱动ad采样芯片,采集单端b(ac)码电压信号,输出对应于1khz脉冲信号的高、低电平状态至解码单元;

48.所述解码单元,由fpga作为控制器,输入1khz脉冲信号及采样单元高低电平状态,根据b码解码规则,恢复b(ac)码中包含的1pps、tod、b(dc)码信号;

49.所述解码单元由数据采集单元、fpga内部驱动模块、解码模块、控制模块组成。控制模块由外部1khz零相位点脉冲信号驱动,驱动数据采集单元采集b(ac)码电平,将b(ac)码恢复为b(dc)码,再经解码单元逻辑判断,恢复为1pps、tod、b(dc)码信号;

50.所述自校单元,由fpga作为控制器,控制时间间隔测量芯片及延时芯片,测量卫导1pps信号与解码单元输出1pps信号时间间隔,反馈控制延时芯片延时量,控制输出b(ac)码相位;

51.所述自校单元由延时芯片ds1023、时间间隔测量芯片tdc

‑

gp22及内部阈值判断逻辑组成。fpga驱动时间间隔测量芯片测量解码单元恢复1pps信号和卫导1pps信号时间间隔,获取均值后,判断是否小于100ns阈值,若小于阈值,则认为输出b(ac)码相位精度满足要求,输出自校完成指示,若不满足阈值则调整延时芯片参数,形成相位反馈控制;

52.自校单元通过一种相位反馈控制算法控制b(ac)码输出相位。

53.一种自校单元b(dc)码输出相位反馈控制方法,如图2所示,包括以下步骤:

54.步骤1、首先差分b(ac)码接入自校接口;

55.步骤2、差分b(ac)码转换为单端信号,经过高速比较器恢复为单端b(ac)码零相位点对应的1khz脉冲;

56.步骤3、控制器检测输入信号格式、脉宽和频率;

57.步骤4、控制器对外输出自校接口信号检测状态;

58.步骤5、解码单元根据1khz脉冲信号控制采样,,根据采样结果恢复1pps、tod、b(dc)码信号;

59.步骤6、时间间隔测量芯片测量恢复1pps信号与卫导1pps信号时间间隔,控制器根据测量结果进行阈值判定;

60.步骤7、完成阈值判定,修正延时芯片参数,若校正过程完成则输出校正完成提示,未完成则调整延时量,返回步骤6;

61.步骤8、流程结束。

62.在本实施例中,自校单元进行b(dc)码相位反馈校正过程,fpga内部控制器首先判断自校接口有无b(dc)码信号输入,解码单元对b(dc)码解码,判断完成后输出提示信号,解码成功后,控制器驱动tdc

‑

gp22,每秒测量一次卫导1pps信号与解码1pps信号时间间隔,多次测量后取均值,判断均值与最大值结果是否满足阈值,若结果均小于阈值,则校正成功次数加1,若有一项不满足阈值,则根据测量均值结果修正延时芯片参数,校正成功次数清零,返回时间间隔测量步骤重新判断,若校正成功,则认为输出b(ac)码满足精度要求,输出校正完成提示,完成校正,返回自校接口输入信号判断步骤。

63.本领域内的技术人员应明白,本申请的实施例可提供为方法、系统、或计算机程序产品。因此,本申请可采用完全硬件实施例、完全软件实施例、或结合软件和硬件方面的实施例的形式。而且,本申请可采用在一个或多个其中包含有计算机可用程序代码的计算机可用存储介质(包括但不限于磁盘存储器、cd

‑

rom、光学存储器等)上实施的计算机程序产品的形式。

64.本申请是参照根据本申请实施例的方法、设备(系统)、和计算机程序产品的流程图和/或方框图来描述的。应理解可由计算机程序指令实现流程图和/或方框图中的每一流程和/或方框、以及流程图和/或方框图中的流程和/或方框的结合。可提供这些计算机程序指令到通用计算机、专用计算机、嵌入式处理机或其他可编程数据处理设备的处理器以产生一个机器,使得通过计算机或其他可编程数据处理设备的处理器执行的指令产生用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的装置。

65.这些计算机程序指令也可存储在能引导计算机或其他可编程数据处理设备以特定方式工作的计算机可读存储器中,使得存储在该计算机可读存储器中的指令产生包括指令装置的制造品,该指令装置实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能。

66.这些计算机程序指令也可装载到计算机或其他可编程数据处理设备上,使得在计算机或其他可编程设备上执行一系列操作步骤以产生计算机实现的处理,从而在计算机或其他可编程设备上执行的指令提供用于实现在流程图一个流程或多个流程和/或方框图一个方框或多个方框中指定的功能的步骤。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。