1.本发明涉及实时时钟装置以及电子设备等。

背景技术:

2.公知有根据振荡时钟信号来进行计时从而生成时刻信息的实时时钟装置。在专利文献1中公开了包含实时时钟装置的时刻控制装置。专利文献1的时刻控制装置检测基于从卫星接收的信息而生成的第一时钟信号与由rtc生成的第二时钟信号的误差,在检测出的误差比预定的值大的情况下,对第二时钟信号进行调整。此时,时刻控制装置使用计数器来检测第一时钟信号与第二时钟信号的误差。

3.专利文献1:日本特开2013

‑

55588号公报

4.在上述专利文献1中,使用计数器来检测第一时钟信号与第二时钟信号的误差,因此,基于该误差而被调整的第二时钟信号的精度受到计数器的时间分辨率限制。rtc根据第二时钟信号来进行计时,因此,其计时精度受到计数器的时间分辨率限制。因此,即使存在例如想要生成比计数器的时间分辨率高的分辨率的时刻信息这样的高精度的时刻信息的需求,也存在无法实现该高精度的时刻信息的课题。

技术实现要素:

5.本公开的一个方式涉及实时时钟装置,该实时时钟装置包含:振子;时钟信号生成电路,其具有使所述振子振荡而生成振荡时钟信号的振荡电路,并且该时钟信号生成电路输出基于所述振荡时钟信号的计时用时钟信号;计时电路,其根据所述计时用时钟信号来生成计时数据;外部信号输入端子,向该外部信号输入端子输入外部信号;以及时间数字转换电路,其以比所述计时电路的计时分辨率高的分辨率对基于从所述外部信号输入端子输入的所述外部信号的第一信号的转变定时与基于所述振荡时钟信号或所述计时用时钟信号的第二信号的转变定时的时间差进行测定,求出与所述时间差对应的时间差信息。

附图说明

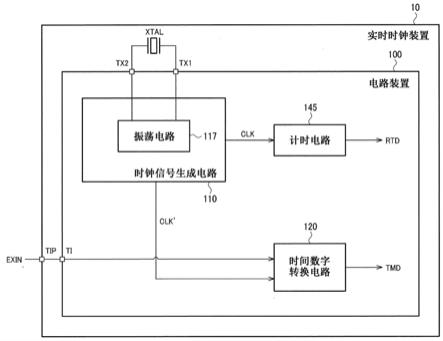

6.图1是实时时钟装置以及电路装置的第一结构例。

7.图2是对实时时钟装置的动作进行说明的波形图。

8.图3是实时时钟装置以及电路装置的第二结构例。

9.图4是时钟信号生成电路的第一详细结构例。

10.图5是电路装置的第三结构例。

11.图6是时钟信号生成电路的第二详细结构例。

12.图7是频率测定电路的详细结构例。

13.图8是对频率测定电路的动作进行说明的波形图。

14.图9是时钟信号生成电路的第三详细结构例。

15.图10是时钟信号生成电路的第四详细结构例。

16.图11是电路装置的第四结构例。

17.图12是使用了gps时刻信号的实时时钟校正系统的结构例。

18.图13是时间数字转换电路的第一详细结构例。

19.图14是对时间数字转换电路的第一详细结构例的动作进行说明的波形图。

20.图15是时间数字转换电路的第二详细结构例。

21.图16是对时间数字转换电路的第二详细结构例的动作进行说明的波形图。

22.图17是电子设备的结构例。

23.标号说明

24.10:实时时钟装置;14:gps接收器;30:测定电路;40:信号生成电路;41、43:积分期间信号生成电路;42、44:极性切换信号生成电路;60:积分处理电路;61~64:积分电路;71、81:环形振荡器;72、82:调整电路;80:计时电路;91:测定电路;92:基准时钟计数器;100:电路装置;110:时钟信号生成电路;111、115、117:振荡电路;112:d/a转换电路;113:驱动电路;114:频率调整电路;118:分频电路;119:分数

‑

n型分频电路;120:时间数字转换电路;130:接口电路;131:存储器接口;145:计时电路;146:时间数据输出电路;147:触发控制器;150:处理电路;160:存储器;175:分频电路;190:频率测定电路;191:计数器电路;192:运算电路;193:第一计数器;194:第二计数器;200:处理装置;500:电子设备;510:通信接口;520:处理装置;530:操作界面;540:显示部;550:存储器;clk:计时用时钟信号;cntm、cntt:计数数据;dq:输出信息;exin:外部信号;fad:频率调整信号;fntd:时间数据;frd:频率信息;osck:振荡时钟信号;rtd:计时数据;sta:第一信号;stp:第二信号;tfp:接口端子;tip:外部信号输入端子;tmd:时间差信息;xtal:振子。

具体实施方式

25.以下,对本公开的优选的实施方式进行详细说明。另外,以下说明的本实施方式并不是对权利要求书所记载的内容进行不当限定,在本实施方式中说明的结构未必全部都是必需的构成要件。

26.1.第一结构例

27.图1是实时时钟装置10以及电路装置100的第一结构例。实时时钟装置10包含电路装置100、振子xtal以及端子tip。tip是外部信号输入端子。

28.电路装置100通过生成计时数据rtd并且进行分辨率比该计时数据rtd的时间分辨率高的时间计测,实现高精度的实时时钟。电路装置100是被称为ic(integrated circuit)的集成电路装置。电路装置100是通过半导体工艺制造的ic,是在半导体基板上形成有电路元件的半导体芯片。

29.振子xtal是通过电信号产生机械振动的元件。振子xtal能够由石英振动片等振动片实现。例如,振子xtal能够通过切角为at切或sc切等的厚度切变振动的石英振动片等实现。

30.另外,本实施方式的振子xtal例如能够通过厚度切变振动型以外的振动片或由石英以外的材料形成的压电振动片等各种振动片实现。例如,作为振子xtal,也可以采用saw谐振器或者使用硅基板形成的作为硅制振子的mems振子。saw是surface acoustic wave(表面声波)的缩写,mems是micro electro mechanical systems(微机电系统)的缩写。

31.电路装置100和振子xtal电连接,该电路装置100和振子xtal例如被收纳在封装中。封装由收纳电路装置100和振子xtal的容器以及设置于容器的外部连接用的端子tip构成。容器例如是陶瓷制容器或金属制容器,但并不限于此。端子tip是设置于容器外侧的金属制的引线或凸块等。另外,本实施方式的连接是电连接。电连接是指能够传递电信号的连接,是能够通过电信号传递信息的连接。电连接也可以是经由无源元件或有源元件等的连接。

32.电路装置100包含时钟信号生成电路110、时间数字转换电路120、计时电路145以及端子tx1、tx2、ti。

33.端子tx1、tx2、ti是形成在半导体基板上的连接盘。端子tx1与振子xtal的一端连接,端子tx2与振子xtal的另一端连接。端子ti与实时时钟装置10的端子tip连接。这些连接如上述那样是电连接,例如由封装内布线、线接合或金属凸块实现。

34.时钟信号生成电路110包含振荡电路117。振荡电路117经由端子tx1、tx2而与振子xtal电连接,使该振子xtal振荡而生成振荡时钟信号。时钟信号生成电路110输出基于振荡时钟信号的计时用时钟信号clk。例如,时钟信号生成电路110也可以包含对振荡时钟信号进行缓冲并作为计时用时钟信号clk输出的输出电路、或者对振荡时钟信号进行分频并作为计时用时钟信号clk输出的分频电路。

35.计时电路145根据计时用时钟信号clk来生成计时数据rtd。计时数据rtd是时间信息,是表示当前时刻的数字值。计时数据rtd例如是将相当于计时分辨率的时间作为1lsb而对时间进行计数得到的计数数据。或者,计时数据rtd也可以是表示秒、分、时、日、月、年等的数据。计时电路80包含根据计时用时钟信号clk来进行计数处理的计数器。计数器对计时用时钟信号clk或其分频时钟信号进行计数,并根据其计数值来输出计时数据rtd。即,由计数器计数的计时用时钟信号clk或其分频时钟信号的周期相当于计时分辨率。

36.从实时时钟装置10的外部向端子tip输入外部信号exin。外部信号exin是在第一电压电平与第二电压电平之间转变的信号。外部信号exin可以是周期性转变的信号,也可以是不定期转变的信号,作为外部信号exin,可以设想时钟信号、脉冲信号或触发信号等。例如,外部信号exin可以是从gnss或网络的接收器输入的时刻信号,或者也可以是从检测事件发生的检测电路输入的事件信号。在gnss为gps的情况下,外部信号exin为1pps信号。另外,gnss是global navigation satellite system(全球导航卫星系统)的缩写,gps是global positioning system(全球定位系统)的缩写。

37.从端子tip经由端子ti向时间数字转换电路120输入外部信号exin,从时钟信号生成电路110向时间数字转换电路120输入时钟信号clk’。时间数字转换电路120测定基于外部信号exin的第一信号的转变定时与基于时钟信号clk’的第二信号的转变定时的时间差,求出与该时间差对应的时间差信息tmd。时钟信号clk’只要是计时用时钟信号clk或其上游的时钟信号即可。即,时钟信号clk’是振荡时钟信号、或振荡时钟信号的分频时钟信号、或计时用时钟信号clk。第一信号是其转变定时基于外部信号exin的转变定时而确定的信号。例如,第一信号可以是外部信号exin本身,也可以是外部信号exin被分频后的信号,还可以是在外部信号exin的转变定时处锁存了低电平或高电平的信号。第二信号是其转变定时根据时钟信号clk’的转变定时而确定的信号。例如,第二信号可以是时钟信号clk’本身,也可以是时钟信号clk’被分频后的信号,还可以是在时钟信号clk’的转变定时处锁存了低电平

或高电平的信号。另外,转变定时是指信号的电压电平发生变化的定时,是信号的上升沿或下降沿。

38.图2是对实时时钟装置10的动作进行说明的波形图。在图2中,图示了外部信号exin是周期性的脉冲信号,时钟信号clk’是计时用时钟信号clk的情况。

39.计时电路145利用计时用时钟信号clk进行计时,并与计时用时钟信号clk的各转变定时对应地输出计时数据drt1、drt2、drt3。由于利用计时用时钟信号clk进行计时,所以计时用时钟信号clk的周期δtrt为计时分辨率。时间数字转换电路120测定外部信号exin的转变定时与计时用时钟信号clk的转变定时的时间差。该测定是在外部信号exin的各转变定时处进行的,按时间序列测定时间差tdf1、tdf2、tdf3。该时间差tdf1~tdf3比计时用时钟信号clk的周期δtrt短。即,时间数字转换电路120按照比计时分辨率高的分辨率进行时间测定。

40.根据本实施方式,通过实时时钟装置10包含时间数字转换电路120,能够取得分辨率比计时电路145的计时分辨率高的时间差信息tmd。即,计时电路145进行使用了计时用时钟信号clk的计数处理,但能够在不被该计数处理的时间分辨率限制的情况下,取得时间差信息tmd。由此,能够实现高精度的实时时钟装置。关于具体的实时时钟装置10的应用例,在后面进行叙述,但例如在外部信号exin是事件信号等触发信号的情况下,能够以比计时电路145的计时精度高的精度求出该触发输入发生的时刻。或者,在外部信号exin是基准时钟信号的情况下,能够以比计时电路145的计时精度高的精度求出基准时钟信号与计时用时钟信号clk的相位差,使用其结果来进行计时用时钟信号clk的频率校正等,能够提高计时精度。

41.并且,在本实施方式中,时钟信号生成电路110、计时电路145以及时间数字转换电路120设置于1个半导体基板。由此,与将时钟信号生成电路110、计时电路145以及时间数字转换电路120构成为不同的ic的情况相比,能够抑制作为测定对象的信号的延迟或波形变形等,因此,能够准确地测定外部信号exin与计时用时钟信号clk的转变定时的时间差。由此,能够实现高精度的实时时钟装置。

42.2.第二结构例

43.图3是实时时钟装置10以及电路装置100的第二结构例。实时时钟装置10包含振子xtal、电路装置100以及端子tip、tfp。端子tfp是接口端子。电路装置100包含时钟信号生成电路110、时间数字转换电路120、接口电路130、计时电路145、时间数据输出电路146、触发控制器147以及端子ti、tf。另外,对与已经说明的构成要素相同的结构要素标注相同的标号,并适当省略该结构要素的说明。

44.在第二结构例中,外部信号exin是触发信号。触发信号是将与其转变定时对应的时间数据的取得向实时时钟装置10进行指示的信号。触发信号是从事件检测电路输入的事件检测信号或者外部的处理装置对实时时钟装置10请求时间数据的信号等。触发控制器147根据作为外部信号exin的触发信号来输出第一信号trg。触发控制器147例如进行外部信号exin的波形成形,并输出在外部信号exin的转变定时处转变的第一信号trg。

45.时间数字转换电路120测定第一信号trg与作为第二信号的计时用时钟信号clk的转变定时的时间差,并输出表示该时间差的时间差信息tmd。在本结构例中,计时用时钟信号clk相当于图1的时钟信号clk’。

46.时间数据输出电路146根据计时数据rtd和时间差信息tmd,输出比计时分辨率高的分辨率的时间数据fntd。时间数据fntd是时间戳信息,时间戳信息表示作为外部信号exin输入的触发信号的转变定时。时间数据输出电路146可以将计时数据rtd和时间差信息tmd作为时间数据fntd来输出,或者也可以根据时间差信息tmd对计时数据rtd进行校正,将该校正后的数据作为时间数据fntd来输出。例如,在图2的外部信号exin是触发信号的情况下,触发信号的转变定时的时间为drt1

‑

tdf1、drt2

‑

tdf2、drt3

‑

tdf3。时间数据输出电路146也可以将drt1和tdf1、drt2和tdf1、drt3和tdf1作为时间数据fntd来输出。或者,时间数据输出电路146也可以运算drt1

‑

tdf1、drt2

‑

tdf2、drt3

‑

tdf3,并将它们作为时间数据fntd来输出。

47.接口电路130将基于计时数据rtd和时间差信息tmd的输出信息dq经由端子tf、tfp向实时时钟装置10的外部输出。在第二结构例中,接口电路130将时间数据fntd作为输出信息dq来输出。

48.另外,接口电路130经由端子tf、tfp来进行设置于实时时钟装置10的外部的处理装置与实时时钟装置10的通信。端子tf是形成在半导体基板上的连接盘。端子tfp是设置于封装的容器外侧的金属制的引线或凸块等。端子tf与端子tfp电连接,该连接例如由封装内布线、线接合、金属凸块实现。作为接口电路130的通信方式,可以采用串行通信或并行通信的各种通信方式。作为串行通信的方式,例如有spi或i2c。spi是3线或4线的串行通信,使用片选信号、时钟信号以及数据信号来进行通信。i2c是2线的串行通信,使用时钟信号和数据信号来进行通信。另外,spi是serial peripheral interface的缩写,i2c是inter

‑

integrated circuit的缩写。另外,在图3中,作为接口端子,图示了1组端子tf、tfp,但并不限于此,也可以根据接口电路130的通信形式而设置多组接口端子。

49.图4是时钟信号生成电路110的第一详细结构例。时钟信号生成电路110包含振荡电路115和分频电路118。振荡电路115相当于图3的振荡电路117。

50.振荡电路115通过使振子xtal振荡而生成振荡时钟信号osck。作为振荡电路115,可以使用皮尔斯型、考毕兹型、反相式或哈特莱型等各种类型的振荡电路。分频电路118对振荡时钟信号osck进行分频,并将该分频时钟信号作为计时用时钟信号clk而输出到计时电路145。向时间数字转换电路120输入计时用时钟信号clk。另外,图3的时钟信号生成电路110并不限于图4的结构。例如,也可以省略图4的分频电路118,将振荡时钟信号osck作为计时用时钟信号clk输入到计时电路145和时间数字转换电路120。

51.3.第三结构例

52.图5是电路装置100的第三结构例。电路装置100包含时钟信号生成电路110、接口电路130、计时电路145、分频电路175、频率测定电路190以及端子ti、tf。另外,对与已经说明的结构要素相同的结构要素标注相同的标号,适当省略该结构要素的说明。

53.向端子tip输入外部时钟信号来作为外部信号exin。外部时钟信号例如是从gnss或网络的接收器输入的时刻信号,或者是从振荡器等基准时钟源输入的基准时钟信号。分频电路175对作为外部信号exin的外部时钟信号进行分频,将通过该分频得到的分频时钟信号ckex输出到频率测定电路190。另外,也可以省略分频电路175,将外部时钟信号输入到频率测定电路190。

54.频率测定电路190根据时钟信号clk’的频率来测定外部时钟信号的频率,从而求

出与外部时钟信号的频率对应的频率信息frd。在图5中,频率测定电路190通过测定分频时钟信号ckex的频率来实质上测定外部时钟信号的频率。频率信息frd是表示频率的信息,具体而言是频率被编码后的数字值。频率信息frd是以时钟信号clk’的频率为基准的、相对的外部时钟信号或其分频时钟信号的频率。例如,在图5中,频率信息frd是以时钟信号clk’的频率为基准的分频时钟信号ckex的频率。

55.频率测定电路190包含时间数字转换电路120。时间数字转换电路120测定基于外部时钟信号的第一信号与基于时钟信号clk’的第二信号的转变定时的时间差,在后面进行详细叙述。频率测定电路190通过使用由时间数字转换电路120输出的时间差信息tmd,能够以比时钟信号clk’的周期高的时间分辨率测定外部时钟信号的周期,并且能够根据该周期来实现高精度的频率测定。

56.接口电路130输出计时数据rtd和频率信息frd来作为输出信息dq。处理装置200接收输出信息dq中的至少频率信息frd。处理装置200根据频率信息frd来生成频率调整信号fad,并将该频率调整信号fad输出到实时时钟装置10。接口电路130将接收到的频率调整信号fad输出到时钟信号生成电路110。时钟信号生成电路110根据频率调整信号fad对计时用时钟信号clk的频率进行调整。频率调整信号fad例如是数字信号的频率调整数据,但也可以是模拟信号的频率调整电压。

57.处理装置200是处理器,处理器例如是微型计算机、cpu或dsp。处理装置200通过进行使用了频率信息frd的信号处理来生成频率调整信号fad。如上述那样,频率信息frd表示外部时钟信号与时钟信号clk’的频率比。处理装置200生成使该频率比为目标值那样的频率调整信号fad。由此,得到相对于外部时钟信号以规定的频率比进行频率同步的计时用时钟信号clk,通过计时电路145使用该计时用时钟信号clk进行计时,能够实现高精度的实时时钟。

58.图6是时钟信号生成电路110的第二详细结构例。时钟信号生成电路110包含振荡电路115、分频电路118以及选择器sel。

59.分频电路118输出以互相不同的分频比对振荡时钟信号osck进行分频而得的分频时钟信号cka~ckc和计时用时钟信号clk。选择器sel选择振荡时钟信号osck、分频时钟信号cka、ckb、ckc或计时用时钟信号clk中的任意一个来作为时钟信号clk’并将其输出到时间数字转换电路120。另外,也可以构成为省略选择器sel,将振荡时钟信号osck或分频时钟信号cka、ckb、ckc中的任意一方作为时钟信号clk’而输入到时间数字转换电路120。

60.图7是频率测定电路190的详细结构例。频率测定电路190包含时间数字转换电路120、计数器电路191以及运算电路192。

61.时间数字转换电路120测定基于分频时钟信号ckex的第一信号sta的转变定时与基于时钟信号clk’的第二信号stp的转变定时的时间差,并求出与该时间差对应的时间差信息tmd。另外,由于分频时钟信号ckex是外部时钟信号的分频时钟信号,所以第一信号sta是基于外部时钟信号的信号。第一信号sta和第二信号stp从计数器电路191输入到时间数字转换电路120。关于第一信号sta和第二信号stp的详细内容,在后面进行叙述。

62.计数器电路191进行基于分频时钟信号ckex和时钟信号clk’的计数处理,输出通过计数处理而得到的计数数据cntm、cntt。具体来说,计数器电路191包含第一计数器193和第二计数器194。第一计数器193进行基于分频时钟信号ckex的计数处理,输出计数数据

cntm。第二计数器194进行基于时钟信号clk’的计数处理,输出计数数据cntt。

63.运算电路192通过进行基于时间差信息tmd和计数数据cntm、cntt的运算来求出频率信息frd。计数数据cntm相当于以分频时钟信号ckex的周期为分辨率的时间,计数数据cntt相当于以时钟信号clk’的周期为分辨率的时间。除此之外,运算电路192通过使用以比时钟周期小的时间分辨率测定出的时间差信息tmd,能够准确地确定以时钟信号clk’的周期为基准的分频时钟信号ckex的周期。频率可以通过周期的倒数来求出。

64.图8是对频率测定电路190的动作进行说明的波形图。在图8中,图示了第一信号sta是开始信号,第二信号stp是停止信号的情况。并且,这里,将转变定时设为上升沿的定时。

65.第一计数器193对分频时钟信号ckex的脉冲数进行计数,按照nm 1计数周期使第一信号sta发生转变。第一计数器193输出计数值nm来作为计数数据cntm。nm是规定计数值,例如可以预先设定,或者也可以通过寄存器设定来设定。

66.具体来说,第一计数器193在分频时钟信号ckex的转变定时处将计数值复位为“0”,并且使第一信号sta从低电平转变为高电平。第一计数器193将分频时钟信号ckex的脉冲数计数到计数值nm,再次在分频时钟信号ckex的转变定时处将计数值复位为“0”,并且使第一信号sta从低电平转变为高电平。第一信号sta例如仅在分频时钟信号ckex的1个周期内成为高电平,但该周期数可以是任意的。

67.在第一信号sta发生转变之后,第二计数器194在时钟信号clk’的转变定时处使第二信号stp发生转变。在从第二信号stp发生转变起到下一次第二信号stp发生转变的期间内,第二计数器194对时钟信号clk’的脉冲数进行计数,并将其计数值nt作为计数数据cntt来输出。

68.具体来说,在第一信号sta从低电平转变为高电平之后,第二计数器194在时钟信号clk’的第2个下降沿处使信号flgm从低电平转变为高电平,并在下一个时钟信号clk’的下降沿处使信号flgm从高电平转变为低电平。信号flgm是第二计数器194的内部信号。在信号flgm为高电平时,第二计数器194在时钟信号clk’的上升沿处使第二信号stp从低电平转变为高电平。

69.在使第二信号stp从低电平转变为高电平的定时处,第二计数器194使计数值复位为“0”。第二计数器194在下一次使第二信号stp转变为高电平的定时之前对时钟信号clk’的脉冲数进行计数,并将此时的计数值nt作为计数数据cntt来输出。

70.时间数字转换电路120测定第一信号sta的转变定时与第二信号的转变定时的时间差。由于第一信号sta周期性地发生转变,所以与该各转变定时对应地测定时间差。将该时间序列的时间差设为tp1、tp2。

71.时间数字转换电路120输出表示时间差tp1、tp2的时间差信息tmd。

72.运算电路192通过下式(1)和(2)来求出分频时钟信号ckex的频率fm。t0为时钟信号clk’的周期,是已知的值。tm为分频时钟信号ckex的周期,其倒数为频率fm。另外,时钟信号clk’的周期t0是已知的,但不过是作为理想值而已知的,实际上由于振荡频率的偏差等,t0与理想值不同。在这一点上,实际的t0是未知的,可以说相对于该未知的时钟信号clk’的频率的相对的分频时钟信号ckex的频率比被测定为fm。

73.【数学式1】

[0074][0075]

【数学式2】

[0076][0077]

根据本实施方式,计数器电路191以时钟信号clk’的周期t0为基准来测定分频时钟信号ckex的周期tm,但时间数字转换电路120进一步以比周期t0小的分辨率测定时间差tp1、tp2。由此,运算电路192能够以比周期t0小的分辨率运算分频时钟信号ckex的周期tm,能够求出准确的分频时钟信号ckex的频率fm。

[0078]

图9是时钟信号生成电路110的第三详细结构例。时钟信号生成电路110包含振荡电路111和分频电路118。振荡电路111相当于图5的振荡电路117。

[0079]

振荡电路111是根据数字信号的频率调整信号fad来控制振荡频率的dcxo。dcxo是digital controlled xtal oscillator(数字补偿晶体振荡器)的缩写。振荡电路111通过使振子xtal振荡而生成振荡时钟信号osck,并根据频率调整信号fad对振荡时钟信号osck的频率进行调整。具体来说,振荡电路111包含驱动电路113和频率调整电路114。

[0080]

驱动电路113经由端子tx1、tx2而与振子xtal电连接,通过对振子xtal进行驱动而使振子xtal振荡,从而输出振荡时钟信号osck。

[0081]

频率调整电路114与将端子tx1或端子tx2和驱动电路113连接起来的节点连接,根据频率调整信号fad对振荡频率进行调整。另外,在图9中,图示了频率调整电路114与将端子tx2和驱动电路113连接起来的节点连接的情况。频率调整电路114包含d/a转换电路112和可变电容电容器cv。d/a转换电路112对频率调整信号fad进行d/a转换,将通过该d/a转换得到的电压daq输出到可变电容电容器cv的一端。可变电容电容器cv的另一端与将端子tx2和驱动电路113连接起来的节点连接。可变电容电容器cv是电容值根据两端的电压而变化的电容器,例如是mos电容器或可变电容二极管。

[0082]

分频电路118对振荡时钟信号osck进行分频,并将该分频得到的时钟信号作为计时用时钟信号clk来输出。输入到时间数字转换电路120的时钟信号clk’是计时用时钟信号clk。

[0083]

根据本实施方式,由于可变电容电容器cv的一端的电压daq根据频率调整信号fad而发生变化,所以可变电容电容器cv的电容值根据频率调整信号fad而变化。由此,对振子xtal进行驱动的驱动电路113的电容负载发生变化,因此,振荡时钟信号osck的频率根据频率调整信号fad而发生变化。由此,实现基于频率调整信号fad的计时用时钟信号clk的频率调整。

[0084]

另外,振荡电路111的结构并不限于图9。例如,在频率调整信号fad是数字信号的情况下,频率调整电路114也可以是电容器阵列。电容器阵列是通过基于频率调整信号fad的开关切换来可变地切换电容值的可变电容电路。电容器阵列的一端与地连接,另一端与将端子tx1或端子tx2和驱动电路113连接起来的节点连接。

[0085]

或者,在频率调整信号fad是模拟信号的情况下,振荡电路111也可以是vco。vco是voltage controlled oscillator(电压控制振荡器)的缩写。即,只要从图9的振荡电路111省略d/a转换电路112并将模拟信号的频率调整信号fad输入到可变电容电容器cv的一端即

可。

[0086]

图10是时钟信号生成电路110的第四详细结构例。时钟信号生成电路110包含振荡电路115和分数

‑

n型分频电路119。振荡电路115相当于图5的振荡电路117。由于振荡电路115如在图4中说明的那样,所以省略其说明。

[0087]

分数

‑

n型分频电路119根据作为数字信号的频率调整信号fad,以小数分频比对振荡时钟信号osck进行分频。具体来说,分数

‑

n型分频电路119包含分频电路fpd和分频比设定电路fpe。

[0088]

分频比设定电路fpe根据频率调整信号fad来设定小数的分频比,并将该分频比的信息输出到分频电路fpd。分频电路fpd按照由分频比的信息指示的分频比对振荡时钟信号osck进行分频,并将该分频时钟信号作为计时用时钟信号clk来输出。具体来说,分频比设定电路fpe通过使整数分频比按时间序列变化,从而设定时间平均为小数的分频比。分频电路fpd以整数分频比对振荡时钟信号osck进行分频,但由于该整数分频比按时间序列发生变化,所以从时间平均来看是以小数分频比对振荡时钟信号osck进行分频。分频比设定电路fpe例如是通过对频率调整信号fad进行δ∑调制而生成小数分频比的δ∑调制电路。另外,向时间数字转换电路120输入振荡时钟信号osck作为时钟信号clk’。

[0089]

根据本实施方式,分数

‑

n型分频电路119的小数分频比根据频率调整信号fad而发生变化。由此,实现基于频率调整信号fad的计时用时钟信号clk的频率调整。

[0090]

4.第四结构例

[0091]

图11是电路装置100的第四结构例。电路装置100包含时钟信号生成电路110、接口电路130、计时电路145、处理电路150、存储器160、分频电路175、频率测定电路190以及端子ti、tf。另外对与已经说明的结构要素相同的结构要素标注相同的标号,适当省略该结构要素的说明。

[0092]

在第四结构例中,接口电路130将来自计时电路145的计时数据rtd作为输出信号而输出到实时时钟装置10的外部。频率信息frd被输入到处理电路150,处理电路150生成与频率信息frd对应的频率调整信号fad。时钟信号生成电路110根据频率调整信号fad对计时用时钟信号clk的频率进行调整。处理电路150生成频率调整信号fad的方法与在图5中说明的处理装置200生成频率调整信号fad的方法相同。处理电路150是处理器,处理器例如是微型计算机、cpu核或dsp。包含处理电路150的电路装置100是集成电路装置。即,处理电路150和存储器160与时钟信号生成电路110、计时电路145、频率测定电路190以及接口电路130一起设置于1个集成电路装置。

[0093]

存储器160存储用于使处理电路150根据频率信息frd来生成频率调整信号fad的程序。处理电路150通过执行存储于存储器160的程序,根据频率信息frd来生成频率调整信号fad。存储器160是非易失性存储器或ram等半导体存储器。

[0094]

接口电路130包含用于从实时时钟装置10的外部访问存储器160的存储器接口131。存储器接口131将接口电路130从实时时钟装置10的外部接收的程序写入到存储器160。并且,存储器接口131也可以读出存储于存储器160的信息,接口电路130将该信息发送到实时时钟装置10的外部。

[0095]

根据本实施方式,用户能够经由存储器接口131向存储器160写入各种程序,通过该程序,能够实现使用了频率信息frd的各种信号处理。并且,通过将处理电路150内置于电

路装置100,不需要将用于进行使用了频率信息frd的信号处理的处理装置设置于实时时钟装置10的外部。即,在实时时钟装置10单体中,能够实现使用了频率信息frd的各种信号处理。

[0096]

5.第五结构例

[0097]

图12是使用了gps时刻信号的实时时钟校正系统的结构例。图12的系统包含gps接收器14、实时时钟装置10以及处理装置200。另外,在图12中,在实时时钟装置10中仅图示了电路装置100的内部结构和振子xtal。并且,省略端子的图示。

[0098]

gps接收器14接收gps卫星信号,将1pps信号作为外部信号exin而输出到实时时钟装置10。1pps是作为时刻基准的信号,是1hz的脉冲信号。

[0099]

频率测定电路190以振荡时钟信号osck为基准来测定作为外部信号exin的1pps信号的频率,并输出频率信息frd。当将振荡时钟信号osck的频率设为f0并将1pps的频率设为fref时,频率信息frd表示为fref/f0。在1pps的各转变定时处测定fref/f0,输出表示其时间序列的fref/f0的频率信息frd。接口电路130将频率信息frd输出到处理装置200。

[0100]

处理装置200包含低通滤波器lpfs。低通滤波器lpfs对表示时间序列的fref/f0的频率信息frd进行低通滤波处理,并输出由此得到的频率调整信号fad。频率调整信号fad是表示通过低通滤波处理而被平滑化的fref/f0的数据。处理装置200将频率调整信号fad输出到实时时钟装置10。

[0101]

接口电路130将接收到的频率调整信号fad输出到时钟信号生成电路110的分数

‑

n型分频电路119。分数

‑

n型分频电路119以分频比fref/f0对振荡时钟信号osck进行分频,并输出计时用时钟信号clk。由于振荡时钟信号osck的频率为f0,所以计时用时钟信号clk的频率为fref。这样,能够使计时用时钟信号clk的频率与1pps的频率fref频率同步,计时电路145能够根据与该1pps同等的计时用时钟信号clk来进行计时。由此,能够实现高精度的实时时钟。

[0102]

6.时间数字转换电路

[0103]

使用图13~图16对时间数字转换电路120的详细结构例进行说明。另外,在将图13~图16的时间数字转换电路120应用于图3的情况下,第一信号sta与图3的trg对应。并且,时间数字转换电路120还可以包含根据时钟信号clk’来输出第二信号stp的电路。该电路例如输出在第一信号sta发生转变后的时钟信号clk’的转变定时处转变的第二信号stp。

[0104]

图13是时间数字转换电路120的第一详细结构例。时间数字转换电路120包含测定电路30、信号生成电路40以及积分处理电路60。

[0105]

信号生成电路40根据第一信号sta、第二信号stp以及时钟信号clk’,生成用于积分处理的信号。在第一详细结构例中,使用时钟信号clk’来作为成为时间测定的基准的基准时钟信号。信号生成电路40包含积分期间信号生成电路41、43和极性切换信号生成电路42、44。

[0106]

积分期间信号生成电路41根据第一信号sta来生成信号sint1。

[0107]

极性切换信号生成电路42根据信号sint1和时钟信号clk’来生成信号sph1、sph2。积分期间信号生成电路43根据第二信号stp来生成信号sint2。极性切换信号生成电路44根据信号sint2和时钟信号clk’来生成信号sph3、sph4。信号sint1、sint是积分期间信号,信号sph1、sph2、sph3、sph4是积分极性切换信号。

[0108]

积分处理电路60通过进行基于信号sint1、sph1、sph2、sint2、sph3、sph4的积分处理,输出作为第一~第四积分值的电压qa1~qa4。电压qa1、qa2表示与第一信号sta和时钟信号clk’的转变定时的时间差对应的相位。电压qa3、qa4表示与第二信号stp和时钟信号clk’的转变定时的时间差对应的相位。积分处理电路60包含积分电路61~64。

[0109]

积分电路61根据信号sint1、sph1来进行第一积分处理。积分电路62根据信号sint1、sph2来进行第二积分处理。积分电路63根据信号sint2、sph3来进行第三积分处理。积分电路64根据信号sint2、sph4来进行第四积分处理。

[0110]

测定电路30对作为第一~第四积分处理的结果的电压qa1~qa4分别进行a/d转换,并根据其a/d转换值来运算时间差信息tmd。时间差信息tmd表示第一信号sta与第二信号stp的转变定时的时间差。

[0111]

图14是对时间数字转换电路120的第一详细结构例的动作进行说明的波形图。这里,以求出表示第一信号sta的相位的电压qa1、qa2的动作为例来进行说明。

[0112]

积分期间信号生成电路41在第一信号sta的转变定时处使信号sint1从低电平转变为高电平,在积分期间tp1内将信号sint1维持为高电平,然后,使信号sint1为低电平。积分期间tp1的时长只要是时钟信号clk’的周期的4倍以上即可,也可以不是时钟信号clk’的周期的整数倍。

[0113]

第一信号sta的相位的检测范围rdet相当于时钟信号clk’的1个周期。在第一信号sta发生转变时,其转变定时所属的时钟信号clk’的周期为检测范围rdet。

[0114]

在积分期间tp1内,极性切换信号生成电路42在与时钟信号clk’同步的定时处使信号sph1从低电平转变为高电平。信号sph1的转变定时与检测范围rdet内的从时钟信号clk’的上升沿起经过了时钟数pci后的上升沿同步。时钟数pci可以任意设定。在图13中,pci=6。

[0115]

将信号sph1的转变定时视为相位的基准、即0度。这相当于在第一信号sta的转变定时与时钟信号clk’的上升沿一致时将第一信号sta的相位视为0度。在图14中,积分期间tp1的时长相当于时钟信号clk’的24个周期。当将该积分期间tp1视为相位360度时,时钟信号clk’的1个周期相当于相位15度。在图14的时钟信号clk’的各脉冲中,以信号sph1的转变定时为基准“0”来标注编号,当编号相差1时,相位相差15度。

[0116]

在积分期间tp1内,极性切换信号生成电路42在从信号sph1的转变定时起经过了时钟信号clk’的时钟数nck后使信号sph2从低电平转变为高电平。在图14中,nck=6,信号sph1与信号sph2的相位相差90度。这相当于获得相位偏移了90度的2个积分值。

[0117]

积分期间tp1根据信号sph1的转变定时而被划分为期间tpp1和期间tpm1。积分电路61在期间tpp1内以第一极性进行第一积分处理,在期间tpm1内以与第一极性相反的极性即第二极性进行第一积分处理。在图14中,第一极性是正极性,第二极性是负极性。积分电路61输出作为积分结果的电压qa1。

[0118]

积分期间tp1根据信号sph2的转变定时而被划分为期间tpp2和期间tpm2。积分电路62在期间tpp2内以第一极性进行第二积分处理,在期间tpm2内以第二极性进行第二积分处理。积分电路62输出作为积分结果的电压qa2。

[0119]

以上,对求出表示第一信号sta的相位的电压qa1、qa2的动作进行了说明,但表示第二信号stp的相位的电压qa3、qa4也通过同样的动作求出。

[0120]

将第一信号sta与第二信号stp的转变定时的时间差设为tdf。测定电路30通过tdf=tc

×

(qa3/az2

‑

qa1/az1)来求出时间差tdf。tc是时钟信号clk’的周期,az1=qa2

‑

qa1,az2=qa4

‑

qa3。az1、az2是恒定的,不依赖于时间差tdf的值。在图14中,积分期间tp1是未知数,起因于该未知数的偏置(offset)发生在qa1/az1、qa3/az2中。但是,由于求出qa1、qa3时的积分期间tp1是共同的,所以qa1/az1的偏置和qa3/az2的偏置为相同的值,通过减法运算而被消除。

[0121]

图15是时间数字转换电路120的第二详细结构例。时间数字转换电路120包含环形振荡器71、81、测定电路91、基准时钟计数器92以及调整电路72、82。

[0122]

在第二结构例中,时间数字转换电路120具有测定模式和调整模式。测定模式是测定时间差的模式,调整模式是对环形振荡器71、81的振荡频率进行调整的模式。

[0123]

首先,对测定模式进行说明。环形振荡器71在第一信号sta的转变定时处使振荡环路被使能(enable)。由此,环形振荡器71开始振荡并生成时钟信号clks。环形振荡器81在第二信号stp的转变定时处使振荡环路被使能。由此,环形振荡器81开始振荡并生成时钟信号clkf。将时钟信号clks的频率设为f1,将时钟信号clkf的频率设为f2。f2比f1高。

[0124]

测定电路91根据时钟信号clks和时钟信号clkf来求出时间差信息tmd。时间差信息tmd表示第一信号sta与第二信号stp的转变定时的时间差。求出时间差信息tmd的方法在后面的图16中叙述。

[0125]

接着,对调整模式进行说明。在第二详细结构例中,使用时钟信号clk’来作为成为环形振荡器71、81的振荡频率的基准的基准时钟信号。基准时钟计数器92对时钟信号clk’的时钟数进行计数,在对给与的时钟数进行计数的期间输出有效的使能信号ena。

[0126]

调整电路72在使能信号ena有效的期间对时钟信号clks的时钟数进行计数。调整电路72对该计数值与第一目标值的差分进行积分,输出通过该积分得到的控制数据fcs。第一目标值是用于设定环形振荡器71的振荡频率的值。环形振荡器71以与控制数据fcs对应的振荡频率进行振荡。例如,可变电容电路被设置为环形振荡器71的振荡环路的负载,并且该可变电容电路的电容值由控制数据fcs控制。这样,环形振荡器71的振荡频率被调整。

[0127]

调整电路82在使能信号ena有效的期间对时钟信号clkf的时钟数进行计数。调整电路82对该计数值与第二目标值的差分进行积分,输出通过该积分得到的控制数据fcf。第二目标值是用于设定环形振荡器81的振荡频率的值。环形振荡器81以与控制数据fcf对应的振荡频率进行振荡。例如,可变电容电路被设置为环形振荡器81的振荡环路的负载,该可变电容电路的电容值由控制数据fcf控制。这样,环形振荡器81的振荡频率被调整。

[0128]

当时间数字转换电路120在调整模式之后被设定为测定模式时,在调整模式中求出的控制数据fcs、fcf被输入到环形振荡器71、81。由此,环形振荡器71、81以在调整模式下被调整的振荡频率进行振荡,测定电路91能够使用频率准确的时钟信号clks、clkf来进行时间测定。

[0129]

图16是对时间数字转换电路120的第二详细结构例的动作进行说明的波形图。图16示出测定模式下的波形图。

[0130]

测定电路91对时钟信号clks和时钟信号clkf的相位进行比较,并且当判定为时钟信号clks的相位和时钟信号clkf的相位互换时,使相位比较结果信号qp从高电平变为低电平。相位比较结果信号qp是测定电路91的内部信号。

[0131]

测定电路91对时钟信号clks的时钟数进行计数。将该计数值设为cts。并且,测定电路91对时钟信号clkf的时钟数进行计数。该计数值为ctf。

[0132]

测定电路91取得相位比较结果信号qp的下降沿处的计数值cts、ctf。设该计数值为n1、n2。当将时钟信号clks的周期设为δt1=1/f1,将时钟信号clkf的周期设为δt2=1/f2时,其差分为分辨率δt=|δt1

‑

δt2|。当设n3=n1

‑

n2时,测定电路91通过n3

×

δt1 n2

×

δt来求出第一信号sta与第二信号stp的转变定时的时间差。在图16中,由于n1=5、n2=4、n3=1,所以时间差为δt1 4

×

δt。

[0133]

7.电子设备

[0134]

图17示出了包含实时时钟装置10的电子设备500的结构例。电子设备500例如是网络设备、车载设备或计测设备。在网络设备或车载设备中,实时时钟装置10用于系统内的时刻同步。例如,在由多个网络设备构成的通信网络中,通过使各网络设备所具有的实时时钟装置的时刻同步,能够在网络内使用共同的时刻。或者,在计测设备中,实时时钟装置10用于测定时刻的记录。本实施方式的实时时钟装置10能够得到高精度的时刻信息,能够进行精密的时刻同步或精密的测定时间的记录。

[0135]

如图17所示,电子设备500包含实时时钟装置10和基于来自实时时钟装置10的输出信号来进行处理的处理装置520。输出信号例如是计时数据、时间差信息、时间数据或频率信息。处理装置520也可以进行使用来自实时时钟装置10的输出信号的信号处理。并且,电子设备500还能够包含通信接口510、操作界面530、显示部540以及存储器550。另外,电子设备500不限于图17的结构,能够实施省略该一部分的结构要素或追加其他结构要素等的各种变形。

[0136]

通信接口510进行从外部接收数据或向外部发送数据的处理。处理装置520进行电子设备500的控制处理、经由通信接口510收发的数据的各种数字处理等。处理装置520的功能例如能够通过微型计算机等处理器来实现。操作界面530用于供用户进行输入操作,能够通过操作按钮或触摸面板显示器等实现。显示部540显示各种信息,能够通过液晶或有机el等显示器实现。存储器550存储数据,其功能能够通过ram或rom等半导体存储器实现。

[0137]

以上说明的本实施方式的实时时钟装置包含振子、时钟信号生成电路、计时电路、外部信号输入端子以及时间数字转换电路。时钟信号生成电路具有使振子振荡而生成振荡时钟信号的振荡电路,并且时钟信号生成电路输出基于振荡时钟信号的计时用时钟信号。计时电路根据计时用时钟信号来生成计时数据。向外部信号输入端子输入外部信号。时间数字转换电路以比计时电路的计时分辨率高的分辨率对基于从外部信号输入端子输入的外部信号的第一信号的转变定时与基于振荡时钟信号或计时用时钟信号的第二信号的转变定时的时间差进行测定,求出与时间差对应的时间差信息。

[0138]

根据本实施方式,通过实时时钟装置包含时间数字转换电路,能够取得比计时电路的计时分辨率高的分辨率的时间差信息。即,计时电路通过使用了计时用时钟信号的计数处理来进行计时,但能够不受该计数处理的时间分辨率限制地取得时间差信息。由此,能够实现高精度的实时时钟装置。

[0139]

并且,在本实施方式中,也可以是,实时时钟装置包含接口电路,该接口电路输出基于计时数据和时间差信息的输出信息。

[0140]

根据本实施方式,实时时钟装置能够将基于计时数据和时间差信息的输出信息输

出到外部。由此,设置于实时时钟装置的外部的处理装置能够利用表示高精度的时间的输出信息。

[0141]

并且,在本实施方式中,也可以是,实时时钟装置包含时间数据输出电路。也可以是,时间数据输出电路根据计时数据和时间差信息,输出比计时分辨率高的分辨率的时间数据。也可以是,接口电路将时间数据作为输出信息来输出。

[0142]

根据本实施方式,实时时钟装置能够将比计时分辨率高的分辨率的时间数据输出到外部。由此,设置于实时时钟装置的外部的处理装置能够利用比计时分辨率高的分辨率的时间数据。

[0143]

并且,在本实施方式中,也可以是,外部信号是触发信号。也可以是,时间数据输出电路输出时间数据来作为表示触发信号的转变定时的时间戳信息。

[0144]

根据本实施方式,实时时钟装置能够将比计时分辨率高的分辨率的时间戳信息输出到外部。由此,设置于实时时钟装置的外部的处理装置能够利用比计时分辨率高的分辨率的时间戳信息。

[0145]

并且,在本实施方式中,也可以是,实时时钟装置包含频率测定电路。也可以是,向外部信号输入端子输入外部时钟信号来作为外部信号。也可以是,频率测定电路包含时间数字转换电路、计数器电路以及运算电路。也可以是,计数器电路进行基于外部时钟信号和振荡时钟信号或外部时钟信号和计时用时钟信号的计数处理,并输出计数数据。也可以是,运算电路通过进行基于时间差信息和计数数据的运算,求出与外部时钟信号的频率对应的频率信息。

[0146]

根据本实施方式,通过实时时钟装置包含频率测定电路,能够取得外部时钟信号的频率信息。此时,由于频率测定电路包含以比计时分辨率高的分辨率测定时间差的时间数字转换电路,所以能够通过使用该时间差信息来高精度地测定频率。由此,能够实现高精度的实时时钟装置。例如,通过基于该频率信息来调整计时用时钟信号的频率,能够进行高精度的计时。

[0147]

并且,在本实施方式中,也可以是,实时时钟装置包含接口电路,该接口电路将计时数据和频率信息作为输出信息来输出。

[0148]

根据本实施方式,实时时钟装置能够将计时数据和频率信息输出到外部。由此,设置于实时时钟装置的外部的处理装置能够利用由包含时间数字转换电路的频率测定电路测定出的高精度的频率信息。例如,处理装置能够根据频率信息来调整计时用时钟信号的频率。

[0149]

并且,在本实施方式中,也可以是,时钟信号生成电路将振荡时钟信号或振荡时钟信号的分频时钟信号作为计时用时钟信号来输出。

[0150]

根据本实施方式,计时电路能够根据振荡时钟信号或振荡时钟信号的分频时钟信号来生成计时数据。

[0151]

并且,在本实施方式中,也可以是,时钟信号生成电路根据经由接口电路输入的频率调整信号,对计时用时钟信号的频率进行调整。

[0152]

根据本实施方式,基于从实时时钟装置的外部经由接口电路输入的频率调整信号来调整计时用时钟信号的频率。

[0153]

由此,能够从外部校正计时用时钟信号的频率,实时时钟装置能够根据该校正后

的计时用时钟信号来高精度地进行计时。

[0154]

并且,在本实施方式中,也可以是,时钟信号生成电路将振荡时钟信号或振荡时钟信号的分频时钟信号作为计时用时钟信号来输出。也可以是,振荡电路根据频率调整信号对振荡时钟信号的频率进行调整。

[0155]

根据本实施方式,基于频率调整信号来调整振荡时钟信号的频率,输出该振荡时钟信号或振荡时钟信号的分频时钟信号来作为计时用时钟信号。由此,能够实现基于频率调整信号的计时用时钟信号的频率调整。

[0156]

并且,在本实施方式中,也可以是,时钟信号生成电路包含分数

‑

n型分频电路,该分数

‑

n型分频电路对振荡时钟信号进行分频并将分频时钟信号作为计时用时钟信号来输出。也可以是,分数

‑

n型分频电路根据频率调整信号对分频比进行调整。

[0157]

根据本实施方式,基于频率调整信号来调整分数

‑

n型分频电路的分频比,振荡时钟信号以该分频比被分频,其分频时钟信号作为计时用时钟信号来输出。由此,实现基于频率调整信号的计时用时钟信号的频率调整。

[0158]

并且,在本实施方式中,也可以是,时钟信号生成电路、计时电路以及时间数字转换电路设置于1个半导体基板。

[0159]

根据本实施方式,与将时钟信号生成电路、计时电路以及时间数字转换电路构成为单独的ic的情况相比,能够抑制作为测定对象的信号的延迟或波形变形等,因此,时间数字转换电路能够测定出准确的时间差。

[0160]

并且,在本实施方式中,也可以是,实时时钟装置包含频率测定电路和处理电路,该频率测定电路包含时间数字转换电路。也可以是,频率测定电路根据作为外部信号而输入的外部时钟信号的频率,求出与计时用时钟信号的频率对应的频率信息。也可以是,处理电路生成与频率信息对应的频率调整信号。也可以是,时钟信号生成电路根据频率调整信号对计时用时钟信号的频率进行调整。

[0161]

根据本实施方式,实时时钟装置能够测定计时用时钟信号的频率,并且根据该频率信息对计时用时钟信号的频率进行调整。并且,通过将处理电路内置于电路装置,不需要将用于进行使用了频率信息的信号处理的处理装置设置于实时时钟装置的外部。即,能够以实时时钟装置单体来调整计时用时钟信号的频率。

[0162]

并且,在本实施方式中,也可以是,实时时钟装置包含存储器,该存储器存储用于使处理电路生成频率调整信号的程序。

[0163]

根据本实施方式,通过存储于存储器的程序,处理电路能够根据频率信息来生成频率调整信号。由于能够将记述了各种信号处理的程序存储在存储器中,所以用户能够对生成频率调整信号的信号处理的算法进行各种定制。

[0164]

并且,本实施方式的电子设备包含:以上任意记载的实时时钟装置;以及处理装置,其进行基于来自实时时钟装置的输出信号的处理。

[0165]

另外,如上所述对本实施方式进行了详细说明,但本领域技术人员能够容易地理解可进行实质上不脱离本公开的新事项及效果的多种变形。因此,本公开的范围包含所有这样的变形例。例如,在说明书或附图中,至少一次与更广义或同义的不同用语一起记载的用语在说明书或附图的任何位置都能够置换为该不同的用语。此外,本实施方式和变形例的所有组合也包含在本公开的范围内。并且,电路装置、实时时钟装置以及电子设备等的结

构和动作等也并不限定于本实施方式中的说明,能够实施各种变形。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。