本发明涉及集成电路测量领域,尤其涉及一种用于fpga型时间数字转换器的延迟线校准电路。

背景技术:

高精度时间间隔测量技术不论在分子生物学、核物理探测和天文观测等理论研究领域,还是在激光测距、高精度定位和食品药品安全监测等工程实践领域都有着广泛的应用,其对国民经济与国防工业建设意义重大。

时间数字转换(tdc)技术是高精度时间间隔测量的重要手段,它可以直接将时间量转换成数字量,具有精度高、抗干扰能力强等优点。大多数工业级的时间数字转换器主要使用专用集成电路(asic)实现。与此相比,基于现场可编程门阵列(fpga)的tdc有着成本低、开发周期短等优点。同时,随着集成电路工艺节点的持续缩减,fpga内部连线和逻辑单元的延迟越来越小,使得该类tdc同样可以达到很高的测量精度。

在基于fpga的时间数字转换器中,一般通过构造延迟线对时间间隔进行内插,提高测量的精度。然而,延迟线中延迟单元的延时并不是固定的,而是会随着温度和电压的变化而改变。文献[1]的研究结果表明,在virtex-4fpga中,tdc延迟单元的延时变化率为0.047ps/℃。若不进行适当补偿,当测试环境温度从30℃升高到80℃时,测量精度则从10ps下降到70ps。为了减小温度/电压变化对tdc测量精度的影响,文献[2]提出了一种用于延迟线校准电路的waveunion方法对延迟线进行在线校准,但在具体实现该方法时,使用了fpga外部晶体振荡器提供标定所需的随机信号,导致该校准电路的可移植性较差;文献[3]基于统计学原理,设计了一种采用双相位延迟线的流水线型在线校准电路。该电路虽然有效提高了校准的精度,但需要很大的先进先出(fifo)存储深度才能满足标定次数的要求,在一定程度上限制了校准精度的提升。

参考文献

[1]wangj,lius,shenq,etal.afullyfledgedtdcimplementedinfield-programmablegatearrays[j].ieeetransactionsonnuclearscience,2010,57(2):446-450.

[2]wuj,shiz.the10-pswaveuniontdc:improvingfpgatdcresolutionbeyonditscelldelay[c].ieeenuclearsciencesymposiumconferencerecord,dresden,germany,2008:3440-3446.

[3]wonjy,kwonsi,yoonhs,etal.dual-phasetapped-delay-linetime-to-digitalconverterwithon-the-flycalibrationimplementedin40nmfpga[j].ieeetransactionsonbiomedicalcircuits&systems,2016,10(1):231-242.

技术实现要素:

本发明提供了一种用于fpga型时间数字转换器的延迟线校准电路,本发明设计了一款可移植性好、能够快速对延迟线进行在线校准的校准电路,降低温度/电压对延迟线延时的影响,提高了tdc的测量精度,详见下文描述:

一种用于fpga型时间数字转换器的延迟线校准电路,所述延迟线校准电路由环形振荡器电路、控制电路、cal_ram与lut_ram存储单元组成;

所述环形振荡器电路由复位信号控制起振,用于生成标定用的随机脉冲信号;所述控制电路通过有限状态机控制cal_ram和lut_ram的读写,完成延迟线的标定和计数值的累加;

所述cal_ram和lut_ram电路通过调用blockramip核实现,在标定状态下,cal_ram用于对延迟线中各延迟单元处出现跳变的次数进行存储;在累加状态下,lut_ram用于对跳变次数的累加值进行存储。

其中,标定状态下,环形振荡器电路生成的随机脉冲信号引入延迟线,在延迟线的各延迟单元处产生1、0跳变;上升沿到来时,寄存器锁存1、0跳变的位置信息,得到温度计码,温度计码经过译码器译码成二进制码,将二进制码作为cal_ram的读地址和写地址,在该二进制码对应地址处加1,至此完成一次标定;

标定状态结束后,电路进入累加状态,将cal_ram[1]、cal_ram[2]……cal_ram[d]和cal_ram[d 1]/2的和存入lut_ram[d]中。

进一步地,所述环形振荡器电路由10个查找表构成的反相器和1个二输入与非门首尾相连,构成振荡环,由复位信号控制起振,从反相器处引出抽头信号,抽头信号经过与门得到随机脉冲信号。

其中,所述环形振荡器电路生成的随机脉冲信号引入延迟链后输出温度计码,经译码电路译码生成二进制码,并将其输入到控制电路中,控制cal_ram和lut_ram的读写;

cal_ram[d 1]/2是通过对cal_ram[d 1]右移一位实现,lut_ram[d 1]中存储的计数值经过右移1位模块后变为原值的一半,实现将延时校准到第d 1个延时单元的中间位置。

本发明提供的技术方案的有益效果是:

1、相对于使用分布式ram(随机存储器)存储标定过程中产生的数据,本发明使用block(块)ram存储标定过程中产生的数据有如下优势:因标定过程需要重复数十万次才能保证较好的精度,所以会产生大量的数据,作为fpga内部定制的存储单元,blockram更适合较大的存储应用;使用blockram可以避免占用大量查找表(lut)资源,且时序特性更好。

2、对于未提供额外有源晶体振荡器的fpga开发板来说,将环形振荡器集成到fpga上,用来生成标定使用的随机脉冲信号,使校准电路的移植性更好。

3、本发明所述校准电路可以将延迟时间校准到延迟单元的中间位置,且进行250000次标定仅耗时16.17ms,具有很好的实时性,可以有效降低温度/电压变化对tdc测量精度的影响。

综上所述,本发明所述校准电路具有占用fpga内部查找表(lut)资源少、电路移植性好、可实时校准等优点,故可显著降低温度/电压变化的影响,有效提高tdc测量精度。

附图说明

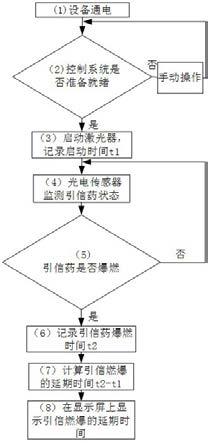

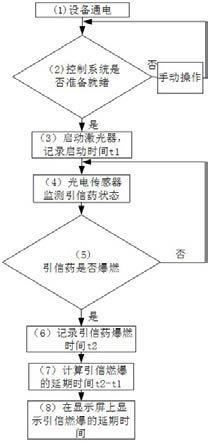

图1为码密度测试的原理图;

图2为环形振荡器的电路结构图;

图3为延迟线校准电路的结构图;

图4为写cal_ram(标定存储单元)的状态转移图;

图5为写lut_ram(查找表存储单元)的状态转移图;

图6为各延迟单元处出现跳变的计数值;

图7为延迟单元的延时示意图。

具体实施方式

为使本发明的目的、技术方案和优点更加清楚,下面对本发明实施方式作进一步地详细描述。

实施例1

本发明实施例提供了一种用于fpga型时间数字转换器的延迟线校准电路,参见图1-图7,该电路包括:

1、本发明实施例中的延迟线校准电路由环形振荡器电路、控制电路、cal_ram与lut_ram存储单元组成。环形振荡器电路由复位信号控制起振,用于生成标定用的随机脉冲信号。控制电路通过有限状态机(fsm)控制cal_ram和lut_ram的读写,完成延迟线的标定和计数值的累加。cal_ram和lut_ram电路是通过调用blockramip核实现的。在标定状态下,cal_ram用于对延迟线中各延迟单元处出现跳变的次数进行存储;在累加状态下,lut_ram用于对跳变次数的累加值进行存储。

2、标定状态下,将环形振荡器生成的随机脉冲信号引入延迟线,在延迟线的各延迟单元处产生1、0跳变。当时钟上升沿到来时,寄存器锁存1、0跳变的位置信息,得到温度计码,温度计码经过译码器译码成二进制码,将二进制码作为cal_ram的读地址和写地址,在该二进制码对应地址处加1,至此完成一次标定。重复上述标定过程,直到标定次数达到预设值。

3、标定状态结束后,电路进入累加状态。将cal_ram[1]、cal_ram[2]……cal_ram[d]和cal_ram[d 1]/2的和存入lut_ram[d]中,cal_ram[d 1]/2是通过对cal_ram[d 1]右移一位实现的。

例如,将cal_ram[1]、cal_ram[2]、cal_ram[3]、cal_ram[4]和lut_ram[5]/2的和存储到lut_ram[4]中。完成累加计算后,即可计算出累加值对应的延时。设用于标定的时钟周期为5ns,标定次数为250000,则累加值n对应的延时为n×5000ps/250000=n×0.02ps。

实施例2

下面结合图1-图7对实施例1中的方案进行进一步地介绍,详见下文描述:

延迟线中各延迟单元的延时需要经过标定得到。在线实时标定可以得出较为真实的延时信息,降低温度/电压变化对fpga型tdc测量精度的影响。对延迟线型tdc标定的方法主要有平均校准法和逐位校准法。平均校准法的系统反应时间快,可以快速地对延迟线进行校准,但这种方法只能计算出延迟单元的平均延时,当延迟线的线性度较差时,这种方式无法对延迟单元进行逐一校准,增大测量误差。因此,本发明实施例设计了一种校准电路对延迟单元进行逐位校准。

1、逐位校准法理论分析

逐位校准法的原理源于模数转换器中的码密度测试。图2为码密度测试原理。使用大量跳变时间均匀分布在[0,ts]的随机脉冲作为延迟线的输入,随机跳变在每个延迟单元累积的次数称为码密度。理想情况下,随机样本的数量越多,标定结果越准确。但在实际操作中,样本数量不可能达到无限多,只要样本数量满足规定的测量误差即可,下面推导校准值以及校准所需样本数量的最小值。

(1)校准值的确定

如果随机事件足够多,那么随机跳变出现在某个延迟单元处的概率pd与该延迟单元的延时td成正比,即pd=td/ts。假设注入随机信号的个数为n,跳变沿在第d个延迟单元处的出现次数为nd,则该延迟单元的延时为:

通过式(1)可以计算出所有延迟单元的延时,进而可以得出前d个延迟单元的累计延时为:

其中,ni为跳变沿在第i个延迟单元处出现的次数,ti为第i个延迟单元的延时。

由于所测时间大小并不确定,所以1、0跳变在延迟线上被锁存的位置也不确定。为了评估测量误差,假设所测时间值为td<ti<td 1,则标准偏差为:

当ti=(td 1 td)/2时,标准偏差最小,所以应该将延时校准到第d 1个延迟单元的中间位置。根据式(2)可得:

(2)标定次数的确定

对于式(4),样本数n越大,所评估的延迟时间越精确。然而在实际标定过程中,样本数不可能无限大。对于有限的样本数n,实际跳变次数nd服从二项式分布,其平均值为

由于所有样本是非相关的,跳变次数ni也是非相关,由式(1)和(4)可得:

理想情况下,每个延迟单元延时相等,随机跳变落在延迟单元d上的概率相等,即pd=1/m,其中m为延迟单元的数量。当d=m时,即d为最后一个延迟单元时,σt达到最大值,即:

假设σtmax误差要求小于10ps,标定用的时钟频率为200mhz,由式(7)可得

n≥250000(8)

即标定次数不少于250000次。

2、校准电路的设计

环形振荡器是利用门电路的固有延迟时间,将奇数个反相器首尾相连而成。在fpga中,可以使用查找表(lut)实现奇数个反相器的首尾相连,并利用查找表(lut)逻辑输出的延时实现振荡。图3是环形振荡器的电路结构图,本发明实施例将10个由查找表(lut)构成的反相器和1个二输入与非门首尾相连,构成振荡环,由复位信号rstn控制起振,从inv2和inv4处引出抽头信号,两个抽头信号经过与门得到随机脉冲信号calsig。

图4为校准电路结构图。环形振荡器生成的随机脉冲信号引入延迟链后输出温度计码,随后经译码电路译码生成二进制码,并将其输入到控制电路中,控制cal_ram和lut_ram的读写。cal_ram通过调用blockramip核实现,设置位宽为15bit,地址宽度为8bit。lut_ram通过调用blockramip核实现,设置位宽为21bit,地址宽度为8bit。cal_ram和lut_ram的地址宽度可以根据延迟线长度进行灵活调整。计数器hit_cnt对标定次数进行计数,当计数次数达到250000次时,标定状态完成。lut_ram[d 1]中存储的计数值经过右移1位模块后变为原值的一半,实现将延时校准到第d 1个延时单元的中间位置。

本发明校准电路的工作过程包括两个阶段:写cal_ram和写lut_ram。写cal_ram的状态机包括4个状态,分别为getcal_adr、rd_cal、wait0和wr_cal,图4是写cal_ram的状态转移图。下面对各状态进行说明:

(1)getcal_adr:将译码电路输出的二进制码作为读地址加载到cal_ram的读地址端口,随后状态跳转到rd_cal。

(2)rd_cal:将cal_ram对应地址处的数据读出到输出寄存器,且将读地址作为写地址加载到写地址端口,随后状态跳转到wait0。

(3)wait0:将输出寄存器中的数据读出到数据总线,且数据加1,随后状态跳转到wr_cal。

(4)wr_cal:写使能有效,将加1后的数据写回原地址,且计数器hit_cnt加1。如果计数器hit_cnt计数到250000,状态跳转到写lut_ram阶段,否则跳回状态getcal_adr,执行新一轮标定。

当标定次数达到250000次后,控制电路进入写lut_ram阶段。写lut_ram的状态机包括5个状态,分别为getcl_adr、rd_cl、wait1、wr_lut和ref_iniadr,图5是写lut_ram的状态转移图。下面对各状态进行说明:

(1)getcl_adr:地址addr_ini初始值为0,将addr_ini 1作为读地址,加载到cal_ram的读地址端口rdadr_cal;将addr_ini作为读写地址,加载到lut_ram的读写地址端口rdadr_lut和wradr_lut,随后状态无条件跳转到rd_cl。

(2)rd_cl:将cal_ram和lut_ram中的数据读出到输出寄存器,随后状态无条件跳转到wait1。

(3)wait1:将lut_ram输出寄存器中的数据通过端口o_lut读出到数据总线;将cal_ram输出寄存器中的数据从o_lut读出,若rdadr_cal等于addr_ini 1,数据选择器mux的s1端选通,否则s0端选通。随后状态无条件跳转到wr_lut。

(4)wr_lut:lut_ram的写使能信号wren_lut有效,o_cal和o_lut相加后写回lut_ram中,同时,rdadr_lut减1。如果radar_lut大于1,状态跳转到rd_cl,否则跳转到状态ref_iniadr,更新地址addr_ini。

(5)ref_iniadr:地址addr_ini加1。如果地址小于延迟单元数量,状态跳转到getcl_adr进行新一轮累加,否则校准完成

利用本发明所述延迟线校准电路对tdc中的两条延迟线进行250000次的标定,整个标定过程仅耗时16.17ms,有着很好的实时性。各延迟单元的跳变计数值如图6所示。根据式(1)可计算出各延迟单元对应的延迟时间,如图7所示。校准电路标定出的各延迟单元延时符合时序仿真结果。

综上所述,本发明的校准电路可以通过灵活调整cal_ram和lut_ram的地址宽度,实现对不同长度延迟线的在线校准。由于无需外部晶体振荡器提供随机脉冲信号,可移植性好。通过调用blockramip核,可大幅降低查找表资源的占用。

本发明实施例对各器件的型号除做特殊说明的以外,其他器件的型号不做限制,只要能完成上述功能的器件均可。

本领域技术人员可以理解附图只是一个优选实施例的示意图,上述本发明实施例序号仅仅为了描述,不代表实施例的优劣。

以上所述仅为本发明的较佳实施例,并不用以限制本发明,凡在本发明的精神和原则之内,所作的任何修改、等同替换、改进等,均应包含在本发明的保护范围之内。

本文用于企业家、创业者技术爱好者查询,结果仅供参考。