一种基于反馈机制的1pps时间同步系统及方法

技术领域

[0001]

本发明属于舰艇时统设备技术领域,涉及1pps时间同步方法及系统,尤其是一种基于反馈机制的1pps时间同步系统及方法。

背景技术:

[0002]

目前,时统设备接收卫星导航设备的时间基准信息,与之完成同步后对外输出,向用户提供统一的时间基准。1pps从卫星导航设备传输到时统设备经同步输出的过程中存在传输延时和同步延时,如未对上述延时进行校正处理,此时统设备输出的时间基准1pps比卫星导航设备输出的1pps相位滞后可高达数百纳秒。随着时间精度要求的提升,需要提高1pps相位同步精度可以更好的满足用户对高精度时间同步的需求。

技术实现要素:

[0003]

本发明的目的在于克服现有技术的不足,提出一种基于反馈机制的1pps时间同步系统及方法,能够实现时统设备输出的1pps与卫星导航接收机输出的1pps的高精度相位同步,用来提高时间基准精度,以满足不断发展的需求。

[0004]

本发明解决其现实问题是采取以下技术方案实现的:

[0005]

一种基于反馈机制的1pps时间同步系统,包括频率基准单元、脉冲同步单元、相位检测单元、核心处理单元和输出校正单元;

[0006]

所述频率基准单元的输出端还与脉冲同步单元相连接,用于将其产生的基准频率输出至脉冲同步单元后,由脉冲同步单元产生与外部输入1pps相位滞后0~1个时钟周期且脉宽为1个时钟周期的同步脉冲1pps信号;

[0007]

所述脉冲同步单元的输出端与相位检测单元相连接,该相位检测单元的输出端与核心处理单元相连接;该相位检测单元用于接收脉冲同步单元输出的同步脉冲1pps信号和外部输入1pps信号,并完成上述两种1pps脉冲上升沿之间的相位差检测后,将相位差数据输出至核心处理单元;

[0008]

所述核心处理单元的输入端分别与频率基准单元和脉冲同步单元相连接,用于接收频率基准单元产生的基准频率和脉冲同步单元产生的同步脉冲1pps信号后生成1pps输出信号;核心处理单元的输入端还与相位检测单元相连接,用于采集1pps相位差测量数据后进行数据滤波处理并结合初始链路时延值,完成初始时延校正补偿值的计算;

[0009]

所述核心处理单元的输出端与输出校正单元相连接,用于将时延校正补偿值和1pps输出信号同时输出至所述输出校正单元,该输出校正单元完成对输出1pps的时延校正补偿;

[0010]

所述相位检测单元用于接收所述输出校正单元输出的1pps反馈信号后,对外部输入1pps和输出1pps反馈信号进行相位检测;所述核心处理单元实时采集上述相位差数值进行处理后,将最新输出1pps和时延校正补偿值发送给输出校正单元。

[0011]

而且,所述频率基准单元包括铷钟等频标器件和时钟倍频电路,铷钟等频标器件

提供10mhz频率输出,通过时钟倍频电路将其倍频。

[0012]

而且,所述脉冲同步单元由2路jk触发器搭建构成,jk触发器的时钟输入为频率基准单元提供的基准频率信号。

[0013]

一种基于反馈机制的1pps时间同步方法,包括以下步骤:

[0014]

步骤1、铷钟等频标器件工作稳定后,经倍频电路生成基准频率;

[0015]

步骤2、外部输入1pps经过脉冲同步单元生成同步脉冲1pps;

[0016]

步骤3、外部输入1pps和同步脉冲1pps均输入到相位检测单元,相位检测单元对上述两种脉冲上升沿之间的相位差进行实时检测;

[0017]

步骤4、核心处理单元实时采集上述相位差数值,并通过一定算法对数据处理,结合初始链路时延值,完成初始时延校正补偿值的计算,并利用同步脉冲和基准频率信号生成1pps输出信号,最后,将时延校正补偿值和1pps输出信号同时传递给输出校正单元;

[0018]

步骤5、输出校正单元根据核心处理单元发送来的校正值完成校正,完成对输出1pps的时延校正补偿;

[0019]

步骤6、输出1pps反馈到相位检测单元,相位检测单元对外部输入1pps和输出1pps进行相位检测;

[0020]

步骤7、核心处理单元实时采集上述相位差数值,并通过一定算法对数据进行处理,将最新输出1pps和时延校正补偿值发送给输出校正单元;

[0021]

步骤8、重复步骤5;

[0022]

步骤9,流程结束。

[0023]

本发明的优点和有益效果:

[0024]

1、本发明提供了一种基于反馈机制的1pps时间同步系统,包括频率基准单元、脉冲同步单元、相位检测单元、核心处理单元和输出校正单元。脉冲同步单元利用频率基准单元输出的基准频率将外部输入1pps生成同步1pps脉冲;相位检测单元对外部输入1pps和同步1pps脉冲上升沿间的相位差进行测量,并将测量结果反馈到核心处理单元;核心处理单元将测量结果按照一定的滤波算法对数据进行处理,得到脉冲同步偏差,结合初始定值链路时延,得到初始时延校正补偿值,完成相位的初始补偿。但由于输入输出链路中所使用的电子元器件的固有特性以及温度特性等因素影响,链路时延存在一定的不确定性,为了更加精确的补偿链路时延,采用动态补偿方式,将输出1pps脉冲反馈至相位检测单元与输入1pps进行相位比较,得到链路时延的动态变化数据,并采用一定的算法将数据进行平滑处理,进而得到链路时延的动态精准数值。核心处理单元将上述补偿值实-时发送给输出校正单元;输出校正单元实现时延补偿功能。经过上述闭环动态校正可实现对输入输出链路时延的精确补偿,进而保证输出1pps与外部输入1pps的高精度同步,应用到实际任务中可以满足时统设备日益增长的高精度时间同步需求,具有较高的应用价值。

[0025]

2、本发明的一种基于反馈机制的1pps时间同步方法,通过对输入1pps和输出1pps的相位差进行实时测量,完成了对外输出1pps的闭环动态校正,最大限度的减小了输入输出电路链路时延的不确定性对时间同步精度的影响,提高了外部输入1pps和输出1pps之间的时间同步精度,应用到实际任务中可以满足舰艇设备对时间基准更高精度的需求。

附图说明

[0026]

图1为本发明的一种1pps相位同步系统的结构示意图;

[0027]

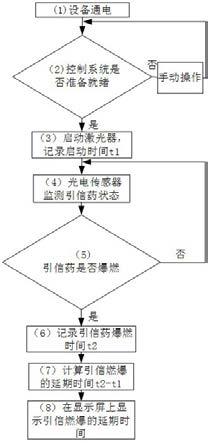

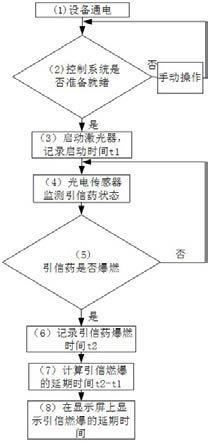

图2为本发明的一种1pps相位同步系统中核心处理单元处理过程的流程示意图;

[0028]

图3为本发明的一种1pps相位同步系统中输出校正单元的结构示意图。

具体实施方式

[0029]

以下结合附图对本发明实施例作进一步详述:

[0030]

一种基于反馈机制的1pps时间同步系统及方法,基于反馈机制,通过对时间同步过程中的时延误差进行动态测量和闭环时延校正,实现输出1pps和外部输入1pps之间的高精度相位同步。

[0031]

一种基于反馈机制的1pps时间同步系统,包括频率基准单元、脉冲同步单元、相位检测单元、核心处理单元和输出校正单元;

[0032]

所述频率基准单元的输出端还与脉冲同步单元相连接,用于将其产生的基准频率输出至脉冲同步单元后,由脉冲同步单元产生与外部输入1pps相位滞后0~1个时钟周期且脉宽为1个时钟周期的同步脉冲1pps信号;

[0033]

所述脉冲同步单元的输出端与相位检测单元相连接,该相位检测单元的输出端与核心处理单元相连接;该相位检测单元用于接收脉冲同步单元输出的同步脉冲1pps信号和外部输入1pps信号,并完成上述两种1pps脉冲上升沿之间的相位差检测后,将相位差数据输出至核心处理单元;

[0034]

所述核心处理单元的输入端分别与频率基准单元和脉冲同步单元相连接,用于接收频率基准单元产生的基准频率和脉冲同步单元产生的同步脉冲1pps信号后生成1pps输出信号;核心处理单元的输入端还与相位检测单元相连接,用于采集1pps相位差测量数据后进行数据滤波处理并结合初始链路时延值,完成初始时延校正补偿值的计算;

[0035]

所述核心处理单元的输出端与输出校正单元相连接,用于将时延校正补偿值和1pps输出信号同时输出至所述输出校正单元,该输出校正单元完成对输出1pps的时延校正补偿;

[0036]

所述相位检测单元用于接收所述输出校正单元输出的1pps反馈信号后,对外部输入1pps和输出1pps反馈信号进行相位检测;所述核心处理单元实时采集上述相位差数值进行处理后,将最新输出1pps和时延校正补偿值发送给输出校正单元。

[0037]

在本实施例中,所述频率基准单元包括铷钟等频标器件和时钟倍频电路,铷钟等频标器件提供10mhz频率输出,通过时钟倍频电路将其倍频。

[0038]

在本实施例中,所述脉冲同步单元由2路jk触发器搭建构成,jk触发器的时钟输入为频率基准单元提供的基准频率信号。

[0039]

下面对系统内各组成单元作进一步说明:

[0040]

所述频率基准单元包括铷钟等频标器件和时钟倍频电路,铷钟等频标器件提供10mhz频率输出,通过时钟倍频电路将其倍频,产生更高的基准频率,供其他单元使用。

[0041]

所述脉冲同步单元由2路jk触发器搭建构成,jk触发器的时钟输入为频率基准单元提供的频率信号;该单元用于产生1路与外部输入1pps相位滞后0~1个时钟周期且脉宽为1个时钟周期的同步脉冲1pps信号。

[0042]

所述相位检测单元,完成不同1pps脉冲上升沿间的相位差检测,相位差数据供核心处理单元使用。

[0043]

所述核心处理单元由fpga作为处理器,完成1pps相位测量数据的采集、数据滤波算法的实现、1pps生成以及输出校正单元时延校正补偿值的计算。

[0044]

所述输出校正单元通过接收核心处理单元发送来的时延校正补偿值,实现链路的可编程时延补偿。

[0045]

一种基于反馈机制的1pps时间同步方法,包括以下步骤:

[0046]

步骤1、铷钟等频标器件工作稳定后,经倍频电路生成基准频率;

[0047]

步骤2、外部输入1pps经过脉冲同步单元生成同步脉冲1pps;

[0048]

步骤3、外部输入1pps和同步脉冲1pps均输入到相位检测单元,相位检测单元对上述两种脉冲上升沿之间的相位差进行实时检测;

[0049]

步骤4、核心处理单元实时采集上述相位差数值,并通过一定算法对数据处理,结合初始链路时延值,完成初始时延校正补偿值的计算,并利用同步脉冲和基准频率信号生成1pps输出信号,最后,将时延校正补偿值和1pps输出信号同时传递给输出校正单元;

[0050]

步骤5、输出校正单元根据核心处理单元发送来的校正值完成校正,完成对输出1pps的时延校正补偿;

[0051]

步骤6、输出1pps反馈到相位检测单元,相位检测单元对外部输入1pps和输出1pps进行相位检测;

[0052]

步骤7、核心处理单元实时采集上述相位差数值,并通过一定算法对数据进行处理,将最新输出1pps和时延校正补偿值发送给输出校正单元;

[0053]

步骤8、重复步骤5;

[0054]

步骤9,流程结束。

[0055]

如图1所示,本发明包括频率基准单元、脉冲同步单元、相位检测单元、核心处理单元和输出校正单元。

[0056]

在本实施例中,频率基准单元包含铷钟等频标器件和时钟倍频电路,时钟倍频电路将铷钟频标器件输出的10mhz频率进行10倍频,产生100mhz基准频率,为脉冲同步单元和核心处理单元提供基准频率;

[0057]

脉冲同步单元完成同步脉冲1pps的产生;相位检测单元完成外部输入1pps与同步脉冲1pps、输出1pps之间的相位差的测量;核心处理单元通过采集相位检测单元的测量数据,根据相应处理算法得出1pps动态时延校正补偿值;输出校正单元根据核心处理单元发送过来的时延校正补偿值校正输出1pps。

[0058]

如图1所示,外部输入1pps进入到脉冲同步单元,脉冲同步单元利用频率信号以外部输入1pps为基准产生1个10ns脉宽的尖脉冲,其与外部输入1pps相位差最大不超过10ns,为了满足相位检测单元的测量范围,将此尖脉冲经过具有固有延时参数的延时电路进行延时。

[0059]

如图1所示,外部输入1pps和同步脉冲1pps均输入到相位检测单元,相位检测单元对两者上升沿间的相位差进行测量,测量完毕后立即发送一个中断信号提示核心处理单元进行数据采集,数据采集过程在1毫秒内完成。

[0060]

如图2所示,核心处理单元处理数据过程包括测量数据采集、数据处理、1pps生成,

时延校正补偿值计算和发送。

[0061]

在本实施例中,通过spi总线实现对相位检测单元的测量数据采集,通过相应数据处理算法计算出时延校正补偿值,并通过并行数据总线将该数据发送给输出校正单元;

[0062]

如图3所示,输出校正单元根据核心处理单元发送来的时延校正补偿值,在链路上产生相应的时延延迟,fpga产生输出的1pps经过该链路后会产生相应的链路时延延迟。

[0063]

如图1所示,经输出校正单元的输出1pps输入到相位检测单元,相位检测单元将其与外部输入1pps进行相位差测量,测量完毕后立即发送另一个中断信号提示核心处理单元进行数据采集。

[0064]

如图2所示,首先,核心处理单元接收到相位检测单元的数据1中断请求后立即采集该数据并判断数据的有效性,若数据无效,继续等待有效数据,若数据有效,对数据进行处理计算出初始时延校正值,并将该初始校正值发送给输出校正单元完成初始校正;然后,核心处理单元会再次接收到相位检测单元的数据2中断请求后立即采集该数据并判断数据的有效性,若数据无效,继续等待有效数据,若数据有效,对数据进行处理计算出动态时延校正补偿值,并将该校正值发送给输出校正单元完成动态闭环校正;

[0065]

如图3所示,输出校正单元根据动态校正值对对外输出1pps的相位进行动态调整,最终实现输出1pps与外部1pps之间的高精度时间同步。

[0066]

综上所述,本发明所述的一种基于反馈机制的1pps时间同步方法,基于反馈机制对外部输入1pps和输出1pps的相位差进行实时测量,完成了对外输出1pps的闭环动态校正,最大限度的减小了输入输出电路链路时延的不确定性对时间同步精度的影响,提高了外部输入1pps和输出1pps之间的时间同步精度。

[0067]

需要强调的是,本发明所述实施例是说明性的,而不是限定性的,因此本发明包括并不限于具体实施方式中所述实施例,凡是由本领域技术人员根据本发明的技术方案得出的其他实施方式,同样属于本发明保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。