1.本发明涉及模拟集成电路技术领域,具体涉及一种时间寄存器及用于时间-数字转换器的时域运算电路。

背景技术:

2.时间-数字转换器(time to digital converter,tdc)是多种应用电路中的关键组成部分,包括飞行时间(time of flight,tof)测量、抖动测量、全数字锁相环等。近年来,随着自动驾驶、人工智能(artificial intelligence,ai)技术的发展以及大规模数字电路时钟频率的提高,对tdc提出了更高的要求,不仅要对时间信号进行更快速更精确的测量,还要求能够对时间信号进行一定的处理。

3.对时间信号进行存储的现有方式是利用电容通过电荷存储的方式保存时间信号。这种方式具有电路结构简单的优点,通过电容的充电完成对时间信号的保存,电容的放电完成对时间信号的输出,但该结构的量程受到电源电压以及电容大小的限制,想要提高量程就势必要提高电源电压或电容大小;同时,基于电容完成对时间信号的保存时,由于电路内部的电荷泄漏以及寄生电容的耦合噪声的存在,会导致电容电压发生变化,这会导致最终输出时间信号产生误差。因此,利用电容实现对时间信号保存的方式难以解决大量程与实现芯片低功耗以及控制芯片面积的矛盾;同时保存时较容易产生误差。

技术实现要素:

4.为解决上述技术问题,本发明提供了一种时间寄存器,其基于延迟链结构,在满足大量程的同时,能够保证对于时间信号保存的稳定性以及实现时域运算。

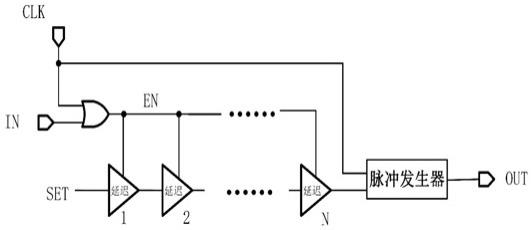

5.本发明所述的一种时间寄存器,其采用的技术方案为:包括延迟链、或门和脉冲发生器,其中:输入时间信号in接或门的输入端,时钟信号clk接或门的另一个输入端并与脉冲发生器的一个输入端相连接,或门的输出端与延迟链的使能端en相连接,高电平信号set接延迟链的输入端,延迟链输出端接脉冲发生器的另一个输入端,脉冲发生器的输出端用作时间寄存器输出端out。

6.作为本发明的一种优选技术方案:所述延迟链由若干个延迟单元级联组成。

7.作为本发明的一种优选技术方案:所述延迟单元包括第一pmos晶体管m

p1

、第二pmos晶体管m

p2

、第三pmos晶体管m

p3

、第四pmos晶体管m

p4

、第一nmos晶体管m

n1

、第二nmos晶体管m

n2

、第三nmos晶体管m

n3

、第四nmos晶体管m

n4

,其中:第一pmos晶体管m

p1

的源极接电源vdd,第一pmos晶体管m

p1

的漏极与第三pmos晶体管m

p3

的源极相连接,第二pmos晶体管m

p2

的源极接电源vdd,漏极与第四pmos晶体管m

p4

的源极相连接,使能信号enb与第一pmos晶体管m

p1

的栅极、第二pmos晶体管m

p2

的栅极相连接;延迟单元的信号输入端与第三pmos晶体管m

p3

的栅极、第一nmos晶体管m

p1

的栅极相连接,第三pmos晶体管m

p3

的漏极接第一nmos晶体管m

n1

的漏极并与第四pmos晶体管m

p4

的栅极、第二nmos晶体管m

n2

的栅极相连接,第四pmos晶体管m

p4

的漏极接第二nmos晶体管m

n2

的漏极

并用作延迟单元的信号输出端;第一nmos晶体管m

n1

的源极接第三nmos晶体管m

n3

的漏极,第二nmos晶体管m

n2

的源极接第四nmos晶体管m

n4

的漏极,使能信号en接第三nmos晶体管m

n3

的栅极并与第四nmos晶体管m

n4

的栅极相连接,第三nmos晶体管m

n3

的源极接地,第四nmos晶体管m

n4

的源极接地。

8.采用上述基于延迟链结构的时间寄存器完成对输入时间信号的保存,并采用时间寄存器的不同连接方式组成时域运算电路,为后级时间-数字转换器(tdc)提供输入信号,完成对时间信号的保存、相加、相减、积分功能。

9.采用上述时间寄存器构成的时间保存功能的时域运算电路,包括时间寄存器1、时间寄存器2、或门和延迟模块,其中:输入时间信号a接或门的一个输入端,输入时间信号b接延迟模块的输入端,延迟模块的输出端接或门的另一个输入端,或门的输出端接时间寄存器1的时间信号输入端,时钟信号clk1接时间寄存器1的时钟信号输入端,时间寄存器1的输出端与时间寄存器2的时间信号输入相连接,时钟信号clk2接时间寄存器2的时钟信号输入端,时间寄存器2的输出端输出时间信号y。

10.作为本发明的一种优选技术方案:采用上述时间寄存器构成的时间相加功能的时域运算电路,包括时间寄存器1、时间寄存器2、或门和延迟模块,其中:输入时间信号a接或门的一个输入端,输入时间信号b接延迟模块的输入端,延迟模块的输出端接或门的另一个输入端,或门的输出端接时间寄存器1的时间信号输入端,时钟信号clk1接时间寄存器1的时钟信号输入端,时间寄存器1的输出端与时间寄存器2的时间信号输入相连接,时钟信号clk2接时间寄存器2的时钟信号输入端,时间寄存器2的输出端输出时间信号y。

11.作为本发明的一种优选技术方案:采用上述时间寄存器构成的时间相减功能的时域运算电路,包括时间寄存器1、时间寄存器2、或门和延迟模块,其中:输入时间信号a接时间寄存器1的时间信号输入端,时钟信号clk1接时间寄存器1的时钟信号输入端,时间寄存器1的输出端接或门的一个输入端,输入时间信号b接延迟模块的输入端,延迟模块的输出端接或门的另一个输入端,或门的输出端与时间寄存器2的输入端相连接,时钟信号clk2接时间寄存器2的时钟信号输入端,时间寄存器2的输出端输出时间信号y。

12.作为本发明的一种优选技术方案:采用上述时间寄存器构成的时间积分功能的时域运算电路,包括时间寄存器1、时间寄存器2、或门和延迟模块,其中:输入时间信号a接或门的一个输入端,输出信号y接延迟模块的输入端,延迟模块的输出端接或门的另一个输入端,或门的输出端与时间寄存器1的时间信号输入端相连接,时钟信号clk1接时间寄存器的时钟信号输入端,时间寄存器1的输出端与时间寄存器2的时间信号输入相连接,时钟信号clk2接时间寄存器2的时钟信号输入端,时间寄存器2的输出端输出时间信号y。

13.本发明的有益技术效果是:本发明所述的时间寄存器,采用延迟链结构,通过使能信号控制时间信号的传输实现时间信号的保存,解决了大量程与实现芯片低功耗以及控制芯片面积的矛盾,同时提高了时间寄存器工作时的稳定性以及抗噪声性能,采用该时间寄存器构成了时域运算电路,实现对时间信号的保存、相加、相减、积分功能,提高了对时间信

号的处理效率。

附图说明

14.图1是本发明所设计一种用于时间-数字转换器的时域运算电路应用框图;图2是本发明所设计时间保存功能的时域运算电路的结构框图;图3是本发明所设计时间相加功能的时域运算电路的结构框图;图4是本发明所设计时间相减功能的时域运算电路的结构框图;图5是本发明所设计时间积分功能的时域运算电路的结构框图:图6是本发明所设计时间寄存器电路的结构框图:图7是本发明所设计延迟单元的电路结构示意图。

具体实施方式

15.下面结合说明书附图对本发明的具体实施方式作进一步详细的说明。

16.如图6所示,本发明所述的一种时间寄存器包括延迟链、或门和脉冲发生器,其中,输入时间信号in接或门的输入端,时钟信号clk接或门的另一个输入端并与脉冲发生器的一个输入端相连接,或门的输出端与延迟链的使能端en相连接,高电平信号set接延迟链的输入端,延迟链的输出端接脉冲发生器的另一个输入端,脉冲发生器的输出端用作时间信号输出端out。

17.所述延迟链由多个延迟单元级联组成,结构如图7所示,所述延迟单元包括第一pmos晶体管m

p1

、第二pmos晶体管m

p2

、第三pmos晶体管m

p3

、第四pmos晶体管m

p4

、第一nmos晶体管m

n1

、第二nmos晶体管m

n2

、第三nmos晶体管m

n3

、第四nmos晶体管m

n4

,其中,第一pmos晶体管m

p1

的源极接电源vdd,第一pmos晶体管m

p1

的漏极与第三pmos晶体管m

p3

的源极相连接,第二pmos晶体管m

p2

的源极接电源vdd,漏极与第四pmos晶体管m

p4

的源极相连接,使能信号enb与第一pmos晶体管m

p1

的栅极、第二pmos晶体管m

p2

的栅极相连接,延迟单元的信号输入端与第三pmos晶体管m

p3

的栅极、第一nmos晶体管m

p1

的栅极相连接,第三pmos晶体管m

p3

的漏极接第一nmos晶体管m

n1

的漏极并与第四pmos晶体管m

p4

的栅极、第二nmos晶体管m

n2

的栅极相连接,第四pmos晶体管m

p4

的漏极接第二nmos晶体管m

n2

的漏极并用作延迟单元的信号输出端,第一nmos晶体管m

n1

的源极接第三nmos晶体管m

n3

的漏极,第二nmos晶体管m

n2

的源极接第四nmos晶体管m

n4

的漏极,使能信号en接第三nmos晶体管m

n3

的栅极并与第四nmos晶体管m

n4

的栅极相连接,第三nmos晶体管m

n3

的源极接地,第四nmos晶体管m

n4

的源极接地。

18.本发明所设计的一种用于时间-数字转换器的时域运算电路在实际应用过程当中,如图1所示,时间信号接时域运算电路输入端,时域运算电路输出时间信号

△

t接tdc的输入端,tdc输出数字信号dout。

19.在实际应用当中,本发明针对时间保存功能的时域运算电路提出了具体设计,如图2所示,所述时间保存功能的时域运算电路包括时间寄存器1和时间寄存器2,其中,输入时间信号a接时间寄存器1的时间信号输入端,时钟信号clk1接时间寄存器的时钟信号输入端,时间寄存器1的输出端与时间寄存器2的时间信号输入相连接,时钟信号clk2接时间寄存器2的时钟信号输入端,时间寄存器2的输出端输出时间信号y。

20.在实际应用当中,本发明针对时间相加功能的时域运算电路提出了具体设计,如

图3所示,所述时间相加功能的时域运算电路包括时间寄存器1、时间寄存器2、或门和延迟模块,其中,输入时间信号a接或门的一个输入端,输入时间信号b接延迟模块的输入端,延迟模块的输出端接或门的另一个输入端,或门的输出端接时间寄存器1的时间信号输入端,时钟信号clk1接时间寄存器1的时钟信号输入端,时间寄存器1的输出端与时间寄存器2的时间信号输入相连接,时钟信号clk2接时间寄存器2的时钟信号输入端,时间寄存器2的输出端输出时间信号y。

21.在实际应用当中,本发明针对时间相减功能的时域运算电路提出了具体设计,如图4所示,所述时间相减功能的时域运算电路包括时间寄存器1、时间寄存器2、或门和延迟模块,其中,输入时间信号a接时间寄存器1的时间信号输入端,时钟信号clk1接时间寄存器1的时钟信号输入端,时间寄存器1的输出端接或门的一个输入端,输入时间信号b接延迟模块的输入端,延迟模块的输出端接或门的另一个输入端,或门的输出端与时间寄存器2的输入端相连接,时钟信号clk2接时间寄存器2的时钟信号输入端,时间寄存器2的输出端输出时间信号y。

22.在实际应用当中,本发明针对时间积分功能的时域运算电路提出了具体设计,如图5所示,所述时间积分功能的时域运算电路包括时间寄存器1、时间寄存器2、或门和延迟模块,其中,输入时间信号a接或门的一个输入端,输出信号y接延迟模块的输入端,延迟模块的输出端接或门的另一个输入端,或门的输出端与时间寄存器1的时间信号输入端相连接,时钟信号clk1接时间寄存器的时钟信号输入端,时间寄存器1的输出端与时间寄存器2的时间信号输入相连接,时钟信号clk2接时间寄存器2的时钟信号输入端,时间寄存器2的输出端输出时间信号y。

23.综上所述,本发明所设计的时间寄存器及用于时间-数字转换器的时域运算电路,其中时间寄存器基于延迟链结构,能够通过增加延迟链长度的方式提高其量程而对电源电压及芯片面积的依赖较小,电荷泄漏以及电路内部噪声对于该时间寄存器的影响较小,解决了大量程与实现芯片低功耗以及控制芯片面积的矛盾,同时提高了保存时间时的稳定性以及抗噪声性能;采用该时间寄存器构成了时域运算电路,实现对时间信号的保存、相加、相减、积分功能,提高了对时间信号的处理效率。

24.上面结合附图对本发明的实施方式作了详细说明,但是本发明并不限于上述实施方式,在本领域普通技术人员所具备的知识范围内,还可以在不脱离本发明宗旨的前提下做出各种变化。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。