本发明涉及集成电路设计,尤其涉及一种时间数字转换器及转换方法。

背景技术:

时间数字转换器是一种将时间间隔转换为数字信号的器件,可以用来计量两个输入信号之间的相位差。

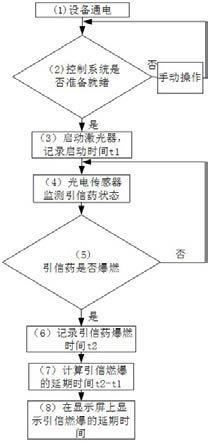

中国专利:cn107272395a,2017.10.20”(参考文献1)公开了一种时间数字转换器及其转换方法,如图1所示,时间数字转换器包括:时间数字转换单元,用于对第一输入或第二输入进行数字转换,第一输入为时间间隔;时间余量提取单元,用于提取时间数字转换单元中紧接在时间间隔后小于时钟周期而未被转换的时间余量,时间余量为从时间间隔的结束到此后时钟信号的第一次上升;时间放大器,用于对时间余量进行线性放大,时间余量的放大信号作为第二输入反馈输入时间数字转换单元并使其匹配于时钟周期。此结构可以准确量化出时间间隔,但是需要经过开关单元、时间数字转换单元、重序输出结果单元、时间余量提取单元以及线性放大器,整个电路结构复杂并且从输入到输出需要经过多个时钟,所以效率相对较低且针对不同的工艺电路可移植性较差。

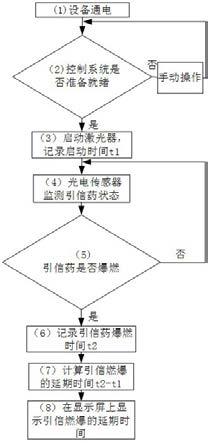

中国专利:cn107809226a,2018.03.16(参考文献2)公开了一种用于时间数字转换器的装置以及时间数字转换的方法,如图2所示,此专利提供了一种通过延迟处理器、粗转换器、精细转换器、节点选择器以及编码器构成的时间数字转换器。在有效信号进入电路时,首先生成延迟电压并在延迟电压中选择信号,然后再确定所选择的电压的过零时刻并对所选择的电压和过零时刻进行编码。此电路可以大大提升tdc的分辨率,但是还需要加入模数转换器(adc)进行辅助,这将增加设计的复杂度以及难度并增大芯片的面积。

技术实现要素:

发明目的:本发明针对现有技术存在的问题,提供一种时间数字转换器及转换方法,本发明结构和设计更简单,效率更高,可移植性更高,实现时芯片面积更小。

技术方案:本发明所述的时间数字转换器包括:

延迟链模块,用于对反馈信号和参考时钟信号的误差进行量化,并在每个参考时钟信号的上升沿将量化值输出送至编码电路模块中;

编码电路模块,用于对延迟链模块的输出进行处理,通过全数字逻辑电路将其转换成为固定位宽、有权位的小数。

进一步的,所述延迟链模块包括n级依次连接的延迟单元,其中,第i级延迟单元包括一个延迟缓冲器bi和一个d触发器di,延迟缓冲器bi的输入端连接上一级延迟缓冲器b(i-1)的输出端,若不存在上一级延迟缓冲器b(i-1),则输入反馈信号,延迟缓冲器bi的输出端连接d触发器di的输入端,d触发器di的时钟端输入参考时钟信号,输出端q[i]作为延迟链模块的输出连接到编码电路模块,i=0,…,n-1,n为所需的固定位宽。

进一步的,所述编码电路模块包括上升沿检测电路、下降沿检测电路、先导零逻辑、减法器、二选一选择器、移位寄存器、ram、乘法器、取补码电路,其中,所述上升沿检测电路和下降沿检测电路的输入端连接延迟链模块的输出,上升沿检测电路的输出in1和下降沿检测电路的输出in2接入先导零逻辑,先导零逻辑对应的输出out1和out2接入减法器,减法器计算出out1-out2的结果r1以及out2-out1的结果r2,r1和r2接入二选一选择器,若r1≥0则二选一选择器输出为r1,反之输出r2,二选一选择器的输出经过移位寄存器左移1位后送至乘法器,同时从ram中提取数据送至乘法器中,乘法器的输出经过取补码电路补码运算后,得到tdc输出,即将参考信号和反馈信号的差值转换为固定位宽、有权位的小数的二进制码。

进一步的,所述ram中存储的数据通过以下方式获得:

从反馈信号中找出第一个“01”位置和第一个“10”位置,将第一个“01”位置命名为δtr,将第一个“10”的位置命名为δtf;

根据以下公式计算反馈信号的周期长度tv:

对周期长度tv求倒,穷举变量tv并将所有可能的倒数

本发明所述的时间数字转换方法包括:

(1)采用延迟连模块对反馈信号和参考时钟信号的误差进行量化,输出位宽为n的数据;

(2)采用全数字逻辑电路对步骤(1)的输出进行处理,将其转换成为固定位宽、有权位的小数。

进一步的,步骤(1)具体包括:

(1.1)将n级延迟单元依次连接,其中,第i级延迟单元包括一个延迟缓冲器bi和一个d触发器di,延迟缓冲器bi的输入端连接上一级延迟缓冲器b(i-1)的输出端,延迟缓冲器bi的输出端连接d触发器di的输入端,i=0,…,n-1,n为所需的固定位宽;

(1.2)将反馈信号输入第一级延迟缓冲器b(i-1),将参考时钟信号输入所有d触发器的时钟端,将所有d触发器的输出作为延迟链模块的输出,输入到编码电路模块。

进一步的,步骤(2)具体包括:

(2.1)提取步骤(1)输出的数据,并检测出第一个由低电平到高电平的信号和第一个由高电平到低电平的信号,并将其结果分别作为in1和in2输出;

(2.2)根据步骤(2.1)输出的in1和in2,计算出有效信号的位置,作为out1和out2输出;

(2.3)根据步骤(2.2)输出的out1和out2,计算并输出r1和r2,其中r1=out1-out2,r2=out2-out1;

(2.4)如果r1≥0,则输出r1,否则输出r2;

(2.5)将步骤(2.4)的输出进行左移一位后输出;

(2.6)从ram中提取数据,并将提取的数据与步骤(2.5)的输出相乘后输出;

(2.7)将步骤(2.6)的输出到进行取补码后输出,输出的结果作为tdc的最终输出,即将参考信号和反馈信号的差值转换为固定位宽、有权位的小数的二进制码。

进一步的,所述ram中存储的数据通过以下方式获得:

从反馈信号中找出第一个“01”位置和第一个“10”位置,将第一个“01”位置命名为δtr,将第一个“10”的位置命名为δtf;

根据以下公式计算反馈信号的周期长度tv:

对周期长度tv求倒,穷举变量tv并将所有可能的倒数

有益效果:本发明与现有技术相比,其显著优点是:本发明将电路结构简化为延迟链电路和编码电路两个部分,具有更广的通用性、降低了设计难度,提升了电路的最高工作频率,本实施例当中的编码电路可以由代码综合生成,这样就省去了其他的辅助电路,获得了更高的速度,更小的版图面积,且编码电路由数字综合实现,所以针对不同工艺具有更优的可移植性并更利于片上实现。

附图说明

图1为参考文献1提出的时间数字转换器的结构图;

图2为参考文献2提出的时间数字转换器的结构图;

图3为本发明提供的时间数字转换器的结构图。

具体实施方式

本实施例提供了一种时间数字转换器,如图3所示,包括延迟链模块100和编码电路模块,延迟链模块用于对反馈信号和参考时钟信号的误差进行量化,并在每个参考时钟信号的上升沿将量化值输出送至编码电路模块中;编码电路模块用于对延迟链模块的输出进行处理,通过全数字逻辑电路将其转换成为固定位宽、有权位的小数。

其中,延迟链模块100包括n级依次连接的延迟单元,第i级延迟单元包括一个延迟缓冲器bi和一个d触发器di,延迟缓冲器bi的输入端连接上一级延迟缓冲器b(i-1)的输出端,若不存在上一级延迟缓冲器b(i-1),则输入反馈信号,延迟缓冲器bi的输出端连接d触发器di的输入端,d触发器di的时钟端输入参考时钟信号,输出端q[i]作为延迟链模块的输出连接到编码电路模块,i=0,…,n-1,n为所需的固定位宽。

其中,编码电路模块包括上、下降沿检测电路200、先导零逻辑201、减法器202、二选一选择器203、移位寄存器204、ram205、乘法器206、取补码电路207。上、下降沿检测电路200的输入端连接延迟链模块100的输出,上升沿检测电路的输出in1和下降沿检测电路的输出in2接入先导零逻辑201,先导零逻辑201对应的输出out1和out2接入减法器202,减法器202计算出out1-out2的结果r1以及out2-out1的结果r2,r1和r2接入二选一选择器203,若r1≥0则二选一选择器203输出为r1,反之输出r2,二选一选择器203的输出经过移位寄存器204左移1位后送至乘法器206,同时从ram205中提取数据送至乘法器206中,乘法器206的输出经过取补码电路207补码运算后,得到tdc输出,即将参考信号和反馈信号的差值转换为固定位宽、有权位的小数的二进制码。

其中,ram中存储的数据通过以下方式获得:

从反馈信号中找出第一个“01”位置和第一个“10”位置,将第一个“01”位置命名为δtr,将第一个“10”的位置命名为δtf;

根据以下公式计算反馈信号的周期长度tv:

对周期长度tv求倒,将所有可能的倒数

编码电路模块的电路可以通过代码生成,也可以为实际的硬件电路。

本实施例还提供了一种时间数字转换方法,包括:

(1)采用延迟连模块对反馈信号和参考时钟信号的误差进行量化,输出位宽为n的数据;

具体包括:(1.1)将n级延迟单元依次连接,其中,第i级延迟单元包括一个延迟缓冲器bi和一个d触发器di,延迟缓冲器bi的输入端连接上一级延迟缓冲器b(i-1)的输出端,延迟缓冲器bi的输出端连接d触发器di的输入端,i=0,…,n-1,n为所需的固定位宽;(1.2)将反馈信号输入第一级延迟缓冲器b(i-1),将参考时钟信号输入所有d触发器的时钟端,将所有d触发器的输出作为延迟链模块的输出,输入到编码电路模块。

(2)采用全数字逻辑电路对步骤(1)的输出进行处理,将其转换成为固定位宽、有权位的小数。具体包括以下步骤:

(2.1)提取步骤(1)输出的数据,并检测出第一个由低电平到高电平的信号和第一个由高电平到低电平的信号,并将其结果分别作为in1和in2输出;

(2.2)根据步骤(2.1)输出的in1和in2,计算出有效信号的位置,作为out1和out2输出;

(2.3)根据步骤(2.2)输出的out1和out2,计算并输出r1和r2,其中r1=out1-out2,r2=out2-out1;

(2.4)如果r1≥0,则输出r1,否则输出r2;

(2.5)将步骤(2.4)的输出进行左移一位后输出;

(2.6)从ram中提取数据,并将提取的数据与步骤(2.5)的输出相乘后输出;

(2.7)将步骤(2.6)的输出到进行取补码后输出,输出的结果作为tdc的最终输出,即将参考信号和反馈信号的差值转换为固定位宽、有权位的小数的二进制码。

其中,所述ram中存储的数据通过以下方式获得:

从反馈信号中找出第一个“01”位置和第一个“10”位置,将第一个“01”位置命名为δtr,将第一个“10”的位置命名为δtf;

根据以下公式计算反馈信号的周期长度tv:

对周期长度tv求倒,穷举变量tv并将所有可能的倒数

本实施例通过改变tdc的结构,将电路结构简化为延迟链电路和编码电路两个部分,具有更广的通用性、降低了设计难度,提升了电路的最高工作频率。本实施例当中的编码电路由代码综合生成,所以针对不同的工艺有更优的移植性并更利于集成。

本文用于企业家、创业者技术爱好者查询,结果仅供参考。