1.本发明实施例涉及电感技术领域,尤其涉及一种电感的测试方法和测试系统。

背景技术:

2.市面上现有的一体电感,根据制备工艺的不同可分为一体成型电感和一体绕线电感。示例性地,一体成型电感需要先将一定量的铁粉、粘结剂、脱模粉等混合后造粒,将造粒后的粉料与线圈一起填入模具中,通过一定的压力、温度等条件压合,然后弯折、裁切而成。一体绕线电感的制备方法与一体成型电感类似,需要先造粒,造粒后的粉料做成磁芯,磁芯烘烤固化后进行绕线,将绕线后的半成品与一定量的粉料放置在模具中进行压合成型,然后通过烘烤、剥漆、电镀等一系列制程加工而成。

3.上述两种制备工艺都需要通过高压力成型的方式来达到器件特性,线圈在高压力作用下容易变形,且铁粉与线圈在高压力时也会发生气压变形,这样容易破坏线圈的绝缘层,从而影响器件品质,例如引发电感层间不良。目前,上述成型方式造成的层间不良是一体电感主要的品质不良项,然而,现有技术中缺乏针对一体电感层间不良的改善方法及对策。

技术实现要素:

4.本发明实施例提供一种电感的测试方法和测试系统,以确定一体电感发生层间不良的具体区域。

5.第一方面,本发明实施例提供了一种电感的测试方法,所述电感为一体电感,所述电感包括线圈、电极和包覆所述线圈的粉材;

6.所述电感的测试方法包括:

7.获取待测电感的电感值、直流电阻值和品质因数;

8.根据所述电感值、所述直流电阻值和所述品质因数,基于所述待测电感的第一切片对所述待测电感的线圈、电极和粉材之间的电学性能进行测试;

9.根据所述待测电感的电学性能测试结果,确定所述待测电感的层间不良区域。

10.可选地,所述第一切片为沿所述线圈的中心轴的切片,所述第一切片的切面暴露所述待测电感的各圈线圈的截面、所述电极和所述粉材。

11.可选地,根据所述电感值、所述直流电阻值和所述品质因数,基于所述待测电感的第一切片对所述待测电感的线圈、电极和粉材之间的电学性能进行测试,包括:

12.在所述直流电阻值低于所述待测电感的标准直流电阻值时,对任一第一截面和任一第二截面进行两两测试,以确定二者对应的线圈是否导通;其中,在所述第一切片的切面中,位于所述线圈的中心轴一侧的各圈所述线圈的截面均为所述第一截面,位于所述线圈的中心轴另一侧的各圈所述线圈的截面均为所述第二截面;

13.根据所述待测电感的电学性能测试结果,确定所述待测电感的层间不良区域,包括:

14.在与任一所述第一截面导通的所述第二截面的数量超过一个时,确定所述待测电感的线圈之间发生层间不良。

15.可选地,根据所述电感值、所述直流电阻值和所述品质因数,基于所述待测电感的第一切片对所述待测电感的线圈、电极和粉材之间的电学性能进行测试,包括:

16.在所述电感值低于所述待测电感的标准电感值,且所述直流电阻值大于或等于所述待测电感的标准直流电阻值时,对所述待测电感的两个电极进行测试,以确定二者之间是否导通,并对所述电极和与所述电极相邻的所述线圈的截面进行测试,以确定二者之间是否导通;

17.根据所述待测电感的电学性能测试结果,确定所述待测电感的层间不良区域,包括:

18.在与任一所述电极导通的所述线圈的截面数量超过两个时,确定所述待测电感的线圈与电极之间发生层间不良。

19.可选地,根据所述电感值、所述直流电阻值和所述品质因数,基于所述待测电感的第一切片对所述待测电感的线圈、电极和粉材之间的电学性能进行测试,包括:

20.在所述品质因数低于所述待测电感的标准品质因数,且所述直流电阻值大于或等于标准直流电阻值,所述电感值大于或等于标准电感值时,对所述线圈的截面及其相邻的预设范围内的粉材进行测试,以确定二者之间是否导通;

21.根据所述待测电感的电学性能测试结果,确定所述待测电感的层间不良区域,包括:

22.在任一所述线圈的截面与其相邻的所述预设范围内的粉材导通时,确定所述待测电感的线圈与粉材之间发生层间不良。

23.可选地,在根据所述待测电感的电学性能测试结果,确定所述待测电感的层间不良区域之后,还包括:

24.基于所述待测电感的第二切片对所述待测电感的层间不良区域进行验证;

25.其中,所述第二切片为暴露根据测试结果确定的所述待测电感的层间不良区域的切片。

26.可选地,在根据测试结果确定所述待测电感的线圈之间发生层间不良时,所述第二切片为暴露所述线圈的外表面的切片;

27.在根据测试结果确定所述待测电感的线圈与电极之间发生层间不良时,所述第二切片为暴露各圈所述线圈的截面和所述电极的切片;

28.在根据测试结果确定所述待测电感的线圈与粉材之间发生层间不良时,所述第二切片为暴露各圈所述线圈的截面及其相邻的预设范围内的粉材的切片。

29.可选地,电感的测试方法还包括:

30.根据所述待测电感的层间不良区域,设置待制备电感中的绝缘层。

31.可选地,在所述待测电感的线圈之间发生层间不良,或者线圈与粉材之间发生层间不良时,设置所述待制备电感的绝缘层厚度大于所述待测电感的绝缘层厚度;

32.在所述待测电感的线圈与电极之间发生层间不良时,在所述待制备电感的电极及其相邻的线圈之间增设绝缘层。

33.第二方面,本发明实施例还提供了一种电感的测试系统,所述电感为一体电感,所

述电感包括线圈、电极和包覆所述线圈的粉材;

34.所述电感的测试系统包括:

35.参数获取模块,用于获取待测电感的电感值、直流电阻值和品质因数;

36.测试模块,用于根据所述电感值、所述直流电阻值和所述品质因数,基于所述待测电感的第一切片对所述待测电感的线圈、电极和粉材之间的电学性能进行测试;

37.层间不良确定模块,用于根据所述待测电感的电学性能测试结果,确定所述待测电感的层间不良区域。

38.本发明实施例提供的电感的测试方法和测试系统,能够根据待测电感的电感值、直流电阻值和品质因数预测待测电感的层间不良原因,以根据预测的层间不良原因,基于待测电感的第一切片对待测电感的线圈、电极和粉材之间的电学性能进行测试,从而根据测试结果确定待测电感发生层间不良的具体区域。与现有技术相比,本方案不仅能够根据待测电感的测试结果确定其发生层间不良的具体区域,并且利用该测试结果还有助于对后续待制备的一体电感的层间不良区域进行改善,从而缓解一体电感的层间不良问题,以提升一体电感的产品品质。

附图说明

39.图1是本发明实施例提供的一种电感的测试方法的流程示意图;

40.图2是本发明实施例提供的一种电感切面的结构示意图;

41.图3是本发明实施例提供的另一种电感的测试方法的流程示意图;

42.图4是本发明实施例提供的一种线圈截面的导通状态示意图;

43.图5是本发明实施例提供的一种线圈的电路原理图;

44.图6是本发明实施例提供的另一种电感切面的结构示意图;

45.图7是本发明实施例提供的另一种电感的测试方法的流程示意图;

46.图8是本发明实施例提供的另一种电感切面的结构示意图;

47.图9是本发明实施例提供的另一种电感切面的结构示意图;

48.图10是本发明实施例提供的另一种线圈的电路原理图;

49.图11是本发明实施例提供的另一种电感切面的结构示意图;

50.图12是本发明实施例提供的另一种电感的测试方法的流程示意图;

51.图13是本发明实施例提供的另一种电感切面的结构示意图;

52.图14是本发明实施例提供的另一种线圈的电路原理图;

53.图15是本发明实施例提供的另一种电感的测试方法的流程示意图;

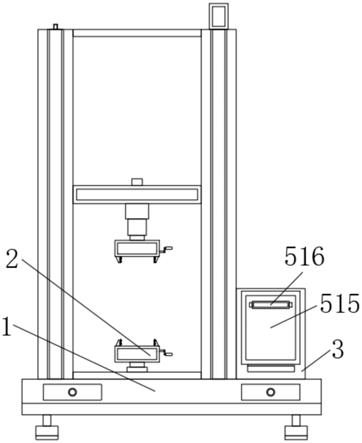

54.图16是本发明实施例提供的一种电感的测试系统的结构示意图;

55.图17是本发明实施例提供的一种终端的结构示意图。

具体实施方式

56.下面结合附图和实施例对本发明作进一步的详细说明。可以理解的是,此处所描述的具体实施例仅仅用于解释本发明,而非对本发明的限定。另外还需要说明的是,为了便于描述,附图中仅示出了与本发明相关的部分而非全部结构。

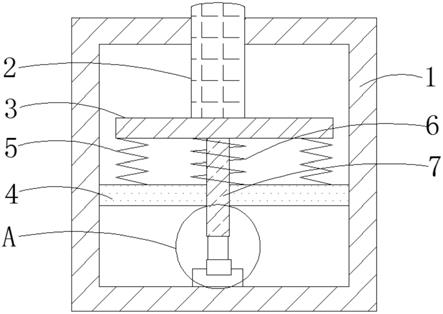

57.本发明实施例提供了一种电感的测试方法,图1是本发明实施例提供的一种电感

的测试方法的流程示意图。本实施例可适用于确定一体电感的层间不良区域的情况,该方法可以由电感的测试系统执行,该系统可以采用软件和/或硬件的方式实现,该系统可配置于电子设备中,例如服务器或终端设备,典型的终端设备包括移动终端,具体包括手机、电脑或平板电脑等。

58.本发明各实施例中的电感均为一体电感,例如采用高压力成型的方式来制备的一体成型电感或一体绕线电感。该电感包括线圈、电极和包覆线圈的粉材。

59.如图1所示,电感的测试方法具体包括:

60.s110、获取待测电感的电感值、直流电阻值和品质因数。

61.图2是本发明实施例提供的一种电感切面的结构示意图,其中的电感可以是待测电感,图2示意性地示出了沿待测电感的线圈的中心轴l所在位置,对该电感进行切片得到的切面图。参见图2,示例性地,该电感的粉材100包覆各圈线圈的外表面,粉材100可以是磁性粉材,粉材200形成该电感的磁性体。该电感的电极包括第一电极200a和第二电极200b,第一电极200a和第二电极200b中的一个连接电感线圈的始端,另一个连接电感线圈的末端。

62.待测电感为存在层间不良的电感,可选地,通过电感线圈的层间短路测量仪确定电感是否存在层间不良,例如根据层间短路测量仪的输出波形确定电感是否存在层间不良,并选择存在层间不良的电感为待测电感。可以通过电感测量仪(lcr)获取待测电感的电感值,并通过直流电阻测量仪(dcr)获取待测电感的直流电阻值。品质因数q是指电感在某一频率的交流电压下工作时,所呈现的感抗与其等效损耗电阻之比。电感的品质因数q越高,其损耗越小,效率越高。

63.通过获取待测电感的电感值、直流电阻值和品质因数,有助于预测待测电感的层间不良类型。示例性地,待测电感的层间不良类型包括但不限于以下几种:

64.层间不良类型(一):电感值低于待测电感的标准电感值,直流电阻值低于待测电感的标准直流电阻值,品质因数低于待测电感的标准品质因数。其中,待测电感的标准电感值、标准直流电阻值和标准品质因数可结合待测电感的型号与规格参数确定。因为待测电感的直流电阻值低于标准直流电阻值,所以可预测待测电感的层间不良的原因是线圈与线圈之间发生短路。

65.层间不良类型(二):电感值低于待测电感的标准电感值,直流电阻值大于或等于待测电感的标准直流电阻值,品质因数低于待测电感的标准品质因数。在待测电感的电感值低于标准电感值,例如待测电感的电感值远小于标准电感值,甚至其电感值接近零,而直流电阻值正常时,说明待测电感的线圈基本失效,因此可预测待测电感的层间不良的原因是两个电极之间发生短路,例如第一电极200a和第二电极200b短接。

66.层间不良类型(三):电感值大于或等于待测电感的标准电感值,直流电阻值大于或等于待测电感的标准直流电阻值,品质因数低于待测电感的标准品质因数。因为待测电感的电感值和直流电阻值均正常,而品质因数偏低,且电感的交流阻抗变大时,品质因数减小,所以可预测待测电感的层间不良的原因是线圈与粉材之间发生导通。

67.s120、根据电感值、直流电阻值和品质因数,基于待测电感的第一切片对待测电感的线圈、电极和粉材之间的电学性能进行测试。

68.可选地,待测电感的第一切片为沿线圈的中心轴的切片,第一切片的切面暴露待

测电感的各圈线圈的截面、电极和粉材。示例性地,图2所示的切面为待测电感的第一切片的切面,该电感包括多圈线圈,该线圈可以是铜线绕制成的线圈,该铜线可以是圆线、扁平线或多股包漆线等。图2示出了该电感包括内外两层线圈,每层线圈包括四圈线圈时,各圈线圈的截面在切面中的分布情况。例如,截面11和截面12为同一圈线圈的两个截面,截面21和截面22为同一圈线圈的两个截面,截面31和截面32为同一圈线圈的两个截面,截面41和截面42为同一圈线圈的两个截面,截面51和截面52为同一圈线圈的两个截面,截面61和截面62为同一圈线圈的两个截面,截面71和截面72为同一圈线圈的两个截面,截面81和截面82为同一圈线圈的两个截面。截面11、12、21、22、31、32、41、42均为内层线圈的截面,截面51、52、61、62、71、72、81、82均为外层线圈的截面。在具体应用时,可根据电感线圈的实际圈数与层数确定各圈线圈的截面分布,本实施例对此不进行限制。

69.示例性地,在根据待测电感的电感值、直流电阻值和品质因数,预测待测电感的层间不良为上述层间不良类型(一)时,可以基于待测电感的第一切片对各圈线圈进行自动测试。例如,测试不同线圈的截面之间的连通性,在正常情况下,第一切片的切面中属于同一圈线圈的截面之间导通,属于不同圈线圈的截面之间断开。因此,通过测试不同线圈的截面之间是否导通,有助于确定待测电感的不同圈线圈之间是否发生短路。

70.在根据待测电感的电感值、直流电阻值和品质因数,预测待测电感的层间不良为上述层间不良类型(二)时,可以基于待测电感的第一切片对各电极和各圈线圈进行自动测试。例如,测试待测电感的两个电极之间的连通性,以确定待测电感的两个电极之间是否发生短路,并测试电极与线圈截面之间的连通性,以进一步确定线圈与电极之间的层间不良区域。在正常情况下,待测电感的第一切片中的两个电极断开,每个电极仅与第一切片的切面中的一圈线圈的截面电连接,并且与除该圈线圈之外的其他圈线圈的截面断开,在待测电感的两个电极短接时,两个电极电连接,并且与其中一个电极电连接的线圈数量大于一圈。

71.在根据待测电感的电感值、直流电阻值和品质因数,预测待测电感的层间不良为上述层间不良类型(三)时,可以基于待测电感的第一切片对各圈线圈及其相邻的粉材进行自动测试。例如,测试各圈线圈的截面及其相邻的粉材100之间的连通性,在正常情况下,待测电感的每圈线圈均与粉材100绝缘,因此,通过测试各圈线圈的截面与粉材之间的连通性,有助于确定待测电感的线圈与粉材之间是否发生导通。

72.s130、根据待测电感的电学性能测试结果,确定待测电感的层间不良区域。

73.示例性地,若通过步骤s120测得待测电感的不同圈线圈之间发生短路,则确定待测电感的层间不良区域具体为发生短路的线圈所在的区域。若通过步骤s120测得待测电感的两个电极之间短路,且任一电极与一圈以上的线圈电连接,则确定待测电感的层间不良区域为相应的线圈与电极之间的区域。若通过步骤s120测得待测电感的线圈与粉材之间是否发生导通,则确定待测电感的层间不良区域具体为线圈与粉材导通的区域。

74.本发明实施例的技术方案,能够根据待测电感的电感值、直流电阻值和品质因数预测待测电感的层间不良原因,以根据预测的层间不良原因,基于待测电感的第一切片对待测电感的线圈、电极和粉材之间的电学性能进行测试,从而根据测试结果确定待测电感发生层间不良的具体区域。与现有技术相比,本方案不仅能够根据待测电感的测试结果确定其发生层间不良的具体区域,并且利用该测试结果还有助于对后续待制备的一体电感的

层间不良区域进行改善,从而缓解一体电感的层间不良问题,以提升一体电感的产品品质。

75.图3是本发明实施例提供的另一种电感的测试方法的流程示意图,在上述实施例的基础上,本实施例进一步优化了电感的测试方法。相应地,如图3所示,本实施例的方法具体包括:

76.s210、获取待测电感的电感值、直流电阻值和品质因数。

77.s220、在直流电阻值低于待测电感的标准直流电阻值时,对任一第一截面和任一第二截面进行两两测试,以确定二者对应的线圈是否导通。

78.参见图2,在第一切片的切面中,位于线圈的中心轴l一侧的各圈线圈的截面均为第一截面,位于线圈的中心轴l另一侧的各圈线圈的截面均为第二截面。例如,a区域内的线圈截面均为第一截面,即截面11、21、31、41、51、61、71、81均为第一截面,b区域内的线圈截面均为第二截面,即截面12、22、32、42、52、62、72、82均为第二截面。

79.示例性地,当前待测电感的电感值低于标准电感值,直流电阻值低于标准直流电阻值,品质因数低于标准品质因数。根据上文中层间不良类型(一)的分析可知,在待测电感的直流电阻值低于标准直流电阻值时,层间不良的原因可能是线圈与线圈之间发生短路。因此,可自动控制万用表对任一第一截面和任一第二截面进行两两测试,以确定二者对应的线圈是否导通。例如,控制万用表的一个探针接触截面11,并控制万用表的另一个探针依次接触b区域内的截面12至82,然后继续控制万用表的一个探针接触截面21,并控制万用表的另一个探针依次接触b区域内的截面12至82,......,直到控制万用表的一个探针接触截面81,并控制万用表的另一个探针依次接触b区域内的截面12至82,以完成a区域内的任一截面与b区域内的任一截面之间的两两测试,从而通过万用表测试a区域内的任一截面与b区域内的任一截面之间的连通性。

80.s230、在与任一第一截面导通的第二截面的数量超过一个时,确定待测电感的线圈之间发生层间不良。

81.在待测电感的各线圈之间未发生短路时,a区域内的每个第一截面均与b区域内的一个第二截面导通。例如,待测电感的第一切片将各线圈一分为二,截面11和截面12为同一圈线圈的两个截面,截面11仅与截面12电连接,同理可知,在各线圈之间未发生短路时,切面中的每个截面仅与和其同属一圈线圈的另一个截面电连接。在某两圈线圈之间导通时,会出现与第一截面导通的第二截面的数量超过一个的情况。

82.图4是本发明实施例提供的一种线圈截面的导通状态示意图,图4仅示意性地示出了对电感进行测试时,在电感的第一切片的切面中,截面21、22、31、32之间的导通状态。示例性地,在控制万用表对截面21、22、31、32进行测试时,测得截面21与截面22和32导通,截面31与截面22和32导通。在正常情况下,截面21仅与截面22导通,截面31仅与截面32导通。因此,截面21和22所属线圈与截面31和32所属线圈之间可能存在一个或多个异常导通点。

83.图5是本发明实施例提供的一种线圈的电路原理图。结合图4和图5,示例性地,l10是截面11和12所属线圈的等效电阻,l20是截面21和22所属线圈的等效电阻,l30是截面31和32所属线圈的等效电阻,l40是截面41和42所属线圈的等效电阻,以此类推,l80是截面81和82所属线圈的等效电阻。在截面21和22所属线圈与截面31和32所属线圈之间存在异常导通点时,相当于等效电阻l20和l30被短接。根据上述测试结果,可确定待测电感的线圈之间发生短路,且相应的层间不良区域为截面21和22所属线圈与截面31和32所属线圈之间。

84.可选地,在步骤s230之后,电感的测试方法还包括:

85.s240、基于待测电感的第二切片对待测电感的层间不良区域进行验证。

86.其中,第二切片为暴露根据测试结果确定的待测电感的层间不良区域的切片。

87.可选地,在根据测试结果确定待测电感的线圈之间发生层间不良时,第二切片为暴露线圈的外表面的切片。

88.图6是本发明实施例提供的另一种电感切面的结构示意图,该切面可以是待测电感的第二切面。结合图4至图6,示例性地,截面11和12均为线圈10的截面,截面21和22均为线圈20的截面,截面31和32均为线圈30的截面,截面41和42均为线圈40的截面,图6中示意性地示出了线圈10至40的外表面。在待测电感的层间不良区域为截面21和22所属线圈与截面31和32所属线圈之间时,待测电感的第二切面暴露内层的线圈10、20、30、40。根据第二切面,能够进一步确定线圈20和30之间存在异常导通点,从而验证待测电感的层间不良区域位于线圈20和30之间,图6中以线圈20和30之间的圆圈对异常导通点的位置进行了示意。

89.可选地,电感的测试方法还包括:

90.s250、根据待测电感的层间不良区域,设置待制备电感中的绝缘层。

91.具体地,待制备电感是一体电感,并且是与待测电感的型号相同、规格参数相同的电感。根据测试确定的待测电感容易发生层间不良的区域,可以对待制备电感的制备工艺进行改进,例如可以在容易发生层间不良的区域增设绝缘层,或者加厚该区域的绝缘层。

92.可选地,在待测电感的线圈之间发生层间不良时,设置待制备电感的绝缘层厚度大于待测电感的绝缘层厚度。例如,根据待测电感的测试结果确定线圈20和30之间存在异常导通点,从而确定待测电感的线圈之间容易发生层间不良,因此可设置待制备电感的绝缘层厚度大于待测电感的绝缘层厚度,例如在待制备电感的制备工艺中,可以为各圈线圈增加绝缘层,或者将各圈线圈浸涂防护层,以使待制备电感的绝缘层厚度大于待测电感的绝缘层厚度。

93.本实施例的技术方案,有助于在待测电感的直流电阻值较低时,确定待测电感的线圈之间是否发生层间不良,并验证待测电感的层间不良区域,有利于根据待测电感的层间不良区域,对待制备电感中的绝缘层进行设置,从而缓解待制备电感的层间不良问题,以提升待制备电感的产品品质。

94.图7是本发明实施例提供的另一种电感的测试方法的流程示意图,本实施例进一步优化了电感的测试方法。可选地,如图7所示,本实施例的方法具体包括:

95.s310、获取待测电感的电感值、直流电阻值和品质因数。

96.s320、在电感值低于待测电感的标准电感值,且直流电阻值大于或等于待测电感的标准直流电阻值时,对待测电感的两个电极进行测试,以确定二者之间是否导通,并对电极和与电极相邻的线圈的截面进行测试,以确定二者之间是否导通。

97.示例性地,当前待测电感的电感值低于标准电感值,直流电阻值大于或等于标准直流电阻值,品质因数低于标准品质因数。根据上文中层间不良类型(二)的分析可知,在待测电感的电感值低于标准电感值,直流电阻值正常时,层间不良的原因可能是两个电极之间发生短路。因此,可自动控制万用表对待测电感的两个电极进行测试,以确定两个电极是否导通,并对电极和与电极相邻的线圈的截面进行测试,以确定电极及其相邻的线圈之间是否导通,从而确定线圈与电极之间的层间不良区域。

98.图8是本发明实施例提供的另一种电感切面的结构示意图,该切面可以是待测电感的第一切面。参见图8,示例性地,与待测电感的第一电极200a和第二电极200b相邻的线圈截面为截面11、12、81、82,控制万用表的一个探针接触待测电感的第一电极200a,并控制万用表的另一个探针依次接触截面11、12、81、82,以通过万用表测试第一电极200a及其相邻的线圈截面之间的连通性。控制万用表的一个探针接触待测电感的第二电极200b,并控制万用表的另一个探针依次接触截面11、12、81、82,以通过万用表测试第二电极200b及其相邻的线圈截面之间的连通性。

99.s330、在与任一电极导通的线圈的截面数量超过两个时,确定待测电感的线圈与电极之间发生层间不良。

100.示例性地,在待测电感的第一电极200a和第二电极200b之间未发生短路时,在第一切片的切面中,第一电极200a和第二电极200b断开,且一个电极与位于电感线圈始端的线圈电连接,另一个电极与位于电感线圈末端的线圈电连接。例如,截面11和12所属的线圈位于电感线圈的始端,截面81和82所属的线圈位于电感线圈的末端,在第一切片的切面中,第一电极200a与截面11电连接,并通过连接在截面11和12之间的铜线与截面12电连接,第二电极200b与截面82电连接,并通过连接在截面81和82之间的铜线与截面81电连接。在控制万用表对待测电感进行测试时,若测得第一电极200a和第二电极200b导通,第一电极200a与截面11、12、81、82电连接,且第二电极200b与截面11、12、81、82电连接,则确定第一电极200a和第二电极200b短路,并且电极短路的原因是第一电极200a与截面81之间存在异常导通点,或者第二电极200b与截面12之间存在异常导通点,从而造成线圈与电极之间的层间不良。

101.需要说明的是,图8仅示意性地示出了第一电极200a与截面11和81之间的导通状态,以及第二电极200b与截面12和82之间的导通状态,由于截面11还与截面12电连接,截面81还与截面82电连接,因此实际与每个电极电连接的截面数量均为四个。

102.可选地,在步骤s330之后,电感的测试方法还包括:

103.s340、基于待测电感的第二切片对待测电感的层间不良区域进行验证。

104.其中,第二切片为暴露根据测试结果确定的待测电感的层间不良区域的切片。

105.可选地,在根据测试结果确定待测电感的线圈与电极之间发生层间不良时,第二切片为暴露各圈线圈的截面和电极的切片。

106.图9是本发明实施例提供的另一种电感切面的结构示意图,该切面可以是待测电感的第二切面。结合图8和图9,在根据测试结果确定待测电感的线圈与电极之间发生层间不良,使得第一电极200a和第二电极200b短路时,可根据第二切片验证线圈与电极之间的异常导通点所在区域。在该情况下,第二切片的截面可以与第一切片的截面相同,或者第二切片也可以是暴露各圈线圈的截面和电极,并且与第一切片的剖切位置不同的切片。示例性地,图9以截面和电极之间的多个圆圈对异常导通点的位置进行了示意,在该情况下,根据第二切片可验证第一电极200a与截面11和81之间,以及第二电极200b与截面12和82之间均存在异常导通点,从而造成线圈与电极之间的层间不良。

107.图10是本发明实施例提供的另一种线圈的电路原理图。结合图8至图10,示例性地,l10是截面11和12所属线圈的等效电阻,l20是截面21和22所属线圈的等效电阻,l30是截面31和32所属线圈的等效电阻,l40是截面41和42所属线圈的等效电阻,以此类推,l80是

截面81和82所属线圈的等效电阻。在第一电极200a与截面11和81之间,以及第二电极200b与截面12和82之间均存在异常导通点时,相当于第一电极200a和第二电极200b之间的等效电阻l10至l80均被短接。

108.可选地,电感的测试方法还包括:

109.s350、根据待测电感的层间不良区域,设置待制备电感中的绝缘层。

110.可选地,在待测电感的线圈与电极之间发生层间不良时,在待制备电感的电极及其相邻的线圈之间增设绝缘层。

111.图11是本发明实施例提供的另一种电感切面的结构示意图,该电感可以是待制备电感。参见图11,示例性地,根据待测电感的测试结果确定第一电极200a与截面11和81之间,以及第二电极200b与截面12和82之间均存在异常导通点,从而确定待测电感的电极及其相邻的线圈之间容易发生层间不良时,可以在待制备电感的第一电极200a与截面11和81之间,以及第二电极200b与截面12和82之间均增设绝缘层400,从而缓解待制备电感的电极及其相邻的线圈之间的层间不良。

112.本实施例的技术方案,有助于在待测电感的电感值较低,品质因数较低,而直流电阻值正常时,确定待测电感的线圈与电极之间是否发生层间不良,并验证待测电感的层间不良区域,有利于根据待测电感的层间不良区域,对待制备电感中的绝缘层进行设置,从而缓解待制备电感的层间不良问题,以提升待制备电感的产品品质。

113.图12是本发明实施例提供的另一种电感的测试方法的流程示意图,本实施例进一步优化了电感的测试方法。可选地,如图12所示,本实施例的方法具体包括:

114.s410、获取待测电感的电感值、直流电阻值和品质因数。

115.s420、在品质因数低于待测电感的标准品质因数,且直流电阻值大于或等于标准直流电阻值,电感值大于或等于标准电感值时,对线圈的截面及其相邻的预设范围内的粉材进行测试,以确定二者之间是否导通。

116.示例性地,当前待测电感的品质因数低于待测电感的标准品质因数,且直流电阻值大于或等于标准直流电阻值,电感值大于或等于标准电感值。根据上文中层间不良类型(三)的分析可知,在待测电感的电感值和直流电阻值均正常,而品质因数偏低时,层间不良的原因可能是线圈与粉材之间发生导通。因此,可自动控制万用表对待测电感的各线圈截面及其相邻的预设范围内的粉材进行测试,以确定线圈与粉材之间是否导通。

117.图13是本发明实施例提供的另一种电感切面的结构示意图,该切面可以是待测电感的第一切面。与线圈截面相邻的预设范围内的粉材所在的具体区域可以根据需求进行设置,图13示意性地示出了与截面11相邻的预设范围内的粉材为c区域内的粉材的情况。参见图13,示例性地,可控制万用表的一个探针接触截面11,并控制万用表的另一个探针接触c区域内的粉材,然后控制万用表的一个探针接触截面21,并控制万用表的另一个探针接触与截面21相邻的预设范围内的粉材,......,直到控制万用表的一个探针接触截面81,并控制万用表的另一个探针接触与截面81相邻的预设范围内的粉材,已完成位于线圈的中心轴左侧的各线圈截面及其相邻的预设范围内的粉材之间的测试,然后继续表完成位于线圈的中心轴右侧的各线圈截面及其相邻的预设范围内的粉材之间的测试,从而通过万用表测试第一切片的切面内所有截面及其相邻的预设范围内的粉材之间连通性。

118.图14是本发明实施例提供的另一种线圈的电路原理图。结合图13至图14,示例性

地,l10是截面11和12所属线圈的等效电阻,l20是截面21和22所属线圈的等效电阻,l30是截面31和32所属线圈的等效电阻,l40是截面41和42所属线圈的等效电阻,以此类推,l80是截面81和82所属线圈的等效电阻。例如,在根据测试结果确定截面12及其相邻的预设范围内的粉材之间导通时,相当于等效电阻l10和等效电阻l10连接等效电阻l20的一侧之间存在短接。

119.s430、在任一线圈的截面与其相邻的预设范围内的粉材导通时,确定待测电感的线圈与粉材之间发生层间不良。

120.在待测电感的线圈与粉材之间未发生短路时,每个线圈的截面均与周围的粉材绝缘。若通过万用表测试发现任一线圈的截面与其相邻的预设范围内的粉材导通,则确定该线圈与粉材之间发生层间不良。

121.可选地,在步骤s430之后,电感的测试方法还包括:

122.s440、基于待测电感的第二切片对待测电感的层间不良区域进行验证;

123.其中,第二切片为暴露根据测试结果确定的待测电感的层间不良区域的切片。

124.可选地,在根据测试结果确定待测电感的线圈与粉材之间发生层间不良时,第二切片为暴露各圈线圈的截面及其相邻的预设范围内的粉材的切片。具体地,第二切片的截面可以与图13所示的第一切片的截面相同,或者第二切片也可以是暴露各圈线圈的截面及其相邻的预设范围内的粉材,并且与第一切片的剖切位置不同的切片。根据第二切片,能够进一步验证待测电感的线圈及其周围的粉材之间的异常导通点。

125.可选地,电感的测试方法还包括:

126.s450、根据待测电感的层间不良区域,设置待制备电感中的绝缘层。

127.可选地,在待测电感的线圈与粉材之间发生层间不良时,设置待制备电感的绝缘层厚度大于待测电感的绝缘层厚度。示例性地,在待制备电感的制备工艺中,可以为各圈线圈增加绝缘层,或者将各圈线圈浸涂防护层,以使待制备电感的绝缘层厚度大于待测电感的绝缘层厚度。

128.本实施例的技术方案,有助于在待测电感的品质因数较低,而直流电阻值和电感值均正常时,确定待测电感的线圈及其周围的粉材之间是否发生层间不良,并验证待测电感的层间不良区域,有利于根据待测电感的层间不良区域,对待制备电感中的绝缘层进行设置,从而缓解待制备电感的层间不良问题,以提升待制备电感的产品品质。

129.图15是本发明实施例提供的另一种电感的测试方法的流程示意图,本实施例进一步优化了电感的测试方法。可选地,如图15所示,本实施例的方法具体包括:

130.s510、通过层间短路测量仪筛选待测电感。

131.其中,待测电感为通过层间短路测量仪进行筛选得到的存在层间不良的一体电感。

132.s520、通过电感测量仪测量待测电感的电感值,通过直流电阻测量仪测量待测电感的直流电阻值,并确定待测电感的品质因数。

133.s530、根据电感值、直流电阻值和品质因数,控制万用表基于待测电感的第一切片对待测电感的线圈、电极和粉材进行测试,以根据测试结果初步确定待测电感的层间不良区域。

134.示例性地,待测电感的第一切片可以是粗砂纸切片,第一切片的切面暴露待测电

感的各圈线圈的截面、电极和粉材。在待测电感的电感值低于标准电感值,直流电阻值低于标准直流电阻值,品质因数低于标准品质因数时,可以控制万用表对第一切片中位于线圈的中心轴一侧的各第一截面,与位于线圈的中心轴另一侧的各第二截面进行两两测试,以确定待测电感的线圈之间是否出现层间不良。在待测电感的电感值低于标准电感值,直流电阻值大于或等于标准直流电阻值,品质因数低于标准品质因数时,可以控制万用表对待测电感的电极和与电极相邻的线圈的截面进行测试,以确定待测电感的电极与线圈之间是否出现层间不良,从而引起待测电感的两个电极之间的短路。在待测电感的品质因数低于待测电感的标准品质因数,且直流电阻值大于或等于标准直流电阻值,电感值大于或等于标准电感值时,可以控制万用表对第一切片中各线圈的截面及其相邻的预设范围内的粉材进行测试,以确定待测电感的线圈与粉材之间是否出现层间不良。

135.s540、根据待测电感的第二切片对待测电感的层间不良区域进行验证。

136.示例性地,待测电感的第二切片可以是细砂纸切片,且第二切片为暴露根据测试结果确定的待测电感的层间不良区域的切片。

137.s550、根据待测电感的层间不良区域,对待制备电感的制备工艺进行改进。

138.具体地,待制备电感是一体电感,并且是与待测电感的型号相同、规格参数相同的电感。根据测试确定的待测电感容易发生层间不良的区域,可以对待制备电感的制备工艺进行改进,例如可以在容易发生层间不良的区域增设绝缘层,或者加厚该区域的绝缘层。

139.s560、判断制备完成后的待制备电感是否存在层间不良问题。

140.若制备完成后的待制备电感存在层间不良问题,则执行s570;若制备完成后的待制备电感不存在层间不良问题,则执行s580。

141.s570、将制备完成后的待制备电感确定为新的待测电感。

142.在执行步骤s570之后,可返回执行s520,继续对该电感进行测试。

143.s580、通过改进后的制备工艺制备其余的待制备电感。

144.本发明实施例的技术方案,能够根据待测电感的电感值、直流电阻值和品质因数预测待测电感的层间不良原因,以根据预测的层间不良原因,基于待测电感的第一切片对待测电感的线圈、电极和粉材之间的电学性能进行测试,从而根据测试结果确定待测电感发生层间不良的具体区域。与现有技术相比,本方案不仅能够根据待测电感的测试结果确定其发生层间不良的具体区域,并且利用该测试结果还有助于对后续待制备的一体电感的层间不良区域进行改善,从而缓解一体电感的层间不良问题,以提升一体电感的产品品质。

145.图16是本发明实施例提供的一种电感的测试系统的结构示意图,本实施例可适用于确定一体电感的层间不良区域的情况。本发明实施例所提供的电感的测试系统,可执行本发明任意实施例所提供的电感的测试方法,具备执行方法相应的功能模块和有益效果。该电感为一体电感,电感包括线圈、电极和包覆线圈的粉材。

146.参见图16,电感的测试系统具体包括参数获取模块610、测试模块620和层间不良确定模块630,其中:

147.参数获取模块610用于获取待测电感的电感值、直流电阻值和品质因数;

148.测试模块620用于根据电感值、直流电阻值和品质因数,基于待测电感的第一切片对待测电感的线圈、电极和粉材之间的电学性能进行测试;

149.层间不良确定模块630用于根据待测电感的电学性能测试结果,确定待测电感的

层间不良区域。

150.本发明实施例所提供的电感的测试系统,可执行本发明任意实施例所提供的电感的测试方法,具备执行方法相应的功能模块和有益效果,不再赘述。

151.图17是本发明实施例提供的一种终端的结构示意图。图17示出了适于用来实现本发明实施方式的示例性设备412的框图。图17显示的设备412仅仅是一个示例,不应对本发明实施例的功能和使用范围带来任何限制。

152.如图17所示,设备412以通用设备的形式表现。设备412的组件可以包括但不限于:一个或者多个处理器416,存储装置428,连接不同系统组件(包括存储装置428和处理器416)的总线418。

153.总线418表示几类总线结构中的一种或多种,包括存储装置总线或者存储装置控制器,外围总线,图形加速端口,处理器或者使用多种总线结构中的任意总线结构的局域总线。举例来说,这些体系结构包括但不限于工业标准体系结构(industry subversive alliance,isa)总线,微通道体系结构(micro channel architecture,mac)总线,增强型isa总线、视频电子标准协会(video electronics standards association,vesa)局域总线以及外围组件互连(peripheral component interconnect,pci)总线。

154.设备412典型地包括多种计算机系统可读介质。这些介质可以是任何能够被设备412访问的可用介质,包括易失性和非易失性介质,可移动的和不可移动的介质。

155.存储装置428可以包括易失性存储器形式的计算机系统可读介质,例如随机存取存储器(random access memory,ram)430和/或高速缓存存储器432。设备412可以进一步包括其它可移动/不可移动的、易失性/非易失性计算机系统存储介质。仅作为举例,存储系统434可以用于读写不可移动的、非易失性磁介质(图17未显示,通常称为“硬盘驱动器”)。尽管图17中未示出,可以提供用于对可移动非易失性磁盘(例如“软盘”)读写的磁盘驱动器,以及对可移动非易失性光盘,例如只读光盘(compact disc read

‑

only memory,cd

‑

rom),数字视盘(digital video disc

‑

read only memory,dvd

‑

rom)或者其它光介质读写的光盘驱动器。在这些情况下,每个驱动器可以通过一个或者多个数据介质接口与总线418相连。存储装置428可以包括至少一个程序产品,该程序产品具有一组(例如至少一个)程序模块,这些程序模块被配置以执行本发明各实施例的功能。

156.具有一组(至少一个)程序模块442的程序/实用工具440,可以存储在例如存储装置428中,这样的程序模块442包括但不限于操作系统、一个或者多个应用程序、其它程序模块以及程序数据,这些示例中的每一个或某种组合中可能包括网络环境的实现。程序模块442通常执行本发明所描述的实施例中的功能和/或方法。

157.设备412也可以与一个或多个外部设备414(例如键盘、指向终端、显示器424等)通信,还可与一个或者多个使得用户能与该设备412交互的终端通信,和/或与使得该设备412能与一个或多个其它计算终端进行通信的任何终端(例如网卡,调制解调器等等)通信。这种通信可以通过输入/输出(i/o)接口422进行。并且,设备412还可以通过网络适配器420与一个或者多个网络(例如局域网(local area network,lan),广域网(wide area network,wan)和/或公共网络,例如因特网)通信。如图17所示,网络适配器420通过总线418与设备412的其它模块通信。应当明白,尽管图中未示出,可以结合设备412使用其它硬件和/或软件模块,包括但不限于:微代码、终端驱动器、冗余处理器、外部磁盘驱动阵列、磁盘阵列

(redundant arrays of independent disks,raid)系统、磁带驱动器以及数据备份存储系统等。

158.处理器416通过运行存储在存储装置428中的程序,从而执行各种功能应用以及数据处理,例如实现本发明实施例所提供的电感的测试方法,该方法包括:

159.获取待测电感的电感值、直流电阻值和品质因数;

160.根据电感值、直流电阻值和品质因数,基于待测电感的第一切片对待测电感的线圈、电极和粉材之间的电学性能进行测试;

161.根据待测电感的电学性能测试结果,确定待测电感的层间不良区域。

162.本发明实施例还提供了一种计算机可读存储介质,其上存储有计算机程序,该程序被处理器执行时实现如本发明实施例所提供的电感的测试方法,该方法包括:

163.获取待测电感的电感值、直流电阻值和品质因数;

164.根据电感值、直流电阻值和品质因数,基于待测电感的第一切片对待测电感的线圈、电极和粉材之间的电学性能进行测试;

165.根据待测电感的电学性能测试结果,确定待测电感的层间不良区域。

166.本发明实施例的计算机存储介质,可以采用一个或多个计算机可读的介质的任意组合。计算机可读介质可以是计算机可读信号介质或者计算机可读存储介质。计算机可读存储介质例如可以是,但不限于是电、磁、光、电磁、红外线、或半导体的系统、装置或器件,或者任意以上的组合。计算机可读存储介质的更具体的例子(非穷举的列表)包括:具有一个或多个导线的电连接、便携式计算机磁盘、硬盘、随机存取存储器(ram)、只读存储器(rom)、可擦式可编程只读存储器(eprom或闪存)、光纤、便携式紧凑磁盘只读存储器(cd

‑

rom)、光存储器件、磁存储器件、或者上述的任意合适的组合。在本文件中,计算机可读存储介质可以是任何包含或存储程序的有形介质,该程序可以被指令执行系统、装置或者器件使用或者与其结合使用。

167.计算机可读的信号介质可以包括在基带中或者作为载波一部分传播的数据信号,其中承载了计算机可读的程序代码。这种传播的数据信号可以采用多种形式,包括但不限于电磁信号、光信号或上述的任意合适的组合。计算机可读的信号介质还可以是计算机可读存储介质以外的任何计算机可读介质,该计算机可读介质可以发送、传播或者传输用于由指令执行系统、装置或者器件使用或者与其结合使用的程序。

168.计算机可读介质上包含的程序代码可以用任何适当的介质传输,包括但不限于无线、电线、光缆、rf等等,或者上述的任意合适的组合。

169.可以以一种或多种程序设计语言或其组合来编写用于执行本发明操作的计算机程序代码,所述程序设计语言包括面向对象的程序设计语言,诸如java、smalltalk、c ,还包括常规的过程式程序设计语言,诸如“c”语言或类似的程序设计语言。程序代码可以完全地在用户计算机上执行、部分地在用户计算机上执行、作为一个独立的软件包执行、部分在用户计算机上部分在远程计算机上执行、或者完全在远程计算机或终端上执行。在涉及远程计算机的情形中,远程计算机可以通过任意种类的网络,包括局域网(lan)或广域网(wan),来连接到用户计算机,或者,可以连接到外部计算机(例如利用因特网服务提供商来通过因特网连接)。

170.注意,上述仅为本发明的较佳实施例及所运用技术原理。本领域技术人员会理解,

本发明不限于这里所述的特定实施例,对本领域技术人员来说能够进行各种明显的变化、重新调整和替代而不会脱离本发明的保护范围。因此,虽然通过以上实施例对本发明进行了较为详细的说明,但是本发明不仅仅限于以上实施例,在不脱离本发明构思的情况下,还可以包括更多其他等效实施例,而本发明的范围由所附的权利要求范围决定。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。