基于三维堆叠的mimo雷达微系统电路芯片

技术领域

1.本发明涉及雷达数字信号处理技术领域,具体是一种基于三维堆叠的mimo雷达微系统电路芯片,可应用于小型化mimo雷达系统中。

背景技术:

2.为了应对日益复杂的电磁干扰环境(强对抗、强干扰),当前的雷达往往需要集成多频段、多传感器、主被动复合、分布式协同调用功能。在现阶段,各个功能模块都是相互独立设计的。功能模块一般都由天线、发射/接收模拟前端、频率源、信号处理等分立组件构成。随着功能不断增多,这种定制开发方法导致硬件规模不断膨胀,而且研制周期很长,不仅难以迅速满足mimo雷达要求,还带来成本高昂、采购、测试和升级困难等问题。因此,要在资源受限的mimo雷达平台上,如何确保设备小负荷、低功耗的前提下实现高复杂度的任务成为雷达系统丞待解决的一个难题。

技术实现要素:

3.针对现有技术存在的问题,本发明的目的在于提供一种基于三维堆叠的mimo雷达微系统电路芯片,本发明通过前端射频信道综合和数字基带综合技术实现mimo雷达上电气电子设备小型化、模块化集成设计,从而大幅减少设备的软硬件规模。

4.为了达到上述目的,本发明采用以下技术方案予以实现。

5.基于三维堆叠的mimo雷达微系统电路芯片,采用系统级封装,对外封装形式采用焊球阵列封装,且对外伸管脚,管壳结构封装外壳,内部基板为多层高密度陶瓷腔体基板,所述多层高密度陶瓷腔体基板的中间设有阶梯型空腔,所述阶梯型空腔的每个阶梯对应一层,由底层到最上层的腔体逐渐增大,每个阶梯面上设有焊盘;所述阶梯型空腔的底面为底层,该底层上安装有信号处理模块,所述阶梯形空腔的中间层和顶层安装有射频前端模块;

6.在接收信号时,所述射频前端模块用于从天线阵面和tr组件接收信号,并对接收信号做放大、下变频和滤波处理;在发射信号时,所述射频前端模块用于将信号处理模块输送过来的发射信号做二级上变频和功率放大处理;所述射频前端模块包含pa、lna、混频器、滤波器组、本振、时钟;其中,滤波器组、本振和时钟源位于所述阶梯形空腔的中间层,pa、混频器和lna位于所述阶梯形空腔的顶层;

7.在接收信号时,所述信号处理模块用于采集射频前端模块的下变频、滤波处理的信号;在发射信号时,所述信号处理模块用于将基带信号做一级上变频处理发射到所述射频前端模块;所述信号处理模块包含一片集成有8路adc、8路dac、arm和fpga的rfsoc芯片、两片ddr4和一片nor flash;其中,所述rfsoc芯片倒装于基板的底层中间,两片ddr4分别放置在rfsoc的两边,且分别连接到rfsoc芯片的pl端和ps端的ddr控制端口,nor flash将放在ps端的ddr4旁边用于连接rfsoc的配置io端口;

8.rfsoc通过fpga的io端口组成控制协议总线与所述射频前端模块的pa、lna、本振、滤波器组和时钟源连接。

9.进一步地,所述射频前端模块包含8路本振,所述8路本振对应的放在中间位置,滤波器组设置于本振的左边,时钟源设置于本振的右边。

10.进一步地,所述阶梯形空腔包含6层阶梯,从下往上,1~2层焊接所述信号处理模块,3~4层埋置滤波器组、本振和时钟源;5~6层安装pa、混频器和lna;每一层芯片均设置于硅转接板上,且其与阶梯形空腔的各层阶梯面分别通过键合线连接。

11.更进一步地,设置于所述阶梯形空腔的顶层、中间层和底层的芯片分别通过硅通孔将部分连接点直接接触到相邻层;所述时钟源通过硅通孔直接将信号处理模块所需的时钟种类端口连接起来。

12.进一步地,所述信号处理模块中的adc和dac由arm端配置采集模式,并通过axis协议总线将数据回传到fpga中。

13.进一步地,各个芯片通过共晶焊接在多层高密度陶瓷腔体基板上,各个阶梯面上的焊盘之间通过基板上的内埋线路实现电气连接。

14.进一步地,所述多层高密度陶瓷腔体基板的底面接入半导体制冷器,用于整个微系统的散热处理。

15.与现有技术相比,本发明的有益效果为:

16.(1)本发明采用三维堆叠技术,将射频前端和信号处理集成于多层高密度陶瓷腔体基板,使得射频前端电路以芯片组的方式集成到微系统模块当中,降低了板块空间的使用,同时实现数字与模拟电路的有效隔离,且数字域的控制器能更好的对前端进行灵活配置。

17.(2)本发明中,数字部分采用具有6g的采样模拟带宽同时集成了ad的转换速率为5gs/s和da的转换速率为10gs/s的8发8收通道的rfsoc,适合mimo雷达的多个rf频段采样。

18.(3)本发明能够将射频前端模块灵活设置,将射频前端以旁路掉的方式,直接实现ad射频直采、da直接射频输出,将模拟信号处理直接转到数字域,具有更高可编程性的解决方案,在降低系统的功耗同时更加灵活应用多场景的mimo雷达模式。

附图说明

19.下面结合附图和具体实施例对本发明做进一步详细说明。

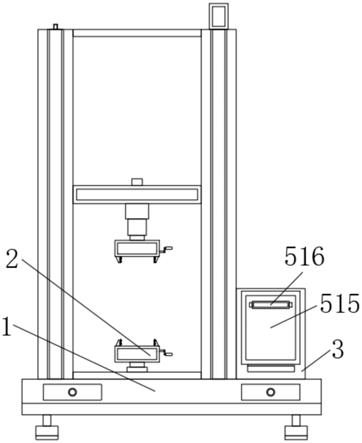

20.图1为本发明基于三维堆叠的mimo雷达微系统电路芯片的系统框图;

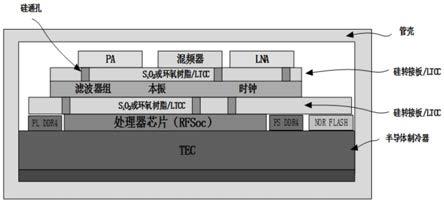

21.图2为本发明的基于三维堆叠mimo雷达的集成微系统的层次图;

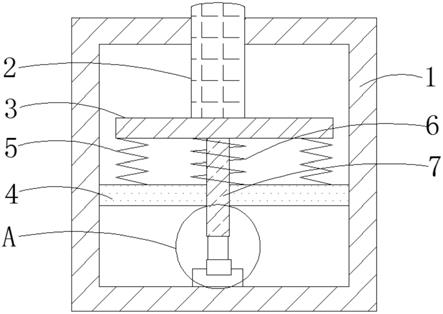

22.图3为本发明的基板开腔嵌入芯片叠层体剖面图;

23.图4为本发明的综合配置时钟源系统框图。

具体实施方式

24.下面将结合实施例对本发明的实施方案进行详细描述,但是本领域的技术人员将会理解,下列实施例仅用于说明本发明,而不应视为限制本发明的范围。

25.随着新技术的发展,mimo雷达系统更新换代对于现代技术的电子集成度提出了更高的要求,在同一射频前端实现多个工作频段的按需配置,在同一信号处理后端实现按任务需求实时切换,减小mimo雷达平台的负荷、消除电磁干扰、满足“尺寸、重量和功率”(swap)需求。

26.针对上述现状,参考图1,本发明提供的一种基于三维堆叠的mimo雷达微系统电路芯片,图1是本发明的基于mimo的微系统集成新技术的原理框图。本发明中主要是分为两部分:射频前端模块和信号处理模块,该设置将模拟电路和数字电路相隔开,保证信号的完整性。其中信号处理模块中的fpga通过对应的通信控制总线协议io端口连接射频前端的pa、lna、本振、和时钟源以及滤波器组的控制端口,信号处理中的adc和dac由arm端配置采集模式,并通过axis协议总线将数据回传到fpga处理分集。对于3d堆叠技术中芯片连接线的总数控制在一定的范围内,电气连接均可通过基板上焊盘、内埋线路和键合线跳到腔体各级中,实现电气的连接。其中配置在rfsoc的ddr4和nor flash芯片也通过对应的并排堆叠的方式实现电气线路的连接。

27.采用3d(三维)堆叠技术的mimo微系统集成电路芯片,采用系统级封装,对外伸管脚通过bga(焊球阵列封装)形式引出,管壳结构封装外壳,内部基板为多层高密度陶瓷腔体基板,所述多层高密度陶瓷腔体基板的中间设有阶梯型空腔,所述阶梯型空腔的每个阶梯对应一层,由底层到最上层的腔体逐渐增大,每个阶梯面上设有焊盘;所述阶梯型空腔的底面为底层,该底层上安装有信号处理模块,所述阶梯形空腔的中间层和顶层安装有射频前端模块。内部芯片堆叠融合flip

‑

chip(倒装芯片)、tsv(硅通孔)、bondwire(键合线)、ltcc/htcc多层高密度陶瓷腔体基板将芯片嵌联结以及埋置无源器件,实现各模块、各功能、各器件管脚的电气互连。

28.参见图2为本发明的微系统内部射频前端和信号处理的模块的芯片堆叠示意图,也是各级腔体高密度陶瓷电路转接基板层次图。

29.本发明中的射频前端模块用于从天线阵面和tr组件接收回来的信号数据做放大和下变频、滤波处理,以及将信号处理模块发射信号数据做二级上变频和功率放大处理。由8路pa、8路lna、8路混频器、8路本振、接收端滤波器组和时钟源组成,8路pa放在腔体的1~2层的左边,8路lna位于腔体1~2层的右边,混频则放在8路pa和8路lna的中间;接下来的3~4层腔体中,接收端的滤波器组摆放在左边,时钟源则摆放在右边基板上,对于提供载波信号的8路本振对应的放在中间位置,其中1~2层通过硅通孔技术将部分连接点直接接触到3~4层,将大大减少对应高速链路的延迟和电磁干扰。此外,时钟源也通过硅通孔技术直接将信号处理模块所需的时钟种类端口连接起来。

30.本发明中信号处理模块用于采集射频前端下变频、滤波处理的信号和将基带信号做一级上变频处理发射到射频前端。由一片集成了8路adc和8路dac、arm和fpga的rfsoc、两片ddr4和一片nor flash组成,该模块中的所有芯片都将置于多级腔体的5~6层中,其中rfsoc的pl端ddr4将安装在其左边,ps端ddr4将摆放在右边以及还有nor flash也放在基板的右边,将rfsoc倒装在基板的中间。

31.本发明中的各个芯片以及裸芯片经过合理的3d堆叠布局,通过共晶焊接技术在多级腔体陶瓷电路基板上,各芯片的管脚通过硅通孔、各层键合线以及基板上的焊盘实现互联,焊盘之间通过基板上的内埋线路实现电气的连接,整个芯片的堆叠结构稳定可靠,抗震能力强。

32.随着mimo雷达在军事领域的应用越来越广泛,应用的场合针对多功能与模块化、低成本与小型化,以及高可靠的要求,这就要保证mimo雷达具备高性能实时处理与控制能力的需求,则对于先进的集成技术提出了更高的挑战。

33.本发明是基于mimo的集成微系统的新技术,在为减低前端tr组件的庞大设计的冗余量,将前端射频电路中的pa、lna、本振、混频器以及滤波器通过先进的3d堆叠集成技术实现小型化多功能的灵活可配置的微系统,大大减轻了原来mimo雷达的系统空间布局。更具有意义的是,集成度越高,性能大大的提升,相对应的功耗也是很好得到控制。是由于减少了面积的使用,使得中间连接线更短,高频线路的特性得到优化,线路上消耗的功率更少,从而一定程度上满足了低功耗的作用。而将前端射频与信号处理模块融合在一起,更使得mimo雷达实现了真正的一体化集成,能够根据各项任务目标,在功能、频率等方面对融合的射频前端进行调度,在接收带宽、接收增益、采样模式、基带发射信号形式、发射功率、发射带宽等环节的自主搭配要求。

34.实施例2

35.基于三维堆叠的mimo雷达微系统芯片,有效的将射频前端和信号处理模块结合,总体结构同实施例1,参见图1,本发明的信号处理模块中具有6g的采样模拟带宽,同时集成了ad的转换速率为5gs/s和da的转换速率为10gs/s的8发8收通道的rfsoc,自带ddc(下变频器)、duc(上变频器)、抽取器、插值器和nco(数字可控振荡器),可以直接在数字端做一级上变频就可以满足一般mimo的雷达要求,从而可以将射频前端模块对应的芯片做旁路处理,达到功耗进一步的降低。又或是降低前端射频的pa的高带宽要求,在信号处理模块做完一级上变频处理后,再在射频前端模块进行二级变频,保证前端的pa满足一定的线性范围内工作,防止pa的失真度。

36.接收端同理,射频前端模块进行一级下变频处理,再在信号处理端使用数字下变频做二级处理,进一步选取对应的抽取滤波,降低数据率再做处理,这些都具有专用的资源而不占用fpga其他资源,极大的提高了整个链路的数据处理能力,为预留其他预处理模块提供更多的资源,功能模块也得到大大的拓展。

37.实施例3

38.本发明中,参见图1,信号处理模块不再采用分立的adc、dac加fpga的架构,而是直接将adc、dac、arm和fpga集成在一起,采集到的信号数据直接通过axis通用的总线送入到fpga,减少了之前的jesd204b的总线接口开支,不仅满足大带宽、高采样率的模拟信号采样和发射,还满足用更低的功耗实现更高的性能模式,采用该器件相较之前削减了50

‑

75%的功耗和封装尺寸,同时无需再使用jesd204b ip核和串行收发器资源,大大缩短了开发周期。

39.实施例4

40.本发明中,参见图1,信号处理模块集成了自主重新封测的大容量ddr4裸芯,一片裸芯的容量可达4gb,同时在pl端和ps端挂载两颗,总容量达到8gb,免去了外部再重新安装储存芯片的电路需求。同时通过先进的集成技术,使得ddr4的工作频率能达到2666mhz,满足在高采样率、高带宽的采集数据回传和发射速率的要求,提高了mimo雷达的整体性能需求。

41.实施例5

42.本发明中,参见图1和图4,时钟源统一分发到本振、adc、dac、arm、fpga、ddr、nor flash等器件的时钟端口,满足雷达的时钟同源准则,同时减少了时钟网络的布局。而且时钟源还能通过fpga的总线协议端口控制配置,根据任务需求实际配置。本发明由于集成度

高,使得微系统内部时钟线短,受到的干扰更小,功耗更低,信号的质量更好,fpga、arm、ddr4、adc和dac、本振等模块的信号完整性能更加稳定可靠。

43.虽然,本说明书中已经用一般性说明及具体实施方案对本发明作了详尽的描述,但在本发明基础上,可以对之作一些修改或改进,这对本领域技术人员而言是显而易见的。因此,在不偏离本发明精神的基础上所做的这些修改或改进,均属于本发明要求保护的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。