1.本技术涉及显示领域,特别涉及一种阵列基板及显示面板。

背景技术:

2.lcd(liquid crystal display,液晶显示器)是目前市场上应用最为广泛的显示产品,其生产工艺技术成熟、良率高,生产成本较低,市场接受度高。

3.在现有的液晶显示器中,阵列基板侧的像素电极常设计为米字型,并分割为多个区域以改善视角特性。但是在靠近像素驱动区的部分像素电极,由于受到薄膜晶体管中栅极、源极或漏极等金属层电压的影响,使得该区域的像素电极的电压不准确,进而导致液晶配向异常的技术问题。

4.因此,目前亟需一种阵列基板及显示面板以解决上述问题。

技术实现要素:

5.本技术提供了一种阵列基板及显示面板,以改善现有显示面板的因像素电极的配向电压不准确而导致配向异常的技术问题。

6.为解决上述方案,本技术提供的技术方案如下:

7.本技术提供一种阵列基板,所述阵列基板包括多条扫描线和多条数据线,多条所述扫描线和多条所述数据线围成多个像素单元,所述像素单元包括薄膜晶体管区和像素电极区;

8.所述像素单元包括设置在所述薄膜晶体管区的薄膜晶体管层以及设置在所述像素电极区的像素电极层,所述像素电极层包括像素电极,所述薄膜晶体管层包括薄膜晶体管,所述像素电极与所述薄膜晶体管电连接;

9.其中,所述像素单元还包括设置于所述薄膜晶体管区内的屏蔽构件,在所述第一方向上,所述屏蔽构件与所述像素电极的间距为第一阈值,所述第一方向与所述数据线的延伸方向平行。

10.在本技术的阵列基板中,所述像素电极包括主干电极和与所述主干电极连接的多条分支电极,所述主干电极包括第一主干电极和第二主干电极,所述第一主干电极和所述第二主干电极将所述像素电极区分隔为多个像素电极子区,所述分支电极设置于所述像素电极子区内,每一所述分支电极与所述第一主干电极或所述第二主干电极呈第一预设角度设置;

11.其中,相邻两个所述像素电极子区内的所述分支电极呈非对称设置。

12.在本技术的阵列基板中,所述阵列基板还包括位于所述数据线上的多条屏蔽主线,所述屏蔽主线与所述数据线平行设置,一所述屏蔽主线与一所述数据线对应;

13.其中,所述屏蔽构件包括与相邻两条所述屏蔽主线连接的第一屏蔽线,在所述第一方向上,所述第一屏蔽线与所述像素电极的间距为所述第一阈值。

14.在本技术的阵列基板中,所述像素电极还包括位于所述像素电极外围的外围电

极,所述外围电极与所述第一主干电极、所述第二主干电极及所述分支电极连接;

15.其中,所述屏蔽构件向所述像素电极区延伸,与所述外围电极、所述主干电极或所述分支电极中的至少一者电连接。

16.在本技术的阵列基板中,所述像素电极包括沿所述数据线的延伸方向设置的至少一所述第一外围电极;

17.所述屏蔽构件包括多条第一屏蔽引线,所述第一屏蔽引线的一端向所述像素电极区延伸以及与所述分支电极和所述第一外围电极连接,所述第一屏蔽引线的另一端向所述薄膜晶体管中的接触孔延伸以及与所述薄膜晶体管连接。

18.在本技术的阵列基板中,所述像素电极包括沿所述数据线的延伸方向设置的至少一所述第一外围电极;

19.所述屏蔽构件包括沿所述扫描线的延伸方向设置的第二屏蔽线,所述第二屏蔽线与一所述像素电极子区对应,且所述第二屏蔽线与对应的所述像素电极子区中的分支电极分离设置;

20.其中,一所述第一外围电极或/和一所述第一主干电极的端部向所述薄膜晶体管区延伸以及与所述第二屏蔽线连接。

21.在本技术的阵列基板中,所述屏蔽构件包括多条第二屏蔽引线,所述第二屏蔽引线的一端与所述第二屏蔽线连接,所述第二屏蔽引线的另一端向所述薄膜晶体管中的接触孔延伸以及与所述薄膜晶体管连接。

22.在本技术的阵列基板中,所述像素电极还包括沿所述扫描线的延伸方向设置的至少一所述第二外围电极,所述第二外围电极与所述第二屏蔽线平行;

23.其中,所述第二外围电极与所述分支电极、所述第一主干电极以及所述第一外围电极连接中的至少一者连接。

24.在本技术的阵列基板中,所述像素电极包括沿所述扫描线的延伸方向设置的至少一所述第二外围电极,相邻两个所述像素电极子区内的所述第二外围电极与所述第二主干电极的间距不相等。

25.本技术还提出了一种显示面板,所述显示面板包括上述阵列基板、彩膜基板以及位于所述阵列基板与所述彩膜基板之间的液晶层。

26.本技术还提出了一种移动终端,所述移动终端包括终端主体和上述显示面板,所述终端主体和所述显示面板组合为一体。

27.有益效果:本技术提供了一种阵列基板及显示面板,所述阵列基板包括多条扫描线和多条数据线,多条所述扫描线和多条所述数据线围成多个像素单元,所述像素单元包括薄膜晶体管区和像素电极区,以及设置于所述薄膜晶体管区内的薄膜晶体管和设置于所述像素电极区内的像素电极,所述像素电极与所述薄膜晶体管电连接;同时,本技术还在薄膜晶体管区内设置屏蔽构件,以及屏蔽构件与像素电极在数据线的延伸方向上的间距为第一阈值,使得屏蔽构件将靠近像素电极区设置的薄膜晶体管中金属层的电压屏蔽,避免了薄膜晶体管的金属层对该区域像素电极的配向电压的影响,改善了该区域中像素电极的因配向电压不准确而导致配向异常的技术问题。

附图说明

28.下面结合附图,通过对本技术的具体实施方式详细描述,将使本技术的技术方案及其它有益效果显而易见。

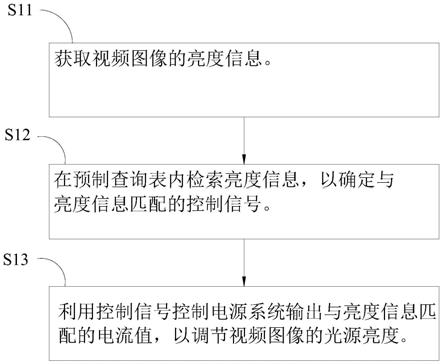

29.图1为本技术阵列基板的俯视结构简图;

30.图2为本技术实施例一中像素单元的结构图;

31.图3为本技术实施例一中像素单元的简化图;

32.图4为图2中截面aa的剖面图;

33.图5为本技术实施例二中像素单元的第一种结构图;

34.图6为本技术实施例二中像素单元的第二种结构图;

35.图7为本技术实施例二中像素单元的第三种结构图;

36.图8为本技术实施例三中像素单元的第一种结构图;

37.图9为本技术实施例三中像素单元的第二种结构图;

38.图10为本技术实施例三中像素单元的第三种结构图;

39.图11为本技术实施例四中像素单元的第一种结构图;

40.图12为本技术实施例四中像素单元的第二种结构图;

41.图13为本技术实施例四中像素单元的第三种结构图;

42.图14为本技术实施例四中像素单元的第四种结构图;

43.图15为本技术实施例五中像素单元的结构图;

44.图16为本技术实施例六中像素单元的结构图。

具体实施方式

45.下面将结合本技术实施例中的附图,对本技术实施例中的技术方案进行清楚、完整地描述。显然,所描述的实施例仅仅是本技术一部分实施例,而不是全部的实施例。基于本技术中的实施例,本领域技术人员在没有作出创造性劳动前提下所获得的所有其他实施例,都属于本技术保护的范围。

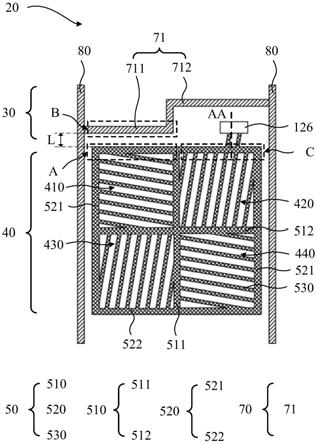

46.请参阅图1至图16,本技术提供一种阵列基板100,所述阵列基板100包括多条扫描线gate和多条数据线date,多条所述扫描线gate和多条所述数据线date围成多个像素单元20,所述像素单元20包括薄膜晶体管区30和像素电极区40。

47.在本实施例中,所述像素单元20包括设置在所述薄膜晶体管区30的薄膜晶体管层12和设置在所述像素电极区40的像素电极层13,所述像素电极层13包括像素电极50,所述薄膜晶体管层12包括薄膜晶体管60,所述像素电极50与所述薄膜晶体管60电连接。

48.在本实施例中,所述像素单元20还包括设置于所述薄膜晶体管区30内的屏蔽构件70;在所述第一方向上,所述屏蔽构件与所述像素电极50的间距l为第一阈值,所述第一方向与所述数据线date的延伸方向平行。

49.在实施例中,所述第一阈值本技术不作具体限定,其可以为0或者大于0的某一数值,第一阈值为0时,则所述屏蔽构件70与像素电极50连接;第一阈值为大于0的某一数值时,则所述屏蔽构件70与像素电极50分离设置。

50.本技术提供了一种阵列基板100及显示面板,所述阵列基板100包括多条扫描线gate和多条数据线date,多条所述扫描线gate和多条所述数据线date围成多个像素单元

20,所述像素单元20包括薄膜晶体管区30和像素电极区40,以及设置于所述薄膜晶体管区30内的薄膜晶体管60和设置于所述像素电极区40内的像素电极50,所述像素电极50与所述薄膜晶体管60电连接;同时,本技术还在薄膜晶体管区30内设置屏蔽构件70,以及屏蔽构件70与像素电极50在数据线date的延伸方向上的间距l为第一阈值,使得屏蔽构件70将靠近像素电极区40设置的薄膜晶体管60中金属层的电压屏蔽,避免了薄膜晶体管60的金属层对该区域像素电极50的配向电压的影响,改善了该区域中像素电极50的因配向电压不准确而导致配向异常的技术问题。

51.需要说明的是,所述屏蔽构件70可以与所述像素电极50同层设置或非同层设置,本技术不作具体限定,下文以所述屏蔽构件70与所述像素电极50同层设置进行描述。

52.现结合具体实施例对本技术的技术方案进行描述。

53.本技术的像素电极50可以为4畴分区或8畴分区,下面实施例中以4畴分区为例对本技术的技术方案进行说明。

54.在现有的液晶显示面板中,像素电极50通常包括主干电极510和分支电极530,主干电极510将像素电极50分割为多个区域。在电场和手性剂的作用下,液晶会向主干电极510收敛,而对于相邻区域内的分支电极530呈对称设置的结构,液晶在收敛到主干电极510时,相邻区域内的液晶在旋转方向上产生冲突,从而呈现大量暗纹。

55.请参阅图2至图16,所述像素电极50可以包括第一主干电极511、第二主干电极512和外围电极520,所述第一主干电极511和所述第二主干电极512将所述像素电极区40分隔为多个像素电极子区,所述像素电极子区内设置有与所述第一主干电极511和所述第二主干电极512电连接的多个分支电极530,每一所述分支电极530与所述第一主干电极511或所述第二主干电极512呈第一预设角度设置;相邻两个所述像素电极子区内的所述分支电极530呈非对称设置。

56.在本实施例中,所述第一主干电极511可以沿所述数据线date的延伸方向平行设置,所述第二主干电极512可以沿所述扫描线gate的延伸方向平行设置,即所述第一主干电极511和所述第二主干电极512垂直。请参阅图2至图16,所述第一主干电极511和所述第二主干电极512可以将所述像素电极50分隔为第一像素电极子区410、第二像素电极子区420、第三像素电极子区430以及第四像素电极子区440,相邻两个所述像素电极子区内的所述分支电极530呈非对称设置。由于相邻像素电极子区内的分支电极530非对称设置,因此相邻的像素电极子区内的所述分支电极530与对应的所述第一主干电极511或所述第二主干电极512所形成的夹角不相同。

57.在本实施例中,所述外围电极520可以包括至少一所述第一外围电极521或/和至少一所述第二外围电极522,所述第一外围电极521沿所述数据线date方向设置,所述第二外围电极522沿所述扫描线gate方向设置。即所述第一外围电极521可以与所述数据线date平行设置,所述第二外围电极522可以与所述扫描线gate平行设置,所述第一外围电极521可以与所述分支电极530及所述第二主干电极512连接,所述第二外围电极522可以与所述分支电极530及所述第一主干电极511连接。

58.本实施例通过将相邻两个所述像素电极子区内的所述分支电极530呈非对称设置,避免了液晶在主干电极510收敛时,相邻所述像素电极子区对应的液晶在旋转方向产生冲突的技术问题,以及提高了像素电极50结构的光穿透率,并且提高不同像素电极子区之

间的亮度均匀性。

59.请参阅图2,图2为本技术实施例一中像素单元20的第一种结构图。

60.图2所示的结构虽然将相邻两个所述像素电极子区内的所述分支电极530呈非对称设置,可以提高不同像素电极子区之间的亮度均匀性,但是由于所述分支电极530与所述像素电极50的外围电极520呈小角度设置,例如请参阅图2,区域a为分支电极530与外围电极520的夹角小于45

°

的区域,区域c为分支电极530与外围电极520的夹角大于45

°

的区域,区域a中的电场方向和地形与区域c中的电场方向和地形不相同,小角度区域的地形更差,易出现配向异常;另外,区域b为靠近区域a的薄膜晶体管60中的金属层所在的区域,区域b中的金属层将影响区域a中分支电极530的配向电压,使得区域a中的分支电极530因配向电压不准确而导致液晶配向异常。

61.请参阅图2,所述阵列基板100还包括设置于所述数据线date上的多条屏蔽主线80,所述屏蔽主线80与所述数据线date平行设置,一所述屏蔽主线80与一所述数据线date对应。所述屏蔽主线80可以与所述像素电极50同层设置,以及所述屏蔽主线80可以与所述像素电极50在同一道工艺中形成。在所述阵列基板100的俯视图方向上,所述屏蔽主线80可以与所述数据线date重叠设置,即所述屏蔽主线80用于遮挡数据线date,以屏蔽所述数据线date对液晶分子偏转所产生的影响。

62.在本实施例中,所述屏蔽主线80接地。

63.在本实施例中,所述阵列基板100还包括构成所述屏蔽构件70的第一屏蔽线71,所述第一屏蔽线71与相邻两条所述屏蔽主线80连接;其中,在所述数据线date的延伸方向上,所述第一屏蔽线71与所述分支电极530的最小间距l小于6微米。

64.请参阅图2和图3,所述第一像素电极子区410中的分支电极530与所述第二外围电极522在延伸方向上的夹角a小于所述第二像素电极子区420中的分支电极530与所述第二外围电极522在延伸方向上的夹角b,即所述第一像素电极子区410中的分支电极530与所述第二外围电极522呈小角度设置。

65.需要说明的是,分支电极的延伸方向为朝向与分支电极连接的主干电极,外围电极的延伸方向为朝向与外围电极连接的主干电极。例如,请参阅图2和图3,所述第一像素电极子区410和所述第二像素电极子区420中的分支电极530均与所述第一主干电极511连接,因此所述第一像素电极子区410和所述第二像素电极子区420中的分支电极530的延伸方向朝向所述第一主干电极511;所述第一像素电极子区410和所述第二像素电极子区420中的所述第二外围电极522均与所述第一主干电极511连接,因此所述第一像素电极子区410和所述第二像素电极子区420中的所述第二外围电极522朝向所述第一主干电极511,具体朝向及夹角如图3所示。

66.所述第一屏蔽线71可以包括靠近像素电极区40设置的第一连接段711和远离像素电极区40设置的第二连接段712,所述第一连接段711与所述第一像素电极子区410对应,所述第二连接段712与所述第二像素电极子区420对应,所述第一连接段711与所述第二外围电极522的最小间距l为第一阈值,所述第一阈值可以为小于6微米且大于0的任一数值。

67.在本实施例中,由于所述第二像素电极子区420中的分支电极530与所述第二外围电极522的夹角大于45

°

,因此薄膜晶体管60中金属层对区域c中的分支电极530的配向电压的影响较小。其中,所述第二像素电极子区420中分支电极530向接触孔126延伸,以及所述

像素电极50通过接触孔126与所述薄膜晶体管60电连接。

68.请参阅图4,图4为图2中截面aa的剖面图。

69.所述阵列基板100可以包括衬底11位于所述衬底11上的薄膜晶体管层12。所述衬底11的材料可以为玻璃、石英或聚酰亚胺等材料制备。所述薄膜晶体管层12包括多个薄膜晶体管60。所述薄膜晶体管60可以为蚀刻阻挡型、背沟道蚀刻型或顶栅薄膜晶体管型等结构,具体没有限制。例如底栅薄膜晶体管型的所述薄膜晶体管60可以包括位于所述衬底11上的栅极层121、位于所述栅极层121上的栅绝缘层122、位于所述栅绝缘层122上的半导体层123、位于所述半导体层123上的源漏极层124、及位于所述源漏极层124上的钝化层125。其中,所述栅极层121可以包括栅极和扫描线gate,所述源漏极层124可以包括源极、漏极和数据线date等,所述钝化层125上形成有所述接触孔126,所述像素电极50通过所述接触孔126与所述薄膜晶体管60的源/漏极连接。

70.在本实施例中,由于区域b中的金属层对区域a中的分支电极530的配向电压产生一定的影响,因此本技术将所述第一屏蔽线71的第一连接段711靠近区域a设置,且通过第一连接段711将靠近区域a的薄膜晶体管60的金属层遮挡,缓解了薄膜晶体管60的金属层对区域a中的分支电极530的配向电压的影响,改善了区域a中分支电极530的因配向电压不准确而导致配向异常的技术问题。

71.请参阅图5,图5为本技术实施例二中像素单元20的第一种结构图。

72.所述像素电极50包括设置于所述像素电极50外围的两条第一外围电极521和一条第二外围电极522,两条所述第一外围电极521位于所述第一主干电极511的两侧,且与四个像素电极子区中的所述分支电极530连接,一条所述第二外围电极522与所述第三像素电极子区430和所述第四像素电极子区440中的分支电极530连接。

73.在本实施例中,所述像素单元20还包括构成所述屏蔽构件70的多条第一屏蔽引线73,所述第一屏蔽引线73的一端向所述像素电极区40延伸以及与所述分支电极530和所述第一外围电极521直接连接,所述第一屏蔽引线73的另一端向所述薄膜晶体管60中的接触孔126延伸以及与所述薄膜晶体管60连接。

74.与图2中的结构相比,图5所示的结构相当于将靠近薄膜晶体管区30的一条第二外围电极522去除,即将第一像素电极子区410和第二像素电极子区420中的第二外围电极522去除,以及将接触孔126的位置移至与第一像素电极子区410对应的区域,第一像素电极子区410中的分支电极530向所述接触孔126延伸以及与所述薄膜晶体管60连接,因此本实施例中的多条第一屏蔽引线73相当于第一像素电极子区410中的分支电极530的延长线。

75.在本实施例中,由于区域b中的金属层对区域a中的分支电极530的配向电压产生一定的影响,而本技术将区域a中的所述第二外围电极522去除,避免了区域a中的分支电极530与外围电极520呈小角度设置,改善了区域a中分支电极530的地形;其次,多条第二屏蔽线72的存在,屏蔽了区域b中的金属层所形成的电场,减弱了区域b中的金属层对区域a中的分支电极530的配向电压的影响,改善了区域a中的分支电极530因配向电压不准确而导致配向异常的技术问题。

76.请参阅图6,图6为本技术实施例二中像素单元20的第二种结构图。

77.所述像素电极50包括设置于所述像素电极50外围的两条第一外围电极521和两条第二外围电极522。其中,两条所述第二外围电极522的长度不相同。

78.与图5中的结构相比,本实施例在第二像素电极子区420中设置一第二外围电极522,所述第二像素电极子区420中的部分分支电极530与所述第二外围电极522直接连接。由于所述第二像素电极子区420中的第二外围电极522与分支电极530的夹角大于45

°

,并且区域c中的分支电极与区域b的间距大于区域a中的分支电极530与区域b的间距,因此区域b中的金属层对区域c中分支电极530电压的影响小于区域b中的金属层对区域a中分支电极530电压的影响,并且第二像素电极子区420中的第二外围电极522对相邻薄膜晶体管区30中的金属层也起到一定的屏蔽作用,进一步保证了区域c中分支电极530电压的准确性。

79.请参阅图7,图7为本技术实施例二中像素单元20的第三种结构图。

80.图7中的结构与图6中的结构相似,不同之处在于:与图6中的结构相比,本实施例还将所述像素单元20中第二像素电极子区420中的第一外围电极521、第三像素电极子区430中的第一外围电极521、以及第四像素电极子区440中的第二外围电极522去除,即避免对应像素电极子区中的分支与外围电极520呈小角度设置,改善易出现配向异常的地形,提高配向的准确性。

81.请参阅图8,图8为本技术实施例三中阵像素单元20的第一种结构图。

82.所述像素电极50包括设置于所述像素电极50外围的两条第一外围电极521和两条第二外围电极522,两条所述第一外围电极521位于所述第一主干电极511的两侧,且与四个像素电极子区中的所述分支电极530连接,两条所述第二外围电极522位于所述第二主干电极512的两侧,且与四个像素电极子区中的所述分支电极530连接。

83.在本实施例中,所述像素单元20还包括构成所述屏蔽构件70的一第二屏蔽线72,所述第二屏蔽线72与一所述像素电极子区对应,且所述第二屏蔽线72与所述第一像素电极子区410中的分支电极530分离设置。

84.在本实施例中,第二屏蔽线72与第一像素电极子区410对应,位于所述第一像素电极子区410和所述第三像素电极子区430中的所述第一外围电极521的端部向所述薄膜晶体管区30延伸以及与所述第二屏蔽线72连接。另外,图8中的结构与图2类似,所述接触孔126与第二像素电极子区420对应,第二像素电极子区420中部分分支电极530向接触孔126延伸以及与薄膜晶体管60连接。

85.与图2中的结构相比,图8所示的结构相当于在薄膜晶体管区30中增加一与所述第二外围电极522平行的电极,以构成本实施例中的所述第二屏蔽线72;而即使区域a中的分支电极530与所述第二外围电极522呈小角度设置,但是所述第二屏蔽线72屏蔽了区域b中的金属层所形成的电场,减弱了区域b中的金属层对区域a中的分支电极530的配向电压的影响,改善了区域a中的分支电极530因配向电压不准确而导致配向异常的技术问题。

86.请参阅图9,图9为本技术实施例三中像素单元20的第二种结构图。

87.图9中的结构与图8中的结构相似,不同之处在于:所述像素电极区40中的所述第一主干电极511的端部向所述薄膜晶体管区30延伸以及与所述第二屏蔽线72连接。即图8中的第二屏蔽线72与所述像素电极50形成具有朝向区域c的开口,图9中的第二屏蔽线72与所述像素电极50形成的开口朝向与图8中的实施例相反。

88.请参阅图10,图10为本技术实施例三中像素单元20的第三种结构图。

89.图10中的结构与图8和图9中的结构相似,不同之处在于:位于所述第一像素电极子区410和所述第三像素电极子区430中的所述第一外围电极521的端部向所述薄膜晶体管

区30延伸以及与所述第二屏蔽线72连接,以及所述像素电极区40中的所述第一主干电极511的端部向所述薄膜晶体管区30延伸以及与所述第二屏蔽线72连接,所述第二屏蔽线72与所述第一主干电极511和第一外围电极521的延长线形成闭环回路。

90.在本实施例中,图9和图10中结构与图8中的结构相似,所述第二屏蔽线可以72屏蔽区域b中的金属层所形成的电场,改善了区域a中的分支电极530因配向电压不准确而导致配向异常的技术问题。

91.同理,所述像素单元20还可以包括构成所述屏蔽构件70的多条第二屏蔽线72(未示出),相邻两条所述第二屏蔽线72可以平行设置。多条所述第二屏蔽线72的设置可以进一步减弱区域b中的金属层对区域a中分支电极530的电压的影响。

92.请参阅图11,图11为本技术实施例四中像素单元20的第一种结构图。

93.所述像素电极50包括设置于所述像素电极50外围的两条第一外围电极521,两条所述第一外围电极521位于所述第一主干电极511的两侧,且与四个像素电极子区中的所述分支电极530连接。

94.在本实施例中,所述像素单元20还包括构成所述屏蔽构件70的至少一第二屏蔽线72,所述第二屏蔽线72与一所述像素电极子区对应,且所述第二屏蔽线72与所述第一像素电极子区410中的分支电极530分离设置。

95.在本实施例中,所述像素单元20还包括构成所述屏蔽构件70的多条第二屏蔽引线74,所述第二屏蔽引线74的一端与所述第二屏蔽线72连接,所述第二屏蔽引线74的另一端向所述薄膜晶体管60中的接触孔126延伸以及与所述薄膜晶体管60连接。其中,位于所述第一像素电极子区410和所述第三像素电极子区430中的所述第一外围电极521的端部向所述薄膜晶体管区30延伸以及与所述第二屏蔽线72连接。

96.与图8中的结构相比,图11所示的结构相当于将像素电极区40中的第二外围电极522去除,避免了区域a中的分支电极530与外围电极520呈小角度设置,改善了区域a中分支电极530的地形;另外,所述第二屏蔽线72以及多条所述第二屏蔽引线74的设置,屏蔽了区域b中的金属层所形成的电场,减弱了区域b中的金属层对区域a中的分支电极530的配向电压的影响,改善了区域a中的分支电极530因配向电压不准确而导致配向异常的技术问题。

97.另外,由于区域b中的金属层对区域a中的分支电极530影响最大,在图8的基础上,可以仅仅去除区域a中的外围电极520,以及保留第二像素电极子区420、第三像素电极子区430以及第四像素电极子区440中的外围电极520。

98.请参阅图12,图12为本技术实施例四中像素单元20的第二种结构图。

99.图12中的结构与图11中的结构相似,不同之处在于:所述像素电极区40中的所述第一主干电极511的端部向所述薄膜晶体管区30延伸以及与所述第二屏蔽线72连接。即图11中的第二屏蔽线72与所述像素电极50形成具有朝向区域c的开口,图12中的第二屏蔽线72与所述像素电极50形成的开口朝向与图11中的实施例相反。

100.请参阅图13,图13为本技术实施例四中像素单元20的第三种结构图。

101.图13中的结构与图11和图12中的结构相似,不同之处在于:位于所述第一像素电极子区410和所述第三像素电极子区430中的所述第一外围电极521的端部向所述薄膜晶体管区30延伸以及与所述第二屏蔽线72连接,以及所述像素电极区40中的所述第一主干电极511的端部向所述薄膜晶体管区30延伸以及与所述第二屏蔽线72连接,所述第二屏蔽线72

与所述第一主干电极511和第一外围电极521的延长线形成闭环回路。

102.在本实施例中图12和图13中结构与图11中的结构相似,其均可以避免了区域a中的分支电极530与外围电极520呈小角度设置,改善了区域a中分支电极530的地形,以及屏蔽了区域b中的金属层所形成的电场,改善了区域a中的分支电极530因配向电压不准确而导致配向异常的技术问题。

103.请参阅图14,图14为本技术实施例四中像素单元20的第四种结构图。

104.位于所述第一像素电极子区410中的部分所述分支电极530的端部向所述薄膜晶体管区30延伸以及与所述第二屏蔽线72连接。与图11至图13中的结构相比,所述第二屏蔽线72与所述第一外围电极521和所述第一主干电极511分离,以及所述第二屏蔽线72与所述第一像素电极子区410中的部分所述分支电极530连接。

105.在本实施例中,所述第一像素电极子区410中的部分所述分支电极530与所述第二屏蔽线72呈小角度设置,而由于所述分支电极530与所述第二屏蔽线72呈小角度设置的区域位于所述薄膜晶体管区30,该区域的异常将被对应遮光材料,例如黑色遮光胶或金属等遮挡,因此本实施例即使出现配向异常区域,但是对透光区域中的像素电极50影响较小;另外,分支电极530的延长线、所述第二屏蔽线72以及所述第二屏蔽引线74三者均具备一定的电压,其可以屏蔽了区域b中的金属层所形成的电场,减弱了区域b中的金属层对区域a中的分支电极530的配向电压的影响,改善了区域a中的分支电极530因配向电压不准确而导致配向异常的技术问题。

106.请参阅图15,图15为本技术实施例五中像素单元20的第一种结构图。

107.所述像素电极50可以包括设置于所述像素电极50外围的两条第一外围电极521和两条第二外围电极522,两条所述第一外围电极521位于所述第一主干电极511的两侧,且与四个像素电极子区中的所述分支电极530连接,两条所述第二外围电极522与所述第三像素电极子区430和所述第四像素电极子区440中的分支电极530连接。其中,相邻两个所述像素电极子区内的所述第二外围电极522与所述第二主干电极512的间距不相等,即设置于所述第一像素电极子区410中的第二外围电极522与设置于所述第二像素电极子区420中的第二外围电极522不再同一条直线上。

108.在本实施例中,所述像素单元20还可以包括构成所述屏蔽构件70的至少一第二屏蔽线72,所述第二屏蔽线72与一所述像素电极子区对应,且所述第二屏蔽线72与所述第一像素电极子区410中的分支电极530分离设置。其中,所述第二屏蔽线72设置于所述薄膜晶体管区30与所述像素电极区40的交界处,所述第二屏蔽线72与所述第二外围电极522平行设置,且与所述第二像素电极子区420中的第二外围电极522在同一条直线上,所述第二屏蔽线72与所述第二像素电极子区420中的第二外围电极522可以连接或不连接,图15公开的结构中所述第二屏蔽线72与所述第二像素电极子区420中的第二外围电极522连接设置。

109.请参阅图15,与图8中的结构相比,本实施例区域a中的结构下移,并且第二屏蔽线72的存在,增加了区域a和区域b的间距,减弱了区域b中的金属层对区域a中的分支电极530的配向电压的影响,改善了区域a中的分支电极530因配向电压不准确而导致配向异常的技术问题。

110.下面实施例将以8畴分区的像素电极50为例对本技术的技术方案进行说明。

111.请参阅图16,图16为本技术实施例六中像素单元20的第一种结构图。

112.所述像素单元20可以包括薄膜晶体管区30和位于所述薄膜晶体管区30两侧的像素电极区40,同一像素单元20内的两个所述像素电极区40内的像素电极50的结构可以相同或不同,任一所述像素电极区40内的像素电极50的结构可以与上述实施例一至实施例五中4畴分区的像素电极50的结构相同。

113.在图16中,两个所述像素电极区40内的像素电极50的结构不相同,即区域m和区域n中的像素电极50结构不相同。图16中的区域m内像素电极的结构可以与图8中像素电极的结构相同,区域n内像素电极的结构可以与图15中像素电极的结构相同,此处不再赘述。

114.本技术还提出了一种显示面板,所述显示面板包括阵列基板、彩膜基板、及位于所述彩膜基板与所述阵列基板之间的液晶层。所述显示面板的工作原理与上述阵列基板的工作原理相同或相似。

115.本技术还提出了一种移动终端,所述移动终端包括终端主体和上述显示面板,所述终端主体和所述显示面板组合为一体。所述移动终端的工作原理与所述显示面板的工作原理相同或相似。所述移动终端可以为但不限于手机、电脑、笔记本等。

116.本技术提供了一种阵列基板及显示面板,所述阵列基板包括多条扫描线和多条数据线,多条所述扫描线和多条所述数据线围成多个像素单元,所述像素单元包括薄膜晶体管区和像素电极区,以及设置于所述薄膜晶体管区内的薄膜晶体管和设置于所述像素电极区内的像素电极,所述像素电极与所述薄膜晶体管电连接,同时本技术还在薄膜晶体管层上设置屏蔽构件,以及屏蔽构件与像素电极在数据线的延伸方向上的间距为第一阈值,使得屏蔽构件将靠近像素电极区设置的薄膜晶体管中金属层的电压屏蔽,避免了薄膜晶体管的金属层对该区域像素电极的配向电压的影响,改善了该区域中像素电极的因配向电压不准确而导致配向异常的技术问题。

117.在上述实施例中,对各个实施例的描述都各有侧重,某个实施例中没有详述的部分,可以参见其他实施例的相关描述。

118.以上对本技术实施例所提供的一种阵列基板及显示面板进行了详细介绍,本文中应用了具体个例对本技术的原理及实施方式进行了阐述,以上实施例的说明只是用于帮助理解本技术的技术方案及其核心思想;本领域的普通技术人员应当理解:其依然可以对前述各实施例所记载的技术方案进行修改,或者对其中部分技术特征进行等同替换;而这些修改或者替换,并不使相应技术方案的本质脱离本技术各实施例的技术方案的范围。

再多了解一些

本文用于企业家、创业者技术爱好者查询,结果仅供参考。